Escolar Documentos

Profissional Documentos

Cultura Documentos

Design of Testable Reversible Sequential Circuits

Enviado por

TechnosIndiaDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Design of Testable Reversible Sequential Circuits

Enviado por

TechnosIndiaDireitos autorais:

Formatos disponíveis

DESIGN OF TESTABLE REVERSIBLE SEQUENTIAL

CIRCUITS

ABSTRACT:

In this paper, we propose the design of two vectors testable sequential circuits based on

conservative logic gates. The proposed sequential circuits based on conservative logic gates

outperform the sequential circuits implemented in classical gates in terms of testability. Any

sequential circuit based on conservative logic gates can be tested for classical unidirectional

stuck-at faults using only two test vectors. The two test vectors are all 1s, and all 0s. The designs

of two vectors testable latches, master-slave flip-flops and double edge triggered (DET) flipflops are presented. The importance of the proposed work lies in the fact that it provides the

design of reversible sequential circuits completely testable for any stuck-at fault by only two test

vectors, thereby eliminating the need for any type of scan-path access to internal memory cells.

The reversible design of the DET flip-flop is designed by Verilog Hardware Description

Language.

EXISTING SYSTEM:

In the existing works on reversible logic, the parity mismatch between the inputs and the

outputs is used for concurrent error detection. Hence, the existing works are limited for single bit

error at the outputs of the reversible logic circuits.

EXISTING SYSTEM TECHNIQUE:

Reversible Logic Technique

EXISTING SYSTEM DRAWBACKS:

More Complexity

PROPOSED SYSTEM:

In proposed system, we propose the design of testable sequential circuits based on

conservative logic gates. The proposed technique will take care of the fan-out (FO) at the output

of the reversible latches and can also disrupt the feedback to make them suitable for testing by

only two test vectors, all 0s and all 1s. The circuits will have feedback while executing in the

normal mode.

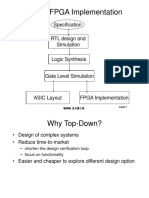

PROPOSED SYSTEM BLOCK DIAGRAM:

FREDKIN GATE BASED D LATCH:

FREDKIN GATE-BASED TESTABLE REVERSIBLE MASTER-SLAVE D FLIP-FLOP

FREDKIN GATE-BASED DET FLIP-FLOP:

PROPOSED SYSTEM TECHNIQUE:

Conservative Logic Reversible QCA Gate Technique

PROPOSED SYSTEM ADVANTAGES:

Testing Complexity reduced

Speed Increased

SOFTWARE REQUIREMENT:

ModelSim6.4c

Xilinx 9.1/13.2

HARDWARE REQUIREMENT:

FPGA Spartan 3/ Spartan 3AN

REAL TIME APPLICATION:

Fault coverage for single missing/additional cell

Testing sequential Circuits

FUTURE ENHANCEMENT:

The testing method will be implemented by using different Combinational or Sequential

circuits.

ALTERNATE TITLES:

Title 1: Implementation of Testable Reversible Sequential Circuits on FPGA

Title 2: Design of Testable Reversible Sequential Circuits based on Ferdkin gate

Title 3: Testable Reversible Sequential Circuits realization Using Verilog HDL

PROJECT FLOW:

Second Review:

Ferdkin Gate and Ferdkin Based Testable D Latch

First Phase:

Ferdkin Based Reversible Master Slave DFF

Third Review:

Ferdkin Based DET Flip-Flop

Fourth Review (Model)

Ferdkin Based DET Flip-Flop & Multiplexers

Final Review:

Future Enhancement (Synchronous and asynchronous Designs using Ferdkin gate)

Você também pode gostar

- Unit 5Documento41 páginasUnit 5sparsh kaudinyaAinda não há avaliações

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsNo EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsNota: 1 de 5 estrelas1/5 (1)

- Delay Testing: System-on-Chip Test Architectures Ch. 6 - Delay Testing - P. 1Documento50 páginasDelay Testing: System-on-Chip Test Architectures Ch. 6 - Delay Testing - P. 1Sudhakar SpartanAinda não há avaliações

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipAinda não há avaliações

- Lab5 Synopsys Tetramax DFTDocumento20 páginasLab5 Synopsys Tetramax DFTJay PadaliyaAinda não há avaliações

- Highly Integrated Gate Drivers for Si and GaN Power TransistorsNo EverandHighly Integrated Gate Drivers for Si and GaN Power TransistorsAinda não há avaliações

- Design For Testability and ScanDocumento19 páginasDesign For Testability and ScanZeina AhmedAinda não há avaliações

- Fault Tolerance and TestabilityDocumento16 páginasFault Tolerance and TestabilitySukhada DeshpandeAinda não há avaliações

- Design For Testability and Design For Testability and Built Built - in Self in Self - Test TestDocumento74 páginasDesign For Testability and Design For Testability and Built Built - in Self in Self - Test TestSyed Waqas Arif Shah100% (1)

- Testing Unit V VLSIDocumento23 páginasTesting Unit V VLSIkalavathi deviAinda não há avaliações

- Vasu DFTDocumento28 páginasVasu DFTsenthilkumarAinda não há avaliações

- Design For TestingDocumento29 páginasDesign For TestingNIKHIL GOWDAAinda não há avaliações

- Unit 5Documento60 páginasUnit 5sparsh kaudinyaAinda não há avaliações

- Digital Testing: Key Concepts of Scan-Path DesignDocumento54 páginasDigital Testing: Key Concepts of Scan-Path DesignaguohaqdoAinda não há avaliações

- Vlsi Module-5Documento56 páginasVlsi Module-5Phanindra ReddyAinda não há avaliações

- ACTEL 1020B-PL44 Datasheet - ACT1 - DSDocumento24 páginasACTEL 1020B-PL44 Datasheet - ACT1 - DSFX RaharjoAinda não há avaliações

- An Introduction To Scan Test For Test Engineers: Part 2 of 2Documento9 páginasAn Introduction To Scan Test For Test Engineers: Part 2 of 2Are VijayAinda não há avaliações

- An experimental chip to evaluate multiple testing techniquesDocumento10 páginasAn experimental chip to evaluate multiple testing techniquesVinod KheraAinda não há avaliações

- Design For Testability NotesDocumento41 páginasDesign For Testability NotesNaga Nithesh100% (3)

- Design For Testability and Automatic Test Pattern GenerationDocumento33 páginasDesign For Testability and Automatic Test Pattern GenerationDilip Mathuria0% (1)

- Controllability and Observability in Circuit TestingDocumento15 páginasControllability and Observability in Circuit TestingaashishscribdAinda não há avaliações

- (Design For Testability) Atpg: - Jaganath SinghDocumento23 páginas(Design For Testability) Atpg: - Jaganath SinghSAI KIRAN100% (3)

- Scan Path DesignDocumento54 páginasScan Path DesignGowtham HariAinda não há avaliações

- DFT For Advanced UserDocumento151 páginasDFT For Advanced UserAnonymous UeI6DVAinda não há avaliações

- VLSI Testing and Design for TestabilityDocumento19 páginasVLSI Testing and Design for TestabilityNikita SridharAinda não há avaliações

- VLSI Testing TechniquesDocumento32 páginasVLSI Testing TechniquesnagarajuAinda não há avaliações

- Vlsi TestingDocumento51 páginasVlsi TestingSriramAinda não há avaliações

- Practically Realizing Random Access Scan (RASDocumento34 páginasPractically Realizing Random Access Scan (RASsundar_mohan_2Ainda não há avaliações

- Fault ModelingDocumento23 páginasFault Modelingshivam007Ainda não há avaliações

- Traditional Asic DesignflowDocumento103 páginasTraditional Asic DesignflowYamini SaraswathiAinda não há avaliações

- A Multimode Scannable Memory Element For High Test Application eDocumento8 páginasA Multimode Scannable Memory Element For High Test Application eDat Nguyen ThanhAinda não há avaliações

- VLSI Presentation SBTDocumento11 páginasVLSI Presentation SBTJay TanwaniAinda não há avaliações

- Digital Test Digital Test Architectures ArchitecturesDocumento46 páginasDigital Test Digital Test Architectures ArchitecturesPAVAN KUMAR TAVADABOINAAinda não há avaliações

- Unit V Cmos Testing FinalDocumento76 páginasUnit V Cmos Testing FinalJagan Rajendiran50% (2)

- TestDocumento38 páginasTestRAHA TUDUAinda não há avaliações

- Testability Concepts and DFTDocumento5 páginasTestability Concepts and DFTkumkum_parishitAinda não há avaliações

- NXP Interview QuestionsDocumento29 páginasNXP Interview Questionsdeepa100% (1)

- TestingDocumento23 páginasTestingsangeethabgAinda não há avaliações

- SUN ScribdDocumento8 páginasSUN Scribdnadim.remaneAinda não há avaliações

- Dual-Vt Design of Fpgas For Subthreshold Leakage ToleranceDocumento6 páginasDual-Vt Design of Fpgas For Subthreshold Leakage Tolerancerostamedastan65Ainda não há avaliações

- Ece5745 Tut3 IccDocumento6 páginasEce5745 Tut3 IccAnonymous UeI6DVAinda não há avaliações

- FPGA Implementation of Self-Testing Logic Gates AdDocumento7 páginasFPGA Implementation of Self-Testing Logic Gates AdTakashi SuohAinda não há avaliações

- Reversible Logic-Based Concurrently Testable Latches For Molecular QCADocumento8 páginasReversible Logic-Based Concurrently Testable Latches For Molecular QCAPolisetti Sn BhaskarAinda não há avaliações

- Mod 4Documento33 páginasMod 4Adi MohantyAinda não há avaliações

- 005 Fpga Spartan Verilog 2003Documento41 páginas005 Fpga Spartan Verilog 2003Thiyagarajan VelayuthamAinda não há avaliações

- Basic ScanDocumento20 páginasBasic Scansaikumar bhavana100% (1)

- Debug and Testability Features For Multi-Protocol 10G SerdesDocumento5 páginasDebug and Testability Features For Multi-Protocol 10G SerdesvelusnAinda não há avaliações

- Design Analysis of NAND Gate Using Cascode-Voltage Switch LogicDocumento4 páginasDesign Analysis of NAND Gate Using Cascode-Voltage Switch LogicNeha Prashant VermaAinda não há avaliações

- Scan Chain BasicsDocumento8 páginasScan Chain Basicsprakashthamankar100% (3)

- L02 FaultModelingDocumento15 páginasL02 FaultModelingAmit RohillaAinda não há avaliações

- 2 Fault Modeling OverviewDocumento10 páginas2 Fault Modeling Overviewsamantha223Ainda não há avaliações

- DFT Interview Questions1Documento34 páginasDFT Interview Questions1rajkumar gunjaAinda não há avaliações

- CMOS Testing Techniques and Design for TestabilityDocumento22 páginasCMOS Testing Techniques and Design for TestabilitylokeshwarrvrjcAinda não há avaliações

- 8B-4 MOS TransistorDocumento4 páginas8B-4 MOS TransistorkammohAinda não há avaliações

- FPGA Interview QuestionsDocumento11 páginasFPGA Interview Questionssneha587Ainda não há avaliações

- Quartus software 1Documento5 páginasQuartus software 1Dhamini GowdaAinda não há avaliações

- Test AbilityDocumento13 páginasTest AbilityGaurav MehraAinda não há avaliações

- HP-AN1244-1 - Minimizing Intrusion Effects When Probing With A Logic AnalyzerDocumento16 páginasHP-AN1244-1 - Minimizing Intrusion Effects When Probing With A Logic Analyzersirjole7584Ainda não há avaliações

- Untitled 1Documento62 páginasUntitled 1Roshan RajuAinda não há avaliações

- Multifunction Residue ArchitecturesDocumento4 páginasMultifunction Residue ArchitecturesTechnosIndiaAinda não há avaliações

- Multicarrier Systems Based On MultistageDocumento4 páginasMulticarrier Systems Based On MultistageTechnosIndiaAinda não há avaliações

- Low-Power, High-Throughput, and Low-Area Adaptive Fir Filter Based On Distributed ArithmeticDocumento5 páginasLow-Power, High-Throughput, and Low-Area Adaptive Fir Filter Based On Distributed ArithmeticTechnosIndiaAinda não há avaliações

- Parallel Aes Encryption Engines For Many-Core Processor ArraysDocumento5 páginasParallel Aes Encryption Engines For Many-Core Processor ArraysTechnosIndiaAinda não há avaliações

- Flexible Integer DCT Architectures For HevcDocumento5 páginasFlexible Integer DCT Architectures For HevcTechnosIndiaAinda não há avaliações

- Improvement of The Security of Zigbee by A New Chaotic AlgorithmDocumento5 páginasImprovement of The Security of Zigbee by A New Chaotic AlgorithmTechnosIndiaAinda não há avaliações

- Low-Power and Area-Efficient Carry Select AdderDocumento5 páginasLow-Power and Area-Efficient Carry Select AdderTechnosIndiaAinda não há avaliações

- Low-Complexity Low-Latency Architecture For Matching of Data Encodedwith Hard SystematicDocumento5 páginasLow-Complexity Low-Latency Architecture For Matching of Data Encodedwith Hard SystematicTechnosIndiaAinda não há avaliações

- High-Throughput Multi Standard Transform Core Supporting Mpegh.264vc-1 Using Common Sharing Distributed ArithmeticDocumento4 páginasHigh-Throughput Multi Standard Transform Core Supporting Mpegh.264vc-1 Using Common Sharing Distributed ArithmeticTechnosIndiaAinda não há avaliações

- Low-Complexity Multiplier For GF (2m) Based On All-One PolynomialsDocumento5 páginasLow-Complexity Multiplier For GF (2m) Based On All-One PolynomialsTechnosIndiaAinda não há avaliações

- Efficient Integer DCT Architectures For HevcDocumento4 páginasEfficient Integer DCT Architectures For HevcTechnosIndiaAinda não há avaliações

- Measurement and Evaluation of Power AnalysisDocumento5 páginasMeasurement and Evaluation of Power AnalysisTechnosIndiaAinda não há avaliações

- Design of Efficient Binary ComparatorsDocumento4 páginasDesign of Efficient Binary ComparatorsTechnosIndiaAinda não há avaliações

- Gate Mapping Automation For AsynchronousDocumento4 páginasGate Mapping Automation For AsynchronousTechnosIndiaAinda não há avaliações

- Improved 8-Point Approximate DCT For Image and Video Compression Requiring Only 14 AdditionsDocumento6 páginasImproved 8-Point Approximate DCT For Image and Video Compression Requiring Only 14 AdditionsTechnosIndiaAinda não há avaliações

- Fast Sign Detection Algorithm For The Rns ModuliDocumento4 páginasFast Sign Detection Algorithm For The Rns ModuliTechnosIndiaAinda não há avaliações

- Area-Delay Efficient Binary Adders in QcaDocumento5 páginasArea-Delay Efficient Binary Adders in QcaTechnosIndiaAinda não há avaliações

- Eliminating Synchronization Latency UsingDocumento5 páginasEliminating Synchronization Latency UsingTechnosIndiaAinda não há avaliações

- Area Delay Power Efficient Carry Select AdderDocumento5 páginasArea Delay Power Efficient Carry Select AdderTechnosIndiaAinda não há avaliações

- Efficient Fpga and Asic Realizations ofDocumento4 páginasEfficient Fpga and Asic Realizations ofTechnosIndia100% (1)

- Design of Digit-Serial Fir Filters Algorithms, Architectures and A Cad ToolDocumento4 páginasDesign of Digit-Serial Fir Filters Algorithms, Architectures and A Cad ToolTechnosIndiaAinda não há avaliações

- Aging-Aware Reliable Multiplier Design With Adaptive Hold LogicDocumento4 páginasAging-Aware Reliable Multiplier Design With Adaptive Hold LogicTechnosIndia0% (1)

- Area-Efficient Parallel Fir Digital Filter Structures For Symmetric Convolutions Based On Fast Fir AlgorithmDocumento4 páginasArea-Efficient Parallel Fir Digital Filter Structures For Symmetric Convolutions Based On Fast Fir AlgorithmTechnosIndiaAinda não há avaliações

- Critical-Path Analysis and Low-ComplexityDocumento5 páginasCritical-Path Analysis and Low-ComplexityTechnosIndiaAinda não há avaliações

- Area Delay Power Efficient Fixed Point LmsDocumento4 páginasArea Delay Power Efficient Fixed Point LmsTechnosIndiaAinda não há avaliações

- Cordic Based Fast Radix-2 DCT AlgorithmDocumento5 páginasCordic Based Fast Radix-2 DCT AlgorithmTechnosIndiaAinda não há avaliações

- Design of An Error Detection and Data Recovery Architecture For Motion Estimation Testing ApplicationsDocumento4 páginasDesign of An Error Detection and Data Recovery Architecture For Motion Estimation Testing ApplicationsTechnosIndiaAinda não há avaliações

- Period Extension and Randomness Enhancement Using High-Throughput Reseeding-Mixing PRNGDocumento4 páginasPeriod Extension and Randomness Enhancement Using High-Throughput Reseeding-Mixing PRNGTechnosIndiaAinda não há avaliações

- A Novel Modulo Adder For 2n-2k-1 Residue Number SystemDocumento5 páginasA Novel Modulo Adder For 2n-2k-1 Residue Number SystemTechnosIndiaAinda não há avaliações

- SRM Institute of Science and Technology Department of Mathematics Probability and Queueing Theory Tutorial Sheet I2Documento1 páginaSRM Institute of Science and Technology Department of Mathematics Probability and Queueing Theory Tutorial Sheet I2Cooldude 69Ainda não há avaliações

- Control Lights with SOU-1 Twilight SwitchDocumento1 páginaControl Lights with SOU-1 Twilight SwitchjsblAinda não há avaliações

- Power Cable Installation ManualDocumento50 páginasPower Cable Installation ManualAnn DodsonAinda não há avaliações

- Pumps - IntroductionDocumento31 páginasPumps - IntroductionSuresh Thangarajan100% (1)

- Smart Dustbin using ArduinoDocumento22 páginasSmart Dustbin using ArduinoEr Dinesh TambeAinda não há avaliações

- Excel 2007 Lesson 7 QuizDocumento5 páginasExcel 2007 Lesson 7 Quizdeep72Ainda não há avaliações

- Ex - No: 4 Integrator and Differentiator Using Fpaa DateDocumento4 páginasEx - No: 4 Integrator and Differentiator Using Fpaa DatechandraprabhaAinda não há avaliações

- Appliance ShipmentsDocumento10 páginasAppliance ShipmentsnAinda não há avaliações

- Tunnel DamperDocumento8 páginasTunnel DamperIvanAinda não há avaliações

- Dollar Bill David Star - Verbal DiagramDocumento4 páginasDollar Bill David Star - Verbal DiagramLuciffer ChongAinda não há avaliações

- ISO 8243 2013 Cigarettes - SamplingDocumento18 páginasISO 8243 2013 Cigarettes - SamplingEko YuliantoAinda não há avaliações

- Sec 2 French ImmersionDocumento1 páginaSec 2 French Immersionapi-506328259Ainda não há avaliações

- Leroy Somer 3434c - GB-NyDocumento28 páginasLeroy Somer 3434c - GB-NyCris_eu09100% (1)

- Water Reducing - Retarding AdmixturesDocumento17 páginasWater Reducing - Retarding AdmixturesAbdullah PathanAinda não há avaliações

- The Order of Historical Time: The Longue Durée and Micro-HistoryDocumento17 páginasThe Order of Historical Time: The Longue Durée and Micro-HistoryGeorgia KoutaAinda não há avaliações

- 0001981572-JAR Resources in JNLP File Are Not Signed by Same CertificateDocumento13 páginas0001981572-JAR Resources in JNLP File Are Not Signed by Same CertificateAnonymous AZGp1KAinda não há avaliações

- Sensor CatalogueDocumento72 páginasSensor Cataloguefurious man67% (3)

- SDH TechnologyDocumento26 páginasSDH TechnologyJayesh SinghalAinda não há avaliações

- Introduction To Oracle GroovyDocumento53 páginasIntroduction To Oracle GroovyDeepak BhagatAinda não há avaliações

- Pipeline Corrosion Assessment MethodsDocumento21 páginasPipeline Corrosion Assessment MethodsGilletAinda não há avaliações

- Timers, Serial CommunicationDocumento19 páginasTimers, Serial CommunicationVyshnav PAinda não há avaliações

- ENGG1330 2N Computer Programming I (20-21 Semester 2) Assignment 1Documento5 páginasENGG1330 2N Computer Programming I (20-21 Semester 2) Assignment 1Fizza JafferyAinda não há avaliações

- Turbine Buyers Guide - Mick Sagrillo & Ian WoofendenDocumento7 páginasTurbine Buyers Guide - Mick Sagrillo & Ian WoofendenAnonymous xYhjeilnZAinda não há avaliações

- Manuale Fancoil - Eng 2012-Rev02Documento19 páginasManuale Fancoil - Eng 2012-Rev02ricardo daccacheAinda não há avaliações

- GenEd Mathematics LLL PDFDocumento32 páginasGenEd Mathematics LLL PDFArmely NiedoAinda não há avaliações

- Displaymax JR 1500 SpecsDocumento1 páginaDisplaymax JR 1500 SpecsFRANCISCOAinda não há avaliações

- How Dna Controls The Workings of The CellDocumento2 páginasHow Dna Controls The Workings of The Cellapi-238397369Ainda não há avaliações

- PF-CIS-Fall 2022 LABDocumento4 páginasPF-CIS-Fall 2022 LABMuhammad FaisalAinda não há avaliações

- Reference Mil-Aero Guide ConnectorDocumento80 páginasReference Mil-Aero Guide ConnectorjamesclhAinda não há avaliações

- Build Your Own Electric Vehicle, Third EditionNo EverandBuild Your Own Electric Vehicle, Third EditionNota: 4.5 de 5 estrelas4.5/5 (3)

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeNo EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeNota: 5 de 5 estrelas5/5 (8)

- High Performance Loudspeakers: Optimising High Fidelity Loudspeaker SystemsNo EverandHigh Performance Loudspeakers: Optimising High Fidelity Loudspeaker SystemsNota: 4 de 5 estrelas4/5 (1)

- The Graphene Revolution: The Weird Science of the Ultra-thinNo EverandThe Graphene Revolution: The Weird Science of the Ultra-thinNota: 4.5 de 5 estrelas4.5/5 (4)

- Understanding Automotive Electronics: An Engineering PerspectiveNo EverandUnderstanding Automotive Electronics: An Engineering PerspectiveNota: 3.5 de 5 estrelas3.5/5 (16)

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionNo EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionNota: 4.5 de 5 estrelas4.5/5 (542)

- 8051 Microcontroller: An Applications Based IntroductionNo Everand8051 Microcontroller: An Applications Based IntroductionNota: 5 de 5 estrelas5/5 (6)

- Off-Grid Projects: Step-by-Step Guide to Building Your Own Off-Grid SystemNo EverandOff-Grid Projects: Step-by-Step Guide to Building Your Own Off-Grid SystemAinda não há avaliações

- Digital Gold: The Beginner's Guide to Digital Product Success, Learn Useful Tips and Methods on How to Create Digital Products and Earn Massive ProfitsNo EverandDigital Gold: The Beginner's Guide to Digital Product Success, Learn Useful Tips and Methods on How to Create Digital Products and Earn Massive ProfitsNota: 5 de 5 estrelas5/5 (3)

- The Rare Metals War: the dark side of clean energy and digital technologiesNo EverandThe Rare Metals War: the dark side of clean energy and digital technologiesNota: 5 de 5 estrelas5/5 (2)

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionNo EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionNota: 4 de 5 estrelas4/5 (331)

- C++ Programming Language: Simple, Short, and Straightforward Way of Learning C++ ProgrammingNo EverandC++ Programming Language: Simple, Short, and Straightforward Way of Learning C++ ProgrammingNota: 4 de 5 estrelas4/5 (1)

- The Fast Track to Your Technician Class Ham Radio License: For Exams July 1, 2022 - June 30, 2026No EverandThe Fast Track to Your Technician Class Ham Radio License: For Exams July 1, 2022 - June 30, 2026Nota: 5 de 5 estrelas5/5 (1)

- Lithium-Ion Battery: The Power of Electric Vehicles with Basics, Design, Charging technology & Battery Management SystemsNo EverandLithium-Ion Battery: The Power of Electric Vehicles with Basics, Design, Charging technology & Battery Management SystemsNota: 5 de 5 estrelas5/5 (2)

- Operational Amplifier Circuits: Analysis and DesignNo EverandOperational Amplifier Circuits: Analysis and DesignNota: 4.5 de 5 estrelas4.5/5 (2)

- Winning in 2025: Digital and Data Transformation: The Keys to SuccessNo EverandWinning in 2025: Digital and Data Transformation: The Keys to SuccessAinda não há avaliações

- Wearable Sensors: Fundamentals, Implementation and ApplicationsNo EverandWearable Sensors: Fundamentals, Implementation and ApplicationsEdward SazonovAinda não há avaliações

- Power Density: A Key to Understanding Energy Sources and UsesNo EverandPower Density: A Key to Understanding Energy Sources and UsesNota: 4.5 de 5 estrelas4.5/5 (2)