Escolar Documentos

Profissional Documentos

Cultura Documentos

Low-Power, High-Throughput, and Low-Area Adaptive Fir Filter Based On Distributed Arithmetic

Enviado por

TechnosIndiaTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Low-Power, High-Throughput, and Low-Area Adaptive Fir Filter Based On Distributed Arithmetic

Enviado por

TechnosIndiaDireitos autorais:

Formatos disponíveis

LOW-POWER, HIGH-THROUGHPUT, AND LOW-AREA

ADAPTIVE FIR FILTER BASED ON DISTRIBUTED

ARITHMETIC

ABSTRACT:

This brief presents a novel pipelined architecture for low-power, high throughput, and

low-area implementation of adaptive filter based on distributed arithmetic (DA). The throughput

rate of the proposed design is significantly increased by parallel lookup table (LUT) update and

concurrent implementation of filtering and weight-update operations. The conventional adderbased shift accumulation for DA-based inner-product computation is replaced by conditional

signed carry-save accumulation in order to reduce the area complexity and reduce power

consumption. It involves the same number of multiplexors, smaller LUT, and nearly half the

number of adders compared to the existing DA-based design.

EXISTING SYSTEM:

For discrete finite impulse response (FIR) Filters, the output y (n) is a linear

convolution of weights w (n), and inputs. For an N-order FIR Filters, the generation of each

output sample y (n) takes N + 1 multiply-accumulate (MAC) operations. Since general purpose

multipliers require significant chip area, alternate methods of implementing multiplication are

often used particularly when the coefficient values are known prior to implementation. A DAbased FIR adaptive lter implementation scheme is presented, which uses extra auxiliary

LUTs to help in the updating; however, memory usage is doubled.

EXISTING SYSTEM TECHNIQUE:

Multiply and accumulate (MAC) units

EXISTING SYSTEM DRAWBACKS:

Low-Throughput

Occupied area high

Increase the system complexity

PROPOSED SYSTEM:

The computation of adaptive filters of large orders needs to be decomposed into small

adaptive filtering blocks since DA based implementation of inner product of long vectors

requires a very large LUT.

PROPOSED SYSTEM BLOCK DIAGRAM:

Proposed structure of DA-based LMS adaptive filter of length N = 16 and P = 4:

PROPOSED SYSTEM ALGORITHM:

LMS Adaptive Algorithms

PROPOSED SYSTEM ADVANTAGES:

Low-Area

High-Throughput

Low-Power

SOFTWARE REQUIREMENT:

ModelSim6.4c

Xilinx 9.1/13.2

HARDWARE REQUIREMENT:

FPGA Spartan 3/ Spartan 3AN

REAL TIME APPLICATION:

Digital communication & Signal processing applications

Digital radio receivers

Down converts

Software Radio

FUTURE ENHANCEMENT:

We will modify the proposed system by reducing the Area of Structure of the four-point

inner-product block.

ALTERNATE TITLES:

Title 1: Adaptive Fir Filter Based On Distributed Arithmetic

Title 2: Distributed Arithmetic Adaptive Fir Filter Implementation Based On FPGA

Title 3: Adaptive Fir Filter Implementation Using Verilog HDL

PROJECT FLOW:

First Phase:

60% of Base Paper (3 Modules only Simulation)

Second Phase:

Remaining 40% of Base Paper with the Future Enhancement (Modification).

Você também pode gostar

- Sound Handbook by DlsDocumento23 páginasSound Handbook by Dlsbocu13100% (1)

- Home Power Magazine - Wind Power BasicsDocumento9 páginasHome Power Magazine - Wind Power BasicsradurusAinda não há avaliações

- Diagnostic Trouble CodesDocumento42 páginasDiagnostic Trouble CodesVictor Nunez100% (2)

- Positive IsolationDocumento10 páginasPositive IsolationArunava Basak0% (1)

- Cat Digital Voltage Regulator Manual: Read/DownloadDocumento2 páginasCat Digital Voltage Regulator Manual: Read/DownloadBrian Jr Ruiz Alegre0% (1)

- Fir ApcDocumento14 páginasFir Apcns saravananAinda não há avaliações

- A Noval Approach of FFTDocumento3 páginasA Noval Approach of FFTSijo MathewAinda não há avaliações

- International Journal of Engineering Research and Development (IJERD)Documento8 páginasInternational Journal of Engineering Research and Development (IJERD)IJERDAinda não há avaliações

- FPGA Implementation of High Speed FIR Filters Using Add and Shift MethodDocumento6 páginasFPGA Implementation of High Speed FIR Filters Using Add and Shift Methodpramani90Ainda não há avaliações

- LMS Algorithm and Distributed Arithmetic Based Adaptive FIR Filter With Low Area ComplexityDocumento5 páginasLMS Algorithm and Distributed Arithmetic Based Adaptive FIR Filter With Low Area ComplexityKriti JainAinda não há avaliações

- High Order Programmable and Tunable Analog Filter ICDocumento16 páginasHigh Order Programmable and Tunable Analog Filter ICRahil JainAinda não há avaliações

- An Efficient Adaptive Fir Filter Based On Distributed ArithmeticDocumento6 páginasAn Efficient Adaptive Fir Filter Based On Distributed ArithmeticinventionjournalsAinda não há avaliações

- Implementation of Reconfigurable Adaptive Filtering AlgorithmsDocumento5 páginasImplementation of Reconfigurable Adaptive Filtering AlgorithmsChaitanyaAinda não há avaliações

- Applying RNS to Reduce Power in DSP ArchitecturesDocumento5 páginasApplying RNS to Reduce Power in DSP ArchitecturesAishwarya a nairAinda não há avaliações

- Desigine and Implimentation of Application Specific Low Power MultipliersDocumento7 páginasDesigine and Implimentation of Application Specific Low Power MultipliersSaiKishoreAinda não há avaliações

- A12Documento6 páginasA12Usha MaddipatiAinda não há avaliações

- High Speed and Area Efficient Fpga Implementation of Fir Filter Using Distributed ArithmeticDocumento7 páginasHigh Speed and Area Efficient Fpga Implementation of Fir Filter Using Distributed ArithmeticZulfiqar AliAinda não há avaliações

- Fpga Based High-Speed A-Oms Lut & Fir System Design: Research ArticleDocumento4 páginasFpga Based High-Speed A-Oms Lut & Fir System Design: Research ArticleSowmya PAinda não há avaliações

- A Low Power Asynchronous VLSI FIR FilterDocumento11 páginasA Low Power Asynchronous VLSI FIR FilterducvillaAinda não há avaliações

- 32-bit Unsigned Multiplier Evaluation Using CLA and CSLADocumento23 páginas32-bit Unsigned Multiplier Evaluation Using CLA and CSLASivasankar YalavarthyAinda não há avaliações

- Embedded Ultra Low-Power Digital Signal Processing: Electronics / ÉlectroniqueDocumento4 páginasEmbedded Ultra Low-Power Digital Signal Processing: Electronics / ÉlectroniquemeasbolasAinda não há avaliações

- DRDDocumento16 páginasDRDAnushree SaranAinda não há avaliações

- VLSI Design of Half-Band IIR Interpolation and Decimation FilterDocumento7 páginasVLSI Design of Half-Band IIR Interpolation and Decimation FiltertansnvarmaAinda não há avaliações

- Edited ProjectDocumento48 páginasEdited ProjectsurendranathAinda não há avaliações

- FPGA-Based Digital Front-End Transmitter Design for OFDM Wireless LAN SystemsDocumento4 páginasFPGA-Based Digital Front-End Transmitter Design for OFDM Wireless LAN SystemsMd.Maruf Ahamed BeddutAinda não há avaliações

- Application-Specific Low-Power MultipliersDocumento6 páginasApplication-Specific Low-Power MultipliersSaiKishoreAinda não há avaliações

- Dual-Band Bandpass Filter Design Using A Novel Feed SchemeDocumento4 páginasDual-Band Bandpass Filter Design Using A Novel Feed Schemevijay bAinda não há avaliações

- New low-complexity reconfigurable architectures for FIR filtersDocumento14 páginasNew low-complexity reconfigurable architectures for FIR filtersSyfunnisa ShaikAinda não há avaliações

- Equalized GMSK, Equalized QPSK and OFDM, A Comparative Study For High-Speed Wireless Indoor Data CommunicationsDocumento5 páginasEqualized GMSK, Equalized QPSK and OFDM, A Comparative Study For High-Speed Wireless Indoor Data CommunicationsAhmed MidoAinda não há avaliações

- J 39 Mat Lab Program Crossover DesignDocumento15 páginasJ 39 Mat Lab Program Crossover DesignismailAinda não há avaliações

- A Novel Modulo Adder For 2n-2k-1 Residue Number SystemDocumento5 páginasA Novel Modulo Adder For 2n-2k-1 Residue Number SystemTechnosIndiaAinda não há avaliações

- Performance Analysis of Reconfigurable Multiplier Unit For FIR Filter DesignDocumento8 páginasPerformance Analysis of Reconfigurable Multiplier Unit For FIR Filter DesignInternational Journal of Innovative Science and Research TechnologyAinda não há avaliações

- ASIP Architecture Implementation of Channel Equalization Algorithms For MIMO Systems in WCDMA DownlinkDocumento5 páginasASIP Architecture Implementation of Channel Equalization Algorithms For MIMO Systems in WCDMA DownlinkMunish JassiAinda não há avaliações

- A Power Efficient Multiplier Architecture For Fir Filters Used For Acoustic Models in Mechanical DiagnosticsDocumento8 páginasA Power Efficient Multiplier Architecture For Fir Filters Used For Acoustic Models in Mechanical DiagnosticsTJPRC PublicationsAinda não há avaliações

- v1 Covered PDFDocumento26 páginasv1 Covered PDFSooraj SattirajuAinda não há avaliações

- A High-Speed/Low-Power Multiplier Using An Advanced Spurious Power Suppression TechniqueDocumento4 páginasA High-Speed/Low-Power Multiplier Using An Advanced Spurious Power Suppression TechniqueBappy DebnathAinda não há avaliações

- High-Performance 8-Bit Modulator Used For Sigma-Delta Analog To Digital ConverterDocumento7 páginasHigh-Performance 8-Bit Modulator Used For Sigma-Delta Analog To Digital ConverterAmeya DeshpandeAinda não há avaliações

- Modified Low Power Low Area Array Multiplier With SOC EncounterDocumento4 páginasModified Low Power Low Area Array Multiplier With SOC EncounterShamia SathishAinda não há avaliações

- 8.my RecentDocumento53 páginas8.my RecentRaoAinda não há avaliações

- VLSI Implementation of Modified Booth Algorithm: Rasika Nigam, Jagdish NagarDocumento4 páginasVLSI Implementation of Modified Booth Algorithm: Rasika Nigam, Jagdish NagarerpublicationAinda não há avaliações

- Multirate Technique of SRAMDocumento5 páginasMultirate Technique of SRAMSanthosh Chandu CAinda não há avaliações

- A Low-Power, Area-Efficient Digital Filter For Decimation and InterpolationDocumento9 páginasA Low-Power, Area-Efficient Digital Filter For Decimation and InterpolationtheTERAstarAinda não há avaliações

- A Review of Different Methods for Booth MultiplierDocumento4 páginasA Review of Different Methods for Booth Multiplierdivya_cestAinda não há avaliações

- Design of Multiplier Less 32 Tap FIR Filter Using VHDL: JournalDocumento5 páginasDesign of Multiplier Less 32 Tap FIR Filter Using VHDL: JournalIJMERAinda não há avaliações

- FIR FilterDocumento5 páginasFIR FilterManasa UpadhyayaAinda não há avaliações

- Tappered Buffers Literature ReviewDocumento5 páginasTappered Buffers Literature ReviewZulfiqar AliAinda não há avaliações

- EECT6306 Miidterm Project Harshit VamshiDocumento13 páginasEECT6306 Miidterm Project Harshit Vamshiafrica threeAinda não há avaliações

- Precision-Aware DWT Hardware ArchitecturesDocumento2 páginasPrecision-Aware DWT Hardware ArchitecturesVij AyAinda não há avaliações

- An Advanced and Area Optimized L.U.T Design Using A.P.C. and O.M.SDocumento5 páginasAn Advanced and Area Optimized L.U.T Design Using A.P.C. and O.M.Ssreelakshmi.ece eceAinda não há avaliações

- Ultra-Wideband Technology For Short-Range, High-Rate Wireless CommunicationsDocumento42 páginasUltra-Wideband Technology For Short-Range, High-Rate Wireless Communicationskartheedhanya008Ainda não há avaliações

- International Journal of Computational Engineering Research (IJCER)Documento11 páginasInternational Journal of Computational Engineering Research (IJCER)International Journal of computational Engineering research (IJCER)Ainda não há avaliações

- Designing Pipeline FFT Processor For Ofdm DemodulationDocumento6 páginasDesigning Pipeline FFT Processor For Ofdm Demodulationhy zhaoAinda não há avaliações

- Efficient Design of FIR Filter Using Modified Booth MultiplierDocumento5 páginasEfficient Design of FIR Filter Using Modified Booth MultiplierijsretAinda não há avaliações

- FIR Filter Design On Chip Using VHDL: IPASJ International Journal of Computer Science (IIJCS)Documento5 páginasFIR Filter Design On Chip Using VHDL: IPASJ International Journal of Computer Science (IIJCS)International Journal of Application or Innovation in Engineering & ManagementAinda não há avaliações

- Wind Band Radar Signal Using RF2051Documento8 páginasWind Band Radar Signal Using RF2051Khushal KharadeAinda não há avaliações

- Efficient Design Using Fpgas: of Application Specific CoresDocumento5 páginasEfficient Design Using Fpgas: of Application Specific CoresK.GurucharanAinda não há avaliações

- Smart Card:: Smart Cards-What Are They?Documento12 páginasSmart Card:: Smart Cards-What Are They?infernobibekAinda não há avaliações

- Survey On DLMS Adaptive Filter With Low DelayDocumento5 páginasSurvey On DLMS Adaptive Filter With Low DelayshastryAinda não há avaliações

- International Journal of Engineering Research and Development (IJERD)Documento4 páginasInternational Journal of Engineering Research and Development (IJERD)IJERDAinda não há avaliações

- Low-Power Viterbi Decoder Design For TCM DecodersDocumento5 páginasLow-Power Viterbi Decoder Design For TCM DecodersPooja BanAinda não há avaliações

- Low-power DA architectures for FIR filtersDocumento5 páginasLow-power DA architectures for FIR filtersAbhijeet VatsAinda não há avaliações

- 2.1 Survey On Parallel Fir FiltersDocumento19 páginas2.1 Survey On Parallel Fir FilterskishorechiyaAinda não há avaliações

- Embedded Radar SignalprocessingDocumento3 páginasEmbedded Radar SignalprocessingManikantaReddyAinda não há avaliações

- High-Performance D/A-Converters: Application to Digital TransceiversNo EverandHigh-Performance D/A-Converters: Application to Digital TransceiversAinda não há avaliações

- Parallel Aes Encryption Engines For Many-Core Processor ArraysDocumento5 páginasParallel Aes Encryption Engines For Many-Core Processor ArraysTechnosIndiaAinda não há avaliações

- Multifunction Residue ArchitecturesDocumento4 páginasMultifunction Residue ArchitecturesTechnosIndiaAinda não há avaliações

- Measurement and Evaluation of Power AnalysisDocumento5 páginasMeasurement and Evaluation of Power AnalysisTechnosIndiaAinda não há avaliações

- High-Throughput Multi Standard Transform Core Supporting Mpegh.264vc-1 Using Common Sharing Distributed ArithmeticDocumento4 páginasHigh-Throughput Multi Standard Transform Core Supporting Mpegh.264vc-1 Using Common Sharing Distributed ArithmeticTechnosIndiaAinda não há avaliações

- Low-Complexity Multiplier For GF (2m) Based On All-One PolynomialsDocumento5 páginasLow-Complexity Multiplier For GF (2m) Based On All-One PolynomialsTechnosIndiaAinda não há avaliações

- Design of Efficient Binary ComparatorsDocumento4 páginasDesign of Efficient Binary ComparatorsTechnosIndiaAinda não há avaliações

- Low-Power and Area-Efficient Carry Select AdderDocumento5 páginasLow-Power and Area-Efficient Carry Select AdderTechnosIndiaAinda não há avaliações

- Multicarrier Systems Based On MultistageDocumento4 páginasMulticarrier Systems Based On MultistageTechnosIndiaAinda não há avaliações

- Flexible Integer DCT Architectures For HevcDocumento5 páginasFlexible Integer DCT Architectures For HevcTechnosIndiaAinda não há avaliações

- Low-Complexity Low-Latency Architecture For Matching of Data Encodedwith Hard SystematicDocumento5 páginasLow-Complexity Low-Latency Architecture For Matching of Data Encodedwith Hard SystematicTechnosIndiaAinda não há avaliações

- Improvement of The Security of Zigbee by A New Chaotic AlgorithmDocumento5 páginasImprovement of The Security of Zigbee by A New Chaotic AlgorithmTechnosIndiaAinda não há avaliações

- Efficient Integer DCT Architectures For HevcDocumento4 páginasEfficient Integer DCT Architectures For HevcTechnosIndiaAinda não há avaliações

- Improved 8-Point Approximate DCT For Image and Video Compression Requiring Only 14 AdditionsDocumento6 páginasImproved 8-Point Approximate DCT For Image and Video Compression Requiring Only 14 AdditionsTechnosIndiaAinda não há avaliações

- Eliminating Synchronization Latency UsingDocumento5 páginasEliminating Synchronization Latency UsingTechnosIndiaAinda não há avaliações

- Fast Sign Detection Algorithm For The Rns ModuliDocumento4 páginasFast Sign Detection Algorithm For The Rns ModuliTechnosIndiaAinda não há avaliações

- Gate Mapping Automation For AsynchronousDocumento4 páginasGate Mapping Automation For AsynchronousTechnosIndiaAinda não há avaliações

- Design of Digit-Serial Fir Filters Algorithms, Architectures and A Cad ToolDocumento4 páginasDesign of Digit-Serial Fir Filters Algorithms, Architectures and A Cad ToolTechnosIndiaAinda não há avaliações

- Design of Testable Reversible Sequential CircuitsDocumento6 páginasDesign of Testable Reversible Sequential CircuitsTechnosIndiaAinda não há avaliações

- Efficient Fpga and Asic Realizations ofDocumento4 páginasEfficient Fpga and Asic Realizations ofTechnosIndia100% (1)

- Critical-Path Analysis and Low-ComplexityDocumento5 páginasCritical-Path Analysis and Low-ComplexityTechnosIndiaAinda não há avaliações

- Cordic Based Fast Radix-2 DCT AlgorithmDocumento5 páginasCordic Based Fast Radix-2 DCT AlgorithmTechnosIndiaAinda não há avaliações

- Area Delay Power Efficient Carry Select AdderDocumento5 páginasArea Delay Power Efficient Carry Select AdderTechnosIndiaAinda não há avaliações

- Area-Delay Efficient Binary Adders in QcaDocumento5 páginasArea-Delay Efficient Binary Adders in QcaTechnosIndiaAinda não há avaliações

- Area Delay Power Efficient Fixed Point LmsDocumento4 páginasArea Delay Power Efficient Fixed Point LmsTechnosIndiaAinda não há avaliações

- Aging-Aware Reliable Multiplier Design With Adaptive Hold LogicDocumento4 páginasAging-Aware Reliable Multiplier Design With Adaptive Hold LogicTechnosIndia0% (1)

- Split Radix Algorithm For Length 6m DFTDocumento5 páginasSplit Radix Algorithm For Length 6m DFTTechnosIndiaAinda não há avaliações

- Design of An Error Detection and Data Recovery Architecture For Motion Estimation Testing ApplicationsDocumento4 páginasDesign of An Error Detection and Data Recovery Architecture For Motion Estimation Testing ApplicationsTechnosIndiaAinda não há avaliações

- Area-Efficient Parallel Fir Digital Filter Structures For Symmetric Convolutions Based On Fast Fir AlgorithmDocumento4 páginasArea-Efficient Parallel Fir Digital Filter Structures For Symmetric Convolutions Based On Fast Fir AlgorithmTechnosIndiaAinda não há avaliações

- Period Extension and Randomness Enhancement Using High-Throughput Reseeding-Mixing PRNGDocumento4 páginasPeriod Extension and Randomness Enhancement Using High-Throughput Reseeding-Mixing PRNGTechnosIndiaAinda não há avaliações

- Tsgenco-Exam Syllabus PDFDocumento9 páginasTsgenco-Exam Syllabus PDForaclerca1Ainda não há avaliações

- Module 6 - Current Divider RuleDocumento10 páginasModule 6 - Current Divider RuleNoel Jr. CornelioAinda não há avaliações

- Defectos y Soluciones de MonitoresDocumento355 páginasDefectos y Soluciones de MonitoresJuan Carlos ContrerasAinda não há avaliações

- Smart Test Series: 1-Circle The Correct One. (15x1 15)Documento3 páginasSmart Test Series: 1-Circle The Correct One. (15x1 15)Zaheer AhmedAinda não há avaliações

- Star Rating List For Distribution TransformerDocumento71 páginasStar Rating List For Distribution TransformerSagar SinghAinda não há avaliações

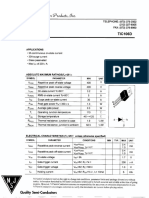

- TIC106DDocumento1 páginaTIC106DMauricio BurgosAinda não há avaliações

- What Are The Main Effects of Electric Current and Its ApplicationsDocumento2 páginasWhat Are The Main Effects of Electric Current and Its ApplicationsMrinal K Roy75% (4)

- Configuration of CNC System: 1. Central Processing Unit (CPU)Documento4 páginasConfiguration of CNC System: 1. Central Processing Unit (CPU)tavish sharmaAinda não há avaliações

- Double-impeller electric pumps technical data sheetDocumento9 páginasDouble-impeller electric pumps technical data sheetNahuel AlthausAinda não há avaliações

- Cisco Catalyst 6500 Series Switch DatasheetDocumento12 páginasCisco Catalyst 6500 Series Switch DatasheetJoannaAinda não há avaliações

- Hcia Lte GeralDocumento48 páginasHcia Lte Geralvictor kudidissaAinda não há avaliações

- PLL 2164Documento24 páginasPLL 2164Benjamín Varela UmbralAinda não há avaliações

- Fuses Del PicDocumento7 páginasFuses Del PicCarlos RodríguezAinda não há avaliações

- Induction Motor DrivesDocumento1 páginaInduction Motor DrivesvagoliyoAinda não há avaliações

- It Information Technology Department - B.E., ANNA UNIVERSITY Important Question and Answers - Regulation 2013,2017 - STUDY MATERIAL, NotesDocumento5 páginasIt Information Technology Department - B.E., ANNA UNIVERSITY Important Question and Answers - Regulation 2013,2017 - STUDY MATERIAL, NotesKali ThaashAinda não há avaliações

- ARINC 429 to Synchro Converter Model 44SM7Documento3 páginasARINC 429 to Synchro Converter Model 44SM7ekinox_es100% (1)

- SF-2001-SureFire II High Energy Igniter (English) 2020-12-17Documento24 páginasSF-2001-SureFire II High Energy Igniter (English) 2020-12-17akash kurheAinda não há avaliações

- Bulb AssignmentDocumento2 páginasBulb AssignmentJamie McGregorAinda não há avaliações

- Philips LED 12836redb1 21 Watts 5 Watts 21w/5w Dois PolosDocumento2 páginasPhilips LED 12836redb1 21 Watts 5 Watts 21w/5w Dois PolosExclusivo1Ainda não há avaliações

- AVA 33 Voltage Operated Auxiliary Relay (3 Elements) With HR ContactsDocumento1 páginaAVA 33 Voltage Operated Auxiliary Relay (3 Elements) With HR ContactsKunjan DalwadiAinda não há avaliações

- M.tech CPLD & Fpga Architecture & ApplicationsDocumento2 páginasM.tech CPLD & Fpga Architecture & Applicationssrinivas100% (1)

- PD Smart PDFDocumento2 páginasPD Smart PDFAriel Leandro Toro MuñozAinda não há avaliações

- LED Thin PAR64 User ManualDocumento10 páginasLED Thin PAR64 User ManualAndy P ParsonsAinda não há avaliações

- BSc Engineering Degree UEE403 AnswersDocumento16 páginasBSc Engineering Degree UEE403 AnswersNipuna Lakmal WeerakkodyAinda não há avaliações

- Answer Section B and C and Paper 3Documento21 páginasAnswer Section B and C and Paper 3Adnan ShamsudinAinda não há avaliações