Escolar Documentos

Profissional Documentos

Cultura Documentos

Vlsi Internal Question Paper Mtech.

Enviado por

Vinay ReddyDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Vlsi Internal Question Paper Mtech.

Enviado por

Vinay ReddyDireitos autorais:

Formatos disponíveis

GEETHANJALI COLLEGE OF ENGINEERING AND TECHNOLOGY

CHEERYAL, KEESARA.

MTECH 1ST YEAR 1ST SEM I MID EXAMINATIONS

DEPARTMENT OF ECE

(Common to VLSI ,ES,ECE)

FACULTY : P. Sneha Naga Shilpa

Subject: VLSI Technology & Design

DURATION : 2HRS

SET-1

PART- A

Answer all the questions. Each question carry 4 marks.

1.

2.

3.

4.

Compare CMOS and Bi-polar Transistors.

Draw the schematic & layout for an CMOS NAND gate.

Derive the expressions for Input transconductance Gm.

What is Fan- out?

PART- B

Answer any THREE questions. Each question carry 8 marks.

1. Determine the Pull-up to pull-down ratio for an NMOS inverters driven through one or more

pass transistors.

2. Explain in detail about BiCMOS Inverters?

3. Write in detail about Pseudo- nmos logic.

4. Explain the Delay through resistive Interconnect.

5. Explain about Standard Cell Layout Design.

GEETHANJALI COLLEGE OF ENGINEERING AND TECHNOLOGY

CHEERYAL, KEESARA.

MTECH 1ST YEAR 1ST SEM I MID EXAMINATIONS

DEPARTMENT OF ECE

(Common to VLSI ,ES,ECE)

FACULTY : P. Sneha Naga Shilpa

Subject: VLSI Technology & Design

DURATION : 2HRS

SET-2

PART- A

Answer all the questions. Each question carry 4 marks.

1.

2.

3.

4.

What is Body effect? How we can overcome it?

Draw the schematic & layout for an CMOS NOR gate.

Write short notes on Enhancement mode Nmos transistor.

Write short notes on Path delay.

PART- B

Answer any THREE questions. Each question carry 8 marks.

1. Determine the Pull-up to pull-down ratio for an NMOS inverter driven by another NMOS

inverter.

2. Explain in detail about the fabrication process of NMOS transistor.

3. Write in detail about Domino logic.

4. Draw a Layout for a CMOS Inverter and explain its transfer characteristics.

5. Explain in detail about Transistor sizing.

GEETHANJALI COLLEGE OF ENGINEERING AND TECHNOLOGY

CHEERYAL, KEESARA.

MTECH 1ST YEAR 1ST SEM I MID EXAMINATIONS

DEPARTMENT OF ECE

(Common to VLSI ,ES,ECE)

FACULTY : P. Sneha Naga Shilpa

Subject: VLSI Technology & Design

DURATION : 2HRS

SET-3

PART- A

Answer all the questions. Each question carry 4 marks.

1.

2.

3.

4.

Write short notes on Enhancement mode nmos transistor.

Draw a transistor schematic for following expressions *a(b+c)+.

Write a short notes on Switch logic.

Write short notes about Fan-in.

PART- B

Answer any THREE questions. Each question carry 8 marks.

1.

2.

3.

4.

5.

What is latch-up condition in CMOS circuits? How it can be eliminated?

Explain in detail about the fabrication process of CMOS transistor.

Write in detail about Pseudo- nmos logic & DCVS logic.

Explain in detail about the delay through RC transmission line.

Explain about device modeling.

GEETHANJALI COLLEGE OF ENGINEERING AND TECHNOLOGY

CHEERYAL, KEESARA.

MTECH 1ST YEAR 1ST SEM I MID EXAMINATIONS

DEPARTMENT OF ECE

(Common to VLSI ,ES,ECE)

FACULTY : P. Sneha Naga Shilpa

Subject: VLSI Technology & Design

DURATION : 2HRS

SET-4

PART- A

Answer all the questions. Each question carry 4 marks.

1.

2.

3.

4.

Differentiate between CMOS inverter and BiCMOS inverter.

Write a short notes on DCVS logic. What are the limitations of scaling?

Differentiate Pseudo-nmos , Domino & DCVS logic.

Write short notes on critical path.

PART- B

Answer any THREE questions. Each question carry 8 marks.

1.

2.

3.

4.

5.

Derive the relationship between Ids & Vds for an nmos transistor.

Explain in detail about the fabrication process of p-well.

Explain in detail about the delay through RLC transmission line.

Explain the Scalable design rules.

Explain how to minimize the crosstalk in VLSI.

Você também pode gostar

- Vlsi Question PapersDocumento1 páginaVlsi Question PapersjahnaviAinda não há avaliações

- JNTU M.Tech Question Papers, VLSI Technology DesignDocumento3 páginasJNTU M.Tech Question Papers, VLSI Technology DesignVijay SagarAinda não há avaliações

- MOSFET Fabrication and IC Design MethodologiesDocumento6 páginasMOSFET Fabrication and IC Design MethodologiessenyadnoireAinda não há avaliações

- Question Papers of Two Year M. Tech I Semester Regular Examinations April - 2012Documento29 páginasQuestion Papers of Two Year M. Tech I Semester Regular Examinations April - 2012mdphilipAinda não há avaliações

- VLSI DESIGN Question Bank: Unit 1Documento12 páginasVLSI DESIGN Question Bank: Unit 1Babu GundlapallyAinda não há avaliações

- VLSI Design ECE A InternalexamDocumento2 páginasVLSI Design ECE A InternalexamJeslin AntonioAinda não há avaliações

- I TEST CmosDocumento1 páginaI TEST CmosBhavya McAinda não há avaliações

- SRG Engineering College, Namakkal Unit Test-I Department of Eee Communication EngineeringDocumento2 páginasSRG Engineering College, Namakkal Unit Test-I Department of Eee Communication Engineeringkrr_apmAinda não há avaliações

- r05410207 Vlsi DesignDocumento7 páginasr05410207 Vlsi Design9010469071Ainda não há avaliações

- Intelligent Manufacturing SystemsDocumento5 páginasIntelligent Manufacturing SystemsVenkata RamuduAinda não há avaliações

- Nanhi Pari Seemant Institute of Technology Pithoragarh Class Test-I Ece - Vi VLSI Circuit Design (TEC-603)Documento2 páginasNanhi Pari Seemant Institute of Technology Pithoragarh Class Test-I Ece - Vi VLSI Circuit Design (TEC-603)Vikash SharmaAinda não há avaliações

- Jntu Vlsi Systems DesignDocumento5 páginasJntu Vlsi Systems Design9010469071Ainda não há avaliações

- ES PaperDocumento22 páginasES PaperRaghu Nath SinghAinda não há avaliações

- EMI/EMC exam questionsDocumento4 páginasEMI/EMC exam questionsKoushik DuttaAinda não há avaliações

- Question Bank Fundamentals of CMOS VLSI-10EC56 15-16Documento10 páginasQuestion Bank Fundamentals of CMOS VLSI-10EC56 15-16Pranav KpAinda não há avaliações

- Advanced Power System ProtectionDocumento1 páginaAdvanced Power System ProtectionKranthi KumarAinda não há avaliações

- 453 SyllabusDocumento4 páginas453 SyllabusPJBAinda não há avaliações

- BTech Telemetry Systems Sessional TestDocumento2 páginasBTech Telemetry Systems Sessional TestAagam JainAinda não há avaliações

- Previous Question PapersDocumento4 páginasPrevious Question Papersshaker423Ainda não há avaliações

- VLSIDesignDocumento5 páginasVLSIDesignVenkatesh KolatiAinda não há avaliações

- Digital CommunicationDocumento4 páginasDigital CommunicationJaya Rajesh RaajAinda não há avaliações

- Code No: R05320402Documento4 páginasCode No: R05320402chvsrsettiAinda não há avaliações

- Answer Any FIVE Questions. All Questions Carry EQUAL MarksDocumento1 páginaAnswer Any FIVE Questions. All Questions Carry EQUAL MarksUday KumarAinda não há avaliações

- Q Paper 09ec61 May June 2012Documento2 páginasQ Paper 09ec61 May June 2012Bhaskar MishraAinda não há avaliações

- Telecommunication 3Documento2 páginasTelecommunication 3Anil RaiAinda não há avaliações

- Previous PapersDocumento12 páginasPrevious PapersKaran SanaAinda não há avaliações

- Anna University VLSI Design Question PaperDocumento3 páginasAnna University VLSI Design Question PapersrgperumalAinda não há avaliações

- M. Tech II Semester Q.P Oct 2015 Day 1Documento5 páginasM. Tech II Semester Q.P Oct 2015 Day 1Prabhath DarlingAinda não há avaliações

- 1st Sem April 2015-2Documento6 páginas1st Sem April 2015-2తెలుగువెలుగుAinda não há avaliações

- B.tech MDU Syllabus (ECE) 3yrDocumento22 páginasB.tech MDU Syllabus (ECE) 3yrbtechkarloAinda não há avaliações

- Modern Control Theory Exam Questions NR/R09Documento3 páginasModern Control Theory Exam Questions NR/R09IbmWasuserAinda não há avaliações

- Ece-V-fundamentals of Cmos Vlsi (10ec56) - NotesDocumento214 páginasEce-V-fundamentals of Cmos Vlsi (10ec56) - NotesNithindev Guttikonda0% (1)

- EC NotesDocumento2 páginasEC Noteshanumantha12Ainda não há avaliações

- Internal Assessment 1: Department of Electronics & Communication EnggDocumento1 páginaInternal Assessment 1: Department of Electronics & Communication EnggNikhil KulkarniAinda não há avaliações

- Set No. 1: M Ds GS TN 2 DSDocumento6 páginasSet No. 1: M Ds GS TN 2 DSSRINIVASA RAO GANTAAinda não há avaliações

- King College of Technology, Namakkal: Unit Test - 3Documento2 páginasKing College of Technology, Namakkal: Unit Test - 3Sri VasanAinda não há avaliações

- Vaigai College of Engineering: Therkutheru, Melur (TK), Madurai - 625122Documento4 páginasVaigai College of Engineering: Therkutheru, Melur (TK), Madurai - 625122Rajesh LingamAinda não há avaliações

- Gautam Buddha University Microelectronics ExamDocumento2 páginasGautam Buddha University Microelectronics ExamSachin PalAinda não há avaliações

- Main Paper EC-306Documento2 páginasMain Paper EC-306Sachin PalAinda não há avaliações

- Main Paper EC-306Documento2 páginasMain Paper EC-306Sachin PalAinda não há avaliações

- Main Paper EC-306Documento2 páginasMain Paper EC-306Sachin PalAinda não há avaliações

- Cs 1251 Computer Architecture Anna University Previous Year Question Bank DownloadDocumento1 páginaCs 1251 Computer Architecture Anna University Previous Year Question Bank DownloadlmsrtAinda não há avaliações

- GTU M.E. Semester II Digital VLSI Design ExamDocumento2 páginasGTU M.E. Semester II Digital VLSI Design ExamPritesh SaxenaAinda não há avaliações

- 1 Vlsi DesignDocumento4 páginas1 Vlsi Designapi-3704956Ainda não há avaliações

- 3 Vlsi Design (Elective III)Documento1 página3 Vlsi Design (Elective III)Rohith Sai RohiAinda não há avaliações

- Google 11Documento2 páginasGoogle 11Suraj TiwariAinda não há avaliações

- Nr-Vlsi Technology and DesignDocumento2 páginasNr-Vlsi Technology and DesignSudhakar SpartanAinda não há avaliações

- Factors Influencing Small Scale Fading and Operation of RAKE ReceiverDocumento3 páginasFactors Influencing Small Scale Fading and Operation of RAKE ReceiverDurga Prasad TumulaAinda não há avaliações

- Rr410505 Vlsi Systems DesignDocumento4 páginasRr410505 Vlsi Systems DesignSrinivasa Rao GAinda não há avaliações

- Jntuworld: Electrical and Electronics EngineeringDocumento30 páginasJntuworld: Electrical and Electronics EngineeringRajeev BujjiAinda não há avaliações

- B .Tech IV Year I Semester (R07) Supplementary Examinations June 2015Documento1 páginaB .Tech IV Year I Semester (R07) Supplementary Examinations June 2015subbuAinda não há avaliações

- Btech Ee 6 Sem Conventional and Cad of Electrical Machines Nee 023 2016 17Documento2 páginasBtech Ee 6 Sem Conventional and Cad of Electrical Machines Nee 023 2016 17Tanisha ShahAinda não há avaliações

- EC2354 - VLSI DesignDocumento2 páginasEC2354 - VLSI DesignSriramAinda não há avaliações

- Introduction to Bond Graphs and their ApplicationsNo EverandIntroduction to Bond Graphs and their ApplicationsNota: 5 de 5 estrelas5/5 (1)

- Mathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsNo EverandMathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsRoderick MelnikAinda não há avaliações

- MOS Integrated Circuit DesignNo EverandMOS Integrated Circuit DesignE. WolfendaleAinda não há avaliações

- Analog Electronics: Circuits, Systems and Signal ProcessingNo EverandAnalog Electronics: Circuits, Systems and Signal ProcessingAinda não há avaliações

- Solution Manual for 100 Genesys Design Examples: Second EditionNo EverandSolution Manual for 100 Genesys Design Examples: Second EditionAinda não há avaliações

- Jyothi 3Documento1 páginaJyothi 3Vinay ReddyAinda não há avaliações

- Postalassitants14 PaperDocumento14 páginasPostalassitants14 PaperVinay ReddyAinda não há avaliações

- Railway MCQ Capsule 4Documento14 páginasRailway MCQ Capsule 4Vinay ReddyAinda não há avaliações

- Time and Work (Maths by Devendra Sir) Vmentor Coaching CentreDocumento16 páginasTime and Work (Maths by Devendra Sir) Vmentor Coaching CentreVinay ReddyAinda não há avaliações

- PGECET SyllabusDocumento2 páginasPGECET SyllabusPurnima KAinda não há avaliações

- Voice Morphing Seminar ReportDocumento36 páginasVoice Morphing Seminar ReportVinay ReddyAinda não há avaliações

- Rafii-Pardo - REpeating Pattern Extraction Technique (REPET) A Simple Method For Music-Voice Separation - TALSP 2013Documento12 páginasRafii-Pardo - REpeating Pattern Extraction Technique (REPET) A Simple Method For Music-Voice Separation - TALSP 2013Vinay ReddyAinda não há avaliações

- Facial Recognition ReportDocumento60 páginasFacial Recognition ReportSamirKhadkaAinda não há avaliações

- Face Recognition TechnologyDocumento33 páginasFace Recognition Technologymshibas83% (6)

- Budget 2015 FinalDocumento2 páginasBudget 2015 FinalVinay ReddyAinda não há avaliações

- Voice MorphingDocumento36 páginasVoice MorphingNiki Patel100% (1)

- Agriculture Last Ranks 2013-14Documento2 páginasAgriculture Last Ranks 2013-14Vinay ReddyAinda não há avaliações

- 13 Ec 533Documento1 página13 Ec 533Vinay ReddyAinda não há avaliações

- Voice Morphing Seminar ReportDocumento36 páginasVoice Morphing Seminar ReportVinay ReddyAinda não há avaliações

- Finite State Machines NotesDocumento1 páginaFinite State Machines NotesVinay ReddyAinda não há avaliações

- (A) - Control System (Electronics) - Part1Documento22 páginas(A) - Control System (Electronics) - Part1Vinay ReddyAinda não há avaliações

- Introduction WCNDocumento30 páginasIntroduction WCNShaami AtmAinda não há avaliações

- Temperature Sensor Based Ceiling Fan Control SystemDocumento25 páginasTemperature Sensor Based Ceiling Fan Control SystemVinay ReddyAinda não há avaliações

- ECE2030 Introduction To Computer Engineering Lecture 13: Building Blocks For Combinational Logic (4) Shifters, MultipliersDocumento30 páginasECE2030 Introduction To Computer Engineering Lecture 13: Building Blocks For Combinational Logic (4) Shifters, MultipliersNguyễn Nam HảiAinda não há avaliações

- Design of an 8-Bit Barrel Shifter Circuit with 200MHz Clock Speed and 20mW PowerDocumento15 páginasDesign of an 8-Bit Barrel Shifter Circuit with 200MHz Clock Speed and 20mW PowerdivyeddAinda não há avaliações

- Group D241113Documento12 páginasGroup D241113Vinay ReddyAinda não há avaliações

- Lecture06b SlidesDocumento10 páginasLecture06b SlidesVinay ReddyAinda não há avaliações

- Barrel ShifterDocumento79 páginasBarrel ShifterVinay Reddy100% (2)

- DD Vahid ch4Documento89 páginasDD Vahid ch4Bobby HalAinda não há avaliações

- 16 BitDocumento15 páginas16 BitVinay ReddyAinda não há avaliações

- Barrel ShifterDocumento79 páginasBarrel ShifterVinay Reddy100% (2)

- DD Vahid ch4Documento89 páginasDD Vahid ch4Bobby HalAinda não há avaliações

- Vinay Acronyms FinalizedDocumento2 páginasVinay Acronyms FinalizedVinay ReddyAinda não há avaliações

- Abstract of Barrel ShifterDocumento1 páginaAbstract of Barrel ShifterVinay ReddyAinda não há avaliações

- Characteristics of ThyristorsDocumento7 páginasCharacteristics of ThyristorsSubaskaran SalavanAinda não há avaliações

- GT60M303Documento6 páginasGT60M303roozbehxoxAinda não há avaliações

- Ladder Logic ProblemsDocumento4 páginasLadder Logic ProblemsEngr. Naveed Mazhar0% (1)

- Arihant Switchgear Products - 8-8-2023Documento115 páginasArihant Switchgear Products - 8-8-2023Utsav PatelAinda não há avaliações

- Transistors & ICs Cross Ref PDFDocumento13 páginasTransistors & ICs Cross Ref PDFDeyPro50% (2)

- BJT Mosfet IgbtDocumento48 páginasBJT Mosfet IgbtJeanmark NeilAinda não há avaliações

- SMD General Purpose TransistorDocumento3 páginasSMD General Purpose TransistorMalay K GhoshAinda não há avaliações

- Bipolar Junction Transistors (BJT) : Department of Physics UAE University Dr. Naser QamhiehDocumento12 páginasBipolar Junction Transistors (BJT) : Department of Physics UAE University Dr. Naser QamhiehAyeshaAinda não há avaliações

- Digital Integrated Circuit Design: Subject Code:18EC2019Documento25 páginasDigital Integrated Circuit Design: Subject Code:18EC2019shiny johnAinda não há avaliações

- EEE 441 Lecture3 (Switching System)Documento60 páginasEEE 441 Lecture3 (Switching System)JAWWAD SADIQ AYON100% (2)

- 2007-Behavioural and Electrothermal Modelling of TheDocumento4 páginas2007-Behavioural and Electrothermal Modelling of TheruanAinda não há avaliações

- SMD CatalogDocumento80 páginasSMD Catalogpbradaric91% (11)

- Type2 - (IEC 60947-4-1)Documento21 páginasType2 - (IEC 60947-4-1)011253Ainda não há avaliações

- Lesson 11 ThyristorsDocumento12 páginasLesson 11 ThyristorsBlueprint MihAinda não há avaliações

- VLSIDocumento3 páginasVLSINuniwal JyotiAinda não há avaliações

- Despiece PSE-PSG-35-140-160-200 MPDocumento31 páginasDespiece PSE-PSG-35-140-160-200 MPDaniel GarnicaAinda não há avaliações

- Semiconductors DiscretesDocumento96 páginasSemiconductors Discretespacho2117100% (4)

- Microprocessor-based medium voltage switchgear components listDocumento10 páginasMicroprocessor-based medium voltage switchgear components listnidnitrkl051296Ainda não há avaliações

- 8KW Heater Control Panel GA DrawingDocumento9 páginas8KW Heater Control Panel GA DrawingBalamurugan ArumugamAinda não há avaliações

- Sss 4 N 60 ADocumento4 páginasSss 4 N 60 AFreddy Enrik SuberoAinda não há avaliações

- Junctionless TransistorsDocumento2 páginasJunctionless TransistorslutfiAinda não há avaliações

- Vlsi in PDFDocumento9 páginasVlsi in PDFnatureheaplerAinda não há avaliações

- Tutorial 2 : Bipolar Junction TransistorDocumento3 páginasTutorial 2 : Bipolar Junction TransistoralexAinda não há avaliações

- Examination of Power Electronics (Pel) : AnswerDocumento10 páginasExamination of Power Electronics (Pel) : Answerves vegasAinda não há avaliações

- Field-Effect Transistors: 6.13 Summary TableDocumento3 páginasField-Effect Transistors: 6.13 Summary TableHoàng NguyễnAinda não há avaliações

- One Mark Questions (Q.1 To Q.6) : Common InstructionsDocumento2 páginasOne Mark Questions (Q.1 To Q.6) : Common InstructionsKrishna Charan GudaAinda não há avaliações

- NPN vs PNP transistor switchingDocumento2 páginasNPN vs PNP transistor switchingbetildejack100% (1)

- Ingeniería y Abastecimiento catalog lists electrical componentsDocumento10 páginasIngeniería y Abastecimiento catalog lists electrical componentsTony NavaAinda não há avaliações

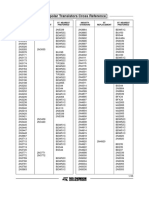

- Bipolar Transistors Cross Reference ChartDocumento35 páginasBipolar Transistors Cross Reference ChartEugenio NanniAinda não há avaliações

- Isc N-Channel MOSFET Transistor IRFP450A: INCHANGE Semiconductor Product SpecificationDocumento2 páginasIsc N-Channel MOSFET Transistor IRFP450A: INCHANGE Semiconductor Product Specificationnanang c-kakakAinda não há avaliações