Escolar Documentos

Profissional Documentos

Cultura Documentos

Dcmatch Appnote

Enviado por

Thomas GeorgeTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Dcmatch Appnote

Enviado por

Thomas GeorgeDireitos autorais:

Formatos disponíveis

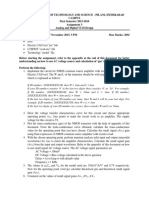

Affirma Spectre DC Device Matching Analysis Tutorial

Affirma Spectre DC Device Matching

Analysis Tutorial

The procedure described in this application note are deliberately broad and

generic. Requirements for your specific design may dictate procedures slightly

different from those described here.

Purpose

This application note describes how to

Use the dcmatch command in SPECTRE.

Examine the dcmatch results generated by SPECTRE.

Describe the models, equations, and theory of dcmatch analysis.

Audience

Circuit designers who want to find out dc variation and predict dc accuracy of

their designs.

Overview

The DCMATCH analysis performs DC device mismatch analysis for a given

output. It computes the deviation in the DC operating point of the circuit caused

by mismatch in the devices. Users need to specify mismatch parameters in their

Release Date

Back

Page 1

Close

Affirma Spectre DC Device Matching Analysis Tutorial

model cards for each device contributing to the deviation. The analysis uses the

device mismatch models to construct equivalent mismatch current sources in

parallel to all the devices that have mismatch modeled. These current sources

will have zero mean and some variance. The analysis computes the 3-sigma

variance of dc voltages or currents at user specified outputs due to the

mismatch current sources. The simulation results displays the devices rank

ordered by their contributions to the outputs. In addition, for mosfet devices

(limited to bsim3v3 now), it displays threshold voltage mismatch, current factor

mismatch, gate voltage mismatch, and drain current mismatch. For bipolar

devices (limited to vbic now), it displays base-emitter junction voltage mismatch.

For resistors (limited to two terminal resistance), it displays resistor mismatches.

The analysis replaces multiple simulation runs in the estimation of circuit

accuracies. It automatically identifies the set of critical matched components

during circuit design. For example, when there are matched pairs in the circuit,

the contribution of two matched transistors will be equal in magnitude and

opposite in sign.

Typical usage are to simulate the output offset voltage of operational amplifiers,

estimate the variation in bandgap voltages, and predict the accuracy of current

steering DACs.

Release Date

Back

Page 2

Close

Affirma Spectre DC Device Matching Analysis Tutorial

Help syntax

To obtain the command syntax on-line, users can type

spectre -h dcmatch

Release Date

Back

Page 3

Close

Affirma Spectre DC Device Matching Analysis Tutorial

Command syntax

The syntax of the dcmatch analysis is as follows:

Name [pnode nnode] dcmatch <parameter=value> ...

where the parameters are

1

mth

Relative mismatch contribution threshold value.

2

where=screen

Where DC-Mismatch analysis results should be printed. Possible values

are screen, logfile, file,or rawfile.

3

file

File name for results to be printed if where=file is used.

Probe parameters

4

oprobe

Compute mismatch at the output defined by this component.

Port parameters

5

portv

Release Date

Back

Page 4

Close

Affirma Spectre DC Device Matching Analysis Tutorial

Voltage across this probe port is output of the analysis. Instead of using

pnode and nnode to identify output, users can use oprobe and portv.

6

porti

Current through this probe port is output of the analysis.

Notice that porti allows users to select a current associated with a specific

device (component) given in oprobe as an output. This device, however,

has to have its terminal current(s) as network variable(s), i.e. the device

has to be an inductor, a switch, a tline, a controlled voltage source, an

iprobe, or other type of device which has branch currents as network

variables. Otherwise, Spectre will invalidate the request. Furthermore, for

inductor, vsource, switch, controlled voltage source and iprobe, porti can

only be set to one, since these devices are one port devices (two terminal);

and for tline porti can be set to one or two, since it is a two port device (four

terminals).

Sweep interval parameters

7

start=0

Start sweep limit.

8

stop

Stop sweep limit.

9

center

Center of sweep.

10

span=0

Sweep limit span.

Release Date

Back

Page 5

Close

Affirma Spectre DC Device Matching Analysis Tutorial

11

step

Step size, linear sweep.

12

lin=50

Number of steps, linear sweep.

13

dec

Points per decade.

14

log=50

Number of steps, log sweep.

15

values=[...]

Array of sweep values.

Sweep variable parameters

16

dev

Device instance whose parameter value is to be swept.

17

mod

Model whose parameter value is to be swept.

18

param

Name of parameter to sweep.

Release Date

Back

Page 6

Close

Affirma Spectre DC Device Matching Analysis Tutorial

State-file parameters

19

readns

File that contains estimate of DC solution (nodeset).

Output parameters

20

save

Signals to output. Possible values are all, lvl, allpub, lvlpub, selected, or

none.

21

nestlvl

Levels of subcircuits to output.

22

oppoint=no

Should operating point information be computed, and if so, where should it

be sent. Possible values are no, screen, logfile, or rawfile.

Convergence parameters

23

prevoppoint=no

Use operating point computed on the previous analysis. Possible values

are no or yes.

24

restart=yes

Do not use previous DC solution as initial guess. Possible values are no or

yes.

Release Date

Back

Page 7

Close

Affirma Spectre DC Device Matching Analysis Tutorial

Annotation parameters

25

annotate=sweep

Degree of annotation. Possible values are no, title, sweep, status, or steps.

26

stats=no

Analysis statistics. Possible values are no or yes.

27

title

Analysis title.

The dcmatch analysis will find a dc operating point first. If the dc analysis fails,

then the dcmatch analysis will fail also. The parameter mth is a threshold value

relative to the maximum contribution. Any device contribution less than (mth *

maximum) will not be reported. Where maximum is the maximum contribution

among all the devices of a given type.

Release Date

Back

Page 8

Close

Affirma Spectre DC Device Matching Analysis Tutorial

Example

dcmm1 dcmatch mth=1e-3 oprobe=vd porti=1

model n1 bsim3v3 type=n ...

+ mvtwl=6.15e-9 mvtwl2=2.5e-12 mvt0=0.0 mbewl=16.5e-9 mbe0=0.0

In the above example, a dcmatch analysis is to be performed to investigate the

3-sigma dc variation at the output of the current flowing through the device vd.

The porti=1 specifies that the current is flowing through the first port of vd (vd

has only one port obviously, thus porti=2 will be illegal). All device mismatch

contributions less than 1e-3 * maximum contribution among devices to the

output will not be reported. dcmm1 is the name of the analysis, which can be

used to identify output among analyses. The mismatch (i.e. the equivalent

mismatch current sources in parallel to all the devices that uses model n1) is

modeled by the model parameters mvtwl, mvtwl2, mvt0, mbewl, and mbe0. The

meaning of these parameters is described in the modeling section.

The output of the dcmatch analysis is displayed like this:

*********************************************

DC Device Matching Analysis mismatch1 at vd

*********************************************

Local Variation = 3-sigma random device variation

Release Date

Back

Page 9

Close

Affirma Spectre DC Device Matching Analysis Tutorial

sigmaOut

sigmaVth

sigmaBeta sigmaVg

sigmaIds

-13.8 uA

2.21 mV

357 m%

2.26 mV

1.71 %

mp6

-6.99 uA

1.63 mV

269 m%

1.68 mV

1.08 %

m01

-2.71 uA

1.11 mV

187 m%

1.16 mV

648 m%

-999 nA

769 uV

131 m%

807 uV

428 m%

m04x4_4

-999 nA

769 uV

131 m%

807 uV

428 m%

m04x4_3

-999 nA

769 uV

131 m%

807 uV

428 m%

m04x4_2

-999 nA

769 uV

131 m%

807 uV

428 m%

m04x4_1

-999 nA

769 uV

131 m%

807 uV

428 m%

m04

-718 nA

1.09 mV

185 m%

1.15 mV

599 m%

m40x04

-520 nA

1.55 mV

263 m%

1.63 mV

835 m%

m20x04

-378 nA

2.21 mV

376 m%

2.34 mV

1.16 %

-363 nA

539 uV

92 m%

567 uV

293 m%

m08

-131 nA

379 uV

64.9 m%

400 uV

203 m%

m16

-46.7 nA

267 uV

45.9 m%

283 uV

142 m%

m32

Release Date

Back

Page 10

m02

m10x04

Close

10

Affirma Spectre DC Device Matching Analysis Tutorial

vd =-3.477 mA +/- 15.91 uA (3-sigma variation)

It says that the 3-sigma variation at i(vdd) is -3.477mA +/- 15.91uA due to the

mismatch models. The -3.477mA is the dc operating value of the i(vdd),

whereas the 15.91uA is the 3-sigma variation due to the device mismatches.

The device mp6 contributes the most to the output at

-13.8 uA followed by m01 which contributes -6.99uA. The equivalent 3-sigma

Vth variation of mp6 is 2.21mV. The relative 3-sigma beta (current factor)

variation of mp6 is 0.357%. The equivalent 3-sigma gate voltage variation

is 2.26mV. The relative 3-sigma Ids variation of mp6 is 1.71%.

Release Date

Back

Page 11

Close

11

Affirma Spectre DC Device Matching Analysis Tutorial

More Examples

dcmm2 n1 n2 dcmatch mth=1e-3 where=rawfile stats=yes

In the above example, a dcmatch analysis is to be performed to investigate the

3-sigma dc variation on output v(n1,n2). The result of the analysis will be printed

in a psf file. The cpu statistics of the analysis will also be generated.

dcmm3 dcmatch mth=1e-3 oprobe=r3 portv=1

In the above example, the output is the voltage drop across the 1st port of r3.

Since r3 has only one port, portv=2 will be illegal.

dcmm4 n3 0 dcmatch mth=1e-3 where=file file="%C:r.info.what"

In the above example, the output of the analysis will be printed in a file of

.info.what prepended with circuit name.

sweep1 sweep dev=mp6 param=w start=80e-6 stop=90e-6 step=2e-6 {

dcmm5 n3 0 dcmatch mth=1e-3 where=rawfile

}

In the above example, a set of analyses will be performed on output v(n3,0) by

sweeping the device parameter w of the device mp6 from 80um to 90um at each

increment of 2um. The results will be printed as psf files. The psf files will be

named as sweep1-000_dcmm5.dcmatch to sweep1-005_dcmm5.dcmatch.

dcmm6 n3 0 dcmatch mth=0.01 dev=x1.mp2 param=w

+ start=15e-6 stop=20e-6 step=1e-6 where=rawfile

Release Date

Back

Page 12

Close

12

Affirma Spectre DC Device Matching Analysis Tutorial

In the above example, an internal sweep of dcmatch analyses will be performed

by sweeping the device parameter w of the device x1.mp2 from 15um to 20um

at each increment of 1um. The results will be printed as psf files. The psf files

will be named as dcmm6_0.dcmatch to dcmm6_5.dcmatch. Notice that even

it is an internal sweep, six files still will be generated. This is contradictory to a

dc or an ac analysis, where only a single psf file is generated while sweeping a

parameter. This is due to the fact while sweeping a parameter, the rank order of

the output contribution for each devices may become different. Thus we need to

store the results in multiple psf files.

dcmm7 n3 0 dcmatch mth=0.01 param=temp

+ start=25 stop=100 step=25

In the above example, temperature is swept from 25C to 100C at increment of

25C.

Release Date

Back

Page 13

Close

13

Affirma Spectre DC Device Matching Analysis Tutorial

Mismatch modeling

1. Use Model

After identifying the output, the user needs to specify the parameters for each device

contributing to the mismatch. Currently, The mismatch model implemented in Spectre for

Mosfet transistors introduces five additional model parameters, one for bjts and nine for

resistors.

To start the dc-mismatch analysis, the user types the analysis statement with the output

voltage on which the dc-mismatch analysis is to be performed. The results are:

1) The 3-sigma random output variation

2) The dc operating point information

3) For each Mosfet:

3-sigma output variation,

3-sigma Beta variation,

3 ( Ids )

Vout

Ids

3 ( )

------------------0

3-sigma Threshold voltage variation, 3(Vth)

3-sigma gate voltage variation, 3(Vg)

3-sigma current mismatch to nominal current ratio,

3 ( Ids )

-----------------------Ids 0

4) For each BJT

3-sigma output variation,

3 ( Ic )

Vout

Ic

3-sigma Vbe Variation, 3(Vbe)

Release Date

Back

Page 14

Close

14

Affirma Spectre DC Device Matching Analysis Tutorial

5) For each Resistor

3-sigma output variation,

3 ( Ir )

Vout

Ir

3-sigma Resistor current mismatch to nominal resistance current ratio,

3 ( Ir )

-------------------Ir 0

3-sigma VR variation, 3(Vr) = 3(Ir).R

3-sigma IR variation, 3(Ir)

3-sigma Resistor variation,

( Ir )

3 -----------------R

Ir 0

We define a threshold mth, below which the contributions will not be shown, currently, in

spectre mth = 0.1%. Mth is an analysis parameter.

2. Summary of Theory.

Statistical variation of drain current in a MOSFET is modeled by:

ds = I ds o + Ids

(EQ 1)

where:

Ids -- is the total drain to source current.

Id s o -- is the nominal current.

Ids -- is the variation in drain to source current due to local device variation.

Let Vout be the output signal of interest, then the variance of Vout due to the i th

MOSFET is approximated by:

2

Vout) i =

Vout

Id s i

Release Date

Back

Id s o

Page 15

2 ( Id s i )

(EQ 2)

Close

15

Affirma Spectre DC Device Matching Analysis Tutorial

Vout in (2) is the sensitivity of the output to the drain to source current

Id s i

and can be efficiently obtained in a standard way as outlined in part b.

The term

a- Mismatch models

The term 2 ( Id s i ) is the variance of the mismatch current in Mosfet transistors. The

mismatch in the current is assumed to be due to a mismatch in the threshold voltage

( Vth ) and the mismatch in the width to length ratio ( ). It is approximated as:

2

2 ( )

gm o

2 ( Ids )

2 ( Vth ) +

--------------------------------=

---------------------2

( Ids 0 ) 2

( Ids 0 ) 2

o

(EQ 3)

where

Ids

gm o = ----------Vth

,

Id s o

and currently, as implemented in Spectre:

2

2

mvtwl2

mvtwl

2 ( Vth ) = ------------------ + -------------------- + mvt0

WL

W L2

2

2 ( )

mbewl

----------------- = ------------------- + mbe0

WL

( 0 ) 2

Note, that gm o is computed at the DC bias solution from the device model equations,

the values a, b, c, d and e are the mismatch parameters while W and L are device

parameters.

Another way of representing the mismatch current is using the gate voltage variation

defined as:

Release Date

Back

Page 16

Close

16

Affirma Spectre DC Device Matching Analysis Tutorial

2 ( Ids )

2

( Vg ) ---------------------2

gm o

(EQ 4)

Similarly to the Mosfet, the bipolar 2 ( Ici ) and the resistor 2 ( Iri ) are computed for

each device provided that the device size, bias point and mismatch parameters are

known.

mrl

mrw

mrlw1

mrlw2

2 ( Ir )

------------------- = mr + ------------ + ----------------- + ------------------------------- + ------------------------------L mrlp W mrwp ( LW ) mrlw1 p ( LW ) mrlw2 p

Ir 02

( gm 0 ) 2

2 ( Ic )

----------------------------------=

( mvt0 ) 2

( Ic 0 ) 2

( Ic 0 ) 2

where gm0 is

Ic

VBE

and Ic0 is the nominal collector current, and Vbe =(mvt0)2

b-Mismatch analysis

Vout for each MOSFET i . The network is characterized

Id s i

with the standard MNA equations with the addition of the term for the mismatch

current:

The goal is to compute

( x ) + m Id s i = 0

i

(EQ 5)

where:

f -- is the vector of equations,

x -- is the vector of unknowns,

Release Date

Back

Page 17

Close

17

Affirma Spectre DC Device Matching Analysis Tutorial

Id s i -- is the mismatch current of the i th MOSFET,

m i -- is incidence column vector that maps the mismatch current of the ith device to

the proper MNA equations.

The output is defined as:

T

Vout = y x ,

(EQ 6)

where y is a column vector and superscript T represents the transpose.

In terms of (6), the sensitivity becomes:

T x

Vout = y ---------------- .

Id s i

Id s i

(EQ 7)

x

The term ---------------- is obtained by differentiating (5) with respect to Id s i -Id s i

f ( x ) x

--------------- ---------------- + m i = 0 ,

x Id s i

(EQ 8)

and then solving

f ( x)

x

---------------- = --------------x

Id s i

mi .

(EQ 9)

Combining (9) with (7), the expression for sensitivity becomes:

T f ( x)

Vout = y --------------x

Id s i

mi

(EQ 10)

Since there is only one output and many MOSFETS, it is efficient to define a

Release Date

Back

Page 18

Close

18

Affirma Spectre DC Device Matching Analysis Tutorial

vector z such that

T

T f ( x)

z = y --------------x

(EQ 11)

or

f ( x) T

--------------- z = y

x

(EQ 12)

After computing the vector z through a transpose solve in (12), the sensitivity of the

output with respect to each transistor current can be computed with one extra vector

product:

T

Vout = z m i

Id s i

(EQ 13)

and finally,

2 ( Vout ) =

( z T mi )

2 2

( Ids

i)

would be the variance of the output, where n is

i=1

the number of devices.

In the equations above, the bjt and the resistor contributions to the mismatch should

be added.

3. Finding Model Parameters.

To determine dcmatch model parameters, users have to go to their foundry or

modeling group, study the statistical process, then do a regression analysis. We will

give an example of how to use the concept of curve fitting to find model parameters.

The actual procedure may vary significantly and is a matter of art. We will only

introduce the concept. In general, to find parameters is not a trivial task.

Lets assume we want to find out the parameters mvtwl, mvtwl2, and mvt0, which are

used in the model equation

Release Date

Back

Page 19

Close

19

Affirma Spectre DC Device Matching Analysis Tutorial

2

mvtwl2

mvtwl

2 ( Vth ) = ------------------ + -------------------- + mvt0

WL

W L2

(EQ 14)

The modeling group needs to make, say 200 statistical measurements of the values

of 2 ( Vth ) by varying values of channel length L and width W. Provided that threshold

voltage extraction is a known procedure. Typically, threshold voltage is the value of

gate voltage that corresponds to a drain current of 1mA. Extraction of this parameter

is done at low drain bias (about 0.1V) although in modern technologies this value may

be even lower. Gate bias is increased gradually until this level of current is achieved.

After the 200 samples are collected, the task becomes to find parameters p1, p2, and

p3 to minimize the curve fitting error via the least square fit formula:

200

error =

i=1

p2

p1

2

y i ------------ + -------------2 + p 3

W i Li W L

(EQ 15)

i i

is the i-th measurement value (among the 200 measurements) of 2 ( Vth ) at

L = L i and W = W i . Once the p1, p2, and p3 are found, we can take the square root of

them to find mvtwl, mvtwl2 and mvt0, repectively. The minimum of error in Equation

(15) occurs where the derivative of error with respect to p1, p2, and p3 vanishes.

where

yi

error = 2

p1

error = 2

p2

Release Date

Back

200

p2

p1

1

y i ------------ + -------------2 + p 3 ------------ = 0

W i Li W L

W i Li

i=1

(EQ 16)

i i

200

p2

p1

1

y i ------------ + -------------2 + p 3 -------------2 = 0

W i Li W L

W L

i=1

i i

i i

Page 20

Close

(EQ 17)

20

Affirma Spectre DC Device Matching Analysis Tutorial

error = 2

p3

200

i=1

p2

p1

y i ------------ + -------------2 + p 3 ( 1 ) = 0

W i Li W L

(EQ 18)

i i

The Equations (16), (17), and (18) can be rearranged in normal form as:

------------------------- W-------------2 2 2 3 W L

i i

W L

L

1

-------------------------- W-------------2 3 2 4

2

L

W L

W L

1

1

-----------W i Li

1

------------2

W i Li

i i

p1

p2 =

p3

yi

-----------W i Li

yi

------------2

W i Li

(EQ 19)

yi

Assuming that the matrix in the Equation (19) is not singular, then (19) can be solved

for p1, p2, and p3, using standard LU decomposition and backsubstitution. If the

matrix is singular, then different method such as singular value decomposition can be

used. The model parameters mvtwl, mvtwl2, and mvt0 are simply the square root of

the p1, p2, and p3, respectively.

As for illustration, we attach a sample C program here. The first half portion of the

program is to cook up 200 sample data points of yi to mimic measurement data. We

also create the right hand side vector rhs as in Equation (19). The last half portion

creates the matrix, and calls dense matrix solver routines dgeco and dgesl from

LINPACK (a popular dense matrix package) to obtain the fitted parameters. Upon

executing the program, we got this result:

model parameter mvtwl = 0.01

model parameter mvtwl2 = 0.003

model parameter mvt0 = 0

Release Date

Back

Page 21

Close

21

Affirma Spectre DC Device Matching Analysis Tutorial

generating 200 samples using the above parameters ...

fitted parameter 0 = 0.0102933

fitted parameter 1 = 0.00290799

fitted parameter 2 = 0

The program is by no means to be robust or efficient. Nevertheless, it illustrates the

concept of curve fitting. The exact procedure for fitting your measurements to obtain

proper model parameters robustly has to be developed by your modeling group.

#include <stdio.h>

#include <string.h>

#include <math.h>

#define F77CONV(array,i,j,lda) (array[ (i) + (lda) * (j) ])

main() {

int i, j, k, samples, n, lda, one, zero;

double y, sigmavth2; /* sigma^2(dvth) */

double mvtwl, mvtwl2, mvt0;

double w, l;

double r, t, rcond, tmp;

double alpha[3][3], rhs[3], work[3];

double farray[9];

int ipvt[3];

double drand_();

/* the following are the model parameters to fit */

Release Date

Back

Page 22

Close

22

Affirma Spectre DC Device Matching Analysis Tutorial

mvtwl = 10e-3;

mvtwl2 = 3e-3;

mvt0 = 0;

printf(" model parameter mvtwl = %g\n", mvtwl);

printf(" model parameter mvtwl2 = %g\n", mvtwl2);

printf(" model parameter mvt0 = %g\n", mvt0);

n = lda = 3;

samples = 200;

zero = 0;

printf(" generating %d samples using the above parameters ...\n",samples);

for (i = 0; i<n; i++) {

for (j = 0; j<n; j++) {

alpha[i][j] = 0.0;

}

rhs[i] = 0.0;

}

r = drand_(&one);

l = 0.18;

/********************************************/

/* portion1: generate fake measurement data */

/********************************************/

k = 0;

for (i = 1; i<=samples; i++) {

w = 1.0 * i; /* different channel widths */

if (i >= samples/2) { /* different channel lengths */

Release Date

Back

Page 23

Close

23

Affirma Spectre DC Device Matching Analysis Tutorial

k++;

l = 0.36;

w = 1.0 * k;

}

sigmavth2 = mvtwl*mvtwl/(w*l) + mvtwl2*mvtwl2/(w*l*l) + mvt0*mvt0;

r = drand_(&zero)*5e-2;

/* generate fake measurement data */

y = (1.0 +r) * sigmavth2;

/* create least square fit right rhs */

rhs[0] += y/(w*l);

rhs[1] += y/(w*l*l);

rhs[2] += y;

}

/********************************************/

/* portion2: solve for p

*/

/********************************************/

/* create the curve fittling matrix */

l = 0.18;

k = 0;

for (i = 0; i<samples; i++) {

w = 1.0 * (i+1);

if ((i+1) >= samples/2) {

k++;

l = 0.36;

w = 1.0 * k;

}

Release Date

Back

Page 24

Close

24

Affirma Spectre DC Device Matching Analysis Tutorial

tmp = 1.0/(w*l);

alpha[0][0] += (tmp*tmp);

alpha[0][1] += (tmp*tmp)/l;

alpha[0][2] += tmp;

alpha[1][0] += (tmp*tmp)/l;

alpha[1][1] += (tmp*tmp)/(l*l);

alpha[1][2] += (tmp/l);

alpha[2][0] += tmp;

alpha[2][1] += tmp/l;

alpha[2][2] += 1.0;

}

/* convert to fortran array, since we will be calling fortran solvers */

for (i = 0; i < n; i++) {

for (j = 0; j < n; j++) {

F77CONV( farray, i, j, lda ) = alpha[i][j];

}

}

/* solve the matrix to obtain the three fitted model parameters */

dgeco_( farray, &n, &lda, ipvt, &rcond, work);

t = 1.0 + rcond;

if (t == 1.0) {

printf("singluar matrix of alpha encountered rcond = %g\n",rcond);

}

dgesl_( farray, &n, &lda, ipvt, rhs, &zero);

Release Date

Back

Page 25

Close

25

Affirma Spectre DC Device Matching Analysis Tutorial

/* after dgesl, rhs contains p1, p2, p3 now */

printf("\n");

for (i = 0; i< 3; i++) {

if (rhs[i] <= 0) rhs[i] = 0.0;

if (rhs[i] >= 0) {

printf(" fitted parameter %d = %g\n", i, sqrt(rhs[i]));

}

}

}

Release Date

Back

Page 26

Close

26

Você também pode gostar

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsNo EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsAinda não há avaliações

- High-Performance D/A-Converters: Application to Digital TransceiversNo EverandHigh-Performance D/A-Converters: Application to Digital TransceiversAinda não há avaliações

- Introduction To Tanner ToolDocumento8 páginasIntroduction To Tanner Toolshantanudeka72% (18)

- DSPACE Procedure With MPPT ExampleDocumento21 páginasDSPACE Procedure With MPPT ExampleSri SriAinda não há avaliações

- SPICEDocumento91 páginasSPICESiva YellampalliAinda não há avaliações

- Analyses and Output ControlDocumento10 páginasAnalyses and Output ControlSezai Alper TekinAinda não há avaliações

- Introduction To Multisim 12Documento11 páginasIntroduction To Multisim 12Madhuri RoyAinda não há avaliações

- Electrical Simulation Lab: EEE 454 IV Sem EN BranchDocumento28 páginasElectrical Simulation Lab: EEE 454 IV Sem EN Branchsachin10dulkarAinda não há avaliações

- Spice Analyse OutputDocumento10 páginasSpice Analyse OutputZealous_ShumbhAinda não há avaliações

- Flash ADC Design in ElectricDocumento22 páginasFlash ADC Design in ElectricNagaraj HegdeAinda não há avaliações

- Experiment Using Capture CMOS & NMOSDocumento14 páginasExperiment Using Capture CMOS & NMOSS.DharanipathyAinda não há avaliações

- Aim-Spice Tutorial: Florida International UniversityDocumento14 páginasAim-Spice Tutorial: Florida International UniversityHari100% (2)

- Module - 08 F2833x Analogue Digital ConverterDocumento28 páginasModule - 08 F2833x Analogue Digital ConverterMaria MEKLIAinda não há avaliações

- AnalogDocumento16 páginasAnalogchandushar1604Ainda não há avaliações

- ET 304A Laboratory Tutorial-Circuitmaker For Transient and Frequency AnalysisDocumento7 páginasET 304A Laboratory Tutorial-Circuitmaker For Transient and Frequency AnalysisZhong XiangAinda não há avaliações

- T Spice ExamplesDocumento42 páginasT Spice ExamplesVENKI50% (2)

- APSP - Lecture Notes 2Documento7 páginasAPSP - Lecture Notes 2Manjula sAinda não há avaliações

- F2833x Analogue Digital Converter: V V V D VDocumento28 páginasF2833x Analogue Digital Converter: V V V D VSaiAinda não há avaliações

- POWER SYSTEM - Prof - Sita SinghDocumento52 páginasPOWER SYSTEM - Prof - Sita Singhanoushka pakhareAinda não há avaliações

- DAC ConverterDocumento10 páginasDAC ConverterAmarnath M DamodaranAinda não há avaliações

- Restricted Earth Fault Protection - 1Documento17 páginasRestricted Earth Fault Protection - 1Ahetesham MullaAinda não há avaliações

- Technical Report TemplateDocumento10 páginasTechnical Report TemplateMohamed Adam Ahmed Fouad Mohamed FAHMYAinda não há avaliações

- Lab - Experiment - 1-3Documento11 páginasLab - Experiment - 1-3Md. Sadique SheikhAinda não há avaliações

- Efficient Energy Meter DesignDocumento35 páginasEfficient Energy Meter DesignMahima RebelloAinda não há avaliações

- A New Algorithm To Determine The Magnitudes of DC Voltage Sources in Asymmetric Cascaded Multilevel Converters Capable of Using Charge Balance Control MethodsDocumento6 páginasA New Algorithm To Determine The Magnitudes of DC Voltage Sources in Asymmetric Cascaded Multilevel Converters Capable of Using Charge Balance Control MethodsUmair AliAinda não há avaliações

- ECE 4101 Computer and Information Lab III (ECE 4141 VLSI Design Part)Documento7 páginasECE 4101 Computer and Information Lab III (ECE 4141 VLSI Design Part)Mark Chow Khoon KeatAinda não há avaliações

- Homework #2 Notes: ECEN 474Documento9 páginasHomework #2 Notes: ECEN 474DanAinda não há avaliações

- DC Motor Speed Control ThesisDocumento5 páginasDC Motor Speed Control Thesisafloziubadtypc100% (1)

- Cad Exp ManualDocumento23 páginasCad Exp ManualRavindra KumarAinda não há avaliações

- Inverter DesignDocumento10 páginasInverter DesignKirthika Vinoth KumarAinda não há avaliações

- NGSPICE Manual-Devices and Circuits LabDocumento15 páginasNGSPICE Manual-Devices and Circuits LabShreya R HAinda não há avaliações

- Dig SilentDocumento32 páginasDig Silentchmsno111Ainda não há avaliações

- PTI Section 9 Analog DigitalDocumento14 páginasPTI Section 9 Analog Digitalchrist9088Ainda não há avaliações

- Case Study of PID Control in An FPGA PDFDocumento18 páginasCase Study of PID Control in An FPGA PDFwigaYeHtetAinda não há avaliações

- ADC Design Guide MicrochipDocumento0 páginaADC Design Guide MicrochipOrlando MartínAinda não há avaliações

- Design of Low Power 4-Bit Flash ADC Based On Standard Cells: Marcel Siadjine Njinowa, Hung Tien Bui François-Raymond BoyerDocumento4 páginasDesign of Low Power 4-Bit Flash ADC Based On Standard Cells: Marcel Siadjine Njinowa, Hung Tien Bui François-Raymond BoyerSunil PandeyAinda não há avaliações

- UPS SystemDocumento4 páginasUPS SystemMadhu JbAinda não há avaliações

- EEE111 Multisim ManualDocumento14 páginasEEE111 Multisim ManualSHADOW manAinda não há avaliações

- AN3190Documento6 páginasAN3190noopreply5316Ainda não há avaliações

- New High Speed PCB Board DesignDocumento58 páginasNew High Speed PCB Board DesignthisyearAinda não há avaliações

- Scs ManualDocumento83 páginasScs ManualSandali SinghAinda não há avaliações

- Frequency Response of A CMOS Common-Source Amplifier: Experiment # 5Documento10 páginasFrequency Response of A CMOS Common-Source Amplifier: Experiment # 5Md. Sadique SheikhAinda não há avaliações

- EECS267B Proj3Documento19 páginasEECS267B Proj3hellwellAinda não há avaliações

- Design Project: (Due: Friday, December 8, 2006, 5pm PT)Documento6 páginasDesign Project: (Due: Friday, December 8, 2006, 5pm PT)Ibrahim MuhammedAinda não há avaliações

- Thesis On Pipeline AdcsDocumento6 páginasThesis On Pipeline Adcsamyholmesmanchester100% (2)

- Mbed BK Ed2 CH 5Documento20 páginasMbed BK Ed2 CH 5NecAinda não há avaliações

- Assignment 3 - ModifiedDocumento5 páginasAssignment 3 - ModifiedEDWIN DOMINICAinda não há avaliações

- Ground Current Distribution Conventional Short Circuit Software ResearchGateDocumento13 páginasGround Current Distribution Conventional Short Circuit Software ResearchGatealberto.rojasAinda não há avaliações

- Monte Carlo Simulation: For Better Yield and PerformanceDocumento51 páginasMonte Carlo Simulation: For Better Yield and PerformanceRizwan Shaik PeerlaAinda não há avaliações

- Central University of Punjab: BhatindaDocumento14 páginasCentral University of Punjab: Bhatindaaayush tomarAinda não há avaliações

- Top-Down, Constraint-Driven Design Methodology Based Generation of N-Bit Interpolative Current Source D/A ConvertersDocumento4 páginasTop-Down, Constraint-Driven Design Methodology Based Generation of N-Bit Interpolative Current Source D/A ConvertersImen Ben MansourAinda não há avaliações

- Implementation An Adaptive Data Window Technique in A Distance Relay M.S. Sachdev T.S. Sidhu D.S. Ghotra University of Saskatchewan, CanadaDocumento4 páginasImplementation An Adaptive Data Window Technique in A Distance Relay M.S. Sachdev T.S. Sidhu D.S. Ghotra University of Saskatchewan, Canadasirisiri100Ainda não há avaliações

- Pspice Lab ManualDocumento30 páginasPspice Lab ManualSrinivasarao ThumatiAinda não há avaliações

- Variable Frequency Digital PWM Control For Low-Power Buck ConvertersDocumento5 páginasVariable Frequency Digital PWM Control For Low-Power Buck Convertersantonytechno100% (1)

- UPS SystemDocumento4 páginasUPS Systemमृत्युंजय झाAinda não há avaliações

- SpectreRF Simulation TutorialDocumento110 páginasSpectreRF Simulation TutorialHaoWangAinda não há avaliações

- Power Electronics Open Ended Lab - 2022Documento7 páginasPower Electronics Open Ended Lab - 2022Hassan AliAinda não há avaliações

- Analog Assignment ADVDDocumento24 páginasAnalog Assignment ADVDRajeevDuttAinda não há avaliações

- Introduction To Ni Multisim: Lucio PancheriDocumento36 páginasIntroduction To Ni Multisim: Lucio PancheriDaniel Enrique Erazo MujicaAinda não há avaliações

- STEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10No EverandSTEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10Ainda não há avaliações

- Important !!Documento1 páginaImportant !!Thomas GeorgeAinda não há avaliações

- Eetop - CN Lecture1Documento4 páginasEetop - CN Lecture1Thomas GeorgeAinda não há avaliações

- Resume ChenDocumento4 páginasResume ChenThomas GeorgeAinda não há avaliações

- PHD Thesis Vincent LORENTZDocumento216 páginasPHD Thesis Vincent LORENTZThomas GeorgeAinda não há avaliações

- Donate To USDocumento1 páginaDonate To USThomas GeorgeAinda não há avaliações

- MitDocumento172 páginasMitThomas GeorgeAinda não há avaliações

- Mississippi State University Dallas Semiconductor: Standard Cell TutorialDocumento133 páginasMississippi State University Dallas Semiconductor: Standard Cell Tutorialshri3415Ainda não há avaliações

- Berkeley Design Automation Announces Analog Fastspice RF-: Edn StaffDocumento2 páginasBerkeley Design Automation Announces Analog Fastspice RF-: Edn StaffThomas GeorgeAinda não há avaliações

- Spectre Transient Simulations: 2.1 ReadingDocumento5 páginasSpectre Transient Simulations: 2.1 ReadingAnonymous CNAdojAinda não há avaliações

- PSP-based Scalable MOS Varactor Model: Proceedings of The Custom Integrated Circuits Conference October 2007Documento9 páginasPSP-based Scalable MOS Varactor Model: Proceedings of The Custom Integrated Circuits Conference October 2007Thomas GeorgeAinda não há avaliações

- LiberateTutorial PDFDocumento6 páginasLiberateTutorial PDFRahul CPAinda não há avaliações

- 001 Course OutlineDocumento35 páginas001 Course OutlineJubin JainAinda não há avaliações

- Dcmatch AppnoteDocumento26 páginasDcmatch AppnoteThomas GeorgeAinda não há avaliações

- Sturm Umn 0130E 13471Documento189 páginasSturm Umn 0130E 13471Thomas GeorgeAinda não há avaliações

- A CMOS Variable Width Short-Pulse Generator CircuiDocumento5 páginasA CMOS Variable Width Short-Pulse Generator CircuiThomas GeorgeAinda não há avaliações

- Synopsys Finfets PDFDocumento8 páginasSynopsys Finfets PDFThomas GeorgeAinda não há avaliações

- NoiseanalysisDocumento18 páginasNoiseanalysisThomas GeorgeAinda não há avaliações

- Cadence Digital and Custom Analog Tools Achieve TSMC Certification For 16FF Process Companies Collaborate On 10nm FinFETDocumento3 páginasCadence Digital and Custom Analog Tools Achieve TSMC Certification For 16FF Process Companies Collaborate On 10nm FinFETThomas GeorgeAinda não há avaliações

- Julien ManifestoDocumento2 páginasJulien ManifestoMax Bateman100% (5)

- Dumping PicDocumento6 páginasDumping PicuserdiedAinda não há avaliações

- Hints For Cadence VirtuosoDocumento7 páginasHints For Cadence VirtuosoThomas GeorgeAinda não há avaliações

- 001 Course OutlineDocumento8 páginas001 Course OutlineThomas GeorgeAinda não há avaliações

- Circuit Extraction and DRC: 17.4.1 SPF, RSPF, and DSPFDocumento7 páginasCircuit Extraction and DRC: 17.4.1 SPF, RSPF, and DSPFThomas GeorgeAinda não há avaliações

- NoiseanalysisDocumento18 páginasNoiseanalysisThomas GeorgeAinda não há avaliações

- Form-6A-Application For Inclusion of Name in Electoral Roll by An Overseas Indian Elector. (English)Documento4 páginasForm-6A-Application For Inclusion of Name in Electoral Roll by An Overseas Indian Elector. (English)Ilamaran HemalathaAinda não há avaliações

- Senesky Law Ee290Documento13 páginasSenesky Law Ee290Thomas GeorgeAinda não há avaliações

- Thesis PsDocumento192 páginasThesis PsThomas GeorgeAinda não há avaliações

- Post-Layout Simulation: 6.1 InstructionsDocumento7 páginasPost-Layout Simulation: 6.1 InstructionsThomas GeorgeAinda não há avaliações

- Switched Capacitor Circuits For DC-DC Conversion: Chi Law Matthew Senesky Nov. 25, 2003Documento17 páginasSwitched Capacitor Circuits For DC-DC Conversion: Chi Law Matthew Senesky Nov. 25, 2003Thomas GeorgeAinda não há avaliações

- A Comparative Study of Methodologies To Optimize PDocumento5 páginasA Comparative Study of Methodologies To Optimize PThomas GeorgeAinda não há avaliações

- Analysis and Design of MOSFET Based Amplifier in Different ConfigurationsDocumento8 páginasAnalysis and Design of MOSFET Based Amplifier in Different ConfigurationsPraveen KumarAinda não há avaliações

- Project Example 1Documento10 páginasProject Example 1dervingameAinda não há avaliações

- User Manual Floppy To USB Emulator: ModelDocumento2 páginasUser Manual Floppy To USB Emulator: ModelRadulian DanielAinda não há avaliações

- Physical Mechanical and Flexural Properties of 3 Orthodontic Wires An in Vitro Study. DANIELA DLICANDocumento8 páginasPhysical Mechanical and Flexural Properties of 3 Orthodontic Wires An in Vitro Study. DANIELA DLICANAlvaro ChacónAinda não há avaliações

- Rail Mechanical PropertiesDocumento46 páginasRail Mechanical PropertiesAGnes Stephani MuntheAinda não há avaliações

- TS 34Documento2 páginasTS 34Sunil Maurya0% (1)

- Maps and Damos ID For EDC16 VAG ECUDocumento7 páginasMaps and Damos ID For EDC16 VAG ECUGuler RahimAinda não há avaliações

- Company ProfileDocumento6 páginasCompany ProfileFaidzil ChabibAinda não há avaliações

- D 2564 - 96 - Rdi1njqtotzb PDFDocumento5 páginasD 2564 - 96 - Rdi1njqtotzb PDFAndre CasteloAinda não há avaliações

- Behringer EPR900 Powered Speaker SchematicsDocumento14 páginasBehringer EPR900 Powered Speaker SchematicsJimAinda não há avaliações

- Croner PKE280 H35 Spec SheetDocumento2 páginasCroner PKE280 H35 Spec Sheetvictor hugoAinda não há avaliações

- 300-430-ENWLSI Implementing Cisco Enterprise Wireless Networks PDFDocumento3 páginas300-430-ENWLSI Implementing Cisco Enterprise Wireless Networks PDFEdu100% (1)

- Boiling MechanismDocumento16 páginasBoiling MechanismherawanadifAinda não há avaliações

- NIC Components NTC-T SeriesDocumento10 páginasNIC Components NTC-T SeriesNICCompAinda não há avaliações

- Data Structures and Algorithms: (CS210/ESO207/ESO211)Documento23 páginasData Structures and Algorithms: (CS210/ESO207/ESO211)Moazzam HussainAinda não há avaliações

- LCD Monitor DC T201WA 20070521 185801 Service Manual T201Wa V02Documento59 páginasLCD Monitor DC T201WA 20070521 185801 Service Manual T201Wa V02cdcdanielAinda não há avaliações

- VVP Engineering College: Assignment 2Documento12 páginasVVP Engineering College: Assignment 2Fake 1Ainda não há avaliações

- E5263 - M4A87TD EVO PDFDocumento76 páginasE5263 - M4A87TD EVO PDFLeandro Henrique AgostinhoAinda não há avaliações

- Recondition BatteryDocumento46 páginasRecondition Batteryafic219473100% (1)

- ETABS 19.0.0-Report ViewerDocumento207 páginasETABS 19.0.0-Report ViewerDaniel Pesca SilvaAinda não há avaliações

- University of Cambridge International Examinations General Certificate of Education Advanced LevelDocumento24 páginasUniversity of Cambridge International Examinations General Certificate of Education Advanced LevelHubbak KhanAinda não há avaliações

- MTK 1023-Material and ConsumableDocumento13 páginasMTK 1023-Material and ConsumableGraceLamAinda não há avaliações

- Amyuni PDF ConverterDocumento22 páginasAmyuni PDF ConverterMikeyarnoldAinda não há avaliações

- Wireless Selection GuideDocumento50 páginasWireless Selection GuideShailesh KshatriyaAinda não há avaliações

- LucasFilm Sound Effects Library - Track & Index ListDocumento22 páginasLucasFilm Sound Effects Library - Track & Index ListKALFER0% (1)

- Baseline Processing ReportDocumento17 páginasBaseline Processing ReportMAMAN MAMANAinda não há avaliações

- Finals DSP WithMinimalErrors PDFDocumento64 páginasFinals DSP WithMinimalErrors PDFanembam putobungbongAinda não há avaliações

- Dax Patel CVDocumento1 páginaDax Patel CVPriyanshAinda não há avaliações

- Toyota 80 SeriesDocumento5 páginasToyota 80 Seriesaagi_dAinda não há avaliações

- H Beam Load Bearing CalculationDocumento31 páginasH Beam Load Bearing CalculationMuhammad Attiq Ur RahmanAinda não há avaliações