Escolar Documentos

Profissional Documentos

Cultura Documentos

Introdução aos Retificadores Monofásicos

Enviado por

Eduardo AlbuquerqueDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Introdução aos Retificadores Monofásicos

Enviado por

Eduardo AlbuquerqueDireitos autorais:

Formatos disponíveis

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

FACULDADE DE ENGENHARIA ELTRICA E DE COMPUTAO UNICAMP

EE 833 ELETRNICA DE POTNCIA

CONVERSORES CA-CC

TEORIA

1.1 Introduo

Na grande maioria das aplicaes a fonte de alimentao ou fonte de potncia do

circuito est disponvel na forma de corrente alternada ou AC na freqncia de 50

ou 60Hz, a partir de uma rede de distribuio em corrente alternada, devido

principalmente, facilidade de adaptao do nvel de tenso por meio de

transformadores.

Assim necessrio quase sempre convert-la em corrente contnua ou corrente

DC. Esta funo pode ser realizada por um retificador. A figura abaixo ilustra um

diagrama em bloco de um retificador.

is

vd

Fig.1.1 Diagrama em bloco de um retificador

As caractersticas do retificador so:

A sada DC deve ser livre de ripple tanto e to menor quanto maior o

capacitor do filtro;

A corrente de entrada (is) elevada perto do pico do sinal AC e descontinua;

Devido a isto a corrente de entrada altamente distorcida produzindo um

baixo fator de potncia;

Limites impostos neste fator de potncia impem que retificadores com

somente diodos sejam evitados.

1

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

1.2 Retificadores no-controlados monofsicos

Os retificadores podem ser classificados segundo a sua capacidade de ajustar

o valor da tenso de sada (controlados x no controlados); de acordo com o nmero

de fases da tenso alternada de entrada (monofsico, trifsico, hexafsico, etc.); em

funo do tipo de conexo dos elementos retificadores (meia ponte x ponte

completa).

Os retificadores no-controlados so aqueles que utilizam diodos como

elementos de retificao.

Os diodos de potncia diferem dos diodos de sinal por terem uma capacidade

superior em termos de nvel de tenso de bloqueio (podendo atingir at alguns kV,

num nico dispositivo), e poderem conduzir correntes de at alguns kA.

Nas aplicaes em que a tenso alternada a da rede, tais diodos no

precisam ter seu processo de desligamento muito rpido, uma vez que a freqncia

da rede baixa (50 ou 60 Hz).

Usualmente topologias em meia ponte no so aplicadas. A principal razo

que, nesta conexo, a corrente mdia da entrada apresenta um nvel mdio diferente

de zero. Tal nvel contnuo pode levar elementos magnticos presentes no sistema

(indutores e transformadores) saturao, o que prejudicial ao sistema.

Topologias em ponte completa absorvem uma corrente mdia nula da rede, no

afetando, assim, tais elementos magnticos.

1.2.1 Carga Puramente resistiva

A figura 1.1 mostra o circuito e as formas de onda com carga resistiva para

um retificador monofsico com topologia de meia-ponte, tambm chamado de meiaonda.

Devido ao grande ripple na tenso v e na corrente i este retificador tem pouco

uso prtico.

i

vd

vs

Fig.1.2 Retificador bsico com carga resistiva

2

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

vs

vd

i

imedia

Fig.1.3 Formas de onda do retificador bsico com carga resistiva

Com carga resistiva as formas de onda da tenso e da corrente na sada do

retificador e na carga so as mesmas, como mostrado na figura 1.3. A corrente de

entrada apresenta-se com a mesma forma e fase da tenso.

1.2.2 Carga indutiva

Vamos considerar agora uma carga indutiva com um indutor em srie com um

resistor. A figura 1.4 mostra este retificador.

vdiodo

vL

L

vd

vs

vR

Fig.1.4 Retificador bsico com carga indultiva

Para vs positiva o diodo pode ser considerando como um curto e a corrente no

circuito dado por:

vs = Ri + Ldi/dt

(1.1)

3

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

As formas de ondas so mostradas na figura 1.5. At o tempo t1, vs > vR ,isto

vL positivo, a corrente aumenta, e o indutor acumula energia. Alm de t1, vL tornase negativa, e a corrente comea a decrescer. Aps t2, a voltagem de entrada vs

negativa mas a corrente ainda positiva e o diodo por causa da energia armazenada

no indutor.

vs

vR

i

imedia

t2

t1

rea

A

vL

t3

rea B

vdiodo

vL

vL

L

vs

vd

i=0

L

R

vR vs

vd=0

Fig.1.5 Formas de onda do retificador bsico com carga indutiva

4

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

A voltagem na carga negativa no intervalo t2 e t3. Portanto, com relao ao

caso resistivo a voltagem mdia de sada menor.

Exerccio: Utilizando a relao vL = Ldi/dt e as formas de onda acima mostre

que a rea A igual a rea B.

1.2.3 Carga indutiva

O retificador com carga capacitiva (fig. 1.6) faz com que a tenso de sada

apresente-se alisada, elevando o seu valor mdio em relao carga resistiva. O

capacitor carrega-se com a tenso de pico da entrada (desprezando a queda nos

diodos). Quando a tenso de entrada se torna menor do que a tenso no capacitor os

diodos ficam bloqueados e a corrente de sada fornecida exclusivamente pelo

capacitor, o qual vai se descarregando, at que, novamente, a tenso de entrada

fique maior, recarregando o capacitor.

A forma de onda da corrente de entrada muito diferente de uma senide,

apresentando pulsos de corrente nos momentos em que o capacitor recarregado,

como mostrado na figura 1.7.

i

vd

vs

Fig.1.6 Retificador bsico com carga capacitiva

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

i

vs

vd

vdmedia

Fig.1.7 Formas de onda do retificador bsico com carga capacitiva

1.3 Retificadores com ponte de diodo monofsico

Um retificador com uma ponte de diodo mostrado na figura 1.8. Um

capacitor de filtro de alto valor colocado na sada do retificador. O fonte de sinal

de entrada modelada sua impedncia interna que normalmente indutiva (LS).

Para facilitar a compreenso deste circuito ns analisaremos com maneira mais

simples.

icarga

id

LS

vs

is

vd

Cd

fig.1.8 Retificador com ponte de diodo monofsico

6

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

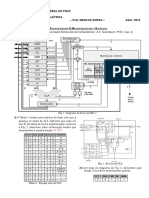

1.3.1 Circuito idealizado com LS = 0

Como uma primeira aproximao, vamos supor que Ls=0 e o lado DC do

retificador substitudo por uma fonte de corrente (carga altamente indutiva) ou

como uma resistncia R. A figura 1.9 mostra esta simplificao.

id

D1

D1

D3

D3

is

is

vs

vs

vd

vd

id

D4

D2

D4

a)

D2

b)

fig.1.9 Retificador idealizado com LS = 0

Os circuitos acima podem ser redesenhados consistindo de dois grupos de

diodos: o de topo como os diodos D1 e D3 e de os baixo D2 e D4 como mostrado

na figura 1.10. Com LS = 0 fcil de verificar a operao de cada grupo. A corrente

id flue continuamente atravs de um diodo de cada grupo.

No grupo de topo, os catodos dos dois diodos esto em um mesmo potencial,

portanto aquele diodo com mais potencial em seu anodo conduzir. Isto , quando vs

for positiva, o diodo D1 conduzir id e vs aparecer como uma voltagem reversa

atravs do diodo D3. Quando vs for negativa , a corrente id comutar

instantaneamente para o diodo D3 e a agora a voltagem vs ser aplicada de forma

reversa em D1.

No grupo de baixo acontece exatamente o anlogo sendo apenas a polalarida

das tenses invertidas.

A figura 1.11 mostra as formas de onda destes retificadores

7

EE 833 Eletrnica de Potncia

2005

is

FEEC - UNICAMP

D1

id

vs

D3

vd

D4

id

D2

fig.1.10 Retificador redesenhado

vs

is

imedia

vd

id

imedia

(a)

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

vs

is

id

t

vd

id

t

(b)

Fig.1.11 Formas de ondas dos retificadores das (a) fig 1.9a e fig 1.9b

Exerccio: Mostre que se Vs for o valor rms de sinal de entrada vs ,ento o valor

mdio na sada do retificador igual 22/ 0.9VS.

1.3.2 Efeitos de LS na comutao de corrente

Vamos agora analisar o efeito da indutncia finita do lado AC na operao do

circuito. Ns assumimos que o lado DC pode ser representado por uma fonte de

corrente constante Id como mostrado na figura 1.12. Devido a presena do indutor

Ls, a transio na corrente de entrada is de um valor +Id para Id ou vice-versa no

ser instantnea. O tempo finito necessrio para isto chamado de tempo de

comutao da corrente, e este processo onde a corrente desloca a conduo de um

diodo para o outro chamado de processo de comutao de corrente.

Para entender este processo, considere o circuito hipottico da figura 1.13 a)

com dois diodos alimentado por uma fonte de voltagem vs = 2VSsent. A figura

1.13 b) mostra as formas de ondas.

9

EE 833 Eletrnica de Potncia

2005

D1

FEEC - UNICAMP

D3

LS

vs

is

Id

vd

D4

D2

Fig1.12 Retificador simples com LS

vL

vs

D1

vs , vd

vd

LS

is

D2

is

Id

Id

t=0

a)

vd

vs

b)

Fig1.12 a) Circuito bsico para ilustrar a comutao de corrente. b) Formas de

ondas

Antes de t=0 a voltagem vs negativa e a corrente Id circula atravs de D2

com vd = 0 e is = 0. Quando vs torna-se positiva em t=0, uma voltagem direta

aparece sobre o diodo D1 e este comea a conduzir. A forma da corrente is pode ser

construda com o auxilio das figuras 1.13a) e b). Desde que o diodo D2 est

conduzindo, este fornece um curto (diodo ideal) por onde a corrente is pode fluir

(0<is<Id) as duas corrente da malha so is e Id. Portanto a corrente do diodo D2, iD2

10

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

= Id is . A corrente is cresce at Id desde que iD2 no pode ser negativa, como

conseqncia, o diodo D2 para de conduzir em u=t como mostra a figura 1.13 b).

As formas de ondas so mostradas na figura 1.14 como funo de t.

vL

vs

vL=0

D1

vs

iD1

LS

iD2

iD1

is=Id

Id

D2

is

LS

D1

Id

D2

vd=vs

iD2

vd=0

a)

b)

Fig.1.13 a) Circuito durante a comutao. b) Aps a comutao

vd

vd =0

0

t

rea A

vs

vL

0

t

is

t

Fig.1.14 Formas de onda do circuito da figura 1.12 a)

Ficou claro que a corrente is atravs do indutor comea com o valor zero no

comeo da comutao e cresce at o Id n0 fim da comutao.

Durante o intervalo da comutao a voltagem vs aparece sobre o indutor,

portanto,

11

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

vL = vs = 2VSsent = Ls dis/dt para 0<t<u

(1.2)

O lado direito desta equao pode ser escrito na forma

Ls dis/dt = Ls dis/d(t)

(1.3)

2VSsent =Ls dis/d(t)

(1.4)

Portanto,

Integrando ambos os lados da equao (1.4), temos

u

2VS 0 sent d(t) = Ls

Id

dis

(1.5)

O lado esquerdo da equao (1.5) a integral da voltagem vL durante o intervalo da

comutao que igual a rea(Au) mostrada na figura 1.14, logo

u

Au = 2VS

sent d(t) = Ls Id

Au =2VS (1-cos u) = Ls Id

(1.6)

(1.7)

Portanto, a equao (1.7) indica que a integral na voltagem de comutao no

intervalo de comutao pode ser sempre calculado pelo produto Ls Id.. Desta

equao temos ainda,

cos u = 1 - Ls Id /2VS

(1.8)

Se Ls =0 implica que u =0. Ou seja, a comutao instantnea.

Exerccio: Estenda o mesmo raciocnio para explicar o processo de

comutao e as formas de onda (fig.1.15) do circuito retificador em ponte mostrado

na figura 1.12. Mostre tambm que agora cos u=1 - 2LsId /2VS.

12

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

vd

vd =0

0

t

vs

rea Au

vL

0

is

Fig. 1.15 Formas de ondas do retificador monofsico com Ls.

1.3.3 Voltagem constante no lado DC

Finalmente vamos considerar o circuito mostrado na figura 1.16, onde

assumimos que o retificador alimenta uma fonte de tenso DC. Esta uma

aproximao para o circuito com um grande capacitor C. Outra suposio que a

corrente id zero durante os cruzamento de zero de vs, como mostrado na figura

1.16c) sob esta condies, o circuito equivalente o da figura 1.16b). Considerando

a figura 1.17, quando vs excede em b, os diodos D1 e D2 comeam a conduzir. A

corrente alcana um pico em p, alm do qual vL torna-se negativa. A corrente torna13

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

se zero em f, quando as reas A e B so iguais. A corrente permanece zero at +b.

Para um dado valor de Vd, o valor mdio Id da corrente dc pode ser facilmente

calculado:

1. O ngulo b pode ser calculado da equao

Vd = 2Vssin b

(1.9)

2. Como mostrado na figura, a voltagem no indutor zero em b e torna-se

novamente zero em p antes de torna-se negativa. Por simetria da figura

temos,

p = - b

(1.20)

id

D1

D3

id

LS

LS

vs

vs

is

is

Vd

Vd

D4

D2

a)

b)

Fig. 1.16 a) Retificador com fonte constante. b) Circuito equivalente

14

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

vs V

d

is

id

Id

vL

0

Fig. 1.17 Formas de ondas

3. Quando a corrente est fluindo, a voltagem no indutor vL dada por

vL = Lsdid /dt =2Vssin (t) - Vd

(1.21)

e integrando com relao a t resulta,

Ls

did =

{2Vssent d(t) -

onde >b. Portanto

15

Vd }d(t) (1.22)

EE 833 Eletrnica de Potncia

2005

id () = 1/Ls

FEEC - UNICAMP

{2Vssent d(t) -

Vd }d(t)

(1.23)

4. O ngulo f pode ser encontrando como

0 = 1/Ls

{2Vssent d(t) -

Vd }d(t)

(1.24)

5. O valor mdio Id da corrente dc pode ser obtido pela a integral de id () de b

f e dividindo por :

Id =

f

b id ()d

(1.25)

6. Se uma fonte vs for curto-cicuitada com uma indutncia Ls a corrente rms Ishort

que passar pelo o indutor dada por:(deixado para provar como exerccio)

Ishort = Vs /Ls

(1.26)

7. Podemos plotar um grfico de Id normalizado com Ishort em funo de Vd

normalizado com 0.9Vs =Vdo.. A figura 1.18 mostra este grfico. Note que Id

igual zero em Vdo = valor de pico de vs (2Vs /0.9 1.57 Vs ).

Id /Ishort

16

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

0.12

0.10

0.08

0.06

0.04

0.02

1.20 1.25

1.30

1.35

1.40

1.45

1.50

1.60 Vd /Vdo

1.55

1.57

Fig. 1.18 Id normalizada versus Vd no retificador com

fonte de tenso constante.

1.3.4 Retificador Prtico

A figura 1.19 mostra um retificador prtico. A carga representada pela

resistncia equivalente Rload. Neste circuito algum ripple existe na voltagem do

capacitor de forma que a anlise deve ser feita de forma diferente da anlise

anterior.

Anlise deve ser feita assumindo novamente uma forte descontinuidade da

corrente is como encontrada comumente na prtica, caso contrrio, a anlise

torna-se difcil.

deixado como exerccio para o aluno a anlise deste retificador.

Aqui fazendo a simulao deste circuito para mostrar na figura 1.20 as formas

de onda da corrente e voltagem neste retificador.

D1

LS

B

17

D3

id

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

Fig. 1.19 Retificador prtico

Circuito simulado

18

EE 833 Eletrnica de Potncia

Date/Time

400mA

run:

2005

FEEC - UNICAMP

* C:\Curso Graduacao\ee833\Simulao\Retificador.sch

08/04/105 16:04:11

Temperature:

(A) Retificador

27.0

80V

60V

300mA

40V

200mA

20V

100mA

0V

0A

-20V

-100mA

-40V

-200mA

-60V

-300mA

>>

-80V

0s

1

5ms

I(Ls)

A1:(9.188m,52.48)

A2:(0.00,0.00)

Date: August 04, 2005

10ms

V(vs:+,vs:-)

V(vd)

Time

DIFF(A):(9.188m,52.48)

Page 1

15ms

Time:

20ms

16:08:00

Fig. 1.20 Formas de onda do retificador prtico.

1.4 Retificadores no-controlados com entrada trifsica

Quando a potncia da carga alimentada se eleva, via de regra so utilizados

retificadores trifsicos, a fim de, distribuindo a corrente entre as 3 fases, evitar

desequilbrios que poderiam ocorrer caso a corrente fosse consumida de apenas 1 ou

2 fases.

19

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

Neste caso a corrente fornecida, a cada intervalo de 60 graus, por apenas 2

das 3 fases. Podero conduzir aquelas fases que tiverem, em mdulo, as duas

maiores tenses. Ou seja, a fase que for mais positiva, poder levar o diodo a ela

conectado, na semi-ponte superior, conduo. Na semi-ponte inferior poder

conduzir o diodo conectado s fases com tenso mais negativa.

A figura 1.21 mostra o retificador com entrada trifsica.

id

P

va

a

vb

LS

vcn

LS

c

D3

D5

ia

Cd

D1

LS

vd

Rload

ib

ic

D4

D6

D2

N

Fig. 1.21 Retificador com entrada trifsica.

1.4.1 Circuito idealizado com LS

Inicialmente vamos analisar o retificador supondo LS = 0 e o lado dc

substitudo por uma fonte de corrente constante. Procedimento anlogo feito

anteriormente para uma fase. As formas de ondas das voltagens e correntes so

mostradas na figura 1.22.

20

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

* C:\Curso Graduacao\ee833\Simulao\exp1\Rettrifasico.sch

Date/Time run: 08/09/105 14:51:12

Temperature: 27.0

(A) Rettrifasico

40V

-40V

V(va:+)

V(vb:+)

V(vc:+)

50V

Vp

Vn

-50V

V(vp)

V(vn)

80V

Vd = Vp - Vn

60

SEL>>

0V

V(vp,vn)

1.1A

D5

D4

D2

D3

D5

D1

D3

D6

D4

D5

D1

D6

D2

D3

D1

D2

D4

D4

-1.1A

0s

-I(Lsa)

10ms

-I(Lsb)

20ms

-I(Lsc)

A1:(12.58m,56.98) A2:(15.27m,56.64)

Date: August 09, 2005

30ms

Time

DIFF(A):(-2.690m,344.93m)

Page 1

40ms

50ms

Time: 15:28:05

Fig. 1.22 Formas de ondas das voltagens e corrente no

retificador trifsico com Ls desprezado.

Com LS = 0, a corrente Id flui atravs de um diodo do grupo superior(D1,D3,D5) e

21

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

de um diodo do grupo inferior(D2,D4,D6). No grupo superior o diodo com maior

potencial no seu anodo conduzir e os outros dois permanecero reversamente

polarizados. No grupo superior o diodo com menor potencial no seu catodo

conduzir e os outros dois permanecero reversamente polarizados.

A voltagem vd pode ser encontrada em funo das voltagens ac pela expresso

vd = vP vn

(1.27)

onde vp e vn so as voltagem no ponto P e no ponto N respectivamente com relao

ao ponto neutro n.

A voltagem instantnea de vd consiste de seis segmentos por ciclo da linha.

Assim, este retificador tambm chamado com retificador de seis pulsos. Cada diodo

conduz por 120.

A comutao da corrente de um dos diodos intantnea baseada na suposio

que Ls =0.

Exerccio: Determine o valor mdio da voltagem de sada para um sinal entre

qualquer duas fases dado por 2VFF cos t.

1.4.2 Efeito de Ls na comutao da corrente

Como j falamos anteriormente, para qualquer tipo de retificador, nos

instantes que ocorre a transferncia de corrente de um par de diodos para outro,

caso exista alguma indutncia presente na conexo de entrada, esta transio no

pode ser instantnea.

Vamos inclu Ls finito no lado ac e uma corrente constante, Id no lado dc.

Nesta situao a comutao da corrente no ser instantnea. Observaremos

apenas um processo de comutao, por exemplo, do diodo D1 para o diodo D5. Os

outros processos so idnticos. Observe na figura 1.22 que no intervalo de interesse

a corrente atravs dos diodos D5 e D6. A figura 1.23 mostra uma simplificao do

circuito retificador para este intervalo de tempo analisado.

22

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

Id

P

va

a

vb

LS

b

vcn

n

D1

LS

LS

c

D5

ia

i a + i c = Id

ib=Id

Id

ic

D4

D6

N

Fig. 1.23 Processo de comutao de corrente

Antes da comutao a corrente flui por D5 e D6 (t= t0) como mostra a figura

1.24. Durante a comutao a corrente Id flui tambm por D1 tal que ia +ic = Id.

Durante a comutao a tenso no n P fica constante.

Quando a alimentao feita por meio de transformadores este fenmeno se

acentua, embora ocorra sempre, uma vez que as linhas de alimentao sempre

apresentam alguma caracterstica indutiva. Em tais situaes, que representam os

casos reais, durante alguns instantes esto em conduo simultnea o diodo que est

entrando em conduo e aquele que est sendo desligado. Isto significa, do ponto de

vista da rede, um curto-circuito aplicado aps as indutncias de entrada, Ls. A

tenso efetiva na entrada do retificador ser a mdia das tenses presentes nas fases.

Tal distoro tambm mostrada na figura 1.24, num circuito trifsico alimentando

carga indutiva. A soma das correntes pelas fases em comutao igual corrente

drenada pela carga.

Quando termina o intervalo de comutao, a tenso retorna sua forma

normal.

Exerccio: Para um sinal entre duas fases dado por 2VFF cos t, calcule o valor da

voltagem mdia na sada do retificador com o efeito de comutao finita.

23

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

* C:\Curso Graduacao\ee833\Simulao\exp1\efeitocomutacao.sch

Date/Time run: 08/09/105 18:08:41

Temperature: 27.0

(A) efeitocomutacao

80V

40V

0V

-40V

SEL>>

-80V

V(Lsc:2)

V(R2:1)

V(R1:1)

2.0A

Intervalo de interesse

1.0A

-0.0A

t=t0

-1.0A

0s

I(D1)

I(D5)

5ms

I(D6)

10ms

Time

A1:(8.997m,-28.64)

A2:(4.937m,-29.06)

DIFF(A):(4.060m,418.88m)

Date: August 09, 2005

Page 1

15ms

Time: 18:08:57

Fig. 1.24 Formas de onda indicando o fenmeno da comutao.

1.4.3 Voltagem constante no lado DC

Finalmente, vamos considerar o circuito mostrado na figura 1.25, onde

assumimos que o retificador alimenta uma fonte de tenso DC. (Esta uma

aproximao para o circuito com um grande capacitor C). Novamente, como no caso

monofsico, utilizamos a suposio que a corrente id fortemente descontnua.

24

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

id

P

vi

va

a

vb

LS

b

vcn

n

LS

c

D3

D1

LS

D5

ia

Vd

ib

ic

D6

D4

D2

N

Fig. 1.25 Retificador com Ls finito e voltagem constante

A figura 1.26 mostra as formas de onda para estas condies. Da analise desta

figura podemos conclui que quando a carga capacitiva, as indutncias de entrada

atuam no sentido de reduzir a derivada inicial da corrente. Neste caso, como a

corrente apresenta-se variando, as mesmas indutncias apresentaro uma queda de

tenso, de modo que a tenso vi mostra-se significativamente distorcida.

25

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

* C:\Curso Graduacao\ee833\Simulao\exp1\voltagemconst.sch

Date/Time run: 08/09/105 19:00:38

Temperature: 27.0

(A) voltagemconst

1.2A

0.8A

0.4A

0A

-0.4A

I(D1)

100V

50V

0V

SEL>>

-50V

0s

5ms

10ms

15ms

20ms

V(Lsc:2)

V(Lsa:2)

V(Lsb:2)

Time

Date: August 09, 2005

Page 1

25ms

30ms

V(vp,vn)

Time: 19:03:56

Fig.1.26 Forma de ondas do retificador com voltagem constante

26

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

1.5 Fator de Potncia

A atual regulamentao brasileira do fator de potncia [1.1] estabelece que o

mnimo fator de potncia (FP) das unidades consumidoras de 0,92, com o clculo

feito por mdia horria. O consumo de reativos alm do permitido (0,425 VArh por

cada Wh) cobrado do consumidor. No intervalo entre 6 e 24 horas isto ocorre se a

energia reativa absorvida for indutiva e das 0 s 6 horas, se for capacitiva.

Consideremos, para efeito das definies posteriores, o esquema da figura

1.27.

Ii

Equipamento

Vi

Fig. 1.27 Circuito genrico utilizado nas definies de FP

1.5.1 Definio de Fator de Potncia

Fator de potncia definido como a relao entre a potncia ativa e a

potncia aparente consumidas por um dispositivo ou equipamento,

independentemente das formas que as ondas de tenso e corrente apresentem.

1

v ( t ) ii ( t ) dt

P T i

FP = =

S

VRMS I RMS

(1.28)

Em um sistema com formas de onda senoidais, a equao anterior torna-se

igual ao cosseno da defasagem entre as ondas de tenso e de corrente:

FPsen o = cos

(1.29)

Quando apenas a tenso de entrada for senoidal, o FP expresso por:

27

EE 833 Eletrnica de Potncia

2005

FPV

sen o

I1

I RMS

FEEC - UNICAMP

cos 1

(1.30)

Neste caso, a potncia ativa de entrada dada pela mdia do produto da

tenso (senoidal) por todas as componentes harmnicas da corrente (no-senoidal).

Esta mdia nula para todas as harmnicas exceto para a fundamental, devendo-se

ponderar tal produto pelo cosseno da defasagem entre a tenso e a primeira

harmnica da corrente. Desta forma, o fator de potncia expresso como a relao

entre o valor RMS da componente fundamental da corrente e a corrente RMS de

entrada, multiplicado pelo cosseno da defasagem entre a tenso e a primeira

harmnica da corrente.

A relao entre as correntes chamada de fator de forma e o termo em

cosseno chamado de fator de deslocamento.

Por sua vez, o valor RMS da corrente de entrada tambm pode ser expresso

em funo das componentes harmnicas:

I RMS =

I +

2

1

I

n=2

2

n

(1.31)

Define-se a Taxa de Distoro Harmnica (TDH) como sendo a relao entre

o valor RMS das componentes harmnicas da corrente e a fundamental:

TDH

I 2n

n=2

(1.32)

I1

Assim, o FP pode ser rescrito como:

FP =

cos1

(1.33)

1 + TDH 2

evidente a relao entre o FP e a distoro da corrente absorvida da linha.

Neste sentido, existem normas internacionais que regulamentam os valores mximos

das harmnicas de corrente que um dispositivo ou equipamento pode injetar na linha

de alimentao.

Exerccio: Calcule o fator de potncia para um retificador monofsico para uma

28

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

carga altamente indutiva (id = constante =Id).

1.6 Normas IEC 61000-3-2: Distrbios causados por equipamento conectado

rede pblica de baixa tenso

Esta norma [1.2] refere-se s limitaes das harmnicas de corrente injetadas

na rede pblica de alimentao. Aplica-se a equipamentos eltricos e eletrnicos que

tenham uma corrente de entrada de at 16 A por fase, conectado a uma rede pblica

de baixa tenso alternada, de 50 ou 60 Hz, com tenso fase-neutro entre 220 e 240

V. Para tenses inferiores, os limites no foram ainda estabelecidos (2001).

Os equipamentos so classificados em 4 classes:

Classe A: Equipamentos com alimentao trifsica equilibrada, aparelhos eletrodomsticos (exeto os da classe D), equipamentos de udio, ferramentas

(exceto as portteis) e todos os demais no includos nas classes seguintes.

Inclui reguladores de intensidade (dimmer) para lmpadas incandescentes.

Classe B: Ferramentas portteis

Classe C: Dispositivos de iluminao, exceto para lmpada incandescente.

Classe D: Receptores de TV, computadores pessoais e monitores de vdeo para

computadores.

A Tabela I indica os valores mximos para as harmnicas de corrente

Tabela I: Limites para as Harmnicas de Corrente

29

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

Ordem da

Classe A

Harmnica

Mxima

n

corrente [A]

Harmnicas

mpares

3

2,30

5

1,14

7

0,77

9

0,40

11

0,33

13

0,21

15<n<39

2,25/n

Harmnicas

Pares

2

1,08

4

0,43

6

0,3

8<n<40

1,83/n

FP: fator de potncia

Classe B

Mxima

corrente[A]

Classe C

% da

fundamental

Classe D

(75W<P<600W)

[mA/W]

3,45

1,71

1,155

0,60

0,495

0,315

3,375/n

30.FP

10

7

5

3

3

3

3,4

1,9

1,0

0,5

0,35

0,296

3,85/n

1,62

0,645

0,45

2,76/n

1.6.1 Desvantagens do baixo fator de potncia (FP) e da

corrente

alta distoro da

Consideremos aqui aspectos relacionados com o estgio de entrada de fontes

de alimentao. As tomadas da rede eltrica domstica ou industrial possuem uma

corrente (RMS) mxima que pode ser absorvida (tipicamente 15A nas tomadas

domsticas).

A figura 1.28 mostra uma forma de onda tpica de um circuito retificador

alimentando um filtro capacitivo. Notem-se os picos de corrente e a distoro

provocada na tenso de entrada, devido impedncia da linha de alimentao. O

espectro da corrente mostra o elevado contedo harmnico, cujas harmnicas

excedem as especificaes da norma IEC 61000-3-2.

10A

1.0A

100mA

0

10mA

-

1.0mA

-

0Hz

30

0.2KHz

0.4KHz

0.6KHz

0.8KHz

1.0KHz

1.2KHz

1.4KHz 1.6KHz

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

(a)

(b)

Figura 1.28 (a) Corrente de entrada e tenso de alimentao de retificador

alimentando filtro capacitivo. (b) Espectro da corrente.

Consideremos os dados comparativos da tabela II [1.3]

Tabela II: COMPARAO DA POTNCIA ATIVA DE SADA

Convencional

Com correo de

FP

Potncia disponvel

1440 VA

1440 VA

Fator de potncia

0,65

0,99

Eficincia do corretor de fator de

100%

95%

potncia

Eficincia da fonte

75%

75%

Potncia disponvel

702 W

1015 W

Nota-se que o baixo fator de potncia da soluo convencional (filtro

capacitivo) o grande responsvel pela reduzida potncia ativa disponvel para a

carga alimentada.

Podem ser citadas como desvantagens de um baixo FP e elevada distoro os

seguintes fatos:

A mxima potncia ativa absorvvel da rede fortemente limitada pelo FP;

As harmnicas de corrente exigem um sobre-dimensionamento da instalao

eltrica e dos transformadores, alm de aumentar as perdas (efeito pelicular);

A componente de 3a harmnica da corrente, em sistema trifsico com neutro, pode

ser muito maior do que o normal;

O achatamento da onda de tenso, devido ao pico da corrente, alm da distoro

da forma de onda, pode causar mau-funcionamento de outros equipamentos

conectados mesma rede;

As componentes harmnicas podem excitar ressonncias no sistema de potncia,

levando a picos de tenso e de corrente, podendo danificar dispositivos

conectados linha.

1.1 Referncias Bibliogrficas

[1.1] Mauro Crestani, "Com uma terceira portaria, o novo fator de potncia j vale

em Abril". Eletricidade Moderna, Ano XXII, n 239, Fevereiro de 1994

[1.2] International Electrotechnical Comission: IEC 61000-3-2: Electromagnetic

Compatibility (EMC) Part 3: Limits Section 2: Limits for Harmonic

Current Emissions (Equipment input current < 16 A per phase), 1998 e

Emenda A14 (2001)

[1.3] J. Klein and M. K. Nalbant: Power Factor Correction - Incentives. Standards

and Techniques. PCIM, June 1990, pp. 26-31

31

EE 833 Eletrnica de Potncia

2005

FEEC - UNICAMP

[1.4] S. B. Dewan: Optimum Input and Output Filters for a Single-Phase Rectifier

Power Supply. IEEE Trans. On Industry Applications, vol. IA-17, no. 3,

May/June 1981

[1.5] A. R. Prasad, P. D. Ziogas and S. Manlas: A Novel Passive Waveshaping

Method for Single-Phase Diode Rectifier. Proc. Of IECON 90, pp. 10411050

[1.6] R. Gohr Jr. and A. J. Perin: Three-Phase Rectifier Filters Analysis. Proc. Of

Brazilian Power Electronics Conference, COBEP 91,Florianpolis - SC, pp.

281-286.

[1.7] I. Suga, M. Kimata, Y. Ohnishi and R. Uchida: New Switching Method for

Single-phase AC to DC converter. IEEE PCC 93, Yokohama, Japan, 1993.

[1.8] B. Mammano and L. Dixon: Choose the Optimum Topology for High Power

Factor Supplies. PCIM, March 1991, pp. 8-18.

32

Você também pode gostar

- Fonte de AlimentaçãoDocumento7 páginasFonte de AlimentaçãoArlindo CNAinda não há avaliações

- Circuitos CeifadoresDocumento11 páginasCircuitos Ceifadoreseddietech100% (1)

- Projeto Fonte Alimentação 10V 30mA Diodo ZenerDocumento6 páginasProjeto Fonte Alimentação 10V 30mA Diodo ZenerMarcos ViníciusAinda não há avaliações

- Exercícios Resolvidos Sobre Conversores CC-CC 2Documento18 páginasExercícios Resolvidos Sobre Conversores CC-CC 2Cesar Jr100% (1)

- Amplificadores transistorizados EC, CC e BCDocumento10 páginasAmplificadores transistorizados EC, CC e BCzuiterionAinda não há avaliações

- O que você precisa saber sobre osciladores eletrônicosDocumento4 páginasO que você precisa saber sobre osciladores eletrônicosAntonio OtavianoAinda não há avaliações

- Introdução à Indutância e suas AplicaçõesDocumento9 páginasIntrodução à Indutância e suas AplicaçõesLucas Matos MunizAinda não há avaliações

- Engenharia elétrica: introdução à emissão termoiônica e válvulas eletrônicasDocumento12 páginasEngenharia elétrica: introdução à emissão termoiônica e válvulas eletrônicasgenivaldo de souza quirinoAinda não há avaliações

- História e funcionamento dos transistoresDocumento17 páginasHistória e funcionamento dos transistoresDarilWAinda não há avaliações

- Transistor - Componente EletrônicoDocumento58 páginasTransistor - Componente EletrônicoZelensky Ukranian VolodimirAinda não há avaliações

- 3.a Aula - ACIJ6 - Eletronica de PotenciaDocumento56 páginas3.a Aula - ACIJ6 - Eletronica de PotenciaFrancisco SantosAinda não há avaliações

- Fonte de AlimentaçãoDocumento3 páginasFonte de Alimentaçãomarcof91Ainda não há avaliações

- Apostila - Eletronica IndustrialDocumento38 páginasApostila - Eletronica IndustrialSandro Hermes100% (1)

- Eletrônica de Potência Combina Potência, Eletrônica e ControleDocumento32 páginasEletrônica de Potência Combina Potência, Eletrônica e ControleLaís OliveiraAinda não há avaliações

- Curvas características de transístoresDocumento6 páginasCurvas características de transístoresVasco Joaquim MhulaAinda não há avaliações

- Eletrônica de Potência - Transistores BJT, FET e IGBTDocumento4 páginasEletrônica de Potência - Transistores BJT, FET e IGBTAkaridAinda não há avaliações

- Fonte ATX modificada para 13,8VDocumento3 páginasFonte ATX modificada para 13,8Vdalima1416Ainda não há avaliações

- SCR: O tiristor mais comumDocumento23 páginasSCR: O tiristor mais comumValdemarDevesa100% (1)

- Circuitos com capacitores e indutoresDocumento60 páginasCircuitos com capacitores e indutoresWagner RibeiroAinda não há avaliações

- Fontes de Alta TensaoDocumento5 páginasFontes de Alta TensaoSamuel TarsiAinda não há avaliações

- Amplificador PUSH PULL Classe BDocumento14 páginasAmplificador PUSH PULL Classe BDaniel ChavierAinda não há avaliações

- Transistor como chave e fonte de correnteDocumento5 páginasTransistor como chave e fonte de correnteCleber OtavianoAinda não há avaliações

- Chaves de Potência - IGBT, MOSFET e ParâmetrosDocumento27 páginasChaves de Potência - IGBT, MOSFET e ParâmetrosKiranoasAinda não há avaliações

- Relatório 2Documento28 páginasRelatório 2Rafael RinconAinda não há avaliações

- Transistores Bipolares: Funcionamento e CaracterísticasDocumento13 páginasTransistores Bipolares: Funcionamento e Característicasrslima2007Ainda não há avaliações

- Tensão Alternada 2Documento9 páginasTensão Alternada 2Pedro Nava100% (1)

- Gradadores monofásicosDocumento11 páginasGradadores monofásicosrockgilAinda não há avaliações

- 14 - Disp Eletrônico - IfBA - Transistor - Polarização FETDocumento46 páginas14 - Disp Eletrônico - IfBA - Transistor - Polarização FETBianca FariasAinda não há avaliações

- Transformadores monofásicos e trifásicosDocumento42 páginasTransformadores monofásicos e trifásicosErik SouzaAinda não há avaliações

- Amplificadores Operacionais Fundamentos e Aplicacoes Gruiter Parte 1Documento8 páginasAmplificadores Operacionais Fundamentos e Aplicacoes Gruiter Parte 1Márcio De Freitas CarneiroAinda não há avaliações

- Cabral e Toledo - Interruptor Eletronico Controlado Por Palmas - 2010Documento66 páginasCabral e Toledo - Interruptor Eletronico Controlado Por Palmas - 2010pedro_cabral_br100% (2)

- Retificadores Trifásicos ControladosDocumento35 páginasRetificadores Trifásicos ControladosLorrane Ribeiro100% (1)

- Lronetto - Eng Forno InduçãoDocumento7 páginasLronetto - Eng Forno InduçãoDantes Alves de SantanaAinda não há avaliações

- Introdução aos TransistoresDocumento79 páginasIntrodução aos TransistoresDaniel Bello BoaventuraAinda não há avaliações

- Apostila de Bobinagem Motor Trifasico ImbricadoDocumento12 páginasApostila de Bobinagem Motor Trifasico ImbricadoCarlos PinheiroAinda não há avaliações

- ListaGradadoresIvo PDFDocumento3 páginasListaGradadoresIvo PDFrodrigoshallerAinda não há avaliações

- Amplificador Darlington Newton Braga MultisimDocumento22 páginasAmplificador Darlington Newton Braga MultisimRoldao AlmeidaAinda não há avaliações

- Definição e uso do PWMDocumento3 páginasDefinição e uso do PWMmojuja67% (3)

- Slides de Eletrônica: Osciladores LC e Cristais de QuartzoDocumento67 páginasSlides de Eletrônica: Osciladores LC e Cristais de QuartzoOtavioAinda não há avaliações

- Regulador de TensãoDocumento5 páginasRegulador de Tensãoanon-49968100% (1)

- Retificação Relatório EletrônicaDocumento30 páginasRetificação Relatório EletrônicaLuciano Santos '-'Ainda não há avaliações

- Transformadores e fator de potência: entenda o que é e como corrigirDocumento10 páginasTransformadores e fator de potência: entenda o que é e como corrigircsorgoAinda não há avaliações

- Sistema de Transporte de Energia em CC e CADocumento16 páginasSistema de Transporte de Energia em CC e CAFrancisco Ivan SitoeAinda não há avaliações

- Apostila de TransistorDocumento50 páginasApostila de Transistorez-criogenics2445100% (1)

- Regulação de tensão com diodo ZenerDocumento14 páginasRegulação de tensão com diodo ZenerlandroaugustoAinda não há avaliações

- Atualizado 300W Subwoofer AmplificadorDocumento24 páginasAtualizado 300W Subwoofer AmplificadorRobmixAinda não há avaliações

- Aplicação do CI CD4046 como PLL e Modulador/Demodulador FMDocumento11 páginasAplicação do CI CD4046 como PLL e Modulador/Demodulador FMVictor PazAinda não há avaliações

- 2.a Aula N5CV1 Transformadores MonofásicosDocumento29 páginas2.a Aula N5CV1 Transformadores MonofásicosricardoAinda não há avaliações

- Amplificadores operacionais como osciladoresDocumento13 páginasAmplificadores operacionais como osciladoresEloi Luiz Giacobbo Filho100% (1)

- Circ RettifDocumento23 páginasCirc RettifDigeo MachadoAinda não há avaliações

- Apostila de Amplificador Operacional - Unifei - ELTA00Documento42 páginasApostila de Amplificador Operacional - Unifei - ELTA00kmi70Ainda não há avaliações

- Circuito RLC série: respostas ao degrau e ressonânciaDocumento3 páginasCircuito RLC série: respostas ao degrau e ressonânciasergiolec2k8Ainda não há avaliações

- Prática 3 FluidosDocumento5 páginasPrática 3 FluidosEduardo AlbuquerqueAinda não há avaliações

- Introdução aos Retificadores MonofásicosDocumento32 páginasIntrodução aos Retificadores MonofásicosEduardo AlbuquerqueAinda não há avaliações

- Plano de Manutenção Preventiva ModeloDocumento3 páginasPlano de Manutenção Preventiva ModeloEduardo AlbuquerqueAinda não há avaliações

- APOSTILA Nocoes de Higiene Ocupacional e Seguranca Do TrabalhoDocumento141 páginasAPOSTILA Nocoes de Higiene Ocupacional e Seguranca Do TrabalhoLeandro RibeiroAinda não há avaliações

- O LivroDocumento216 páginasO LivroEduardo AlbuquerqueAinda não há avaliações

- Medidas de Controle2014Documento27 páginasMedidas de Controle2014Eduardo AlbuquerqueAinda não há avaliações

- Medidas de Controle2014Documento27 páginasMedidas de Controle2014Eduardo AlbuquerqueAinda não há avaliações

- Planilha Preventiva Das Pc'sDocumento2 páginasPlanilha Preventiva Das Pc'sEduardo AlbuquerqueAinda não há avaliações

- Código de Etica PsicopedagogiaDocumento8 páginasCódigo de Etica PsicopedagogiaEduardo AlbuquerqueAinda não há avaliações

- Hidraulica - BoschDocumento43 páginasHidraulica - BoschPaulo LaraAinda não há avaliações

- PosDocumento1 páginaPosEduardo AlbuquerqueAinda não há avaliações

- Microcontroladores 2 Exercicios Macro e Microarquitetura v2Documento4 páginasMicrocontroladores 2 Exercicios Macro e Microarquitetura v2Marcelo LimaAinda não há avaliações

- Cap.05 Gerência Local v12Documento94 páginasCap.05 Gerência Local v12Alex BrinnerAinda não há avaliações

- Cálculo Da Probabilidade em Eventos AleatóriosDocumento6 páginasCálculo Da Probabilidade em Eventos AleatóriossergioloisAinda não há avaliações

- Sistema de Administração de Concursos DSEADocumento1 páginaSistema de Administração de Concursos DSEAnantesAinda não há avaliações

- Ficha 4 ExcelDocumento2 páginasFicha 4 ExcelBiaRosad0Ainda não há avaliações

- AP2 - Atividade Teórica de Aprendizagem 02 - 2022A - Fundamentos de Marketing (57725)Documento3 páginasAP2 - Atividade Teórica de Aprendizagem 02 - 2022A - Fundamentos de Marketing (57725)Hugo EstevesAinda não há avaliações

- Opm-ombr-oem-18-0037-Edbr - Gom Mobile para Inspeções Via TabletDocumento44 páginasOpm-ombr-oem-18-0037-Edbr - Gom Mobile para Inspeções Via TabletIvanildo pereiraAinda não há avaliações

- Implantação de Sistema de Gerenciamento de Parque AquaticoDocumento25 páginasImplantação de Sistema de Gerenciamento de Parque AquaticoAcademicosTIAinda não há avaliações

- Relatório de Autoavaliação Institucional da Faculdade de Tecnologia ENIAC - FAPI 2014Documento124 páginasRelatório de Autoavaliação Institucional da Faculdade de Tecnologia ENIAC - FAPI 2014Claudio SantosAinda não há avaliações

- Information Security Training by JoasDocumento1.720 páginasInformation Security Training by JoasJose Gustavo100% (2)

- COM BT Gestao de Compras Publicas BR TDMLOKDocumento98 páginasCOM BT Gestao de Compras Publicas BR TDMLOKAnderson MachadoAinda não há avaliações

- 05 - The Torid AffairDocumento204 páginas05 - The Torid AffairJadna Rodrigues100% (1)

- NR 01 - OrDEM SERVIÇO Chefe - de - EquipaDocumento1 páginaNR 01 - OrDEM SERVIÇO Chefe - de - EquipaCPSSTAinda não há avaliações

- Fornecimento em tensão secundáriaDocumento113 páginasFornecimento em tensão secundáriaDiogo Feltrin100% (1)

- Falhas FH4 FCIOMDocumento5 páginasFalhas FH4 FCIOMVINI100% (6)

- Aula 3 Arquiteturas Microcontroladores e Microprocessadores PDFDocumento24 páginasAula 3 Arquiteturas Microcontroladores e Microprocessadores PDFAllas JonyAinda não há avaliações

- Tabela Handytech - Ssa e Ios Quinta Feira 31 05Documento50 páginasTabela Handytech - Ssa e Ios Quinta Feira 31 05Danilo Costa RamalhoAinda não há avaliações

- Lista de Segurança Da Informação IIDocumento9 páginasLista de Segurança Da Informação IIKaneda ShotaroAinda não há avaliações

- Fechamento de Motor ElétricoDocumento5 páginasFechamento de Motor ElétricoGuilherme DombroskiAinda não há avaliações

- Livro Automacao 2 EdDocumento18 páginasLivro Automacao 2 EdAtila DavidAinda não há avaliações

- Grafos Planares e a Fórmula de EulerDocumento3 páginasGrafos Planares e a Fórmula de EulerJoão A. de SanctisAinda não há avaliações

- NGN Voice Study: History, Design & PolicyDocumento149 páginasNGN Voice Study: History, Design & PolicyYuyun ManiezAinda não há avaliações

- BIOCON READER 300 - Manual de OperaçõesDocumento33 páginasBIOCON READER 300 - Manual de Operaçõeshebertrocha76Ainda não há avaliações

- Arduino Básico - Conceitos e aplicações do microcontrolador ATmegaDocumento42 páginasArduino Básico - Conceitos e aplicações do microcontrolador ATmegaMozart ÁvilaAinda não há avaliações

- Acessando e configurando OLT IntelbrasDocumento19 páginasAcessando e configurando OLT IntelbrasJilvan jilAinda não há avaliações

- Ana Valecia Ribeiro e Cyrille BrissotDocumento15 páginasAna Valecia Ribeiro e Cyrille BrissotNaldogbiAinda não há avaliações

- A Tic Tecnologia Da Informacao e Comunicacao Na EducacaoDocumento32 páginasA Tic Tecnologia Da Informacao e Comunicacao Na EducacaoEnio LucioAinda não há avaliações

- Instalação do painel J3P em elevadores Selectron ACDocumento3 páginasInstalação do painel J3P em elevadores Selectron ACAlexandre JorgeAinda não há avaliações

- Excel Básico MÓDULO 1Documento37 páginasExcel Básico MÓDULO 1abdhuljafarAinda não há avaliações

- APQ ISO20000-1 2018-Webinar v.1.2 Final PDFDocumento16 páginasAPQ ISO20000-1 2018-Webinar v.1.2 Final PDFVanildo SouzaAinda não há avaliações