Escolar Documentos

Profissional Documentos

Cultura Documentos

Temario de Diseño Logico

Enviado por

Stephany BradburyDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Temario de Diseño Logico

Enviado por

Stephany BradburyDireitos autorais:

Formatos disponíveis

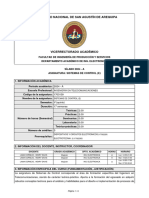

LABORATORIO DE DISEO LGICO

CLAVE:

GRUPO:

TRIMESTRE:

PROFESOR:

1121040

CEL-82

14-I

FRANCISCO JAVIER SNCHEZ RANGEL

Cubculo:

G-301: cubculo 3

e-mail:

fjsr@correo.azc.uam.mx

HORARIO DE ASESORAS:

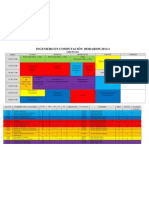

HORARIO

10:00-11:30

11:30-13:00

13:00-14:30

14:30-16:00

16:00-17:30

LUNES

ASESORA

MARTES

ASESORA

MIRCOLES

JUEVES

ASESORA

VIERNES

ASESORA

ASESORA

ASESORA

ASESORA

ASESORA

ASESORA

ASESORA

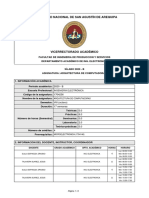

PRCTICAS.

PRCTICA NO. 0: CONCEPTOS BSICOS DE SISTEMAS DIGITALES

PRCTICA NO. 1: CARACTERIZACIN DE COMPUERTAS

PRCTICA NO. 2: ANLISIS DE CIRCUITOS COMBINATORIOS

PRCTICA NO. 3: DISEO DE CIRCUITOS COMBINATORIOS

PRCTICA NO. 4: DISEO DE CIRCUITOS COMBINATORIOS CON COMPUERTAS UNIVERSALES

PRCTICA NO. 5: DISEO DE CIRCUITOS ARITMTICOS

PRCTICA NO. 6: CARACTERIZACIN Y USO DE BLOQUES COMBINATORIOS

PRCTICA NO. 7: CARACTERIZACION DE FLIP FLOPS

PRCTICA NO. 8: CONTADORES

PRCTICA NO. 9: REGISTROS

PRCTICA NO. 10: MQUNAS DE ESTADO ALGORTMICAS.

EVALUACIN.

REPORTES DE LAS PRCTICAS:

PARTICIPACIN:

PUNTUALIDAD Y ASISTENCIA:

40%

50%

10%

REPORTES.

Se entregan una semana despus de haber terminado la prctica.

Por cada da hbil de retraso se calificar con 10%.

Despus de cuatro das hbiles de retraso no se reciben reportes.

El formato del reporte es el siguiente:

o Cartula:

Universidad Autnoma Metropolitana Azcapotzalco.

Divisin de C.B.I.

Departamento de Electrnica

Laboratorio de Diseo Lgico I.

Nmero de la prctica.

T.1

Nombre de la prctica.

Nmero de equipo.

Nombre y matricula de los integrantes del equipo.

Nombre de los profesores.

Grupo.

Trimestre.

Fecha de entrega.

o Objetivos.

o Introduccin Terica.

o Desarrollo Terico.

o Material y Equipo.

o Desarrollo Experimental

o Bibliografa y/o paginas www.

o Conclusiones.

El reporte es por equipos, a excepcin de las conclusiones.

Las conclusiones son individuales y obligatorias.

Quien no entregue conclusiones, tiene cero en el reporte.

PARTICIPACIN.

Todos los integrantes del equipo participaran en el desarrollo de las prcticas.

Se debern presentar al laboratorio con el material completo.

Se debern presentar al laboratorio con Desarrollo Terico realizado.

No podrn retirarse del laboratorio antes de la hora de salida sin haber concluido la prctica.

Se revisaran los circuitos funcionando correctamente.

PUNTUALIDAD Y ASISTENCIA.

Se pasar lista a las 13:15 hrs.

Por cada 5 minutos tarde se bajar -1% de la calificacin.

El lmite para llegar tarde es a las 14:00 hrs.

Por cada falta injustificada, tendrn cero en la sesin.

A la tercera falta injustificada tendrn NA en el curso.

ESCALA DE CALIFICACIONES.

90 >

75 >

MB

B

S

NA

90

75

60

< 60

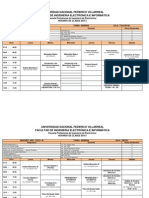

BIBLIOGRAFA.

MANO, KIME; FUNDAMENTOS DE DISEO LGICO Y DE COMPUTADORAS; 3 EDICIN;

ED. PEARSON2005.

TOCCI, WIDMER, MOSS; SISTEMAS DIGITALES: PRINCIPIOS Y APLICACIONES; 10

EDICIN; ED. PEARSON 2007.

VRANESIC, BROWN; FUNDAMENTOS DE LGICA DIGITAL CON DISEO VHDL; ED.

MCGRAW-HILL 2006.

T.2

MAXINEZ, ALCAL; VHDL: EL ARTE DE PROGRAMAR SISTEMAS DIGITALES, ED. CECSA

2010.

SCHNADOWER; FUNDAMENTOS DE DISEO DIGITAL Y MODELADO VHDL; UAM 2013.

SCHNADOWER; FUNDAMENTOS DE DISEO DIGITAL Y VHDL; UAM 2013.

SCHNADOWER; VHDL: MODELADO Y SNTESIS DE CIRCUITOS DIGITALES; UAM 2012.

SNCHEZ RANGEL; INSTRUCTIVO PARA EL USO DEL PROGRAMA XILINX ISE DESIGN

SUITE 12.1; UAM 2013.

DIGILENT INC.; NEXYS3 BOARD REFERENCE MANUAL, REVISION: DECEMBER 28, 2011.

DIGILENT INC.; NEXYS4 FPGA BOARD REFERENCE MANUAL, NEXYS4 REV. B; REVISED

SEPTEMBER 6, 2013.

SCHNADOWER; DISEO Y APLICACIONES DE CONTROLADORES CON VHDL; UAM 2010.

CONSULTAS EN INTERNET LOS MANUALES Y LAS DATASHEET DE LOS CIRCUITOS A

UTILIZAR.

TTL DATABOOK.

T.3

Você também pode gostar

- NRC Unidad IngenieriaDocumento15 páginasNRC Unidad Ingenieriabrayansma93Ainda não há avaliações

- Diagnostico en Redes Can BusDocumento2 páginasDiagnostico en Redes Can BusAnonymous SystemAinda não há avaliações

- Computacion 2012 1Documento7 páginasComputacion 2012 1PaIacios G GPalaciosAinda não há avaliações

- Marcelino Martinez@uv EsDocumento4 páginasMarcelino Martinez@uv EsJHonJorgeWilsonTapiaAlmanzaAinda não há avaliações

- OGATA-Sistemas de Control en Tiempo Discreto-Katsuhiko OgataDocumento757 páginasOGATA-Sistemas de Control en Tiempo Discreto-Katsuhiko Ogatagillomate100% (10)

- CONTENIDO A. de E. III (EBC) CIV 931 2024Documento4 páginasCONTENIDO A. de E. III (EBC) CIV 931 2024erwin leonel soliz rodriguezAinda não há avaliações

- Sistemas de Control en Tiempo Discreto - OgataDocumento757 páginasSistemas de Control en Tiempo Discreto - OgataCarmen Giuliana Prado Barrios100% (23)

- Horarios ESIS - 2012-I - OriginalDocumento18 páginasHorarios ESIS - 2012-I - OriginalMario Gauna ChinoAinda não há avaliações

- Horario - Pool 2Documento2 páginasHorario - Pool 2Claudio Pool Jovanhy Corcuera ParedesAinda não há avaliações

- 02-09-2021 - Programacion Del Seminario de Prsentacion de Avances de Protocolos de Investigacion 02-09-2021Documento4 páginas02-09-2021 - Programacion Del Seminario de Prsentacion de Avances de Protocolos de Investigacion 02-09-2021Alejandro Guerrero LeónAinda não há avaliações

- SILABO-1703139-SISTEMAS DE CONTROL (E) (2024-A) Ing. Henry Davis Lama CornejoDocumento6 páginasSILABO-1703139-SISTEMAS DE CONTROL (E) (2024-A) Ing. Henry Davis Lama CornejoGONZALO RAUL TICONA GRANADOSAinda não há avaliações

- Análisis de Requerimientos de InformaciónDocumento18 páginasAnálisis de Requerimientos de InformaciónAlex Edgar VpmAinda não há avaliações

- Actividad t3-03 Modelo de RequisitosDocumento9 páginasActividad t3-03 Modelo de RequisitosRichar GomezAinda não há avaliações

- Diario MetacognitivoDocumento65 páginasDiario MetacognitivoKarla Romero PonceAinda não há avaliações

- SILABODocumento6 páginasSILABOAlvaro LCAinda não há avaliações

- Temario MNCTG02Documento3 páginasTemario MNCTG02CRISTIAN ALEXIS MARTINEZ ZACARIASAinda não há avaliações

- Curriculum Vitae - Antony4Documento7 páginasCurriculum Vitae - Antony4TonyPsAinda não há avaliações

- Silabo de Proyecto de Redes UNUDocumento6 páginasSilabo de Proyecto de Redes UNURaul Romani FloresAinda não há avaliações

- TRABAJO TERMINADO Auditoria de SistemasDocumento74 páginasTRABAJO TERMINADO Auditoria de SistemasLuisito SegoviaAinda não há avaliações

- Silabo-Informática Básica (2020)Documento4 páginasSilabo-Informática Básica (2020)Ana TolkienAinda não há avaliações

- IF3001 Algoritmos y Estructuras de Datos - I-19 (2791) PDFDocumento10 páginasIF3001 Algoritmos y Estructuras de Datos - I-19 (2791) PDFJosealberto HernandezAinda não há avaliações

- Temas de ExposiciónDocumento3 páginasTemas de ExposicióngonloqAinda não há avaliações

- Diario MetacognitivoDocumento48 páginasDiario MetacognitivokarliuxintiAinda não há avaliações

- Brochure Matlab Básico - Intermedio 04 de JulioDocumento18 páginasBrochure Matlab Básico - Intermedio 04 de JulioCarlos AlmanzaAinda não há avaliações

- CURRICULUM 2017 TODO - Opt PDFDocumento27 páginasCURRICULUM 2017 TODO - Opt PDFCarlos TicoAinda não há avaliações

- Cronograma de Actividades Diplomado Auditoria MedicaDocumento4 páginasCronograma de Actividades Diplomado Auditoria MedicaAnonymous e4S3hqHnAinda não há avaliações

- Programa AnalíticoDocumento4 páginasPrograma AnalíticoJulián AriasAinda não há avaliações

- TALLERDocumento52 páginasTALLERGacitua Matos GeraldAinda não há avaliações

- Sistema de Deteccion de Huella Digital Luis Eduardo Moran LopezDocumento0 páginaSistema de Deteccion de Huella Digital Luis Eduardo Moran LopezLeo GonzalezAinda não há avaliações

- LdePdeA-01a Presentacion 2022Documento27 páginasLdePdeA-01a Presentacion 2022yohan6ludwig6vidal6sAinda não há avaliações

- Contenido Control de Procesos 2019-IIDocumento3 páginasContenido Control de Procesos 2019-IITania RodriguezAinda não há avaliações

- Oscar Gonzalo Apaza Perez - Curriculum FDocumento3 páginasOscar Gonzalo Apaza Perez - Curriculum FOscar Oscar GonzaloAinda não há avaliações

- Horario Examen FinalDocumento3 páginasHorario Examen FinalsadimitaAinda não há avaliações

- M.A. Sensores y Acondicionamiento de Se AlesDocumento36 páginasM.A. Sensores y Acondicionamiento de Se AlesRafael Villegas MetelinAinda não há avaliações

- Brochure Matlab Básico - Intermedio 210328Documento19 páginasBrochure Matlab Básico - Intermedio 210328Wilo GuamanAinda não há avaliações

- Silabo-Instrumentacion y Automatizacion (2020-A)Documento5 páginasSilabo-Instrumentacion y Automatizacion (2020-A)Carlos AlvaAinda não há avaliações

- 3erapractica PDFDocumento12 páginas3erapractica PDFJorge Matta CanalesAinda não há avaliações

- Redes de ComputadorasDocumento4 páginasRedes de ComputadorasRodrigo OlivaAinda não há avaliações

- Horario DesfaseDocumento14 páginasHorario DesfaseIvan CondoriAinda não há avaliações

- Flores - MM - Tramie DocumentarioDocumento109 páginasFlores - MM - Tramie Documentariodvmvnt1noAinda não há avaliações

- Instalaciones ElectricasDocumento3 páginasInstalaciones ElectricasMilton CopañaAinda não há avaliações

- MFYEDocumento13 páginasMFYEDaniel GamezAinda não há avaliações

- PROGRAMA PROGRAMACION COMERCIAL (667) ING. HERMAN VELIZ SECCION 2dosem2016Documento3 páginasPROGRAMA PROGRAMACION COMERCIAL (667) ING. HERMAN VELIZ SECCION 2dosem2016JEFFERSON ANTONIO OLIVA ORTEGAAinda não há avaliações

- Análisis de Sistema - Sistema 'Gestión de Notas' PDFDocumento25 páginasAnálisis de Sistema - Sistema 'Gestión de Notas' PDFLAinda não há avaliações

- Caso de Estudio - Espina de PescadoDocumento3 páginasCaso de Estudio - Espina de PescadoCristian TabaresAinda não há avaliações

- Ingenieria Electronica UNFV FIEI Horario 2015 1Documento5 páginasIngenieria Electronica UNFV FIEI Horario 2015 1Juan Gabriel LinaresAinda não há avaliações

- El algoritmo de sintonización simple de controladores difusos: (ASSCD)No EverandEl algoritmo de sintonización simple de controladores difusos: (ASSCD)Ainda não há avaliações

- Reingeniería De Procesos De Manufactura Industrial: Colaboración Entre Cuerpos Académicos Tlaxcala Y Puebla (Enero 2021)No EverandReingeniería De Procesos De Manufactura Industrial: Colaboración Entre Cuerpos Académicos Tlaxcala Y Puebla (Enero 2021)Nota: 5 de 5 estrelas5/5 (2)

- Investigación de Operaciones I: Programación linealNo EverandInvestigación de Operaciones I: Programación linealAinda não há avaliações

- Sistema de telemedicina basado en una arquitectura orientada a servicios y aplicado a la rehabilitación físicaNo EverandSistema de telemedicina basado en una arquitectura orientada a servicios y aplicado a la rehabilitación físicaAinda não há avaliações

- Análisis de estructuras - métodos clásico y matricial - 4a ed.No EverandAnálisis de estructuras - métodos clásico y matricial - 4a ed.Nota: 5 de 5 estrelas5/5 (4)

- Enfoque práctico de la teoría de robots: Con aplicaciones en MatlabNo EverandEnfoque práctico de la teoría de robots: Con aplicaciones en MatlabNota: 5 de 5 estrelas5/5 (2)

- Curso de programación orientada a objetos en C# .NET: Ejemplos con aplicacines visualez y de consolaNo EverandCurso de programación orientada a objetos en C# .NET: Ejemplos con aplicacines visualez y de consolaAinda não há avaliações

- Mecatrónica - sistemas de control electrónico en la ingeniería mecánica y eléctricaNo EverandMecatrónica - sistemas de control electrónico en la ingeniería mecánica y eléctricaNota: 5 de 5 estrelas5/5 (3)

- Ea U3 PaacDocumento4 páginasEa U3 PaacStephany BradburyAinda não há avaliações

- Actividad 4Documento1 páginaActividad 4Stephany BradburyAinda não há avaliações

- Ciencias de La Salud Cuatro Proteinas PDFDocumento6 páginasCiencias de La Salud Cuatro Proteinas PDFmasternet3000Ainda não há avaliações

- Glosario de Ciencias Sociales PDFDocumento10 páginasGlosario de Ciencias Sociales PDFMario Seb ChoAinda não há avaliações

- Ambient eDocumento9 páginasAmbient eWilmer David Quispe HaroAinda não há avaliações

- Tdsu U1 A3 RorfDocumento4 páginasTdsu U1 A3 RorfStephany BradburyAinda não há avaliações

- AlmacenamientoDocumento20 páginasAlmacenamientoStephany BradburyAinda não há avaliações

- Deor U1 A3 FeggDocumento5 páginasDeor U1 A3 FeggFelipe GutierrezAinda não há avaliações

- Midiendo La Diversidad JOMGDocumento2 páginasMidiendo La Diversidad JOMGStephany BradburyAinda não há avaliações

- Fórmulas de Cinemática y DinámicaDocumento3 páginasFórmulas de Cinemática y DinámicaStephany BradburyAinda não há avaliações

- El Foda de Tu AplicaciónDocumento2 páginasEl Foda de Tu AplicaciónStephany BradburyAinda não há avaliações

- Ejercicios Nodos y MallasDocumento1 páginaEjercicios Nodos y MallasStephany BradburyAinda não há avaliações

- Guia TermoDocumento31 páginasGuia TermoStephany BradburyAinda não há avaliações

- Programación EstructuradaDocumento31 páginasProgramación EstructuradaStephany BradburyAinda não há avaliações

- Pe 06 ProcesoTraduccion ImpDocumento39 páginasPe 06 ProcesoTraduccion ImpStephany BradburyAinda não há avaliações

- Programación EstructuradaDocumento21 páginasProgramación EstructuradaStephany BradburyAinda não há avaliações

- Programación EstructuradaDocumento34 páginasProgramación EstructuradaStephany BradburyAinda não há avaliações

- ArchivosDocumento30 páginasArchivosStephany BradburyAinda não há avaliações

- ProgramacionDocumento30 páginasProgramacionStephany BradburyAinda não há avaliações

- ProgramacionDocumento22 páginasProgramacionStephany BradburyAinda não há avaliações

- EstructuradoDocumento36 páginasEstructuradoStephany BradburyAinda não há avaliações

- ProgramacionDocumento30 páginasProgramacionStephany BradburyAinda não há avaliações

- Calendario ActividadesDocumento11 páginasCalendario ActividadesStephany BradburyAinda não há avaliações

- Programación EstructuradaDocumento34 páginasProgramación EstructuradaStephany BradburyAinda não há avaliações

- ArreglosDocumento15 páginasArreglosStephany BradburyAinda não há avaliações

- Prob 3Documento6 páginasProb 3Bladimir Guevara MinayaAinda não há avaliações

- Transforacion de FuentesDocumento1 páginaTransforacion de FuentesStephany BradburyAinda não há avaliações

- 1.1 Algunos Tipos de NúmerosDocumento5 páginas1.1 Algunos Tipos de NúmerosJosé Emilio Román de AndaAinda não há avaliações

- MagnetismoDocumento5 páginasMagnetismoMarlyu GuzmanAinda não há avaliações

- Imp Euler Mejor A DoDocumento15 páginasImp Euler Mejor A DoStephany BradburyAinda não há avaliações

- Procedimiento Recomendado para La Calibración de Termómetros en El Laboratorio ClínicoDocumento4 páginasProcedimiento Recomendado para La Calibración de Termómetros en El Laboratorio ClínicoLorena Ek MaciasAinda não há avaliações

- Datasheet DW 310p EspDocumento6 páginasDatasheet DW 310p EspDano DabuferixAinda não há avaliações

- Ios27000 y Derivadas Mapa Conceptual - Daniel HidalgoDocumento4 páginasIos27000 y Derivadas Mapa Conceptual - Daniel HidalgoDaniel Israel Hidalgo RuedaAinda não há avaliações

- Proyecto Cobertura CajamarcaDocumento25 páginasProyecto Cobertura CajamarcaJosé Mundaca RodríguezAinda não há avaliações

- Manual de Comisionamiento V3 TDP ProjectDocumento26 páginasManual de Comisionamiento V3 TDP ProjectJosephAinda não há avaliações

- Listado de Precios 2015Documento36 páginasListado de Precios 2015Dennis Vides AbregoAinda não há avaliações

- La Importancia de Implementar Una Norma Voluntaria - Iso 14001 en Una Empresa de Interventoria de Obras CivilesDocumento13 páginasLa Importancia de Implementar Una Norma Voluntaria - Iso 14001 en Una Empresa de Interventoria de Obras CivilesFresia M IngaAinda não há avaliações

- Manual Usuario Logiq S8Documento1.545 páginasManual Usuario Logiq S8javier govantes100% (1)

- Poster CientificoDocumento8 páginasPoster CientificoVictor GonzalezAinda não há avaliações

- MPM-GPR-20CC044-1000-XXXX (Montaje y Desmontaje Valvulas ) OK CALIDADDocumento36 páginasMPM-GPR-20CC044-1000-XXXX (Montaje y Desmontaje Valvulas ) OK CALIDADMarck KollAinda não há avaliações

- Diplomado Sistemas de Gestion de Calidad NTC Iso 9001:2015 - 112 HorasDocumento14 páginasDiplomado Sistemas de Gestion de Calidad NTC Iso 9001:2015 - 112 Horasangie santanaAinda não há avaliações

- Terminología Identificación VehicularDocumento13 páginasTerminología Identificación Vehicularrichard01p50% (2)

- Audiometro - Silbmed - Sibelsound 400 - Manual de ServicioDocumento90 páginasAudiometro - Silbmed - Sibelsound 400 - Manual de ServicioSoporte BiomedicoAinda não há avaliações

- Taller 1 - Iso - 14001 - 2015Documento9 páginasTaller 1 - Iso - 14001 - 2015cesar augusto gomez lopezAinda não há avaliações

- Manual Sistema de TicketsDocumento9 páginasManual Sistema de TicketsOfelia Flores SanchezAinda não há avaliações

- Manual BERADocumento149 páginasManual BERALilith Samael SturdbridgeAinda não há avaliações

- Traducción Direcciones de Red IPv4Documento36 páginasTraducción Direcciones de Red IPv4jccp19691969100% (1)

- Esp Tecnicas TMC - 36Documento6 páginasEsp Tecnicas TMC - 36Jose AlvarezAinda não há avaliações

- Catalogo Normas de Metrologia de IndecopiDocumento9 páginasCatalogo Normas de Metrologia de IndecopiAndrés PacompíaAinda não há avaliações

- El ContactorDocumento10 páginasEl ContactorPablo AngerAinda não há avaliações

- Especificaciones PinturaDocumento51 páginasEspecificaciones PinturaSebas FaustoAinda não há avaliações

- Cuadro Comparativo Sobre Principios y Normas de ContabilidadDocumento3 páginasCuadro Comparativo Sobre Principios y Normas de ContabilidadLayubia Espinoza100% (7)

- Tabla de ConversionesDocumento6 páginasTabla de ConversionesAbel ColungaAinda não há avaliações

- Codigos AsciiDocumento2 páginasCodigos AsciitavoycoAinda não há avaliações

- Pruebas de Diferencia de MediasDocumento5 páginasPruebas de Diferencia de MediasKarl AlloNxo50% (2)

- Costo de CalidadDocumento3 páginasCosto de CalidadYeidis Eduardo EspinosaAinda não há avaliações

- Comunicacion IED630-PCM600Documento28 páginasComunicacion IED630-PCM600aderrlyAinda não há avaliações

- NAT CiscoDocumento400 páginasNAT CiscoAndresAinda não há avaliações

- Informe Final de EMSDocumento4 páginasInforme Final de EMSHeiserHQAinda não há avaliações

- Catalogo LINET-LAN Octubre2013Documento5 páginasCatalogo LINET-LAN Octubre2013Centro de ConectividadAinda não há avaliações