Escolar Documentos

Profissional Documentos

Cultura Documentos

Mitsubishi Semiconductor

Enviado por

edgardo2004Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Mitsubishi Semiconductor

Enviado por

edgardo2004Direitos autorais:

Formatos disponíveis

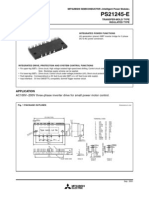

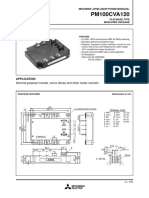

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21964-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

PS21964-4S

INTEGRATED POWER FUNCTIONS

600V/15A low-loss 5th generation IGBT inverter bridge for

three phase DC-to-AC power conversion.

Open emitter type.

INTEGRATED DRIVE, PROTECTION AND SYSTEM CONTROL FUNCTIONS

For upper-leg IGBTS :Drive circuit, High voltage high-speed level shifting, Control supply under-voltage (UV) protection.

For lower-leg IGBTS : Drive circuit, Control supply under-voltage protection (UV), Short circuit protection (SC).

Fault signaling : Corresponding to an SC fault (Lower-leg IGBT) or a UV fault (Lower-side supply).

Input interface : 3V, 5V line (High Active).

UL Approved : Yellow Card No. E80276

APPLICATION

AC100V~200V inverter drive for small power motor control.

Fig. 1 PACKAGE OUTLINES

Dimensions in mm

38 0.5

201.778(=35.56 )

35 0.3

3.5

3 MIN

18

(3.5)

14.4 0.5

Lot No.

29.2 0.5

Code

33.7 0.5

Type name

18.9 0.5

12

QR

24 0.5

.6

R1

(3.3)

14.4 0.5

17

(1)

16-0.5

2-

TERMINAL CODE

1.5 0.05

0.4

0.28

1.778 0.2

0.8

HEAT SINK SIDE

0.28

2.54 0.2

8-0.6

4-C1.2

142.54(=35.56)

(2.656)

(1.2)

0.5

5.5 0.5

HEAT SINK SIDE

2.5 MIN

0.5

9.5 0.5

0.5

(VNC)

VUFB

VVFB

VWFB

UP

VP

WP

VP1

VNC *

UN

VN

WN

VN1

FO

CIN

VNC *

NC

NW

NV

NU

W

V

U

P

NC

1.5m

in

(0~5)

0.5

0.4

25

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15.

16.

17.

18.

19.

20.

21.

22.

23.

24.

25.

(1.2)

(2.756)

DETAIL A

DETAIL B

*) Two VNC terminals (9 & 16 pin) are connected inside DIP-IPM, please connect either one to the 15V power supply GND outside and

leave another one open.

Mar. 2007

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21964-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

MAXIMUM RATINGS (Tj = 25C, unless otherwise noted)

INVERTER PART

Symbol

VCC

VCC(surge)

VCES

IC

ICP

PC

Tj

Parameter

Condition

Applied between P-NU, NV, NW

Supply voltage

Supply voltage (surge)

Collector-emitter voltage

Each IGBT collector current

Each IGBT collector current (peak)

Collector dissipation

Junction temperature

Ratings

Applied between P-NU, NV, NW

TC = 25C

TC = 25C, less than 1ms

TC = 25C, per 1 chip

(Note 1)

450

500

600

15

30

33.3

20~+125

Unit

V

V

V

A

A

W

C

Note 1 : The maximum junction temperature rating of the power chips integrated within the DIP-IPM is 150C (@ TC 100C). However, to

ensure safe operation of the DIP-IPM, the average junction temperature should be limited to Tj(ave) 125C (@ TC 100C).

CONTROL (PROTECTION) PART

Symbol

Parameter

VD

VDB

Control supply voltage

Control supply voltage

VIN

Input voltage

VFO

IFO

VSC

Fault output supply voltage

Fault output current

Current sensing input voltage

Condition

Ratings

Unit

Applied between VP1-VNC, VN1-VNC

Applied between VUFB-U, VVFB-V, VWFB-W

Applied between UP, VP, WP, UN, VN,

WN-VNC

Applied between FO-VNC

20

20

V

V

0.5~VD+0.5

0.5~VD+0.5

1

0.5~VD+0.5

V

mA

V

Ratings

Unit

400

20~+100

40~+125

1500

Vrms

Sink current at FO terminal

Applied between CIN-VNC

TOTAL SYSTEM

Symbol

Condition

VD = 13.5~16.5V, Inverter part

Tj = 125C, non-repetitive, less than 2s

(Note 2)

Parameter

VCC(PROT) Self protection supply voltage limit

(short circuit protection capability)

Module case operation temperature

TC

Tstg

Storage temperature

Viso

60Hz, Sinusoidal, 1 minute,

Between pins and heat-sink plate

Isolation voltage

Note 2: TC measurement point

Control terminals

11.6mm

DIP-IPM

3mm

IGBT chip position

TC point

FWD chip position

Heat sink side

Power terminals

Mar. 2007

2

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21964-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

THERMAL RESISTANCE

Symbol

Rth(j-c)Q

Rth(j-c)F

Condition

Parameter

Junction to case thermal

resistance

(Note 3)

Inverter IGBT part (per 1/6 module)

Inverter FWD part (per 1/6 module)

Min.

Limits

Typ.

Max.

3.0

3.9

Unit

C/W

C/W

Note 3 : Grease with good thermal conductivity should be applied evenly with about +100m~+200m on the contacting surface of DIP-IPM

and heat-sink.

The contacting thermal resistance between DIP-IPM case and heat sink (Rth(c-f)) is determined by the thickness and the thermal

conductivity of the applied grease. For reference, Rth(c-f) (per 1/6 module) is about 0.3C/W when the grease thickness is 20m and

the thermal conductivity is 1.0W/mk.

ELECTRICAL CHARACTERISTICS (Tj = 25C, unless otherwise noted)

INVERTER PART

Symbol

VCE(sat)

VEC

ton

trr

tc(on)

toff

tc(off)

ICES

Condition

Parameter

Collector-emitter saturation

voltage

FWD forward voltage

Switching times

IC = 15A, Tj = 25C

VD = VDB = 15V

VIN = 5V

IC = 15A, Tj = 125C

Tj = 25C, IC = 15A, VIN = 0V

VCC = 300V, VD = VDB = 15V

IC = 15A, Tj = 125C, VIN = 0 5V

Inductive load (upper-lower arm)

Collector-emitter cut-off

current

Tj = 25C

VCE = VCES

Tj = 125C

Min.

Limits

Typ.

0.70

1.70

1.80

1.70

1.30

0.30

0.50

1.60

0.50

Max.

2.20

2.30

2.20

1.90

0.75

2.20

0.80

1

10

Min.

4.9

0.43

0.70

10.0

10.5

10.3

10.8

20

0.8

Limits

Typ.

0.48

1.00

2.1

1.3

Max.

2.80

0.55

2.80

0.55

0.95

0.53

1.50

12.0

12.5

12.5

13.0

2.6

0.35

0.65

Unit

V

V

s

s

s

s

s

mA

CONTROL (PROTECTION) PART

Symbol

ID

VFOH

VFOL

VSC(ref)

IIN

UVDBt

UVDBr

UVDt

UVDr

tFO

Vth(on)

Vth(off)

Vth(hys)

Parameter

Circuit current

Fault output voltage

Short circuit trip level

Input current

Control supply under-voltage

protection

Fault output pulse width

ON threshold voltage

OFF threshold voltage

ON/OFF threshold hysteresis

voltage

Condition

VD = VDB = 15V

Total of VP1-VNC, VN1-VNC

VIN = 5V

VUFB-U, VVFB-V, VWFB-W

Total of VP1-VNC, VN1-VNC

VD = VDB = 15V

VIN = 0V

VUFB-U, VVFB-V, VWFB-W

VSC = 0V, FO terminal pull-up to 5V by 10k

VSC = 1V, IFO = 1mA

Tj = 25C, VD = 15V

(Note 4)

VIN = 5V

Trip level

Reset level

Tj 125C

Trip level

Reset level

(Note 5)

Applied between UP, VP, WP, UN, VN, WN-VNC

Unit

mA

V

V

V

mA

V

V

V

V

s

V

V

V

Note 4 : Short circuit protection is functioning only for the lower-arms. Please select the external shunt resistance such that the SC trip-level is

less than 1.7 times of the current rating.

5 : Fault signal is asserted corresponding to a short circuit or lower side control supply under-voltage failure.

Mar. 2007

3

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21964-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

MECHANICAL CHARACTERISTICS AND RATINGS

Condition

Parameter

Mounting screw : M3

Recommended : 0.69 Nm

(Note 6)

Mounting torque

Weight

Heat-sink flatness

Note 6 : Plain washers (ISO 7089~7094) are recommended.

(Note 7)

Min.

Limits

Typ.

Max.

0.59

0.78

Nm

50

10

100

g

m

Min.

Limits

Typ.

Max.

0

13.5

13.0

1

1.5

300

15.0

15.0

400

16.5

18.5

1

20

7.5

4.5

0.5

0.5

5.0

5.0

Unit

Note 7: Flatness measurement position

Measurement position

4.6mm

DIP-IPM

Heat sink side

Heat sink side

RECOMMENDED OPERATION CONDITIONS

Symbol

Parameter

VCC

VD

VDB

VD, VDB

tdead

fPWM

Supply voltage

Control supply voltage

Control supply voltage

Control supply variation

Arm shoot-through blocking time

PWM input frequency

IO

Allowable r.m.s. current

Condition

Applied between P-NU, NV, NW

Applied between VP1-VNC, VN1-VNC

Applied between VUFB-U, VVFB-V, VWFB-W

For each input signal, TC 100C

TC 100C, Tj 125C

VCC = 300V, VD = VDB = 15V,

fPWM = 5kHz

P.F = 0.8, sinusoidal PWM,

(Note 8) fPWM = 15kHz

Tj 125C, TC 100C

PWIN(on) Allowable minimum input

PWIN(off) pulse width

VNC variation

VNC

(Note 9)

Unit

V

V

V

V/s

s

kHz

Arms

Between VNC-NU, NV, NW (including surge)

Note 8 : The allowable r.m.s. current value depends on the actual application conditions.

9 : IPM might not make response if the input signal pulse width is less than the recommended minimum value.

s

V

Mar. 2007

4

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21964-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

Fig. 2 THE DIP-IPM INTERNAL CIRCUIT

DIP-IPM

VUFB

HVIC

VP1

VCC

VUB

UP

UP

UOUT

VNC

VVFB

VP

IGBT1

Di1

VUS

COM

IGBT2

VVB

Di2

VOUT

VP

VVS

VWFB

WP

VWB

WP

IGBT3

Di3

IGBT4

Di4

IGBT5

Di5

WOUT

VWS

LVIC

UOUT

VN1

VCC

NU

VOUT

UN

UN

VN

VN

WN

WN

Fo

Fo

NV

IGBT6

Di6

WOUT

CIN

NW

VNO

VNC

GND

CIN

Mar. 2007

5

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21964-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

Fig. 3 TIMING CHART OF THE DIP-IPM PROTECTIVE FUNCTIONS

[A] Short-Circuit Protection (Lower-side only with the external shunt resistor and CR filter)

a1. Normal operation : IGBT ON and carrying current.

a2. Short circuit detection (SC trigger).

a3. IGBT gate hard interruption.

a4. IGBT turns OFF.

a5. FO outputs (tFO(min) = 20s).

a6. Input L : IGBT OFF.

a7. Input H : IGBT ON.

a8. IGBT OFF in spite of input H.

Lower-side control

input

a6 a7

Protection circuit state

SET

Internal IGBT gate

RESET

a3

a2

a1

SC

a4

Output current Ic

a8

SC reference voltage

Sense voltage of the

shunt resistor

CR circuit time

constant DELAY

Error output Fo

a5

[B] Under-Voltage Protection (Lower-side, UVD)

b1. Control supply voltage rising : After the voltage level reaches UVDr, the circuits start to operate when next input is applied.

b2. Normal operation : IGBT ON and carrying current.

b3. Under voltage trip (UVDt).

b4. IGBT OFF in spite of control input condition.

b5. FO outputs (tFO 20s and FO outputs continuously during UV period).

b6. Under voltage reset (UVDr).

b7. Normal operation : IGBT ON and carrying current.

Control input

Protection circuit state

Control supply voltage VD

RESET

UVDr

b1

SET

UVDt

b2

RESET

b6

b3

b4

b7

Output current Ic

Error output Fo

b5

Mar. 2007

6

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21964-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

[C] Under-Voltage Protection (Upper-side, UVDB)

c1. Control supply voltage rising : After the voltage level reaches UVDBr, the circuits start to operate when next input is applied.

c2. Normal operation : IGBT ON and carrying current.

c3. Under voltage trip (UVDBt).

c4. IGBT OFF in spite of control input signal level, but there is no FO signal outputs.

c5. Under voltage reset (UVDBr).

c6. Normal operation : IGBT ON and carrying current.

Control input

Protection circuit state

RESET

RESET

SET

UVDBr

Control supply voltage VDB

c1

UVDBt

c2

c5

c3

c4

c6

Output current Ic

High-level (no fault output)

Error output Fo

Fig. 4 RECOMMENDED MCU I/O INTERFACE CIRCUIT

5V line

DIP-IPM

10k

UP,VP,WP,UN,VN,WN

MCU

3.3k (min)

Fo

VNC(Logic)

Note : The setting of RC coupling at each input (parts shown dotted) depends on the PWM control scheme and the

wiring impedance of the printed circuit board.

The DIP-IPM input section integrates a 3.3k (min) pull-down resistor. Therefore, when using an external

filtering resistor, pay attention to the turn-on threshold voltage.

Fig. 5 WIRING CONNECTION OF SHUNT RESISTOR

DIP-IPM

Each wiring inductance should be less than 10nH.

Equivalent to the inductance of a copper

pattern in dimension of width=3mm,

thickness=100m, length=17mm

VNC

NU

NV

NW

Shunt resistors

Please make the GND wiring connection

of shunt resistor to the VNC terminal

as close as possible.

Mar. 2007

7

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21964-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

Fig. 6 AN EXAMPLE OF TYPICAL DIP-IPM APPLICATION CIRCUIT

C1: Electrolytic capacitor with good temperature characteristics

C2,C3: 0.22~2F R-category ceramic capacitor for noise filtering

C2 C1 C2 C1

C2 C1

Bootstrap negative electrodes

should be connected to U, V,

W terminals directly and

separated from the main output

wires.

VUFB

VVFB

VWFB

DIP-IPM

P

HVIC

VP1

C3

UP

VCC

UP

VUB

UOUT

VUS

VVB

VP

VP

VOUT

VVS

VWB

WP

VNC

WP

COM

WOUT

VWS

MCU

LVIC

UOUT

VN1

5V line

NU

VCC

C3

VOUT

UN

VN

WN

Fo

UN

NV

VN

WN

WOUT

Fo

CIN

NW

VNO

VNC

Long wiring here might

cause short-circuit.

GND

CIN

15V line

Long wiring here might cause

SC level fluctuation and

malfunction.

Long GND wiring here might

generate noise to input and

cause IGBT malfunction.

Shunt resistors

A

B R1

+

-

Vref

Vref

C4

B R1

+

-

C4

B R1

OR Logic

N1

Vref

Comparator

C4

External protection circuit

Note 1 : Input drive is High-Active type. There is a 3.3k(min.) pull-down resistor integrated in the IC input circuit. To prevent malfunction, the wiring of each input should be as short as possible. When using RC coupling circuit, make sure the input signal level meet the turn-on and turn-off threshold voltage.

2 : Thanks to HVIC inside the module, direct coupling to MCU without any opto-coupler or transformer isolation is possible.

3 : FO output is open drain type. It should be pulled up to the positive side of a 5V power supply by a resistor of about 10k.

4 : To prevent erroneous protection, the wiring of A, B, C should be as short as possible.

5 : The time constant R1C4 of the protection circuit should be selected in the range of 1.5-2s. SC interrupting time might vary with the

wiring pattern. Tight tolerance, temp-compensated type is recommended for R1, C4.

6 : All capacitors should be mounted as close to the terminals of the DIP-IPM as possible. (C1: good temperature, frequency characteristic electrolytic type, and C2, C3: good temperature, frequency and DC bias characteristic ceramic type are recommended.)

7 : To prevent surge destruction, the wiring between the smoothing capacitor and the P, N1 terminals should be as short as possible.

Generally a 0.1-0.22F snubber between the P-N1 terminals is recommended.

8 : Two VNC terminals (9 & 16 pin) are connected inside DIP-IPM, please connect either one to the 15V power supply GND outside and

leave another one open.

9 : It is recommended to insert a Zener diode (24V/1W) between each pair of control supply terminals to prevent surge destruction.

10 : If control GND is connected to power GND by broad pattern, it may cause malfunction by power GND fluctuation. It is recommended

to connect control GND and power GND at only a point.

11 : The reference voltage Vref of comparator should be set up the same rating of short circuit trip level (Vsc(ref): min.0.43V to max.0.53V).

12 : OR logic output high level should exceed the maximum short circuit trip level (Vsc(ref): max.0.53V).

Mar. 2007

8

Você também pode gostar

- PS21245 eDocumento9 páginasPS21245 eTol SirtAinda não há avaliações

- Mitsubishi Semiconductor Mitsubishi SemiconductorDocumento8 páginasMitsubishi Semiconductor Mitsubishi Semiconductoramired2Ainda não há avaliações

- Ps 21245Documento9 páginasPs 21245pukymottoAinda não há avaliações

- Ps22a78 eDocumento10 páginasPs22a78 evishwa_001Ainda não há avaliações

- Air Acond Ps21246 OnduladorDocumento10 páginasAir Acond Ps21246 OnduladorJ CorreoAinda não há avaliações

- Mitsubishi Igbt CSTBT Pm150rl1a120 E2Documento9 páginasMitsubishi Igbt CSTBT Pm150rl1a120 E2Damiano ZitoAinda não há avaliações

- Irams 06 Up 60 ADocumento18 páginasIrams 06 Up 60 AAndré Roberto EvangelistaAinda não há avaliações

- PM 150 CSD 120Documento7 páginasPM 150 CSD 120elecompinnAinda não há avaliações

- PM20CSJ060Documento6 páginasPM20CSJ060Dany Carrasco Ysus TecladosAinda não há avaliações

- IRAMX16UP60ADocumento18 páginasIRAMX16UP60Atheylor1990Ainda não há avaliações

- Pm100cva120 - e IGBT PDFDocumento6 páginasPm100cva120 - e IGBT PDFDoDuyBacAinda não há avaliações

- Ps 11034Documento5 páginasPs 11034Tanvon MalikAinda não há avaliações

- Double Channel High Side Solid State Relay: VND600SPDocumento17 páginasDouble Channel High Side Solid State Relay: VND600SPDan EsentherAinda não há avaliações

- 10884Documento13 páginas10884karthikeidAinda não há avaliações

- Ps 21 A 79Documento10 páginasPs 21 A 79Omar LeonAinda não há avaliações

- BSP 75NDocumento14 páginasBSP 75NmikosoyAinda não há avaliações

- BSP75NDocumento15 páginasBSP75NroozbehxoxAinda não há avaliações

- FSBB20CH60: Smart Power ModuleDocumento16 páginasFSBB20CH60: Smart Power ModuleDhaka AsasaAinda não há avaliações

- ECN3021Documento10 páginasECN3021Wasang Juwi PracihnoAinda não há avaliações

- L 6565Documento17 páginasL 6565tatatabuchoAinda não há avaliações

- Bit 3713Documento24 páginasBit 3713neckoprvak5Ainda não há avaliações

- Iramx 16 Up 60 ADocumento17 páginasIramx 16 Up 60 AJandfor Tansfg ErrottAinda não há avaliações

- 1N002 DatasheetDocumento33 páginas1N002 DatasheetJorge DeganteAinda não há avaliações

- EN5322QI: 2 A Voltage Mode Synchronous Buck PWM DC-DC Converter With Integrated InductorDocumento16 páginasEN5322QI: 2 A Voltage Mode Synchronous Buck PWM DC-DC Converter With Integrated Inductorcatsoithahuong84Ainda não há avaliações

- LCD Bias Power Integrated With WLED Backlight Drivers: FeaturesDocumento31 páginasLCD Bias Power Integrated With WLED Backlight Drivers: FeaturesJoseph BernardAinda não há avaliações

- VND 7 N 04Documento30 páginasVND 7 N 04Juan Guillermo MansillaAinda não há avaliações

- Driver Bobina de Encendido VB326SPDocumento9 páginasDriver Bobina de Encendido VB326SPteroplasAinda não há avaliações

- General Description Features: Bipolar/CMOS/DMOSDocumento13 páginasGeneral Description Features: Bipolar/CMOS/DMOSjavierrincon800Ainda não há avaliações

- Iso 5500Documento40 páginasIso 5500Syukri HakimiAinda não há avaliações

- Double Channel High Side Solid State RelayDocumento18 páginasDouble Channel High Side Solid State RelayDan EsentherAinda não há avaliações

- Bd9397efv e PDFDocumento30 páginasBd9397efv e PDFshafiuddin7326Ainda não há avaliações

- Auips 7111 SDocumento15 páginasAuips 7111 SPham LongAinda não há avaliações

- FNB41560 / FNB41560B2: Motion SPM 45 SeriesDocumento16 páginasFNB41560 / FNB41560B2: Motion SPM 45 SeriesHadeedAhmedSherAinda não há avaliações

- HV9971Documento10 páginasHV9971Jazmin JorgeAinda não há avaliações

- Low Power Quad Operational Amplifier: Description Pin ConfigurationDocumento8 páginasLow Power Quad Operational Amplifier: Description Pin ConfigurationPaulbert ThomasAinda não há avaliações

- Ps21867 P OriginalDocumento6 páginasPs21867 P OriginalOmar LeonAinda não há avaliações

- UA723Documento6 páginasUA723Gheorghe DanielAinda não há avaliações

- Mcp1416 Power Mosfet DriverDocumento18 páginasMcp1416 Power Mosfet DriverNegru P. PlantatieAinda não há avaliações

- Double Channel High Side Driver: Type R I VDocumento19 páginasDouble Channel High Side Driver: Type R I VDan EsentherAinda não há avaliações

- LM8364 Micropower Undervoltage Sensing Circuits: Features DescriptionDocumento14 páginasLM8364 Micropower Undervoltage Sensing Circuits: Features DescriptionToni BioscaAinda não há avaliações

- VNB35NV04 / VNP35NV04 VNV35NV04 / VNW35NV04: "Omnifet Ii": Fully Autoprotected Power MosfetDocumento19 páginasVNB35NV04 / VNP35NV04 VNV35NV04 / VNW35NV04: "Omnifet Ii": Fully Autoprotected Power MosfetJosé AdelinoAinda não há avaliações

- "Omnifet Ii": Fully Autoprotected Power Mosfet: VNS3NV04DDocumento14 páginas"Omnifet Ii": Fully Autoprotected Power Mosfet: VNS3NV04DDan EsentherAinda não há avaliações

- Ltc1871ems (LTSX, Frntoluz Welch Allyn)Documento36 páginasLtc1871ems (LTSX, Frntoluz Welch Allyn)RICHIHOTS2Ainda não há avaliações

- 2A, 28V, 1.5Mhz Step-Down Converter: The Future of Analog Ic TechnologyDocumento16 páginas2A, 28V, 1.5Mhz Step-Down Converter: The Future of Analog Ic TechnologyCazbir MariAndradaAinda não há avaliações

- VN800S VN800PT: High Side DriverDocumento21 páginasVN800S VN800PT: High Side DriverDan EsentherAinda não há avaliações

- LTC 1625Documento24 páginasLTC 1625Sakura KunAinda não há avaliações

- MAX038Documento17 páginasMAX038Brane PetkoskiAinda não há avaliações

- SSC2001S Application NoteDocumento18 páginasSSC2001S Application NoteGerardo Mendez CamarilloAinda não há avaliações

- DPM 1As-Bl: Product DescriptionDocumento4 páginasDPM 1As-Bl: Product DescriptionFane PelinAinda não há avaliações

- Viper 53Documento24 páginasViper 53Cadena CesarAinda não há avaliações

- Low Power Dual Operational Amplifier: Description Pin ConfigurationDocumento8 páginasLow Power Dual Operational Amplifier: Description Pin ConfigurationAmrutha AmmuAinda não há avaliações

- TLC 2934Documento9 páginasTLC 2934Carlos DanielAinda não há avaliações

- Self-Oscillating Half-Bridge Driver: Ir2153 (D) (S) & (PBF)Documento9 páginasSelf-Oscillating Half-Bridge Driver: Ir2153 (D) (S) & (PBF)Zoltán HalászAinda não há avaliações

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Ainda não há avaliações

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1No EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Nota: 2.5 de 5 estrelas2.5/5 (3)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsAinda não há avaliações

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsNo EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsNota: 3.5 de 5 estrelas3.5/5 (6)

- 110 Waveform Generator Projects for the Home ConstructorNo Everand110 Waveform Generator Projects for the Home ConstructorNota: 4 de 5 estrelas4/5 (1)

- Upstream Process Engineering Course: 5. Produced WaterDocumento27 páginasUpstream Process Engineering Course: 5. Produced WaterMohamed SelimAinda não há avaliações

- Planets and Solar System The Complete Manual 2016Documento132 páginasPlanets and Solar System The Complete Manual 2016Sonechka Sonya100% (3)

- PowerPoint Practice Exercise 1 InstructionsDocumento3 páginasPowerPoint Practice Exercise 1 InstructionsErick OumaAinda não há avaliações

- State-Of-The-Art of Battery State-Of-Charge DeterminationDocumento19 páginasState-Of-The-Art of Battery State-Of-Charge Determinationyasvanthkumar sAinda não há avaliações

- Recent Developments On The Interpretation of Dissolved Gas Analysis in TransformersDocumento33 páginasRecent Developments On The Interpretation of Dissolved Gas Analysis in TransformersputrasejahtraAinda não há avaliações

- Virtual Memory & Demand PagingDocumento22 páginasVirtual Memory & Demand PagingAli AhmadAinda não há avaliações

- Electronic Devices & Practice: InstructorDocumento23 páginasElectronic Devices & Practice: Instructorjavaid musaAinda não há avaliações

- EIE3123 Dynamic Electronic Systems - p1-p57Documento57 páginasEIE3123 Dynamic Electronic Systems - p1-p57Safwat KhairAinda não há avaliações

- Ns 3 TutorialDocumento105 páginasNs 3 TutorialparabavireoAinda não há avaliações

- Eaton Xeffect Industrial Switchgear Range Catalog Ca003002en en UsDocumento379 páginasEaton Xeffect Industrial Switchgear Range Catalog Ca003002en en UsMAURIZIO MARINIAinda não há avaliações

- 5-EN 4050-A (Dig) - 2F1CDocumento9 páginas5-EN 4050-A (Dig) - 2F1Cabuzer1981Ainda não há avaliações

- Compressor Anti-Surge ValveDocumento2 páginasCompressor Anti-Surge ValveMoralba SeijasAinda não há avaliações

- Wasif CVDocumento2 páginasWasif CVTalha BaigAinda não há avaliações

- Potassium in Water by Atomic Absorption Spectrophotometry: Standard Test Method ForDocumento4 páginasPotassium in Water by Atomic Absorption Spectrophotometry: Standard Test Method ForhydrogenperoksideAinda não há avaliações

- ANSYS Tutorial Design OptimizationDocumento9 páginasANSYS Tutorial Design OptimizationSimulation CAE100% (4)

- Unit 2 - Introduction To Java - Solutions For Class 9 ICSE APC Understanding Computer Applications With BlueJ Including Java Programs - KnowledgeBoatDocumento8 páginasUnit 2 - Introduction To Java - Solutions For Class 9 ICSE APC Understanding Computer Applications With BlueJ Including Java Programs - KnowledgeBoatGopi Selvaraj67% (3)

- 3.032 Problem Set 2 Solutions: Due: Start of Lecture, 09.21.07Documento16 páginas3.032 Problem Set 2 Solutions: Due: Start of Lecture, 09.21.07Pkay TandohAinda não há avaliações

- LAB211 Assignment: Title Background ContextDocumento2 páginasLAB211 Assignment: Title Background ContextDuong Quang Long QP3390Ainda não há avaliações

- Normativ Panouri SandwichDocumento58 páginasNormativ Panouri SandwichAlex ChiraAinda não há avaliações

- MICOM P12x-TechnicalDataSheetDocumento28 páginasMICOM P12x-TechnicalDataSheetSeba GonzálezAinda não há avaliações

- Java OOP Arrays and ExceptionsDocumento11 páginasJava OOP Arrays and ExceptionsJava OOPAinda não há avaliações

- CTX 310 Communication With Fast Ethernet Board V2 (Fanuc)Documento34 páginasCTX 310 Communication With Fast Ethernet Board V2 (Fanuc)iveAinda não há avaliações

- Statistics Hand NotesDocumento16 páginasStatistics Hand NotesAtul VermaAinda não há avaliações

- Staircase Preliminary Design Based On NBC and IS CodeDocumento10 páginasStaircase Preliminary Design Based On NBC and IS CodeEducation. HubAinda não há avaliações

- Datasheet Cpu 416-2Documento13 páginasDatasheet Cpu 416-2Danu MaldinoAinda não há avaliações

- Data Structure and AlgorithmDocumento12 páginasData Structure and Algorithmleah pileoAinda não há avaliações

- Database Management SystemsDocumento19 páginasDatabase Management Systemsshreeya PatilAinda não há avaliações

- Jee Advanced PaperDocumento3 páginasJee Advanced PaperGaurav YadavAinda não há avaliações

- ScriptHookDotNet ReadmeDocumento8 páginasScriptHookDotNet ReadmeFajar Hari MuliaAinda não há avaliações

- TractionDocumento26 páginasTractionYogesh GurjarAinda não há avaliações