Escolar Documentos

Profissional Documentos

Cultura Documentos

Informe Del Alu

Enviado por

Wilson ManobandaDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Informe Del Alu

Enviado por

Wilson ManobandaDireitos autorais:

Formatos disponíveis

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

I.

PORTADA

UNIVERSIDAD TCNICA DE AMBATO

Facultad de Ingeniera en Sistemas, Electrnica e Industrial

Ttulo:

ALU

Carrera:

Electrnica y Comunicaciones

rea Acadmica:

Sistemas Electrnicos

Lnea de Investigacin:

Fsica - Electrnica

Ciclo Acadmico y Paralelo:

Abril/2015 Septiembre/2015

Sexto E A

Alumnos participantes:

Juan Carlos Jordn

Wilson Manobanda

Daro Sols

Lizbeth Villarroel

Mdulo y Docente:

Microprocesadores

Ing. Patricio Crdova

II.

Fecha de envi:

28 de mayo del 2015

Fecha de entrega:

12 de junio del 2015

INFORME

1. YY

1.1 Ttulo

Implementacin de una Unidad Aritmtica Lgica (ALU)

1.2 Objetivos

1.2.1

General

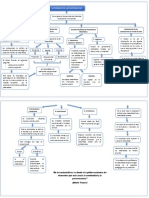

Disear e implementar un ALU de operaciones aritmticas y operaciones lgicas de

dos nmeros que contenga una parte entera y una parte decimal.

2.2.2 Especifico

Comprobar el correcto funcionamiento de los circuitos diseados.

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Implementar un ALU (Unidad Aritmtica Lgica), distribuida en etapas.

Implementar el ingreso de las entradas como el de las salidas mediante displays

para una mejor comprensin y una mejor esttica del trabajo

Aplicar los conocimientos sobre Algebra Booleana y Aritmtica Binaria.

1.3 Resumen

El presente trabajo es el diseo y la implementacin de una unidad aritmtica lgica

(ALU), que ser desarrollado, para la realizacin del proyecto se hace una recopilacin

de los conocimientos adquirido en el rea de la electrnica digital como algebra

boolean y aritmtica binaria de esta manera se involucro el diseo de cada una de sus

partes de los procesos lgicos, los circuitos combinacionales, circuitos de memoria, el

cual fueron simulados en proteus para la comprobacin de su correcto funcionamiento y

proceder su elaboracin.

1.4 Palabras Claves

implementacin)

(Combinacional,

Proceso,

Diseo,

Funcin,

Registros,

1.5 Introduccin

Una funcin esencial de muchas computadoras y calculadoras es la realizacin de

operaciones aritmticas. Estas operaciones se efectan en la unidad aritmticalgica de una computadora, donde se combinan compuertas lgicas y flip-flops de

manera que puedan sumar, restar, multiplicar y dividir nmeros binarios.

La unidad aritmtica lgica es una de las unidades que forman parte de la Unidad

Central de Procesos es decir, del Procesador, Microprocesador o CPU mediante la cual

es posible realizar una gran cantidad de operaciones aritmticas bsicas (Suma, Resta,

Divisin y Multiplicacin) operaciones Lgicas (NOT, OR, NAND, AND).

La ALU est formado por:

Circuito operacional

Registros de entrada (REN)

Registro acumulador

Registro de estado (flags)

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

1.6 Materiales y Metodologa

1.6.1

Marco Terico

Unidad aritmtica y lgica (ALU)

ALU (Arithmetic Logic Unit). Es el elemento de procesamiento clave del

microprocesador, puede realizar un conjunto de operaciones aritmticas bsicas y un

conjunto de operaciones lgicas, a travs de lneas de seleccin Esta unidad realiza

clculos (suma, resta, multiplicacin y divisin) y operaciones lgicas (comparaciones),

dirigida por una unidad de control.

Transfiere los datos entre las posiciones de almacenamiento.

Tiene un registro muy importante conocido como: Acumulador ACC Al realizar

operaciones aritmticas y lgicas, la ALU mueve datos entre ella y el almacenamiento.

Los datos usados en el procesamiento se transfieren de su posicin en el

almacenamiento a la ALU. Los datos se manipulan de acuerdo con las instrucciones del

programa y regresan al almacenamiento. Debido a que el procesamiento no puede

efectuarse en el rea de almacenamiento, los datos deben transferirse a la UAL. Para

terminar una operacin puede suceder que los datos pasen de la UAL al rea de

almacenamiento o varias veces. [1]

Fig. [1] Diagrama de bloques en una ALU

Estructura de la unidad lgica aritmtica

La estructura bsica de una unidad lgica aritmtica a suele consistir en utilizar

multiplexores con tantas entradas como operaciones queremos que realice dicha ALU y

en cada entrada colocar el circuito que ha de realizar la operacin correspondiente

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Fig. [2] Diagrama de bloques de un ejemplo de ALU

Las Terminales de la ALU son:

Entrada, los dos operando con los datos o con nmeros a ser procesados y la

entrada de un cdigo desde la unidad de Control con la informacin de que

operacin debe realizar.

Salida, la respuesta a computo de la operacin y el notificador de la operacin

realizada.

Registros de estado, entradas y salidas con informacin de acarreo, overflow,

divisin por cero y otras ms.

Buses utilizados:

El data bus (de entrada): lleva la informacin a la unidad aritmtica para su

procesamiento.

El status bus (de salida): los resultados e informacin procesada en la ALU son

transportados a la unidad de Control.

Registro de estado. [2]

Operaciones de desplazamiento

Desplazamientos lgicos

Independientemente del sistema de representacin de los operandos se introducen

ceros por la derecha o por la izquierda segn se trate de un desplazamiento a la

izquierda o a la derecha, respectivamente

El bit o los bits que salen suelen copiarse en el indicador de acarreo (el ltimo que

ha salido es el que queda)

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Fig. [3] Desplazamientos lgicos

Desplazamientos aritmticos:

Equivalen a multiplicaciones y divisiones por dos, segn sean hacia la izquierda o a

la derecha, respectivamente.

El sistema de representacin de los operandos debe tenerse en cuenta si los

operandos tienen signo

El bit o los bits que salen suelen copiarse en el indicador de acarreo (el ltimo que ha

salido es el que queda)

Fig. [4] Desplazamientos aritmtico

Desplazamientos circulares:

Los bits que salen por un extremo entran por el otro

El bit o los bits que salen suelen copiarse en el indicador de acarreo (el ltimo que ha

salido es el que queda)

Fig. [5] Desplazamientos circulares

Desplazamientos circulares a travs del flag de acarreo:

Los bits que salen por un extremo entran por el otro

El bit o los bits que salen suelen copiarse en el indicador de acarreo

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Fig. [6] Desplazamientos circulares a travs del flag de acarreo [5]

Lgica combinacional

Se denomina sistema combinacional o lgica combinacional a todo sistema digital en el

que sus salidas son funcin exclusiva del valor de sus entradas en un momento dado, sin

que intervengan en ningn caso estados anteriores de las entradas o de las salidas. Las

funciones (OR, AND, NAND, XOR) son booleanas donde cada funcin se puede

representar en una tabla de la verdad. Por tanto, carecen de memoria y de

realimentacin.

En electrnica digital la lgica combinacional est formada por ecuaciones simples a

partir de las operaciones bsicas del lgebra de Boole.

Los circuitos combinacionales:

Lgicos: Generador/Detector de paridad Multiplexor y De multiplexor Codificador

y Decodificador Conversor de cdigo Comparador

Aritmticos: Sumador Aritmticos y lgicos Unidad aritmtico lgica

Estos circuitos estn compuestos nicamente por puertas lgicas interconectadas

entre s

Operaciones aritmticas

Suma

Las computadoras digitales realizan una variedad de tareas de procesamiento de

informacin. Entre las funciones bsicas encontradas estn las diversas funciones

aritmticas. Sin duda, la operacin aritmtica ms bsica es la adicin de dos dgitos

binarios. Esta adicin simple consta de cuatro operaciones elementales posibles, a saber,

0 + 0 = 0, 0 + 1 = 1, 1 + 0 = 1 y 1 + 1 = 10. Las primeras tres operaciones producen una

suma cuya longitud es un dgito, pero cuando tanto los bits sumando como son iguales a

1, la suma binaria consta de dos dgitos. El bit significativo ms alto de este resultado se

denomina acarreo. Un circuito combinacional que lleva a cabo la adicin de dos bits se

denomina medio sumador. Uno que lleva a cabo la adicin de tres bits (dos bits

significativos y una cuenta que se lleva a previo) es un sumador completo. [2]

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Fig. [7] Sumador completo de un bit

El sumador completo de 4 bits es una concatenacin de 4 sumadores binarios completos

de 1 bit, como se muestra en el grfico inferior. La concatenacin se realiza a travs de

los terminales de acarreo saliente (Cin) y acarreo entrante (Cout).

El sumador que se muestra suma dos nmeros binarios de 4 bits cada uno.

A = A3A2A1A0 y B = B3B2B1B0 entonces la suma ser S = C (out) 3S3S2S1S0

El bit menos significativo en los dos sumandos A y B es Ao y Bo y el bit ms

significativo es A3 y B3.

Fig. [8] Sumador completo de dos nmeros de 4 bits

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

La suma se inicia en el sumador completo 0 (el inferior) con las suma de Ao y Bo, si

esta suma tuviese acarreo (Cout=1) este pasara al sumador 1, y as sucesivamente hasta

llegar al sumador 3 en la parte superior del grfico.

Si el sumador superior tiene acarreo ("1"), ste se refleja en la suma al lado izquierdo de

la sumatoria final.

Fig. [9] Diagrama de bloques de sumador completo de dos nmeros de 4 bit

Tipos de sumadores:

Half-Adder.-Se denomina semisumador aun circuito que admite 2 bits como

entrada y genera como salida: Un bit que representa la suma de los 2 bits

de entrada y otro bit que representa el acarreo generado por la suma.

Full-Adder.- La principal diferencia entre el sumador completo y el semisumador

es que este admite un valor que represente un acarreo de entrada

Mtodo Ripple.-Un circuito sumador completo permite sumar dos nmeros de un

bit con un acarreo de entrada y generar un acarreo de salida.

Carry-Look-Ahead.- Llamado

tambin

sumador

paralelo

con acarreo

anticipado, realiza la suma aumentando la velocidad de proceso sobre la

conexin en serie. Lo logra mediante la generacin de todos los bits de acarreo en

el mismo proceso de clculo de las sumas parciales

Resta

Un restador es un circuito combinacional que lleva a cobo la resta binaria de dos

nmero de n bits. La resta o sustraccin de nmeros binarios es similar a los nmeros

decimales. La diferencia radica en que, en binario, cuando el minuendo es menor que el

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

sustraendo, se produce un prstamo o borrow de 2, mientras que en decimal se produce

un prstamo de 10.

Fig. [10] restador completo de dos nmeros de 4 bits.

Al igual que la suma la resta puede ser implementada de varias formas para este caso lo

vamos hacer con complemento A2 para poder encontrar el signo de la operacin en caso

de que el minuendo sea menor que el sustraendo.

Complemento A2

El complemento A2 es un algoritmo binario que se utiliza para la resta partiendo desde

la suma para realizar la resta en binario se requiere seguir un proceso descrito por los

siguientes pasos:

Se iguala el nmero de cifras en el minuendo y el sustraendo aadiendo ceros a la

izquierda del nmero con menos cifras.

Se conserva el minuendo.

Se complementa a 1 el sustraendo. El complemento consiste en la cantidad que le

hace falta a un nmero para alcanzar el nmero mximo de su base. En el sistema

binario el complemento a 1 equivale a intercambiar 1 por 0 y 0 por 1.

Se suma el minuendo con el sustraendo complementado.

Si existe acarreo, se suma el acarreo al resultado de la suma anterior. La existencia

del acarreo indica que el resultado es positivo.

Si no existe acarreo, se complementa a 1 el resultado de la suma anterior. La no

existencia de acarreo indica que el resultado es negativo.[2]

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Fig. [11] Resta en complemento A2 de dos nmeros de n bits

Entonces el algoritmo indica los siguientes pasos:

Complementar a 1 el sustraendo. Dada dos entradas A y B, el sustraendo se

puede complementar haciendo uso de la compuerta NOT.

Sumar el minuendo con el sustraendo complementado. Se puede hacer uso

entonces del CI 74283. La siguiente figura muestra estos dos pasos.

Fig. [12] Resta en complemento A2 de dos nmeros de n bits

Complemento A1

Requiere que se identifique el bit de signo y tomar muy en cuenta el acarreo, el cual se

debe sumar al resultado para determinar el valor correcto de la operacin.

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Fig. [13] Resta en complemento A1 de dos nmeros de n bits

Sumador/Restador

El circuito Sumador/Restador mostrado a continuacin, tiene una entrada adicional

denominada MODO DE CONTROL. Si esta entrada est en un nivel bajo (0 lgico), las

cuatro puertas XOR no tienen efecto en el dato de las entradas B (el dato pasa a travs

de las puertas XOR y no es invertido). La entrada Cin del primer FA es mantenido en un

nivel BAJO, lo cual hace que este primer FA trabaje como semisumador. Cuando la

entrada de Modo de Control est en un nivel alto (1 lgico), las cuatro XOR actan

como inversores. Se invierte el sustraendo (entradas B). La entrada Cin del primer FA

est en un nivel ALTO, lo que es lo mismo que sumar +1 al sustraendo en complemento

a 1. La diferencia (resultado) se puede apreciar en los visualizadores

Fig. [14] Sumador/Restador de 4 bits

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Multiplicacin

La multiplicacin en binario es ms fcil que en cualquier otro sistema de numeracin.

Como los factores de la multiplicacin slo pueden ser CEROS o UNOS, el producto

slo puede ser CERO o UNO. En otras palabras, las tablas de multiplicar del cero y del

uno son muy fciles de aprender. En un ordenador, sin embargo, la operacin de

multiplicar se realiza mediante sumas repetidas. Eso crea algunos problemas en la

programacin porque cada suma de dos UNOS origina un arrastre, que se resuelven

contando el nmero de UNOS y de arrastres en cada columna. Si el nmero de UNOS

es par, la suma es un CERO y si es impar, un UNO. Luego, para determinar los arrastres

a la posicin superior, se cuentan las parejas de UNOS.

Fig. [15] Multiplicacin de dos nmeros de n bits

La multiplicacin de dos nmeros binarios de 4 bits con un entero y un decimal

respectivamente se lo puede describir como una multiplicacin sencilla teniendo como

resultado una suma al finalizar la operacin esta operacin se lo puede realizar mediante

comparadores que indican si los nmero son iguales o diferentes en cada una de las

posiciones.[3]

Divisin

Igual que en el producto, la divisin es muy fcil de realizar, porque no son posibles en

el cociente otras cifras que UNOS y CEROS.

Fig. [16] Divisin de dos nmeros de n bits

Se intenta dividir el dividendo por el divisor, empezando por tomar en ambos el mismo

nmero de cifras (100 entre 110, en el ejemplo). Si no puede dividirse, se intenta la

divisin tomando un dgito ms (1001 entre 100).

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Si la divisin es posible, entonces, el divisor slo podr estar contenido una vez en el

dividendo, es decir, la primera cifra del cociente es un UNO. En ese caso, el resultado

de multiplicar el divisor por 1 es el propio divisor. Restamos las cifras del dividendo del

divisor y bajamos la cifra siguiente.

El procedimiento de divisin contina del mismo modo que en el sistema decimal.[4]

Operaciones lgicas

Multiplexor

Un multiplexor (MUX) es un dispositivo que permite dirigir la informacin digital

procedente de diversas fuentes a una nica lnea para ser transmitida a travs de dicha

lnea a un destino comn. El multiplexor bsico posee varias lneas de entrada de datos

y una nica lnea de salida. Tambin posee entradas de seleccin de datos, que permiten

conmutar los datos digitales provenientes de cualquier entrada hacia la lnea de salida. A

los multiplexores tambin se les conoce como selectores de datos

Fig. [17]

Diagrama de bloques y diseo lgico del multiplexor

Comparador

La funcin bsica de un comparador consiste en comparar las magnitudes de dos

cantidades binarias para determinar su relacin. En su forma ms sencilla, un circuito

comparador determina si dos nmeros son iguales.

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Son elementos que en base a introducirle dos nmeros de n bits (A, B) entregan a su

salida mediante tres seales el valor de la comparacin M (A>B), I (A=B) y m (A<B).

Segn sus magnitudes

Comparador de Magnitudes de un Bit: La comparacin de dos bits se puede realizar

por medio de una compuerta OR exclusiva o una NOR exclusiva. La salida del

circuito es 1 si sus dos bits de entrada son diferentes y 0 si son iguales.

Comparador de Magnitudes de Dos Bits: Los nmeros A y B de dos bits en orden

significativo ascendente a descendente se ordenan.

Comparador de magnitudes de cuatro bits: Las entradas son A y B y las salidas son las

tres variables binarias A>B, A=B y A<B. Escribiendo los coeficientes de los nmeros

A y B en orden significativo de ascendente a descendente.

Fig. [18] Tabla de comparador

Fig. [19] Comparador binario de 4 bits

Contador

Los contadores son sistemas secuenciales con una sola entrada de impulsos a contar,

cuyo estado interno en cada instante representa el nmero de impulsos que se han

aplicado.

Si los impulsos ocurren a intervalos de tiempo conocidos, un contador puede utilizarse

como un instrumento de medida de tiempos

Registro de desplazamiento

Un registro de desplazamiento es un circuito digital secuencial (es decir, que

los valores de sus salidas dependen de sus entradas y de los valores

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

anteriores) consistente en una serie de biestables, generalmente de tipo D,

conectados en cascada, que basculan de forma sincrnica con la misma seal

de reloj. Segn las conexiones entre los biestables, se tiene un desplazamiento

a la izquierda o a la derecha de la informacin almacenada. Es de sealar que

un desplazamiento a la izquierda de un conjunto de bits, multiplica por 2,

mientras que uno a la derecha, divide entre 2. Existen registros de

desplazamiento

Bidireccionales, que pueden funcionar en ambos sentidos., los registros

universales, adems de bidireccionales permiten la carga en paralelo. [6]

1.6.2

Equipos y Materiales

Sumador

7 Displays 7 segmentos ctodo comn

4 circuitos integrados 74ls83

3 circuitos integrados 74ls48

1 circuito integrado 74ls 08

2 circuitos integrados 74ls32

2 Deep Swich de 8 lneas cada uno

2 Protoboard

Cable UTP ( Para las conexiones)

Cargador de 5v para alimentar a nuestro circuito

Restador

8 Displays 7 segmentos ctodo comn

6 circuitos integrados 74ls83

8 circuitos integrados 74ls48

1 circuito integrado 74ls 08

1 circuito integrados 74ls32

2 Deep Swich de 8 lneas cada uno

2 Protoboard

Cable UTP ( Para las conexiones)

Cargador de 5v para alimentar a nuestro circuito

Multiplicacin

8 Displays 7 segmentos ctodo comn

8 circuitos integrados 74ls48

8 circuitos integrado 74ls90

1 circuito integrado 74ls76

1 circuito integrado 74ls 08

1 circuito integrados 74ls32

4 circuitos integrados 75ls85

1 pulsador NA

2 Deep Swich de 8 lneas cada uno

1 resistencia de 330

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

3 Protoboard

Cable UTP ( Para las conexiones)

Cargador de 5v para alimentar a nuestro circuito

Divisin

8 Displays 7 segmentos ctodo comn

10 circuitos integrado 74ls90

8 circuitos integrados 74ls48

8 circuito integrado 74ls 08

1 circuito integrados 74ls32

1 circuito integrados 74ls76

4 circuitos integrados 75ls85

1 pulsador NA

2 Deep Swich de 8 lneas cada uno

1 resistencia de 330

3 Protoboard

Cable UTP ( Para las conexiones)

Cargador de 5v para alimentar a nuestro circuito

Comparador

4 Displays 7 segmentos ctodo comn

4circuitos integrados 74ls48

2 circuitos integrados 75ls85

1 pulsador NA

3 Diodos led

3 resistencias de 330

2 D1p Swich de 8 lneas cada uno

1 Protoboard

Cable UTP ( Para las conexiones)

Cargador de 5v para alimentar a nuestro circuito

Contador

4 Displays 7 segmentos nodo comn

4 circuitos integrados 74ls47

4 circuitos integrados 74ls85

8 circuitos integrados 74ls90

1 circuito integrado 74ls08

1 circuito integrado 74ls04

1 circuito integrado 74ls73

2 Dip Swich de 8 lneas cada uno

1 Protoboard

Cable UTP ( Para las conexiones)

Cargador de 5v para alimentar a nuestro circuito

Registro

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

4 Displays 7 segmentos nodo comn

4 circuitos integrados 74ls47

8circuitos integrados 74ls74

2 circuitos integrados 75ls157

2 Deep Swich de 8 lneas cada uno

1 Protoboard

Cable UTP ( Para las conexiones)

Cargador de 5v para alimentar a nuestro circuito

1.6.3

Diagrama

1.6.4

Procedimiento

Fig. 20] AL

Suma

Un sumador completo es un circuito combinacional que forma la suma aritmtica de

cuatro bits de entrada. Este consiste en dos entradas {a bits) y una salida {a bits). Dos

de las variables d

e entrada denotadas por A y B representan los nmeros a operarse.

Las entradas son proporcionadas por los bits de los sumandos, mientras las salidas son

producidas por la suma y el bit de acarreo.

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Fig. [21] Suma de dos nmeros de 4 bits con decimal en el programa Isis Proteus.

Resta

1.n2

2.n2

3.n2

4.n2

1n2

2n2

3n2

4n2

1.n1

U108

U109

NOT

NOT

NOT

C0

C4

14

U111

7483

A4

A3

A2

A1

15

2

6

9

S4

S3

S2

S1

A4

A3

A2

A1

1

3

8

10

15

2

6

9

S4

S3

S2

S1

7483

1

3

8

10

13

1

3

8

10

7483

S4

S3

S2

S1

A4

A3

A2

A1

U114

15

2

6

9

B4

B3

B2

B1

C0

C4

16

4

7

11

AND

13

U116

A4

A3

A2

A1

AND

AND

U101

U113

7483

S4

S3

S2

S1

U115

OR_3

U118

15

2

6

9

14

U120

AND

16

4

7

11

U117

OR_3

B4

B3

B2

B1

15

2

6

9

14

U119

14

B4

B3

B2

B1

C0

C4

14

C4

7483

16

4

7

11

13

C0

U112

B4

B3

B2

B1

1

3

8

10

15

2

6

9

S4

S3

S2

S1

A4

A3

A2

A1

7483

S4

S3

S2

S1

A4

A3

A2

A1

C0

C4

14

13

16

4

7

11

B4

B3

B2

B1

C4

C0

U110

1

3

8

10

U107

N OT

16

4

7

11

U106

NOT

13

U105

NOT

1

3

8

10

U104

NOT

16

4

7

11

U103

NOT

13

U102

B4

B3

B2

B1

2.n1

3.n1

4.n1

4n1

3n1

2n1

1n1

La resta de dos nmeros binarios puede lograrse tomando el complemento del

sustraendo para agregarlo al minuendo, mediante este mtodo, la operacin de

sustraccin se convierte en una operacin de suma que necesita sumadores

completos para su ejecucin, es por ello que si se lo requiere necesario

armaremos un circuito sumador restador unificado. Para la resta hay que tomar en

consideracin que se ha prestado un 1 de un estado menos significativo.

5resta

1resta

2resta

4resta

6resta

3resta

7resta

8resta

Fig. [22] Resta de dos nmeros de 4 bits con decimal en el programa Isis Proteus.

Multiplicacin

La operacin de multiplicacin se lo hace a travs de contadores de dcada y

comparadores los cuales inician su conteo y se detienen al recibir una orden de

comparacin siendo este el resultado de dicha operacin.

El ingreso de datos se lo hace a travs de interruptores comunes los cuales

ingresan compararse con algn patrn.

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Fig. [23] Multiplicacin de dos nmeros entero-decimal en el programa Isis Proteus

Divisin

La divisin se la obtiene por el mismo principio de funcionamiento que la con la

diferencia de que al existir indeterminaciones (divisiones para 0) el circuito

muestra un mensaje de error.

Fig. [24] Divisin de dos nmeros entero-decimal en el programa Isis Proteus

Comparacin

La comparacin se realiza por medio de compuertas XOR que alimentan a un full

adder, esta operacin es la ms bsica de la Unidad aritmtica lgica ya que esta

simplemente mediante comparadores verifica si los numero ingresados en este caso A

y B, determina y compara cual es el mayor, el menor o si son iguales.

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Fig. [25] Divisin de dos nmeros entero-decimal en el programa Isis Proteus.

Contador

El contador se realiz a travs de contadores de dcada y comparadores los cuales

inician su conteo y se detienen al recibir una orden de comparacin siendo este el

resultado de dicha operacin.

El ingreso de datos se lo hace a travs de interruptores comunes los cuales

ingresan compararse con algn patrn.

U2:A(A)

U2:A

U14

U1:A

Q

12

13

14

1

2

3

6

7

7408

CLK

K

CKA

CKB

Q0

Q1

Q2

Q3

12

9

8

11

R0(1)

R0(2)

R9(1)

R9(2)

7490

7473

14

R1

330R

U3

14

1

U7:A

CKA

CKB

1

3

2

7432

2

3

6

7

R0(1)

R0(2)

R9(1)

R9(2)

U9

Q0

Q1

Q2

Q3

12

9

8

11

7490

10

12

13

15

2

3

4

9

11

14

1

U15

14

1

COMP

P

3

<

=

>

0

P<Q

P=Q

P>Q

2

3

6

7

6

5

CKA

CKB

12

9

8

11

7490

10

12

13

15

2

3

4

9

11

14

1

12

9

8

11

U2:B

5

4

U10

Q0

Q1

Q2

Q3

R0(1)

R0(2)

R9(1)

R9(2)

Q0

Q1

Q2

Q3

2

3

6

7

R0(1)

R0(2)

R9(1)

R9(2)

7490

74HC85

U4

14

1

CKA

CKB

7408

COMP

P

3

<

=

>

0

P<Q

P=Q

P>Q

U16

14

1

2

3

6

7

3

74HC85

CKA

CKB

R0(1)

R0(2)

R9(1)

R9(2)

Q0

Q1

Q2

Q3

12

9

8

11

7490

U5

14

1

2

3

6

7

CKA

CKB

U11

Q0

Q1

Q2

Q3

12

9

8

11

R0(1)

R0(2)

R9(1)

R9(2)

7490

10

12

13

15

2

3

4

9

11

14

1

COMP

P

3

<

=

>

0

P<Q

P=Q

P>Q

Q

9

74HC85

U6

14

1

2

3

6

7

CKA

CKB

R0(1)

R0(2)

R9(1)

R9(2)

7490

12

9

8

11

10

12

13

15

2

3

4

9

11

14

1

U13:A

8

10

U12

Q0

Q1

Q2

Q3

U17

U2:C

7408

COMP

P

3

<

=

>

0

P<Q

P=Q

P>Q

7

6

7404

14

1

2

3

6

7

CKA

CKB

Q0

Q1

Q2

Q3

12

9

8

11

R0(1)

R0(2)

R9(1)

R9(2)

7490

Q

3

74HC85

Fig. [26] Divisin de dos nmeros entero-decimal en el programa Isis Proteus

Registro

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Vcc

SW1

GND

GND

GND

GND

GND

GND

GND

SW -SPDT-MOM

GND

13

14

10

11

6

5

3

2

4B

4A

3B

3A

2B

2A

1B

1A

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

1Y

2Y

VCC

3Y

4Y

12

Q

12

11

13

CLOCK

74LS74

VCC

74LS74

CLK

VCC

VCC

U28:B

10

D

CLK

74LS74

U28:A

13

CLOCK

74157

VCC

Q

D

CLK

11

CLOCK

12

74LS74

U27:B

10

VCC

CLOCK

D

CLK

U35

1Y

4

2Y

7

4Y

3Y

9

12

VCC

VCC

U27:A

4

CLOCK

A15

13

14

10

11

6

5

3

2

15

1

74157

E

A/B

4B

4A

3B

3A

2B

2A

1B

1A

E

A/B

GND

U36

15

1

GND

GND

A12

CLOCK

A13

VCC

Q

U30:B

10

12

11

13

74LS74

CLK

VCC

VCC

74LS74

CLK

74LS74

VCC

13

CLOCK

74LS74

CLK

CLOCK

11

12

U30:A

10

CLOCK

CLK

U29:B

VCC

CLOCK

U29:A

VCC

VCC

A14

VCC

A15

A10

12

11

74LS74

VCC

74LS74

CLK

CLOCK

VCC

VCC

U32:B

10

CLK

13

2

3

13

CLOCK

U32:A

74LS74

VCC

VCC

Q

CLK

CLOCK

12

11

74LS74

U31:B

10

S

R

U31:A

Q

CLK

VCC

CLOCK

2

3

A8

VCC

A9

VCC

A11

A6

A5

A4

74LS74

A2

VCC

Q

12

11

74LS74

A1

U34:B

10

D

CLK

CLOCK

CLK

13

4

2

U34:A

VCC

A3

CLOCK

74LS74

D

CLK

CLOCK

11

VCC

10

12

U33:B

13

VCC

D

CLK

VCC

CLOCK

U33:A

VCC

VCC

VCC

A7

74LS74

A0

Fig. [27] Divisin de dos nmeros entero-decimal en el programa Isis Proteus.

II.4.

Resultados esperados

Obtener el correcto funcionamiento de la unidad aritmtica lgica cumpliendo con las

operaciones aritmticas y operaciones lgicas diseadas visualizadas sus salidas

haciendo uso de displays.

II.5.

Resultados obtenidos

Se obtuvo el funcionamiento de la unidad aritmtica lgica en la cual se cumpli

satisfactoriamente con la suma, la multiplicacin, la divisin comparacin, el contador

y el registro.

La resta no se pudo realiz ya que no cumpli con su funcionamiento correcto debido

que su diseo fue compleja.

Un ALU recibe en su entrada datos los cuales son comparados para realizar una

Todas las etapas de las operaciones aritmticas se realiz el ingreso de los nmeros A y

B con su parte entera y su parte decimal respectivamente los procesa para realizar dicha

operacin la cual es visualizada en display con su parte entera y decimal.

II.6.

Conclusiones

Empleando los fundamentos del diseo digital se logr hallar e implementar el circuito

requerido para adquirir los resultados de operaciones aritmticas y operaciones lgicas

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Al disear e implementar el circuito de dos nmeros de 4 bits se debe tener en cuenta

que si el nmero ingresado en cualquier operacin es mayor que 9 el resultado no es

vlido.

Un ALU recibe en su entrada datos los cuales son comparados para realizar una

operacin bsica.

En la etapa de seleccin se hizo uso de multiplexores para poder escoger el tipo de

operacin que se desee realizar al ingresar los datos y comprobar que todas las

operaciones funcionen correctamente.

II.7.

Recomendaciones

II.8.

Verificar el correcto funcionamiento de los integrados antes de implementar.

Tener todos los materiales y dispositivos necesarios para efectuar la implementacin.

Hacer uso de los datasheet para realizar una correcta conexin.

Antes de implementar verificar el correcto funcionamiento en el simulador.

Tener paciencia al momento de implementar.

Referencias Bibliogrficas

[1] IV congreso Microelectrnica aplicada uEA -2013

[2] Fundamentos de los microprocesadores, 2da Edicin Roger L. Tokheim

[3] Aprendizaje de microprocesadores con PC, 2da Edicin F-J Varela Martnez

[4] Electrnica digital fundamental ,3ra Edicin Antonio Hermosa Donate.

[5] Fundamentos de sistemas digital ,9na Edicin Floyd.

[6] Unidada aritmtica lgica recopilado de: http://www.uned.es/cabergara/ppropias/Morillo/web_etc_II/4_alu/transp_alu.pdf

[7] Arquitectura de computadores recopilado de:

http://atc2.aut.uah.es/~avicente/asignaturas/ac/pdf/ac_t3.pdfpdf

2.6.

Anexos

FACULTAD DE INGENIERIA EN SISTEMAS, ELECTRONICA E INDUSTRIAL

UNIVERSIDAD TCNICA DE AMBATO

F . I . S . E E. INDUSTRIAL

I

FACULTAD DE INGENIERA EN SISTEMAS, ELECTRNICA

PERODO ACADMICO: ABRIL/2015 SEPTIEMBRE/2015

Você também pode gostar

- VPN SiemensDocumento39 páginasVPN SiemensWilson ManobandaAinda não há avaliações

- Informe Codigo PreestablecidoDocumento7 páginasInforme Codigo PreestablecidoWilson ManobandaAinda não há avaliações

- Proyecto Final Dimmer Motor RevisadoDocumento14 páginasProyecto Final Dimmer Motor RevisadoWilson ManobandaAinda não há avaliações

- Modulador PSKDocumento8 páginasModulador PSKWilson ManobandaAinda não há avaliações

- Conversores EstaticosDocumento19 páginasConversores EstaticosWilson ManobandaAinda não há avaliações

- Informe BooteableDocumento6 páginasInforme BooteableWilson Manobanda0% (1)

- Teoria Probabilidad PDFDocumento7 páginasTeoria Probabilidad PDFJoel PalosAinda não há avaliações

- Taller 6 MateBas CH CE CSDocumento3 páginasTaller 6 MateBas CH CE CSEira YulianaAinda não há avaliações

- Explicación Del RPN de FMEA - Tarea 4Documento5 páginasExplicación Del RPN de FMEA - Tarea 4Sergio LoayzaAinda não há avaliações

- Planificacion Individual Anual Alumno Nee Permanente Pie 2017Documento3 páginasPlanificacion Individual Anual Alumno Nee Permanente Pie 2017Ruben Quisbert EspindolaAinda não há avaliações

- Practica 1 Chavez Malena Comunicaciones AnalogicasDocumento8 páginasPractica 1 Chavez Malena Comunicaciones AnalogicasVázquez García Naomi QuetzalliAinda não há avaliações

- Máquinas Eléctricas 1-2015 (Modo de Compatibilidad) PDFDocumento164 páginasMáquinas Eléctricas 1-2015 (Modo de Compatibilidad) PDFJulián Palacios BarreroAinda não há avaliações

- Plano CartesianoDocumento2 páginasPlano CartesianoKarina MuleroAinda não há avaliações

- Triángulos CongruentesDocumento5 páginasTriángulos Congruentesgohanuhernandes hernandesAinda não há avaliações

- Prueba Multiplicación 4toDocumento2 páginasPrueba Multiplicación 4toPamela ÁvilaAinda não há avaliações

- Nrf-174-Pemex-2007-F1 (Helipuertos)Documento23 páginasNrf-174-Pemex-2007-F1 (Helipuertos)jpcc1986Ainda não há avaliações

- La RectaDocumento5 páginasLa RectaLcccccccccAinda não há avaliações

- Ejercicios 20-28Documento22 páginasEjercicios 20-28angelo pialuisaAinda não há avaliações

- PolipastoDocumento3 páginasPolipastoJosse CeervantesAinda não há avaliações

- Metodo de Los Elementos Finitos en El Analisis Estructural de Porticos Con Muros de CorteDocumento64 páginasMetodo de Los Elementos Finitos en El Analisis Estructural de Porticos Con Muros de CorteGaby VinuezaAinda não há avaliações

- Taller N 1 Cálculo Diferencial: Clasificación de Problemas: N Básico, Medio, F RetoDocumento3 páginasTaller N 1 Cálculo Diferencial: Clasificación de Problemas: N Básico, Medio, F RetobreinerAinda não há avaliações

- Metodos Numericos - Resumen Capitulo 5Documento9 páginasMetodos Numericos - Resumen Capitulo 5Lindon Emil Castillo BurgosAinda não há avaliações

- Solucionario CalvacheDocumento13 páginasSolucionario CalvacheRicardo EmilioAinda não há avaliações

- Deber VLSIDocumento7 páginasDeber VLSIAlex LamiñoAinda não há avaliações

- Actividad 3 Estadistica DescriptivaDocumento13 páginasActividad 3 Estadistica DescriptivaLewis GOMEZAinda não há avaliações

- HernandezFelipe GabrielAlejandro M12S2AI3Documento6 páginasHernandezFelipe GabrielAlejandro M12S2AI3laura hernandez felipe0% (1)

- Números FraccionariosDocumento2 páginasNúmeros FraccionariosLuis Enrique Lara MorenoAinda não há avaliações

- Preguntas Orientadoras ElasticidadDocumento7 páginasPreguntas Orientadoras ElasticidadMartin HerreraAinda não há avaliações

- Tema 1Documento6 páginasTema 1AitorAinda não há avaliações

- Población 2019Documento31 páginasPoblación 2019Pedro Manuel RamAinda não há avaliações

- Mapa Conceptual de La Naturaleza de Las MatematicasDocumento2 páginasMapa Conceptual de La Naturaleza de Las MatematicasCesar0% (1)

- Plantilla Trabajo S6 - DeccDocumento7 páginasPlantilla Trabajo S6 - DeccDaisy E ContrerasAinda não há avaliações

- Física I Y Laboratorio - Paralelo "C" Práctica Nº1: InstruccionesDocumento3 páginasFísica I Y Laboratorio - Paralelo "C" Práctica Nº1: InstruccionesMarializ HuallpaAinda não há avaliações

- Caminatas en DiagráficasDocumento16 páginasCaminatas en DiagráficasPanda100% (1)

- Antena YugiDocumento13 páginasAntena YugiNeo RodriguezAinda não há avaliações

- Características Reológicas de AlimentosDocumento20 páginasCaracterísticas Reológicas de AlimentosJunior Artur Carmen VilelaAinda não há avaliações

- Laboratorio de Fisica MecanicaDocumento9 páginasLaboratorio de Fisica MecanicaYamile Lobo Marquez77% (13)