Escolar Documentos

Profissional Documentos

Cultura Documentos

Assignment 1 VLSI

Enviado por

arafatasghar0 notas0% acharam este documento útil (0 voto)

53 visualizações4 páginasFirst Assignment

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

DOCX, PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoFirst Assignment

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato DOCX, PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

53 visualizações4 páginasAssignment 1 VLSI

Enviado por

arafatasgharFirst Assignment

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato DOCX, PDF, TXT ou leia online no Scribd

Você está na página 1de 4

Description and Uses of Open Source VLSI Libraries

Arafat Asghar, Tariq Mehmood, and Tahir Hussain.

AbstractThis paper examines open source VLSI libraries

from a physical design perspective. The concept of a cell is

discussed as a basic unit of a library. Different categories of

libraries are discussed with respect to their process and

functionality. A cell of from library is examined and

discussed in detail.

Index TermsVLSI, ASIC, Layout, Process, EDA, CAD,

Logic, Gates, DRC, Standard Cells, Libraries, Open Source.

CMOS. TSMC, MOSIS, Cadence, Synopsis, VTVT.

I.

INTRODUCTION

ery Large Scale Integration (VLSI) chips are

categorized by the design methodology applied to

manufacture them. A full-custom design requires

every individual circuit to be custom built thereby rendering it

significantly complex, time consuming, and impractical to

execute [1].

Application-specific integrated circuits (ASICs) are

customized for a particular use, rather than intended for

general-purpose [2]. Knowledge of underlying electronics is

unavailable to the designer therefore delay times, along with

other physical constraints cannot be changed or optimized.

A semi-custom design allows for a reasonable tradeoff

between full-custom design and ASIC design. Predefined

primitive cells that have already been developed and tested are

used as basic building blocks for complex circuits. Designers

save time by reuse of these cells. If and when required, the

cell(s) can be modified or reconfigured to meet the desired

system characteristics.

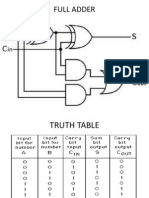

A cell is a compact layout for basic logic gate(s) (such as

NOR gates) and small networks that are frequently used (such

as flip-flops and full adders). A collection of these layouts

forms a part of the cell library [3].

A standard cell library is designed to have a set of logical

functions/gates that cover an adequate range. Libraries

generally have 100 to 1000 cell types so that functions can be

implemented in more than one way. The complexity of a cells

function is determined largely by the size of the cell.

A standard cell library must contain at least NAND, NOR,

NOT and Delay Flip Flops (DFFs) to be able to implement

any function [4]. Input/Output Cells consisting of input pads,

output pads, and bidirectional pads may also be present.

Figure 1 shows these gates as cell blocks.

This work was submitted as part of a graduate course assignment on

Advance VLSI Design. Arafat Asghar is a graduate student at the Center For

Advanced Studies in Engineering, Islamabad, Pakistan and works as a Lab

Engineer at Hamdard University, Islamabad Campus (e-mail: arafat_asghar@

hotmail.com).

Tariq Mehmood, is a graduate student at the Center For Advanced Studies

in Engineering, Islamabad, Pakistan (e-mail: engr.tariq127@gmail.com).

Tahir Hussain is a graduate student at the Center For Advanced Studies in

Engineering, Islamabad, Pakistan and works as a Software Engineer at (email: author@nrim.go.jp).

In addition full layouts, spice models, Verilog Hardware

Description Language (VHDL) Vital models, Parasitic

Extraction models, Design Rule Checks (DRCs) and Layout

Versus Schematic (LVS) checks may also be present. This

information is needed to allow interoperability across different

Computer Aided Design (CAD) tools. CAD or Electronic

Design Automation tools use libraries to automate synthesis,

placement, and routing of a digital VLSI chip.

Within the same library, standard cells share the same

height, and the placement tool creates rows of cells, each cell

adjoining its neighbor.

Libraries are characterized according to the Library

Fig. 6. Layout Using Cell Concepts

Database and Timing Abstract. Library Database contains all

of the above mentioned information while Timing Abstract

provides functional definitions, timing, power, and noise

information for each cell.

The library is developed and distributed either

commercially or in open source format [5]. Commercial

library cells are companies proprietary information, and

understandably, companies usually impose certain restrictions

on the access and use of their library cells. These restrictions

on commercial library cells restrict VLSI research and

teaching activities of academia [6]. Open source libraries

overcomes these restrictions by promoting universal access via

free license to the library design and universal redistribution of

this design, including subsequent improvements to it by any

individual, research group or company [7].

In the following paragraphs, various libraries and their

constituent cells are briefly reviewed.

II. LIBRARY TYPES AND DESIGNS

Virginia Tech VLSI for Telecommunications (VTVT) group

has developed two standard-cell libraries targeting the Taiwan

Semiconductor Manufacturing Company (TSMC) 0.18um and

TSMC 0.25um CMOS processes available via Metal Oxide

Semiconductor Implementation Service (MOSIS).

A. VTVT 0.25m Standard Cell Library

(vtvt_tsmc250)

This standard cell library is based on the TSMC 0.25um,

2.5V CMOS process, was released on December 21, 2006.

The VTVTs cell library supports a cell-based VLSI design

flow starting from a behavioral description to a layout.

Specifically, it supports major tasks such as logic simulation

and synthesis, place and routing (P&R), and layout versus

schematic (LVS). The VTVTs cell library has been targeted

and tested with Synopsys tools for logic simulation and

synthesis, and with Cadence tools for P&R and physical

design. It has 84 cells including both combinational and

sequential cells with different drive strengths. Some of the

representative cells are listed in Table II [8].

TABLE I

TABLE 1: CELLS CONTAINED IN THE LIBRARY VTVT_TSMC250

Cell Name

Function

buf_[1,2,4]

Noninverting buffer, drive strength 1, 2, or 4

inv_[1,2,4]

Inverter, drive strength 1, 2 or 4

and2_[1,2,4]

2-input AND gate, drive strength 1, 2, or 4

and3_[1,2,4]

3-input AND gate, drive strength 1, 2, or 4

and4_[1,2,4]

4-input AND gate, drive strength 1, 2, or 4

or2_[1,2,4]

2-input OR gate, drive strength 1, 2, or 4

or3_[1,2,4]

3-input OR gate, drive strength 1, 2, or 4

or4_[1,2,4]

4-input OR gate, drive strength 1, 2, or 4

nand2_[1,2,4]

2-input NAND gate, drive strength 1, 2, or 4

nand3_[1,2,4]

3-input NAND gate, drive strength 1, 2, or 4

nand4_[1,2,4]

4-input NAND gate, drive strength 1, 2, or 4

nor2_[1,2,4] 2

input NOR gate, drive strength 1, 2, or 4

nor3_[1,2,4]

3-input NOR gate, drive strength 1, 2, or 4

nor4_[1,2,4]

4-input NOR gate, drive strength 1, 2, or 4

xor2_[1,2]

2-input XOR gate, drive strength 1 or 2

xnor2_[1,2]

2-input XNOR gate, drive strength 1 or 2

mux2_[1,2,4]

2-to-1 multiplexer, drive strength 1, 2, or 4

mux3_2

3-to-1 multiplexer, drive strength 2

mux4_2

4-to-1 multiplexer, drive strength 2

ABnorC

(ip1*ip2+ip3), drive strength 1

ABorC

ip1*ip2+ip3, drive strength 1

ab_or_c_or_d

ip1*ip2+ip3+ip4, drive strength 1

Not_ab_or_c_or_d

(ip1*ip2+ip3+ip4), drive strength 1

fulladder

One-bit ripple-carry adder, drive strength 1

bufzp_2

noninverting tristate buffer, low-enabled,

drive strength 2

invzp_[1,2,4]

inverting tristate buffer, low-enabled, drive

strength 1, 2, or 4

cd_8

clock driver, drive strength 8

cd_12

clock driver, drive strength 12

cd_16

clock driver, drive strength 16

lp_[1,2]

high-active D latch, drive strength 1 or 2

Lrp_[1, 2, 4]

high-active D latch with asynchronous lowactive reset and drive strength 1, 2, or 4

Lrsp_[1, 2, 4]

high-active D latch with asynchronous lowactive reset and asynchronous high-active

set, drive strength 1, 2, or 4

Dp_[1,2,4]

rising-edge triggered D flip-flop (with 1, 2,

or 4 drive strength)

Drp_[1,2,4]

rising-edge triggered D flip-flop with

asynchronous low-active reset (1, 2, or 4

drive strength)

drsp_[1,2,4]

rising-edge triggered D flip-flop with

asynchronous low-active reset and

asynchronous high-active set

dksp_1

rising-edge triggered D flip-flop with

asynchronous active high set and extra

inverted output.

dtsp_1

rising-edge triggered D flip-flop with

asynchronous active high set input and serial

scan input.

dtrsp_2

rising-edge triggered D flip-flop with

asynchronous low-active reset, asynchronous

jkrp_2

Filler

high-active set, and serial scan input

rising-edge triggered JK flip-flop with

asynchronous active-low reset and extra

inverted output, drive strength 2.

filler cell (empty cell with power and ground

rails and nwell

VTVT library based on the TSMC 0.18um, 1.8V CMOS

process was on had all of the above mentioned features with

the only improvement being the reduction of process size and

power supply.

B. NanGate 45nm Open Cell Library

The Nangate Open Cell library is a generic open-source,

standard-cell library provided for the purposes of research,

testing, and exploring EDA flows. It was officially released on

March 3, 2008.

Salient features of this library include: 1) Liberty formatted

libraries with Composite Current Source (CCS) Timing,

Effective Current Source Model (ECSM) Timing and NonLinear Delay Model (NLDM)/Non-Linear Power Models

(NLPM) data (slow, typical, fast, low temperature and worst

low temperature corners); 2) Geometric library in LEF; 3)

Simulation libraries in Verilog and Spice (pre and post

parasitic extracted netlists); 4) Cell layouts in Graphic Data

System (GDSII); 5) Schematics in Electronic Design

Interchange Format (EDIF) and Portable Network Graphics

(PNG) formats; 6) Library databook in Hypertext Markup

Language (HTML) format; and 7) Open-Access database

containing layouts and netlists.

The library contains the following cells types where all cell

functions come in multiple drive strength variants as listed in

Table 3[9].

TABLE III

TABLE 3: CELLS CONTAINED IN THE 45NM OPEN CELL LIBRARY

Always-on cell

Isolation cell

Level-shifter cell

Power-switch (header) cell

A special circuit located in a

switched-off domain, and whose

power supply is continuous even

when the power supply for the

remaining logic in the power domain

is off.

A circuit used to isolate signals

between two power domains where

one is switched on and one is

switched off. The most common

usage of such cells is to isolate

signals originating in a power

domain that is being switched off,

from the power domain that receives

these signals and that remains

switched on.

Logic to pass data signals between

power domains operating at different

voltages (or levels).

Logic used to connect and disconnect

the power supply from the gates in a

power domain.

III. CELL DESCRIPTION OF VTVT_TSMC250 LIBRARY

Figure 2 through Figure 4 show cell views of 2-input AND

gates with different driving strengths.

Figure 2: 2-input AND gate with driving strength 2

Drive

strength

Fig. 2. 2-input AND gate with driving strength 1

is the

Figure 3: 2-input AND gate with driving strength 4

capacity of a cell to drive a value to the cell connected to its

output. Different sizes of standard cells have different

capacitance, smaller cells have small capacitance and vice

versa. It is simpler to drive a small cell than a large one. The

load connected at the output of a cell is the combined

capacitance of all the cells connected at the output. So larger

the load, larger is the drive required to "force" the values at the

output.

From another point of view, it is just the strength required to

charge/discharge the capacitance at the output to the required

value. Greater the drive strength, higher current can be drawn

from the supply and the output capacitors can be charged

quickly, if drive strength is low, then the current is less and the

output capacitance takes time to charge/discharge.

Table III below gives a list of rules which were adopted for

the design of the cells in the library. The value lambda ()

design rule is kept at 0.12m.

Metal Width

Metal Offset

Power/Ground Pins/Rails

IV. SUMMARY AND CONCLUSION

The concept of library and cell was discussed with an

emphasis on open source designs. Two examples of open

source standard cell libraries were presented. Finally cell

designs with their physical layouts and defining characteristics

from one of the libraries were specifically shown.

REFERENCES

[1]

TABLE III

TABLE 3: RULES FOR CELL LAYOUTS

Cell Design

Cell Height

Cell Width

Metal Pitch

Settings Values

108

Multiple of 9

9 for metal 1 through metal

4, 18 for metal 5

4 for all layers

0 for all layers

11 for VDD and VSS

[3]

[4]

[5]

[6]

[7]

[8]

[9]

J. P. Uyemara, Introduction to VLSI Circuits and Systems, Atlanta, GA,

2001.

[2] http://en.wikipedia.org/wiki/Applicationspecific_integrated_circuit

W.K. Chen, The VLSI Handbook, Boca Raton, FL, 2007

ece.unm.edu/~jimp/vlsi_synthesis/contrib/MissStateStdCellTut.ppt

http://en.wikipedia.org/wiki/Standard_cell.

http://www.vtvt.ece.vt.edu/research/papers/07TSMC.pdf

http://en.wikipedia.org/wiki/Open_source

http://www.vtvt.ece.vt.edu/vlsidesign/cell.php

http://www.nangate.com/?page_id=22 Example:

Você também pode gostar

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Pension Papers Complete For Fresh RetirementDocumento19 páginasPension Papers Complete For Fresh RetirementarafatasgharAinda não há avaliações

- Laboratory Alert - 20e32 Heating Test - TransformersDocumento2 páginasLaboratory Alert - 20e32 Heating Test - TransformersarafatasgharAinda não há avaliações

- MATLAB Workshop Lecture 2Documento35 páginasMATLAB Workshop Lecture 2arafatasgharAinda não há avaliações

- Infineon BSC093N04LSG DS v02 01 enDocumento10 páginasInfineon BSC093N04LSG DS v02 01 enarafatasgharAinda não há avaliações

- Sun2014 PDFDocumento3 páginasSun2014 PDFarafatasgharAinda não há avaliações

- Distance 12Documento4 páginasDistance 12arafatasgharAinda não há avaliações

- Quickcmc3: Test ModuleDocumento4 páginasQuickcmc3: Test ModulearafatasgharAinda não há avaliações

- Hacking VoIP ExposedDocumento57 páginasHacking VoIP ExposedarafatasgharAinda não há avaliações

- Ee 701 Lecture NotesDocumento261 páginasEe 701 Lecture NotesarafatasgharAinda não há avaliações

- Rad e Rawafiz (Refutation of Ithna Ashari Creed)Documento63 páginasRad e Rawafiz (Refutation of Ithna Ashari Creed)arafatasgharAinda não há avaliações

- Summer Time TableDocumento3 páginasSummer Time TablearafatasgharAinda não há avaliações

- Islami Saqafat Aur Dore JadeedDocumento211 páginasIslami Saqafat Aur Dore JadeedarafatasgharAinda não há avaliações

- Question Bank Linear Control SystemsDocumento15 páginasQuestion Bank Linear Control SystemsarafatasgharAinda não há avaliações

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- Neamen - Electronic Circuit Analysis and Design 2nd Ed Chap 008Documento17 páginasNeamen - Electronic Circuit Analysis and Design 2nd Ed Chap 008greyiris7Ainda não há avaliações

- Microprocessors Chapter 2: Programming With 8085 MicroprocessorDocumento29 páginasMicroprocessors Chapter 2: Programming With 8085 MicroprocessorDere JesusAinda não há avaliações

- 32Kx 4 Bit Ram Using 32K X 1 Bit Rams: Data inDocumento9 páginas32Kx 4 Bit Ram Using 32K X 1 Bit Rams: Data inHata MadžakAinda não há avaliações

- EE6301-Digital Logic Circuits QBDocumento7 páginasEE6301-Digital Logic Circuits QBariv2009Ainda não há avaliações

- Which Among Following Can Be Considered As Most Advanced ROM ?Documento5 páginasWhich Among Following Can Be Considered As Most Advanced ROM ?Krishnakumar VeerabathranAinda não há avaliações

- 74HC195Documento10 páginas74HC195MUHAMMAD SISWANTOROAinda não há avaliações

- DRamDocumento16 páginasDRamshastryAinda não há avaliações

- Butterworth Filters: Polynomials, Poles and Circuit ElementsDocumento4 páginasButterworth Filters: Polynomials, Poles and Circuit ElementsFregone FregoAinda não há avaliações

- EE342 13 ProjectsDocumento10 páginasEE342 13 ProjectsherrberkAinda não há avaliações

- ZXURR-Installation InstructionsDocumento2 páginasZXURR-Installation InstructionsRafa manchoiAinda não há avaliações

- Full AdderDocumento4 páginasFull AdderMuniba Ahmad0% (1)

- Service Manual: SharpDocumento21 páginasService Manual: SharpMarco MinottiAinda não há avaliações

- DSP Builder Handbook Volume 1: Introduction To DSP BuilderDocumento18 páginasDSP Builder Handbook Volume 1: Introduction To DSP BuildermauricetaAinda não há avaliações

- Digital Electronics AssignmentDocumento1 páginaDigital Electronics Assignmentbskr4s100% (2)

- (Biasing Bipolar Junction Transistors) : Electronics Lab-Experiment 6Documento5 páginas(Biasing Bipolar Junction Transistors) : Electronics Lab-Experiment 6Mhmd MsttAinda não há avaliações

- Array ProcessorsDocumento3 páginasArray ProcessorsAastha Kohli0% (1)

- AddersDocumento5 páginasAddersShanuj GargAinda não há avaliações

- Docs Openhwgroup Org Openhw Group Cv32e41p en LatestDocumento100 páginasDocs Openhwgroup Org Openhw Group Cv32e41p en LatestSaheba ShaikAinda não há avaliações

- VLSI Lab ManualDocumento46 páginasVLSI Lab ManualPriyam JainAinda não há avaliações

- Digital Fundamentals CHAPTER 7 Latches FDocumento39 páginasDigital Fundamentals CHAPTER 7 Latches FNurul Syifa Bt EdrussalamAinda não há avaliações

- DFT Interview QuestionsDocumento2 páginasDFT Interview Questionsjagruthims75% (4)

- Verilog ManalDocumento16 páginasVerilog Manalj4everAinda não há avaliações

- K9G8G08B0B SamsungDocumento43 páginasK9G8G08B0B SamsungThienAinda não há avaliações

- Lec17 FSM PDFDocumento27 páginasLec17 FSM PDFNithin KumarAinda não há avaliações

- XC4000XLA/XV Field Programmable Gate Arrays: This Datasheet Has Been Downloaded From at ThisDocumento14 páginasXC4000XLA/XV Field Programmable Gate Arrays: This Datasheet Has Been Downloaded From at ThisMasood Ur RehmanAinda não há avaliações

- Comparison of MicrocontrollerDocumento5 páginasComparison of MicrocontrollerGitesh MisalAinda não há avaliações

- Assignment 2Documento10 páginasAssignment 2Vishakh BharadwajAinda não há avaliações

- Lec 5Documento8 páginasLec 5Elisée NdjabuAinda não há avaliações

- BDSSSSSSDocumento66 páginasBDSSSSSSshanmukhasaiAinda não há avaliações

- UNIT 1 - Introduction To EDA ToolsDocumento16 páginasUNIT 1 - Introduction To EDA ToolsMonali NiphadeAinda não há avaliações