Escolar Documentos

Profissional Documentos

Cultura Documentos

Imd3 Booths Algorithm

Enviado por

Alzheimer B. BoonthDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Imd3 Booths Algorithm

Enviado por

Alzheimer B. BoonthDireitos autorais:

Formatos disponíveis

IMD 3.

11-1

In More Depth

In More Depth

In More Depth: Booths Algorithm

A more elegant approach to multiplying signed numbers than above is called

Booths algorithm. It starts with the observation that with the ability to both add

and subtract there are multiple ways to compute a product. Suppose we want

to multiply 2ten by 6ten, or 0010two by 0110two:

0010two

0110two

+

0000

+

0010

+ 0010

+ 0000

shift

add

add

shift

(0

(1

(1

(0

in

in

in

in

multiplier)

multiplier)

multiplier)

multiplier)

00001100two

Booth observed that an ALU that could add or subtract could get the same

result in more than one way. For example, since

6ten = 2ten + 8ten

or

0110two = 0010two + 1000two

we could replace a string of 1s in the multiplier with an initial subtract when we

first see a 1 and then later add when we see the bit after the last 1. For example,

x

0010two

0110two

+

0000

0010

+ 0000

+0010

00001100two

shift (0 in multiplier)

sub (first 1 in multiplier)

shift (middle of string of 1s)

add (prior step had last 1)

IMD 3.11-2

In More Depth

Booth invented this approach in a quest for speed because in machines of

his era shifting was faster than addition. Indeed, for some patterns his algorithm would be faster; its our good fortune that it handles signed numbers as

well, and well prove this later. The key to Booths insight is in his classifying

groups of bits into the beginning, the middle, or the end of a run of 1s:

Middle of run

End of run

Beginning of run

0

1 1

Of course, a string of 0s already avoids arithmetic, so we can leave these

alone.

If we are limited to looking at just 2 bits, we can then try to match the situation in the preceding drawing, according to the value of these 2 bits:

If we are limited to looking at just 2 bits, we can then try to match the situation in the preceding drawing, according to the value of these 2 bits:

Current bit

Bit to the right

Explanation

Example

Beginning of a run of 1s 00001111000two

Middle of a run of 1s

00001111000two

End of a run of 1s

00001111000two

Middle of a run of 0s

00001111000two

Booths algorithm changes the first step of the algorithmlooking at 1 bit of

the multiplier and then deciding whether to add the multiplicandto looking

at 2 bits of the multiplier. The new first step, then, has four cases, depending on

the values of the 2 bits. Lets assume that the pair of bits examined consists of

the current bit and the bit to the rightwhich was the current bit in the previous step. The second step is still to shift the product right. The new algorithm is

then the following:

1. Depending on the current and previous bits, do one of the following:

00:

Middle of a string of 0s, so no arithmetic operation.

01:

End of a string of 1s, so add the multiplicand to the left half of the

product.

10:

Beginning of a string of 1s, so subtract the multiplicand from the

left half of the product.

11:

Middle of a string of 1s, so no arithmetic operation.

2. As in the previous algorithm, shift the Product register right 1 bit.

IMD 3.11-3

In More Depth

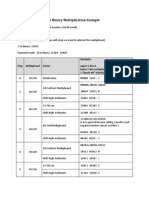

Now we are ready to begin the operation, shown in Figure 3.11.2. It starts

with a 0 for the mythical bit to the right of the rightmost bit for the first stage.

Figure 3.11.2 compares the two algorithms, with Booths on the right. Note

that Booths operation is now identified according to the values in the 2 bits. By

the fourth step, the two algorithms have the same values in the Product register.

The one other requirement is that shifting the product right must preserve

the sign of the intermediate result, since we are dealing with signed numbers.

The solution is to extend the sign when the product is shifted to the right.

Thus, step 2 of the second iteration turns 1110 0011 0two into 1111 0001 1two

instead of 0111 0001 1two. This shift is called an arithmetic right shift to differentiate it from a logical right shift.

Original algorithm

Booths algorithm

Iteration

Multiplicand

0010

Initial values

0000 0110

Initial values

0000 0110 0

0010

1: 0 no operation

0000 0110

1a: 00 no operation

0000 0110 0

Step

Product

Step

Product

0010

2: Shift right Product

0000 0011

2: Shift right Product

0000 0011 0

0010

1a: 1 Prod = Prod + Mcand

0010 0011

1c: 10 Prod = Prod Mcand

1110 0011 0

0010

2: Shift right Product

0001 0001

2: Shift right Product

1111 0001 1

0010

1a: 1 Prod = Prod + Mcand

0011 0001

1d: 11 no operation

1111 0001 1

0010

2: Shift right Product

0001 1000

2: Shift right Product

1111 1000 1

0010

1: 0 no operation

0001 1000

1b: 01 Prod = Prod + Mcand

0001 1000 1

0010

2: Shift right Product

0000 1100

2: Shift right Product

0000 1100 0

FIGURE 3.11.2 Comparing algorithm in Booths algorithm for positive numbers. The bit(s) examined to determine the

next step is circled in color.

Booths Algorithm

Lets try Booths algorithm with negative numbers: 2ten 3ten = 6ten, or

0010two 1101two = 1111 1010two.

Figure 3.11.3 shows the steps.

EXAMPLE

ANSWER

IMD 3.11-4

In More Depth

Iteration

Step

Multiplicand

Product

0010

0000 1101 0

1c: 10 Prod = Prod Mcand

0010

1110 1101 0

2: Shift right Product

0010

1111 0110 1

1b: 01 Prod = Prod + Mcand

0010

0001 0110 1

2: Shift right Product

0010

0000 1011 0

1c: 10 Prod = Prod Mcand

0010

1110 1011 0

2: Shift right Product

0010

1111 0101 1

1d: 11 no operation

0010

1111 0101 1

2: Shift right Product

0010

1111 1010 1

Initial values

1

2

FIGURE 3.11.3 Booths algorithm with negative multiplier example. The bits examined to determine the next step are circled in color.

Our example multiplies one bit at a time, but it is possible to generalize

Booths algorithm to generate multiple bits for faster multiplies (see Exercise

3.50)

Now that we have seen Booths algorithm work, we are ready to see why it

works for twos complement signed integers. Let a be the multiplier and b be

the multiplicand and well use ai to refer to bit i of a. Recasting Booths algorithm in terms of the bit values of the multiplier yields this table:

ai

ai1

Operation

Do nothing

Add b

Subtract b

Do nothing

Instead of representing Booths algorithm in tabular form, we can represent it

as the expression

(ai1 ai)

where the value of the expression means the following actions:

0 : do nothing

+1: add b

1: subtract b

Since we know that shifting of the multiplicand left with respect to the Product

register can be considered multiplying by a power of 2, Booths algorithm can

be written as the sum

IMD 3.11-5

In More Depth

+

+

...

+

+

(a1

(a0

(a1

...

(a29

(a30

a0) b 20

a1) b 21

a2) b 22

a30) b 230

a31) b 231

We can simplify this sum by noting that

ai 2 i+ ai 2 i + 1 = (ai + 2ai) 2 i = (2ai ai) 2 i = ai 2i

recalling that a1 = 0 and by factoring out b from each term:

b ((a31 231) + (a30 230) + (a29 229) + . . . + (a1 21) + (a0 20))

The long formula in parentheses to the right of the first multiply operation is

simply the twos complement representation of a (see page 163). Thus, the sum

is further simplified to

ba

Hence, Booths algorithm does in fact perform twos complement multiplication of a and b.

3.23 [30] <3.6> The original reason for Booths algorithm was to reduce the

number of operations by avoiding operations when there were strings of 0s and

1s. Revise the algorithm on page IMD 3.11-2 to look at 3 bits at a time and compute the product 2 bits at a time. Fill in the following table to determine the 2-bit

Booth encoding:

Current bits

Previous bit

ai+1

ai

ai1

Operation

Reason

Assume that you have both the multiplicand and 2 multiplicand already in

registers. Explain the reason for the operation on each line, and show a 6-bit

example that runs faster using this algorithm. (Hint: Try dividing to conquer;

see what the operations would be in each of the eight cases in the table using a

2-bit Booth algorithm, and then optimize the pair of operations.)

Você também pode gostar

- Booth MultiplierDocumento5 páginasBooth Multiplierrahul rAinda não há avaliações

- Booth's Multiplication AlgorithmDocumento27 páginasBooth's Multiplication AlgorithmNikita vermaAinda não há avaliações

- COA Mod 3Documento30 páginasCOA Mod 3BasithAinda não há avaliações

- BoothDocumento14 páginasBoothFarhat VooDooAinda não há avaliações

- 9 Multiplication and DivisionDocumento11 páginas9 Multiplication and DivisionAkhilReddy SankatiAinda não há avaliações

- Booth AlgDocumento7 páginasBooth AlgSivajisadhana SadhanaAinda não há avaliações

- Mod 1Documento29 páginasMod 1Abin KurianAinda não há avaliações

- COA Unit 2Documento25 páginasCOA Unit 2Shivam KumarAinda não há avaliações

- Computer Arithmetic 1. Addition and Subtraction of Unsigned NumbersDocumento19 páginasComputer Arithmetic 1. Addition and Subtraction of Unsigned NumbersSai TrilokAinda não há avaliações

- CSI - 03b - OperationsDocumento36 páginasCSI - 03b - OperationsKhanh HungAinda não há avaliações

- Booths AlgoDocumento23 páginasBooths AlgoSanjog ShresthaAinda não há avaliações

- C++ Bitwise OperatorsDocumento19 páginasC++ Bitwise OperatorsÄbûýé SêñdèkúAinda não há avaliações

- PPTDocumento9 páginasPPTsindhuvindhya100% (1)

- Booth MultiplierDocumento14 páginasBooth MultiplierAhmed WahiedAinda não há avaliações

- Chapter10-Computer ArithmaticDocumento25 páginasChapter10-Computer ArithmaticGeorgian ChailAinda não há avaliações

- Booth RecodingDocumento4 páginasBooth RecodingGurumurthy JaAinda não há avaliações

- MultiplierDocumento19 páginasMultiplierDwaraka OrugantiAinda não há avaliações

- Floating Point AluDocumento11 páginasFloating Point Aluthuan phamAinda não há avaliações

- COS101 Module 4Documento20 páginasCOS101 Module 4Daniel olayioyeAinda não há avaliações

- Bit Manipulation TutorialDocumento5 páginasBit Manipulation TutorialSumitra BiswalAinda não há avaliações

- MultipliersDocumento19 páginasMultipliersDwaraka OrugantiAinda não há avaliações

- Building The ALUDocumento11 páginasBuilding The ALUGiacomo BecattiAinda não há avaliações

- DRO-Lesson 09 - Negative Numbers Representation Part 3fchsDocumento26 páginasDRO-Lesson 09 - Negative Numbers Representation Part 3fchsRifky AhmedAinda não há avaliações

- 2.2 Multiplication & Division PDFDocumento28 páginas2.2 Multiplication & Division PDFGireesh DgAinda não há avaliações

- Floating Point ExampleDocumento2 páginasFloating Point Exampleanukriti meenaAinda não há avaliações

- Subtract SubtractorDocumento3 páginasSubtract SubtractorJannel SalvaAinda não há avaliações

- COA Mod 3Documento25 páginasCOA Mod 3Rosh Roy GeorgeAinda não há avaliações

- Pipelining - Basic Principles, Classification of Pipeline ProcessorsDocumento30 páginasPipelining - Basic Principles, Classification of Pipeline ProcessorsJoel K SanthoshAinda não há avaliações

- Running Addition ON Partial-Products (Multiplication)Documento16 páginasRunning Addition ON Partial-Products (Multiplication)Niel Roel VelascoAinda não há avaliações

- Booth AlgorithmDocumento25 páginasBooth AlgorithmSanvi Singh ChauhanAinda não há avaliações

- Unit - Ii Arithmetic For ComputersDocumento28 páginasUnit - Ii Arithmetic For ComputersAlexander Rueda OrduzAinda não há avaliações

- Computer Architecture Number RepresentationsDocumento74 páginasComputer Architecture Number RepresentationsLuciusAinda não há avaliações

- COA Module4Documento26 páginasCOA Module4Aditya Dhanaraj KunduAinda não há avaliações

- CPT111 2021-2022Documento98 páginasCPT111 2021-2022omotayo emmanuelAinda não há avaliações

- CS205 Assignment1 SolutionDocumento7 páginasCS205 Assignment1 SolutionjohnnybyzhangAinda não há avaliações

- Array MultiplierDocumento10 páginasArray MultiplierVarsha LalapuraAinda não há avaliações

- Pes U: Niversity, BDocumento7 páginasPes U: Niversity, BMilos ArsicAinda não há avaliações

- Presentation EE471 MultiplicationDocumento20 páginasPresentation EE471 MultiplicationVõ Hoàng ChươngAinda não há avaliações

- Chapter Four - Number Systems 2 NDocumento10 páginasChapter Four - Number Systems 2 Nnjamaa91Ainda não há avaliações

- Number SystemDocumento45 páginasNumber Systemhrishipisal0% (1)

- CH 7updated Unit 6 Computer ArithmeticDocumento18 páginasCH 7updated Unit 6 Computer ArithmeticSujan TimalsinaAinda não há avaliações

- Unit-2 Arithmetic Logic Unit (ALU)Documento13 páginasUnit-2 Arithmetic Logic Unit (ALU)Shubham KumarAinda não há avaliações

- Complete-Unit-01-Soft Copy of Notes - Computer Data Representations - CAODocumento15 páginasComplete-Unit-01-Soft Copy of Notes - Computer Data Representations - CAOaayushgithala101Ainda não há avaliações

- Binary Arithmetic - Negative Numbers and Subtraction: Not All Integers Are PositiveDocumento7 páginasBinary Arithmetic - Negative Numbers and Subtraction: Not All Integers Are PositiveBharath ManjeshAinda não há avaliações

- Booth'S Algorithm: (Signed & Unsigned)Documento18 páginasBooth'S Algorithm: (Signed & Unsigned)sakthikothandapaniAinda não há avaliações

- CSC340 - HW3Documento28 páginasCSC340 - HW3Daniel sAinda não há avaliações

- Number System ConversionDocumento12 páginasNumber System Conversiontusharvip2005Ainda não há avaliações

- Addition and SubtractionDocumento26 páginasAddition and SubtractionRam GaneshAinda não há avaliações

- Lec9 Fixed Point RepresentationDocumento19 páginasLec9 Fixed Point RepresentationRaman KalraAinda não há avaliações

- Unit - Ii Arithmetic For ComputersDocumento28 páginasUnit - Ii Arithmetic For Computerssathya priyaAinda não há avaliações

- Module-2 - Lecture 2: Alu - Signed Addition/SubtractionDocumento44 páginasModule-2 - Lecture 2: Alu - Signed Addition/SubtractionWINORLOSEAinda não há avaliações

- CH 4Documento27 páginasCH 4AakarshAinda não há avaliações

- Lab Report D1Documento10 páginasLab Report D1Muhammad Feisal IliasAinda não há avaliações

- ALU Inputs and OutputsDocumento63 páginasALU Inputs and OutputsattappAinda não há avaliações

- ALU ReportDocumento11 páginasALU ReportAzad Kiyal100% (2)

- NumSys Part2Documento25 páginasNumSys Part2sweethome1997Ainda não há avaliações

- Microcomputer Systems I: Dr. Burchard R.B. Bagile B008 CoictDocumento61 páginasMicrocomputer Systems I: Dr. Burchard R.B. Bagile B008 CoictSaid AhmedAinda não há avaliações

- 1 5 4 1TwosComplementReviewDocumento5 páginas1 5 4 1TwosComplementReviewHao AiAinda não há avaliações

- Digital Electronics For Engineering and Diploma CoursesNo EverandDigital Electronics For Engineering and Diploma CoursesAinda não há avaliações

- Modeling and Simulation of Logistics Flows 3: Discrete and Continuous Flows in 2D/3DNo EverandModeling and Simulation of Logistics Flows 3: Discrete and Continuous Flows in 2D/3DAinda não há avaliações

- WickedWhims Info & LicenseDocumento1 páginaWickedWhims Info & LicenseAlzheimer B. BoonthAinda não há avaliações

- !read MeDocumento1 página!read MeAlzheimer B. BoonthAinda não há avaliações

- Install NotesDocumento1 páginaInstall NotesAli Hossain AdnanAinda não há avaliações

- Ableton L10manual enDocumento759 páginasAbleton L10manual enDominic AuAinda não há avaliações

- Dashboard SidePanelDocumento1 páginaDashboard SidePanelAlzheimer B. BoonthAinda não há avaliações

- HP Man CA Suite Premium at A Glance 2014 01 PDFDocumento8 páginasHP Man CA Suite Premium at A Glance 2014 01 PDFAlzheimer B. BoonthAinda não há avaliações

- A. SSD Quota B. SAS Quota C. SATA QuotaDocumento1 páginaA. SSD Quota B. SAS Quota C. SATA QuotaAlzheimer B. BoonthAinda não há avaliações

- VMAutomate 1Documento8 páginasVMAutomate 1Alzheimer B. BoonthAinda não há avaliações

- Aws-Overview Latest PDFDocumento52 páginasAws-Overview Latest PDFmunnazAinda não há avaliações

- Admin OrgDocumento2 páginasAdmin OrgAlzheimer B. BoonthAinda não há avaliações

- Deep Security WebService SDKDocumento163 páginasDeep Security WebService SDKAlzheimer B. BoonthAinda não há avaliações

- Air - Minimal SlidedizerDocumento65 páginasAir - Minimal SlidedizermohammednatiqAinda não há avaliações

- Trend Micro Soap ExampleDocumento6 páginasTrend Micro Soap ExampleAlzheimer B. BoonthAinda não há avaliações

- 1 PDFsam DDD PDFDocumento1 página1 PDFsam DDD PDFAlzheimer B. BoonthAinda não há avaliações

- 2 PDFsam DDD PDFDocumento1 página2 PDFsam DDD PDFAlzheimer B. BoonthAinda não há avaliações

- Vmware ExtDocumento28 páginasVmware ExtRach BoonthAinda não há avaliações

- Vsphere Esxi Vcenter Server 50 Basics GuideDocumento38 páginasVsphere Esxi Vcenter Server 50 Basics Guideastro123321Ainda não há avaliações

- Vsphere Automation SDK 65 Net Programming GuideDocumento70 páginasVsphere Automation SDK 65 Net Programming GuideAlzheimer B. BoonthAinda não há avaliações

- Docker CheatSheet 08.09.2016 0 PDFDocumento1 páginaDocker CheatSheet 08.09.2016 0 PDFArabs AlcaideAinda não há avaliações

- Booth ExampleDocumento1 páginaBooth ExampleRajinder SanwalAinda não há avaliações

- Balistic SomdoonDocumento50 páginasBalistic SomdoonAlzheimer B. BoonthAinda não há avaliações

- Design and Analysis of Algorithms Laboratory Manual-15CSL47 4 Semester CSE Department, CIT-Mandya Cbcs SchemeDocumento30 páginasDesign and Analysis of Algorithms Laboratory Manual-15CSL47 4 Semester CSE Department, CIT-Mandya Cbcs Schemesachu195100% (1)

- Sequencing Problems: Abu BasharDocumento17 páginasSequencing Problems: Abu BasharGabriel RoitoAinda não há avaliações

- AI Lec4Documento17 páginasAI Lec4Asil Zulfiqar 4459-FBAS/BSCS4/F21Ainda não há avaliações

- Tutorial On Neural Network Optimization Problems: Presentation by Ian GoodfellowDocumento42 páginasTutorial On Neural Network Optimization Problems: Presentation by Ian GoodfellowkanchanAinda não há avaliações

- Heuristic SearchDocumento49 páginasHeuristic SearchsaikiranAinda não há avaliações

- CSCE 411H Design and Analysis of Algorithms: Set 8: Greedy Algorithms Prof. Evdokia Nikolova Spring 2013Documento61 páginasCSCE 411H Design and Analysis of Algorithms: Set 8: Greedy Algorithms Prof. Evdokia Nikolova Spring 2013Tanvi SharmaAinda não há avaliações

- Viva QuestionsDocumento12 páginasViva QuestionsVickyGaming YTAinda não há avaliações

- Computer Software MA30007 PDFDocumento2 páginasComputer Software MA30007 PDFYkAinda não há avaliações

- DP 2Documento19 páginasDP 2ADVAITAAinda não há avaliações

- Scientific Writing Parallel Computing V2Documento15 páginasScientific Writing Parallel Computing V2VD MirelaAinda não há avaliações

- Management Science ActivityDocumento7 páginasManagement Science ActivityVixen Aaron Enriquez100% (1)

- Datastructure PRGMDocumento39 páginasDatastructure PRGMMarianinu antonyAinda não há avaliações

- Assessment - 6: Question 1: Write The C Program To Implement A Linked List File Allocation MethodDocumento6 páginasAssessment - 6: Question 1: Write The C Program To Implement A Linked List File Allocation MethodVinayak MahadevanAinda não há avaliações

- Canvas Quiz: Greedy StrategiesDocumento3 páginasCanvas Quiz: Greedy StrategiesChaitanya MagarAinda não há avaliações

- Lec-6 List ADT & Linked ListsDocumento60 páginasLec-6 List ADT & Linked ListsTaqi ShahAinda não há avaliações

- Divide N Conquer and Greedy StrategyDocumento50 páginasDivide N Conquer and Greedy StrategyAbhijit BodheAinda não há avaliações

- Dmitrijs Rutko, Faculty of Computing, University of Latvia: Fuzzified Tree Search in Real Domain GamesDocumento1 páginaDmitrijs Rutko, Faculty of Computing, University of Latvia: Fuzzified Tree Search in Real Domain GamesMorgoth BauglirAinda não há avaliações

- Apriori Algorithm in Data Mining Implementation With ExamplesDocumento13 páginasApriori Algorithm in Data Mining Implementation With Examplesaarthi devAinda não há avaliações

- Doubly Linked ListDocumento10 páginasDoubly Linked Listlakshmi.sAinda não há avaliações

- Section 7: OBJECTIVES: at The End of The Section, The Student Is Expected To Be Able ToDocumento8 páginasSection 7: OBJECTIVES: at The End of The Section, The Student Is Expected To Be Able ToYT PremoneAinda não há avaliações

- Optimal Placement of Valves in A Water Distribution NetworkDocumento3 páginasOptimal Placement of Valves in A Water Distribution NetworkmeshahanAinda não há avaliações

- REGNO:311119106029 Melodina Carnelian D Loyola - Icam College of Engineering and Technology (Licet)Documento6 páginasREGNO:311119106029 Melodina Carnelian D Loyola - Icam College of Engineering and Technology (Licet)MELODINA CARNELIAN 19EC061Ainda não há avaliações

- Lpp. - MHT Cet 2020Documento1 páginaLpp. - MHT Cet 2020ManojKumar DeogadeAinda não há avaliações

- Daa Ue18cs280 PDFDocumento2 páginasDaa Ue18cs280 PDFPruthvi PutuAinda não há avaliações

- Greedy AlgorithmsDocumento39 páginasGreedy AlgorithmsHarsh SoniAinda não há avaliações

- Semester 5: WN Question PapersDocumento1 páginaSemester 5: WN Question PapersRahul ThoratAinda não há avaliações

- Duality ModuleDocumento16 páginasDuality ModuleJanet GravilesAinda não há avaliações

- 15 Parameter FittingDocumento15 páginas15 Parameter FittingEnriqueAinda não há avaliações

- HKUST COMP3211 Quiz1 SolutionDocumento6 páginasHKUST COMP3211 Quiz1 SolutionTKFAinda não há avaliações

- CSE 326 Lecture 9: Splay Trees and B-Trees What's On Our Plate Today?Documento11 páginasCSE 326 Lecture 9: Splay Trees and B-Trees What's On Our Plate Today?Sakura2709Ainda não há avaliações