Escolar Documentos

Profissional Documentos

Cultura Documentos

(EA773) Experimento 1 - Roteiro

Enviado por

Gabriela ShimaTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

(EA773) Experimento 1 - Roteiro

Enviado por

Gabriela ShimaDireitos autorais:

Formatos disponíveis

EA773 LABORATRIO DE CIRCUITOS LGICOS

FEEC-UNICAMP - 2 Semestre de 2015 Turmas S e T

Turma:______________ Grupo:__________________ Data:______________

RA:_________________ Nome:______________________________________

RA:_________________ Nome:______________________________________

Experincia 1: Circuitos Integrados.

Objetivo: Montagem de circuitos combinacionais e

seqenciais utilizando integrados da famlia TTL

1. Circuitos integrados

Identifique no TTL Data Book os componentes necessrios

para implementao do circuito da figura 1 (NOT e AND).

Faa o lay-out (esquema eltrico-lgico) do circuito da Fig. 1,

isto , especifique em um desenho esquemtico do protoboard

a posio relativa dos CIs utilizados e apresente a lista de

conexes. Evidencie no lay-out as ligaes de alimentao

(terra e VCC). Monte o circuito no protoboard e anote em

uma tabela os valores, com dois algarismos, de tenso nas

entradas (D e Clock) e nas sadas ( Q e Q ).

Determine a funo implementada pelo circuito da figura 1.

Verifique e justifique a compatibilidade dos valores medidos

com os valores considerados para a famlia TTL.

Visto:

No PC da sua bancada h um subdiretrio

C:\EA773\TURMAXX\GRUPOYY, onde XX a sua turma e

YY o seu grupo. Crie um diretrio para a experincia 1 no

subdiretrio de seu grupo.

Usando o software Quartus II, faa a captura do esquemtico

do circuito do item 1 (Graphic Editor), compile-o (Compiler),

edite formas de onda (Waveform Editor) e realize a simulao

(Simulator) para todas as possveis combinaes de entrada

(configurar o ambiente de simulao para a Famlia Cyclone

II;

componente:

EP2C20F484C7,

atravs

de

Assingments>Device ...).

Compare as formas de onda obtidas de uma simulao

funcional e de uma simulao temporal. Explique as

diferenas observadas. Qual a utilidade de cada um dos

modos de simulao no desenvolvimento de um projeto

digital?

___

___

Data:

2. Detetor de Dgitos do RA

Especifique os componentes, faa o diagrama eltrico-lgico

(anotando a pinagem) e o lay-out do circuito que realiza a

expresso booleana mnima associada ao seu RA, sendo que

cada dgito decimal define um mintermo da funo e os

binrios correspondentes aos decimais 10, 11, 12, 13, 14 e 15

so dont care states.

Manipule a expresso, se necessrio, para adequ-la aos

componentes existentes no almoxarifado (tais como NOR,

NAND, etc).

Solicite os componentes necessrios no almoxarifado, monte o

circuito e verifique a tabela verdade anotando os valores da

tenso na sada da porta lgica para todas as 16 entradas

possveis.

V isto :

3. QUARTUS II da Altera

No circuito da fig. 1 inclua os sinais CLR (clear) e PR

(preset). Clear e Preset so sinais ativos baixo que modificam

as sadas independentemente dos nveis das outras variveis de

entrada set e reset assncrono. Verifique por simulao o

funcionamento do circuito.

RA:

Visto:

Data:

Observaes:

1. O roteiro com o visto do professor (aps o funcionamento)

faz parte integrante do relatrio do grupo.

2. Esquemas e simulaes preparatrias devem ser depositadas

no portfolio do grupo em Ensino Aberto da Unicamp antes do

incio de cada aula e esquemas e simulaes finais aps o

termino da experincia.

D ata:

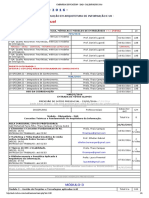

Figura 1 Diagrama Lgico.

EA773 LABORATRIO DE CIRCUITOS LGICOS

FEEC-UNICAMP - 2 Semestre de 2015 Turmas S e T

Turma:______________

Grupo:__________________ Data:______________

RA:_________________

Nome:______________________________________

RA:_________________

Nome:______________________________________

Experincia 1: Circuitos Integrados.

1) Circuitos integrados

Visto:

Data:

2. Detetor de Dgitos do RA

Visto:

Data:

3) Quartus II da Altera

Visto:

Data:

Relatrio e programas depositados no portfolio do grupo em: _____/_____/2015

Comentrios / avaliao

Você também pode gostar

- Cap1 Elo4 v7Documento65 páginasCap1 Elo4 v7Gabriela ShimaAinda não há avaliações

- EA076 RelatorioDocumento17 páginasEA076 RelatorioGabriela ShimaAinda não há avaliações

- (F429) Experimento 3 - RelatórioDocumento4 páginas(F429) Experimento 3 - RelatórioGabriela ShimaAinda não há avaliações

- QG100 - Aula 00 IntroDocumento3 páginasQG100 - Aula 00 IntroGabriela ShimaAinda não há avaliações

- QG100 - Exercícios p1Documento8 páginasQG100 - Exercícios p1Gabriela ShimaAinda não há avaliações

- Aula6 EcDocumento34 páginasAula6 EcGabriela ShimaAinda não há avaliações

- Filtros Elétricos: Tipos e Circuitos BásicosDocumento9 páginasFiltros Elétricos: Tipos e Circuitos BásicosGabriela ShimaAinda não há avaliações

- Leis Velocidade Reações QuímicasDocumento12 páginasLeis Velocidade Reações QuímicasmiltonsampaioAinda não há avaliações

- Control Aula19 Casos Especial EstabilidadeDocumento8 páginasControl Aula19 Casos Especial EstabilidadeLuiz RoqueAinda não há avaliações

- QG100 - Aula 01Documento21 páginasQG100 - Aula 01Gabriela ShimaAinda não há avaliações

- QG100 - Experimento 5Documento6 páginasQG100 - Experimento 5Gabriela ShimaAinda não há avaliações

- QG100 - Questoes para Estudo - p1Documento1 páginaQG100 - Questoes para Estudo - p1Gabriela ShimaAinda não há avaliações

- EA616 - Atividade 1Documento4 páginasEA616 - Atividade 1Gabriela ShimaAinda não há avaliações

- QG100 - Experimento 3Documento7 páginasQG100 - Experimento 3Gabriela ShimaAinda não há avaliações

- QG100 - Experimento 4Documento4 páginasQG100 - Experimento 4Gabriela ShimaAinda não há avaliações

- Microcomputador de 4 bitsDocumento4 páginasMicrocomputador de 4 bitsGabriela ShimaAinda não há avaliações

- QG100 - Experimento 4Documento4 páginasQG100 - Experimento 4Gabriela ShimaAinda não há avaliações

- QG100 - Experimento 2Documento6 páginasQG100 - Experimento 2Gabriela ShimaAinda não há avaliações

- EA773 - Projeto FinalDocumento4 páginasEA773 - Projeto FinalGabriela ShimaAinda não há avaliações

- Ea616 Atividade1Documento2 páginasEa616 Atividade1Gabriela ShimaAinda não há avaliações

- QG100 - Experimento 1Documento9 páginasQG100 - Experimento 1Gabriela ShimaAinda não há avaliações

- EA616 - Atividade 1Documento4 páginasEA616 - Atividade 1Gabriela ShimaAinda não há avaliações

- 00 - EA616 SyllabusDocumento2 páginas00 - EA616 SyllabusGabriela ShimaAinda não há avaliações

- Circuitos seqüenciais FPGADocumento2 páginasCircuitos seqüenciais FPGAGabriela ShimaAinda não há avaliações

- Cmfarra Education - Ead - Calendário 2016Documento6 páginasCmfarra Education - Ead - Calendário 2016Gabriela ShimaAinda não há avaliações

- Circuitos Lógicos TTLDocumento7 páginasCircuitos Lógicos TTLGabriela ShimaAinda não há avaliações

- Circuitos de IluminaçãoDocumento52 páginasCircuitos de Iluminaçãoecozoom100% (4)

- Estudo de propagação de surtos atmosféricos em subestação e comportamento de transformadorDocumento10 páginasEstudo de propagação de surtos atmosféricos em subestação e comportamento de transformadorHUGO GOMESAinda não há avaliações

- Motores, Automação, Energia e Tintas Conceitos BásicosDocumento18 páginasMotores, Automação, Energia e Tintas Conceitos BásicosJrobertoregoAinda não há avaliações

- CLIMATÉCNICADocumento13 páginasCLIMATÉCNICAJoão Augusto De Carvalho NaganoAinda não há avaliações

- MPK253Documento2 páginasMPK253WillianBizerradaSilvaAinda não há avaliações

- Manual Jupiter (2) (1) 2Documento16 páginasManual Jupiter (2) (1) 2felix coelhoAinda não há avaliações

- Eletricidade BásicaDocumento36 páginasEletricidade BásicaMarcos Marzano Jr100% (1)

- Harley Davidson - Dyna - 2011 - Electrical Diagnostics Manual - (PDF) - (99496-11br) - PT-BRDocumento376 páginasHarley Davidson - Dyna - 2011 - Electrical Diagnostics Manual - (PDF) - (99496-11br) - PT-BRThiago MicAinda não há avaliações

- Partida direta de motor trifásicoDocumento5 páginasPartida direta de motor trifásicoBianca FariasAinda não há avaliações

- Eletricidade de Automoveis - Sistemas de Cargas e Partidas Atualizada 1Documento54 páginasEletricidade de Automoveis - Sistemas de Cargas e Partidas Atualizada 1ZetroAinda não há avaliações

- Rev NBR16659Documento17 páginasRev NBR16659Alvaro RegoAinda não há avaliações

- Transformacao Estrela TrianguloDocumento4 páginasTransformacao Estrela Trianguloherbert0309Ainda não há avaliações

- Vestibular Estadual 2012 2a fase Exame DiscursivoDocumento26 páginasVestibular Estadual 2012 2a fase Exame DiscursivoTalita Raquel Luz RomeroAinda não há avaliações

- Guia do ventilador mecânicoDocumento27 páginasGuia do ventilador mecânicodiegolimanaAinda não há avaliações

- O Que e Corrosao AtritoDocumento5 páginasO Que e Corrosao AtritoautomaticosbrasilAinda não há avaliações

- Apostila de EletricidadeDocumento13 páginasApostila de EletricidadesilvinhocgvAinda não há avaliações

- Cópia Traduzida Oziel - de Documento em TítuloDocumento84 páginasCópia Traduzida Oziel - de Documento em TítuloDiego Maldinini50% (2)

- Controle de velocidade em máquinas de induçãoDocumento42 páginasControle de velocidade em máquinas de induçãoSamuel MartinsAinda não há avaliações

- Solis Manual (2,5-6) K 4G V2,3Documento26 páginasSolis Manual (2,5-6) K 4G V2,3Ton HecklerAinda não há avaliações

- Projeto de conversor CA/CC de alta potência para automóveisDocumento157 páginasProjeto de conversor CA/CC de alta potência para automóveisStefanoViganóAinda não há avaliações

- Equalizador versátil para adaptar o som ao ambienteDocumento82 páginasEqualizador versátil para adaptar o som ao ambienteg30.mirandaAinda não há avaliações

- Resolução de Circuitos Pneumáticos Pelo Método SequencialDocumento3 páginasResolução de Circuitos Pneumáticos Pelo Método SequencialFrancisco Pereira NunesAinda não há avaliações

- Esquema elétrico GolDocumento9 páginasEsquema elétrico GolChristian FrancisAinda não há avaliações

- Uninter - Caderno de Apoio Potencia CADocumento19 páginasUninter - Caderno de Apoio Potencia CAGil XavierAinda não há avaliações

- Exercicios de BJTDocumento8 páginasExercicios de BJTAugusto AntunesAinda não há avaliações

- Dimensionamento de circuitos elétricosDocumento37 páginasDimensionamento de circuitos elétricosscorpion-acmAinda não há avaliações

- Circuitos combinacionais: decodificadores e multiplexadoresDocumento17 páginasCircuitos combinacionais: decodificadores e multiplexadoresDiógenes Muller PereiraAinda não há avaliações

- Digital Multimeter GuideDocumento33 páginasDigital Multimeter Guidejos_jfnf5601Ainda não há avaliações

- Resumo Eletricidade BasicaDocumento10 páginasResumo Eletricidade BasicaMarcos Schneider ReichertAinda não há avaliações

- LIVRO - U2 Eletrônica Analógica IIDocumento68 páginasLIVRO - U2 Eletrônica Analógica IINei BarretoAinda não há avaliações