Escolar Documentos

Profissional Documentos

Cultura Documentos

Wireless Sensor Networks' Node Supported With Remote Hardware Modifications Capability

Enviado por

Editor IJRITCCTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Wireless Sensor Networks' Node Supported With Remote Hardware Modifications Capability

Enviado por

Editor IJRITCCDireitos autorais:

Formatos disponíveis

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 4

ISSN: 2321-8169

1979 1984

_______________________________________________________________________________________________

Wireless Sensor Networks Node Supported with Remote Hardware

Modifications Capability

Ali El Kateeb

University of Michigan-Dearborn

Email: elkateeb@umich.edu

Abstract

Wireless Sensor Networks (WSNs) nodes are generally have simple hardware design that can be classified as

inflexible, support one or more applications, and inexpensive. These nodes are designed and programmed before their

release on the application field and will stay on the field to support the need of the target application.

Although the existing wireless sensor nodes are designed to support remote software modifications, they are,

however, are not supporting remote hardware modifications. Using wireless sensor nodes that can support remote

nodes modification capability for both hardware and software will provide WSNs with flexible infrastructures that

can support nodes with over-the-air design modification even after the deployment of WSNs on the sensing field.

In this paper, we are presenting the design concept and challenges of such infrastructure. Also, we present the use

of such flexible infrastructure in potential WSNs applications.

Key Words: WSNs, Node design, FPGA

______________________________________*****____________________________________________

I.

INTRODUCTION

The Wireless Sensor Networks (WSNs) are

generally use many tiny nodes that integrated sensing,

computing, communication units, and may use some

other application-dependent units such as power

generators and location finding units [1-3]. These nodes

are characterized as low-cost, low-power, and have

multifunctional sensors.

These WSNs offer

economically viable solutions for applications that can

be found in different settings such as industry, military,

environment, health, etc. [4, 5]. Currently, the sensor

nodes are designed and programmed to match the needs

of the target applications before they are released to the

field. We present flexible WSN node that will be capable

of supporting remote hardware modification in addition

to software reprogramming feature. This type of nodes

will be called RH-node throughout this paper. This

type of nodes is not available in any commercially

available of WSNs infrastructure. Therefore, it is crucial

to explore the design challenges and the use of such

nodes in next-generation WSNs, which require on-field

system modifications. The design and the development

of the proposed RH-node will provide WSNs with

dynamically adaptable feature. Such feature will provide

nodes with design adjusting capability to the surrounding

environment even after the deployment of the RH-nodes

on the sensing field.

Supporting the proposed RH-node design with

remote hardware modifications capability will require

the use of Field Programmable Gate Array (FPGA)

technology in WSNs nodes design. However, nodes that

currently used in WSNs have not supported with FPGA

technology in their designs due to the main drawback of

the FPGA, which is high power consumption. However,

such drawback can be overcome by using variety of

different design approaches such as using modern FPGA

chips that consume low power, supporting nodes with

solar panel to recharge node batteries, and the use of

partial reconfigurations technique that available in some

FPGA design tools such as Xilinx.

In addition, the use of partial reconfiguration in

FPGA design can reduce the bit file size of the target

design, which will result in supporting nodes with fast

hardware modification and at low power consumption.

Despite the use of low power FPGA technology and

partial reconfiguration technique, the use of FPGA in

nodes design will still consume more power than those

nodes designed using microcontrollers. The availability

and low-cost tiny solar units have made these units

useful to be used to provide recharging batteries of the

RH-nodes. This will provide long operation time and

elevate the drawback for the large power consumption of

using FPGA in the proposed infrastructure. Typically,

increasing nodes cost due to the use of solar units will

not be acceptable in low-cost WSNs applications.

Nevertheless, nodes increasing cost is acceptable when

they are deployed in some WSNs applications, as in

forest fire monitoring application, as will be discussed

later on in this paper.

RH-NODES DESIGN CONCEPT AND

CHALLENGES

Sensor nodes in some existing WSNs have the

support for software reprogramming capability. For

example, the SOS project at UCLA provides software

modifying on individual nodes of a sensor network after

the network has been deployed and initialized. The

incremental update ability for new software modules and

II.

1979

IJRITCC | April 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 4

ISSN: 2321-8169

1979 1984

_______________________________________________________________________________________________

removed unused software module after network

design. As the solar panel used for charging battery of

deployment have been implemented in SOS project [6].

WSNs nodes are small in size and inexpensive, it is

Also, the lightweight virtual machines such as Mate and

feasible and acceptable for using these units for

modular operating systems such as Contiki are using

recharging the RH-node batteries. When nodes are

incremental code updates.

placed in the application field and are exposed to Sun

The design of the RH-node is focused on

light, nodes operation time can vary and depends on the

supporting WSNs with nodes remote hardware

existing sun light period during the day time.

modifications capability, which is a new feature for

iii)

Wireless JTAG: The JTAG port supported with

WSNs and has not been investigated thoroughly yet [7].

FPGA chips is commonly used for hardware

The main design challenges of supporting RH-node with

modifications. Typically, the design is downloaded from

remote hardware modifications are as follows:

a computer to FPGA chip using the JTAG port. To

i)

Hardware

Technology:

The

Field

remotely modify nodes design on the application field, a

Programmable Gate Array (FPGA) technology can

wireless JTAG unit needs to be used to receive the

provide very fast design modifications through the use of

design file and deliver it to the JTAG port of the FPGA

the computers USB. The USB cable can be used to

chip of the RH-nodes. However, since the wireless

download the design to program or reprogram the FPGA

JTAG unit is currently not available as a commercial

chip. However, the remote FPGA design modification

product; therefore, such unit should be designed and

has not been provided yet with any FPGA design tools.

developed to support remote hardware modification for

Therefore, it is required to develop a design tools for

RH-nodes.

remote FPGA design modifications to enhance the use of

iv)

Library development for system design

existing FPGA technology. As the JTAG protocol is

components: The infrastructure of the RH-nodes is

used to modify the FPGA design, it will be required to

intended to be a flexible in order to support the needs of

develop a remote JTAG unit that can be used to modify

the different requirements required by the target

the designs implemented in the FPGA chips. The FPGA

applications. Therefore, a library of components is

technology can be considered as the most effective

required to be developed to help design and develop RHtechnology that can support fast and efficeint hardware

nodes quickly and efficiently and to fulfill the

design modifications.

applications needs. Components that useful to be

ii)

Minimizing RH-nodes power consumption:

supported in such library are those that can be used in

One of the main characteristics of the WSNs is the use of

different applications such as soft-core processor

low power nodes. Typically, nodes should be capable to

component, wireless transceiver interface, and JTAG

work for a year using an AA battery. However, the RHcontroller. In addition, sensors interfaces such as CMOS

node infrastructure design has to use FPGA technology

pixels, temperature, and humidity sensors are important

to support hardware modifications, which is generally a

to be included in the library since such sensors are used

power hungry technology. The RH-nodes power

in many WSNs applications. As the FPGA is the

consumption can be reduced by using some of the

technology that will be used in RH-node design, these

recently developed FPGA chips that consume low power

components will be developed using VHDL language

such as Actel Igloo, Xilinx Spartan 6, etc. In addition,

and synthesized using the FPGA design tools.

using partial reconfiguration technique supported by

some FPGA design tools, such as with using Xilinx

III.

RH-NODE DEVELOPMENT

PlanAhead, could reduce the size of the FPGA design

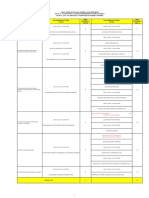

The System-On-Chip (SOC) design approach is used

file, which significantly reduces power consumption.

for RH-node development where components have

Transferring design file is usually consume large power,

integrated on FPGA processing core of the RH-node.

for instance it is known that the power consumption of

The RH-node design has included different soft

transferring one bit is equal to the execution of 1000

components such as MIPS processor core, sensor

instructions [8].

interfaces, JTAG controller, memory interface, and

To elevate the FPGA high power consumption

wireless transceiver controller. In addition to these soft

problem, the use of a large battery unit may support node

components, other off-the-shelf components such as the

operation for extended period of time. However, the

temperature/humidity sensor, CMOS pixels sensor,

battery charge will eventually be depleted when a node

memory, wireless transceiver, solar unit, and nodes

serves the target application for long period of time. We

rechargeable batteries have been integrated with the soft

believe that using a solar-based charging battery unit in

components and placed on the RH-nodes PCB board

the sensor node design can be used to extend the RH[Figure 1].

nodes batteries life even when the FPGA is used in node

1980

IJRITCC | April 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 4

ISSN: 2321-8169

1979 1984

_______________________________________________________________________________________________

Soft core

MIPS

processor

Transceiver

JTAG

signals

JTAG controller

Temperature/

humidity

sensor

Sensors

Interface

JTAG

controller

Flash

memory

Flash memory

interface

FPGA chip

CMOS pixels

sensor

Figure 1: components used for RH-node design

The main components of the RH-node are as follow:

3.1. Soft-core MIPS processor

Existing WSNs nodes are generally using

standard processor core for their processing need. The

ATmega128 micro-controller can be considered the most

commonly used processing element for sensing nodes.

However, the ATmega128 uses an 8-bit architecture and

is thus cannot be as efficient as 16 and 32-bit

architectures. Generally, the processing cores used in

existing WSNs nodes are off-the-shelf custom made

processors that provide reprogramming capability and

have no support for remote hardware modification

capability.

Some soft-core processors are currently

available such as Microblaze, ARM Cortex, etc.

Using such cores in sensor nodes can be useful in

supporting a variety of applications since they are

designed to serve general purpose computations.

However, using these processing cores has a drawback in

which they have many resources that may not be

required for the target application. Therefore, they will

consume more power and their cost is high. Design a

special soft-core processor for WSNs nodes will provide

some advantages such as optimized, flexible, and

efficient processor that can match the RH-nodes need of

the target WSNs applications. Moreover, using FPGA

technology for the soft-core processor development used

for the RH-node is useful to support remote node

hardware modifications on the applications field.

We have used non-pipeline MIPS architecture for

the soft-core processor since it has a small; simple; and

efficient processing architecture, which can be integrated

in a low-power FPGA chip. A specialized 32-bit nonpipelined MIPS soft-core processor has been developed

for RH-node [Figure 2]. The developed soft-core

processor has a performance of 10 MIPS, which is

acceptable for many sensor Network applications [9, 10].

Moreover, developing MIPS pipelined core can be used

in next-generation WSNs applications to support higher

processing performance, if required by specific

application.

1981

IJRITCC | April 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 4

ISSN: 2321-8169

1979 1984

_______________________________________________________________________________________________

to support heterogeneous RH-nodes using Spartan chips

3.2 Wireless JTAG unit

Most FPGA chips use a JTAG port to download the

shown in Table 1. The time required for achieving

design file to the target FPGA chip. As the RH-nodes

remote hardware modifications for these two

will support remote hardware modifications capability

components will depend on the transfer time of the

on the application field, a wireless JTAG unit is required

design file. For example, when we have used 56Kbit/sec

to be used with each RH-node. Developing a wireless

transceiver, the 16-bit ALU is remotely modified to 32JTAG port is essential since no commercially available

bit has required 6.1 second using XA3S200A chip. This

wireless JTAG that can be used to download design file

time requirement is achieved by segmented the design

to the target FPGA chip used in RH-node. The JTAG

file into packets and the packet transferred using a data

unit design can be designed using a wireless transceiver

packet frame format, which has 8-bit header and 8-bit

and Complex Programmable Logic Device (CPLD)

trailer, 8-byte size of data, and a CRC field. The

based controller to generate the signals and timing for

transmission range for the used transceiver was 100-feet.

the wireless JTAG port.

Using faster transceiver will help to achieve RH-node

The design file size produced by the Xilinx design

design modifications faster. This transmission range is

tools has a default size of 344,468 bytes. However, using

acceptable for some applications where the sensing area

the file compression option that supported with Xilinx

is small and few sensor nodes are required to monitor

design tools, the size of the design file can be reduced

that area.

significantly as shown in Table 1. Therefore, the remote

hardware modifications can be done faster. For example,

the design file size that support 16-bit and 32-bit of two

CPU components,namely ALU and Register File (RF),

CLASS

SPARTAN 3A

Device:XA3S200A

Device:XA3S400A

Device:XA3S700A

16 bit, 16 register

32 bit, 32 register

ALU

RF

ALU

RF

28KB

100KB

81KB

116KB

33KB

145KB

117KB

174KB

40KB

54KB

43KB

281KB

Table 1: ALU and RF design file size

3.3. Sensor interfaces

There are many off-the-shelf sensors available today.

However, only those sensors required for serving the

target application are placed on the PCB board of the

proposed RH-nodes. Off-the-shelf sensors, such as

CMOS pixels and temperature/humidity sensors have

been utilized by the RH-node to provide a proof-ofconcept for using remote hardware modification

capability feature in remotely modify the sensors

controllers and interfaces that placed on RH-node.

The VHDL language has been used for soft-core

processor core and all other sensors interfaces and

controllers. Also, a tiny LCD has been used with the RHnode at the base station since it is useful in some

applications where WSNs used for security and

monitoring applications where the operators located at

the base station site can watch the events around the RHnodes located at the applications filed where they capture

the images and transfer them to the base station for

observation and analyzes by the operator. The pixels

sensor placed on the PCB of each RH-node can be

programmed to capture and transfer the image to the

base station. Also, RH-nodes can be programmed to

process the image at the application site and analyze the

image and only transfer the analyzing results to the base

station. However, any one of these two methods can be

used by RH-node and that depends on the target

application needs.

3.4. Recharging the battery unit

Despite the use of low power FPGA chip and partial

reconfiguration technique in the design of the RH-node

to reduce the power consumption, a small solar unit is

used with each node for recharging nodes batteries.

Using a solar unit in a well-setting environment will

provide the RH-node with a sustain power. A tiny and

low-cost off-the-shelf battery recharging solar unit is

available that can recharge one AA battery and cost less

than $10 for a unit [Figure 3]. Clearly, the cost of the

proposed node will be increased due to the use of the

1982

IJRITCC | April 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 4

ISSN: 2321-8169

1979 1984

_______________________________________________________________________________________________

solar recharging unit. However, such increasing cost will

support the processing required for each RH-node that

be acceptable for the use in WSNs. The RH-node has

deployed on the application field. Simple processing

been developed using Xilinx Spartan FPGA chip and

required by all nodes at the start of the WSNs and under

two solar recharging units to recharge two AA batteries

normal WSNs operation mode, i.e., no fire is detected.

to power the FPGA of the RH-node.

Each RH-node at the WSNs will check the humidity

level at surrounding environment. When the humidity

IV.

USING REMOTE HARDWARE/SOFTWARE

drops to a low level, this is either an indication of dry

MODIFICATION IN WSNS

weather or a fire has occurred around certain nodes

A small size WSNs prototype of ten RH-node is

location. The node processing unit for the node that

under development to provide a proof-of-concept for

closely located near the fire area will then switch to

using remote hardware modifications and software

check the temperature and when the temperature level is

reprogramming capability of the RH-node in WSN

reached above a certain high level, the node will switch

applications [Figure 4].

The remote software

to scan the captured image of the surrounding forest to

reprogramming capability has been used in different

verify occurrence of fire, which require the use of most

WSNs applications. However, the WSNs applications

of the soft-core processor resources. In the case that no

that use remote hardware modifications capability is not

fire is detected, the nodes processing core will be

fully implemented on any existing WSNs yet and they

restored to its temperature sensing mode.

are still under research. Therefore, we used one possible

While the node located at the fire area is locally

application, namely the forest fire monitoring, to provide

processed the captured images to identify the existence

the proof of concept of providing both the remote

of fire, other nodes located distantly from the fire will

hardware and software modifications capability in

continue to process the basic and simple operation of

WENs applications.

checking humidity or temperature. Clearly, the

This forest fire monitoring application could

processing required for capturing and analyzing the fire

demonstrates the remote modifications of the softimage is more complex than the processing required for

processing cores of RH-nodes on their application field

analyzing the sensors reading of humidity and

to match the needs of the surrounding application

temperature. Therefore, all ALU instructions and softenvironment. Each RH-node is supported with three

processor capabilities will be used by the nodes located

sensors: humidity, temperature, and CMOS pixels. There

near the fire location while other nodes will use fewer

are different possible scenarios of using the RH-nodes on

ALU instructions and potion of the soft-processor

forest fire monitoring application. However, one possible

capabilities for processing the humidity and temperature

simple scenario is presented to explore the dynamic

sensing.

modification of the nodes soft-core processors to

Figure 3

Tiny solar unit for recharging WSN node

1983

IJRITCC | April 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 4

ISSN: 2321-8169

1979 1984

_______________________________________________________________________________________________

The implementation of the RH-nodes remote

hardware modification capability can be used in this

application to save the network power consumption. For

instance, the node resources can be set to the level that

can be used to conduct the image processing and

communicate the result to the base station or to use the

node minimum resources that serve the basic node

function of checking the surrounding temperature and

humidity level. Therefore, the network power

consumption will be optimized by using only the nodes

full resources for processing the image of the fire at the

fire surrounding area and transmitting the image to the

base station and keep all other nodes located far from the

fire location to run using their minimum resources.

V.

CONCLUSION

We presented the research work underway at

University of Michigan-Dearborn on the design of the

next-generation of WSNs, which use FPGA technology

to support remote hardware/software modifications. The

concept and the challenges in designing the flexible RHnode has been highlight in this paper. The development

of such node infrastructure will advance different

research areas of WSNs in applications, architecture,

routings, etc.

One example of using RH-nodes

infrastructure in environmental monitoring such as forest

fire monitoring application has been discussed in this

paper. Using FPGA chips in RH-nodes will consume

large power. However, we propose using a low-cost tiny

solar unit to recharge the RH-nodes batteries. This will

provide long operation time and elevate the drawback for

the large power consumption of using FPGA in the RHnode design.

REFERENCES

[1] C. Intanagonwiwat, R. Govindan, and D. Estrin,

Directed Diffusion: A Scalable and Robust

Communication Paradigm for Sensor Networks,

Proc. ACM MobilCom00, Boston, MA, 2000, pp.

56-67.

[2] G. J. Pottie and W. J. Kaiser, Wireless Integrated

Network Sensors, Commun. ACM, vol. 43, no. 5,

May 2000, pp. 551-558.

[3] J. M. Kahn, R. H. Katz, and K. S. Pister, Next

Century Challenges: Mobile Networking for Smart

Dust, Proc. ACM MobiCom99, Washinton, DC,

1999, pp. 271-278.

[4] C. Intanagonwiwat, R. Govindan, and D. Estrin,

Directed Diffusion: A Scalable and Robust

Communication Paradigm for Sensor Networks,

Proc. ACM MobilCom00, Boston, MA, 2000, pp.

56-67.

[5] G. J. Pottie and W. J. Kaiser, Wireless Integrated

Network Sensors, Commun. ACM, vol. 43, no. 5,

May 2000, pp. 551-558.

[6] V.

Mudagal,

Methods

for

Upgrading

Reconfigurable Hardware use in Mobile Phones,

Freescale Semiconductor, Inc., White paper, 2006.

[7] Ali El Kateeb, Hardware Reconfiguration

Capability for Third-Generation Sensor Nodes,

IEEE Computer, May 2009, pp. 95-97.

[8] J. Culler, Incremental Network Programming for

Wireless Sensors, Proc. 1st Annual IEEE ComSoc.

Conf. Sensor and Ad Hoc Commun. And Networks

(SECON), 2004, pp.25-33.

[9] Ali El Kateeb, Aiyappa Ramesh, and Lubna Azzawi,

Wireless Sensor Nodes Processor Architecture and

Design, the 22nd IEEE International Conference on

Advanced Information Networking and Application,

March 2008, Japan, pp892-897.

[10]

Ali Elkateeb, Remote Modification of Sensor

Mote Design for Next-generation Wireless Sensor

Networks, IEEE International Conference on

Wireless for Space and Extreme Environment,

WiSEE 2013, November 2013, Baltimore, USA.

1984

IJRITCC | April 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

Você também pode gostar

- Importance of Similarity Measures in Effective Web Information RetrievalDocumento5 páginasImportance of Similarity Measures in Effective Web Information RetrievalEditor IJRITCCAinda não há avaliações

- A Review of Wearable Antenna For Body Area Network ApplicationDocumento4 páginasA Review of Wearable Antenna For Body Area Network ApplicationEditor IJRITCCAinda não há avaliações

- Channel Estimation Techniques Over MIMO-OFDM SystemDocumento4 páginasChannel Estimation Techniques Over MIMO-OFDM SystemEditor IJRITCCAinda não há avaliações

- Regression Based Comparative Study For Continuous BP Measurement Using Pulse Transit TimeDocumento7 páginasRegression Based Comparative Study For Continuous BP Measurement Using Pulse Transit TimeEditor IJRITCCAinda não há avaliações

- A Review of 2D &3D Image Steganography TechniquesDocumento5 páginasA Review of 2D &3D Image Steganography TechniquesEditor IJRITCCAinda não há avaliações

- Channel Estimation Techniques Over MIMO-OFDM SystemDocumento4 páginasChannel Estimation Techniques Over MIMO-OFDM SystemEditor IJRITCCAinda não há avaliações

- Comparative Analysis of Hybrid Algorithms in Information HidingDocumento5 páginasComparative Analysis of Hybrid Algorithms in Information HidingEditor IJRITCCAinda não há avaliações

- IJRITCC Call For Papers (October 2016 Issue) Citation in Google Scholar Impact Factor 5.837 DOI (CrossRef USA) For Each Paper, IC Value 5.075Documento3 páginasIJRITCC Call For Papers (October 2016 Issue) Citation in Google Scholar Impact Factor 5.837 DOI (CrossRef USA) For Each Paper, IC Value 5.075Editor IJRITCCAinda não há avaliações

- Performance Analysis of Image Restoration Techniques at Different NoisesDocumento4 páginasPerformance Analysis of Image Restoration Techniques at Different NoisesEditor IJRITCCAinda não há avaliações

- A Study of Focused Web Crawling TechniquesDocumento4 páginasA Study of Focused Web Crawling TechniquesEditor IJRITCCAinda não há avaliações

- A Review of 2D &3D Image Steganography TechniquesDocumento5 páginasA Review of 2D &3D Image Steganography TechniquesEditor IJRITCCAinda não há avaliações

- A Review of Wearable Antenna For Body Area Network ApplicationDocumento4 páginasA Review of Wearable Antenna For Body Area Network ApplicationEditor IJRITCCAinda não há avaliações

- Diagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmDocumento5 páginasDiagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmEditor IJRITCCAinda não há avaliações

- Modeling Heterogeneous Vehicle Routing Problem With Strict Time ScheduleDocumento4 páginasModeling Heterogeneous Vehicle Routing Problem With Strict Time ScheduleEditor IJRITCCAinda não há avaliações

- Network Approach Based Hindi Numeral RecognitionDocumento4 páginasNetwork Approach Based Hindi Numeral RecognitionEditor IJRITCCAinda não há avaliações

- Fuzzy Logic A Soft Computing Approach For E-Learning: A Qualitative ReviewDocumento4 páginasFuzzy Logic A Soft Computing Approach For E-Learning: A Qualitative ReviewEditor IJRITCCAinda não há avaliações

- Efficient Techniques For Image CompressionDocumento4 páginasEfficient Techniques For Image CompressionEditor IJRITCCAinda não há avaliações

- 41 1530347319 - 30-06-2018 PDFDocumento9 páginas41 1530347319 - 30-06-2018 PDFrahul sharmaAinda não há avaliações

- Prediction of Crop Yield Using LS-SVMDocumento3 páginasPrediction of Crop Yield Using LS-SVMEditor IJRITCCAinda não há avaliações

- Itimer: Count On Your TimeDocumento4 páginasItimer: Count On Your Timerahul sharmaAinda não há avaliações

- 45 1530697786 - 04-07-2018 PDFDocumento5 páginas45 1530697786 - 04-07-2018 PDFrahul sharmaAinda não há avaliações

- Predictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth KotianDocumento3 páginasPredictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth Kotianrahul sharmaAinda não há avaliações

- 44 1530697679 - 04-07-2018 PDFDocumento3 páginas44 1530697679 - 04-07-2018 PDFrahul sharmaAinda não há avaliações

- Hybrid Algorithm For Enhanced Watermark Security With Robust DetectionDocumento5 páginasHybrid Algorithm For Enhanced Watermark Security With Robust Detectionrahul sharmaAinda não há avaliações

- Safeguarding Data Privacy by Placing Multi-Level Access RestrictionsDocumento3 páginasSafeguarding Data Privacy by Placing Multi-Level Access Restrictionsrahul sharmaAinda não há avaliações

- A Clustering and Associativity Analysis Based Probabilistic Method For Web Page PredictionDocumento5 páginasA Clustering and Associativity Analysis Based Probabilistic Method For Web Page Predictionrahul sharmaAinda não há avaliações

- Vehicular Ad-Hoc Network, Its Security and Issues: A ReviewDocumento4 páginasVehicular Ad-Hoc Network, Its Security and Issues: A Reviewrahul sharmaAinda não há avaliações

- Image Restoration Techniques Using Fusion To Remove Motion BlurDocumento5 páginasImage Restoration Techniques Using Fusion To Remove Motion Blurrahul sharmaAinda não há avaliações

- A Content Based Region Separation and Analysis Approach For Sar Image ClassificationDocumento7 páginasA Content Based Region Separation and Analysis Approach For Sar Image Classificationrahul sharmaAinda não há avaliações

- Space Complexity Analysis of Rsa and Ecc Based Security Algorithms in Cloud DataDocumento12 páginasSpace Complexity Analysis of Rsa and Ecc Based Security Algorithms in Cloud Datarahul sharmaAinda não há avaliações

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (894)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (399)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (119)

- Home Power Magazine - Wind Power BasicsDocumento9 páginasHome Power Magazine - Wind Power BasicsradurusAinda não há avaliações

- Bersemuka LDocumento7 páginasBersemuka LPK K0% (1)

- Compressor Technical Data: NJ6226Z 220-240 V 50 HZ 142HAO4 A - Application / Limit Working ConditionsDocumento3 páginasCompressor Technical Data: NJ6226Z 220-240 V 50 HZ 142HAO4 A - Application / Limit Working ConditionsFernando GomezAinda não há avaliações

- Configuration of CNC System: 1. Central Processing Unit (CPU)Documento4 páginasConfiguration of CNC System: 1. Central Processing Unit (CPU)tavish sharmaAinda não há avaliações

- Buchholz Relay in Transformers (Working Principle) - Electrical4UDocumento5 páginasBuchholz Relay in Transformers (Working Principle) - Electrical4UHarsh PatelAinda não há avaliações

- UNIT 3 Fourier Series Symmetry Properties Questions and Answers - Sanfoundry PDFDocumento3 páginasUNIT 3 Fourier Series Symmetry Properties Questions and Answers - Sanfoundry PDFzohaibAinda não há avaliações

- Acceleration Measurement and Applications: Prof. R.G. LongoriaDocumento34 páginasAcceleration Measurement and Applications: Prof. R.G. LongoriaOscar SotomayorAinda não há avaliações

- SA100 V 14 BulletinDocumento8 páginasSA100 V 14 BulletinTeepoonsab somsaiAinda não há avaliações

- Op and Tech-Gen2 Mnl-000003Documento52 páginasOp and Tech-Gen2 Mnl-000003Salazar HCAinda não há avaliações

- ED - Mid Lecture-10 - Part 2Documento12 páginasED - Mid Lecture-10 - Part 2Pritam ChakrabortyAinda não há avaliações

- ReferencesDocumento3 páginasReferencesKUHENDRAN A/L RAVANDRANAinda não há avaliações

- WEG Regulador de Tensao Grt7 Th4 10040217 Manual Portugues BRDocumento50 páginasWEG Regulador de Tensao Grt7 Th4 10040217 Manual Portugues BRJuan I. Meza Lozano100% (1)

- SRP-6MA (-HV) : Key FeaturesDocumento2 páginasSRP-6MA (-HV) : Key FeaturesNanangDatadikJatimAinda não há avaliações

- PM4018MUDocumento11 páginasPM4018MUaldo_suviAinda não há avaliações

- SENZIT USER GUIDE INSTALLATIONDocumento6 páginasSENZIT USER GUIDE INSTALLATIONDaniel AyalaAinda não há avaliações

- Detail of Maximum Current - ChillersDocumento3 páginasDetail of Maximum Current - ChillersMohamed RifanAinda não há avaliações

- 8 isolated DC output module with optical isolation and diode protectionDocumento1 página8 isolated DC output module with optical isolation and diode protectionDelshad DuhokiAinda não há avaliações

- CSC 111 - Introduction To Computing Lecture One: C. I Eke Eke - Ifeanyi @fulafia - Edu.ngDocumento49 páginasCSC 111 - Introduction To Computing Lecture One: C. I Eke Eke - Ifeanyi @fulafia - Edu.ngLawalAinda não há avaliações

- Bfou1kv (3) Nek606 CablesDocumento14 páginasBfou1kv (3) Nek606 Cables54045114Ainda não há avaliações

- SF-2001-SureFire II High Energy Igniter (English) 2020-12-17Documento24 páginasSF-2001-SureFire II High Energy Igniter (English) 2020-12-17akash kurheAinda não há avaliações

- SMARDT Catalogue Ta ClassDocumento18 páginasSMARDT Catalogue Ta ClassAlhgasjsghjagjsdajlsd AsdalsdlkaksdAinda não há avaliações

- TL866 DesignDocumento12 páginasTL866 Designtemplpa100% (1)

- VHF FM Handheld Transceiver: 144 MHZ, Ultra-Rugged, 5 Watts!Documento2 páginasVHF FM Handheld Transceiver: 144 MHZ, Ultra-Rugged, 5 Watts!Jc Sevillano AlejandroAinda não há avaliações

- 70 Series Maintenance Training Manual - MitsuDocumento299 páginas70 Series Maintenance Training Manual - Mitsuboystudy83100% (1)

- ASUS Sound Card GuideDocumento1 páginaASUS Sound Card GuideilabuloAinda não há avaliações

- ECE216Documento2 páginasECE216Aryan GourAinda não há avaliações

- Instantaneous 4 Contact RelaysDocumento3 páginasInstantaneous 4 Contact RelaysSetecma IndustrialAinda não há avaliações

- Computer Components Worksheet 1A Processor ComponentsDocumento2 páginasComputer Components Worksheet 1A Processor ComponentsShakila.D Raks PallikkoodamAinda não há avaliações

- 7SK80xx Catalog SIP-2008 A3 enDocumento36 páginas7SK80xx Catalog SIP-2008 A3 enalainAinda não há avaliações

- TROUBLESHOOTING AIR CONDITIONER ERRORSDocumento11 páginasTROUBLESHOOTING AIR CONDITIONER ERRORSMuhamad PriyatnaAinda não há avaliações