Escolar Documentos

Profissional Documentos

Cultura Documentos

HM6264

Enviado por

Kaustuv MishraDescrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

HM6264

Enviado por

Kaustuv MishraDireitos autorais:

Formatos disponíveis

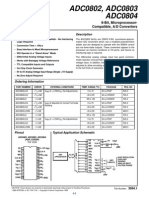

HM6264A Series

8192-word 8-bit High Speed CMOS Static RAM

Features

Low-power standby

0.1 mW (typ)

10 W (typ) L-/LL-version

Low power operation

15 mW/MHz (typ)

Fast access time

l00/120/150 ns (max)

Single +5 V supply

Completely static memory

No clock or timing strobe required

Equal access and cycle time

Common data input and output, three-state

output

Directly TTL compatible

All inputs and outputs

Battery back up operation capability

(L-/LL-version)

Ordering Information

Type No.

Access

time

HM6264AP-10

100 ns

HM6264AP-12

120 ns

HM6264AP-15

150 ns

HM6264ALP-10

100 ns

HM6264ALP-12

120 ns

HM6264ALP-15

150 ns

Type No.

Access

time

HM6264ASP-10

100 ns

HM6264ASP-12

120 ns

HM6264ASP-15

150 ns

Package

300-mil, 28-pin

plastic DIP

(DP-28N)

HM6264ALSP-10 100 ns

HM6264ALSP-12 120 ns

HM6264ALSP-15 150 ns

HM6264ALSP-10L 100 ns

HM6264ALSP-12L 120 ns

HM6264ALSP-15L 150 ns

HM6264AFP-10

100 ns

HM6264AFP-12

120 ns

HM6264AFP-15

150 ns

28-pin plastic

SOP *1

(FP-28D/DA)

Package

HM6264ALFP-10 100 ns

600-mil, 28-pin

plastic DIP

(DP-28)

HM6264ALFP-12 120 ns

HM6264ALFP-15 150 ns

HM6264ALFP-10L 100 ns

HM6264ALFP-12L 120 ns

HM6264ALFP-15L 150 ns

HM6264ALP-10L 100 ns

Note: 1. T is added to the end of the type number

for a SOP of 3.00 mm (max) thickness.

HM6264ALP-12L 120 ns

HM6264ALP-15L 150 ns

HM6264A Series

HM6264A Series

Pin Arrangement

NC

A12

A7

A6

A5

A4

A3

1

2

A2

A1

A0

8

9

10

11

12

21

20

19

18

17

VCC

WE

CS2

A8

A9

A11

OE

A10

CS1

I/O8

I/O7

I/O6

13

14

16

15

I/O5

I/O4

I/O1

I/O2

I/O3

VSS

28

27

26

25

24

3

4

5

6

7

23

22

(Top view)

Block Diagram

A11

A8

A9

A7

A12

A5

A6

A4

Row

decoder

I/O1

Column I/O

Input

data

control

I/O8

CS2

CS1

WE

OE

Memory array

256 256

Column decoder

A1 A2 A0 A10 A3

Timing pulse generator

VCC

VSS

HM6264A Series

HM6264A Series

Truth Table

WE

CS1

CS2

OE

Mode

I/O pin

VCC current

Not selected

(power down)

High Z

ISB, ISB1

High Z

ISB, ISB1

Output disabled

High Z

ICC

Read

Dout

ICC

Read cycle

Write

Din

ICC

Write cycle 1

Write

Din

ICC

Write cycle 2

Note:

: Dont care.

Note

Absolute Maximum Ratings

Parameter

Symbol

Rating

Unit

Terminal voltage *1

VT

0.5 *2 to +7.0

Power dissipation

PT

1.0

Operating temperature

Topr

0 to +70

Storage temperature

Tstg

55 to +125

Storage temperature (under bias)

Tbias

10 to +85

Notes: 1. With respect to VSS.

2. 3.0 V for pulse width 50 ns

Recommended DC Operating Conditions (Ta = 0 to +70C)

Parameter

Symbol

Min

Typ

Max

Unit

Supply voltage

VCC

4.5

5.0

5.5

VSS

VIH

2.2

6.0

VIL

0.3 *1

0.8

Input voltage

Note:

1. 3.0 V for pulse width 50 ns

HM6264A Series

HM6264A Series

DC and Operating Characteristics (VCC = 5 V 10%,VSS = 0 V, Ta = 0 to +70C)

Parameter

Symbol

Min

Typ

Max

Unit

Test condition

Input leakage current

|ILI|

Vin = VSS to VCC

Output leakage current |ILO|

CS1 = VIH or CS2 = VIL or OE = VIH or

WE = VIL, VI/O = VSS to VCC

Operating power

supply current

ICCDC

15

mA

CS1 = VIL, CS2 = VIH, II/O = 0 mA

Average operating

current

ICC1

30

30

45*5

55*6

mA

Min. cycle, duty = 100%,

CS1 = VIL, CS2 = VIH, II/O = 0 mA

ICC2

mA

Cycle time = 1 s, duty = 100%,

II/O = 0 mA, CS1 0.2 V,

CS2 VCC 0.2 V, VIH VCC 0.2 V,

VIL 0.2 V

mA

CS1 = VIH or CS2 = VIL

Standby power supply ISB

current

ISB1 *2

Output voltage

Notes: 1.

2.

3.

4.

5.

6.

0.02 2

mA

CS1 VCC 0.2 V, CS2 VCC 0.2 V or

2*3

100*3 A

0 V CS2 0.2 V, 0 V Vin

2*4

50*4

VOL

0.4

IOL = 2.1 mA

VOH

2.4

IOH = 1.0 mA

Typical values are at VCC = 5.0 V, Ta = 25C and not guaranteed.

VIL min = 0.3 V

These characteristics are guaranteed only for the L-version.

These characteristics are guaranteed only for the LL-version.

For 120 ns/150 ns version.

For 100 ns version.

Capacitance (f = 1 MHz, Ta = 25C)*1

Parameter

Symbol

Typ

Max

Unit

Test condition

Input capacitance

Cin

pF

Vin = 0 V

Input/output capacitance

CI/O

pF

VI/O = 0 V

Note:

1. This parameter is sampled and is not 100% tested.

HM6264A Series

HM6264A Series

AC Characteristics (VCC = 5 V 10%, Ta = 0 to +70C)

AC Test Conditions:

Input pulse levels: 0.8 V/2.4 V

Input rise and fall time: 10 ns

Input timing reference level: 1.5 V

Output timing reference level

HM6264A-10: 1.5 V

HM6264A-12/15: 0.8 V/2.0 V

Output load: 1 TTL gate and CL (100 pF) (including scope and jig)

Read Cycle

Parameter

Symbol

HM6264A-10

Min

Max

Read cycle time

tRC

100

120

150

ns

Address access time

tAA

100

120

150

ns

CS1

tCO1

100

120

150

ns

CS2

tCO2

100

120

150

ns

tOE

50

60

70

ns

CS1

tLZ1

10

10

15

ns

CS2

tLZ2

10

10

15

ns

Output enable to output in low Z

tOLZ

ns

CS1

tHZ1

35

40

50

ns

CS2

tHZ2

35

40

50

ns

Output disable to output in high Z

35

40

50

ns

Output hold from address change

10

10

10

ns

Chip selection to output

Output enable to output valid

Chip selection to output

in low Z

Chip deselection to

output in high Z

Notes

OHZ

OH

HM6264A-12

Min

Max

HM6264A-15

Min

Max

Unit

1. tHZ and tOHZ are defined as the time at which the outputs to achieve the open circuit

condition and are not referred to output voltage levels.

2. At any given temperature and voltage condition, tHZ maximum is less than tLZ minimum both for

a given device and from device to device.

HM6264A Series

HM6264A Series

Read Timing Waveform

tRC

Address

tAA

tCO1

CS1

tLZ1

tCO2

CS2

tHZ1

tLZ2

tOE

tHZ2

tOLZ

OE

tOHZ

Dout

Valid Data

tOH

Note: WE is high for read cycle.

Write Cycle

Parameter

Symbol

HM6264A-10

Min

Max

Write cycle time

tWC

100

120

150

ns

Chip selection to end of write

tCW

80

85

100

ns

Address setup time

tAS

ns

Address valid to end of write

tAW

80

85

100

ns

Write pulse width

tWP

60

70

90

ns

Write recovery time

tWR

ns

Write to output in high Z

tWHZ

35

40

50

ns

Data to write time overlap

tDW

40

40

50

ns

Data hold from write time

tDH

ns

Output enable to output in high Z

tOHZ

35

40

50

ns

Output active from end of write

tOW

ns

HM6264A-12

Min

Max

HM6264A-15

Min

Max

Unit

HM6264A Series

HM6264A Series

Write Timing Waveform (1) (OE Clock)

tWC

Address

OE

tCW *2

tWR *4

CS1

*6

CS2

WE

tAW

tAS *3

tWP *1

tOHZ *5

Dout

Din

tDW

tDH

Valid Data

HM6264A Series

HM6264A Series

Write Timing Waveform (2) (OE Low Fix)

tWC

Address

tAW

tWR *4

tCW

*2

*6

CS1

tCW *2

CS2

WE

tWP *1

tAS *3

*5

tOH

tOW

tWHZ

*7

Dout

tDW

*8

tDH

*9

Din

Valid Data

Notes: 1. A write occurs during the overlap of a low CS1, a high CS2, and a low WE. A write begins

at the latest transition among CS1 going low, CS2 going high and WE going low. A write

ends at the earliest transition among CS1 going high, CS2 going low and WE going high.

Time tWP is measured from the beginning of write to the end of write.

2. tCW is measured from the later of CS1 going low or CS2 going high to the end of write.

3. tAS is measured from the address valid to the beginning of write.

4. tWR is measured from the earliest of CS1 or WE going high or CS2 going low to the end

of the write cycle.

5. During this period, I/O pins are in the output state, therefore the input signals of opposite

phase to the outputs must not be applied.

6. If CS1 goes low simultaneously with WE going low or after WE goes low, the outputs

remain in high impedance state.

7. Dout is the same phase of the latest written data in this write cycle.

8. Dout is the read data of the next address.

9. If CS1 is low and CS2 is high during this period, I/O pins are in the output state. Input signals

of opposite phase to the outputs must not be applied to I/O pins

HM6264A Series

HM6264A Series

Low VCC Data Retention

In data retention mode, CS2 controls the address,

WE, CS1, OE, and the Din buffer. If CS2 controls

data retention mode, Vin (for these inputs) can be

in the high impedance state. If CS1 controls the

data retention mode, CS2 must satisfy either

CS2 VCC 0.2 V or CS2 0.2 V. The other

input levels (address, WE, OE, I/O) can be in the

high impedance state.

Low VCC Data Retention Characteristics (Ta = 0 to +70C)

This characteristics is guaranteed only L/LL-version.

Parameter

Symbol

Min

Typ

Max

Unit

Test Condition

VCC for data retention

VDR

2.0

CS1 VCC 0.2 V,

CS2 VCC 0.2 V, or

CS2 0.2 V

Data retention current

ICCDR

1*1

50*1

1*2

25*2

VCC = 3.0 V,

CS1 VCC 0.2 V,

CS2 VCC 0.2 V, or

0 V CS2 0.2 V, 0 V Vin

ns

See retention waveform

ns

See retention waveform

Chip deselect to data

retention time

Operation recovery time

tR

CDR

*3

RC

Notes: 1. VIL min = 0.3 V, 20 A max at Ta = 0 to 40C. These characteristics are guaranteed only for

the L-version.

2. VIL min = 0.3 V, 10 A max at Ta = 0 to 40C. These characteristics are guaranteed only for

the LL-version.

3. tRC = Read cycle time.

Low VCC Data Retention Waveform (1) (CS1 Controlled)

tCDR

Data retention mode

tR

VCC

4.5 V

2.2 V

VDR

CS1

0V

CS1 VCC 0.2 V

HM6264A Series

HM6264A Series

Low VCC Data Retention Waveform (2) (CS2 Controlled)

Data retention mode

VCC

4.5 V

tCDR

tR

CS2

VDR

0.4 V

0V

10

CS2 0.2 V

Você também pode gostar

- HM6264B Series: 64 K SRAM (8-Kword 8-Bit)Documento16 páginasHM6264B Series: 64 K SRAM (8-Kword 8-Bit)Nguyen Hai Tran SonAinda não há avaliações

- 6264 DatasheetDocumento15 páginas6264 DatasheetjlfmotaAinda não há avaliações

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Ainda não há avaliações

- 4Mb-SRAM 512Kx1BDocumento18 páginas4Mb-SRAM 512Kx1BserjaniAinda não há avaliações

- 24LC02BDocumento26 páginas24LC02Bjab_arx1Ainda não há avaliações

- HM62256B Series: 32,768-Word 8-Bit High Speed CMOS Static RAMDocumento15 páginasHM62256B Series: 32,768-Word 8-Bit High Speed CMOS Static RAMJose LopezAinda não há avaliações

- HY6264A - (I) Series: 8kx8bit CMOS SRAMDocumento9 páginasHY6264A - (I) Series: 8kx8bit CMOS SRAMLexuanhoa ProAinda não há avaliações

- 128mbit SDRAM: 2M X 16bit X 4 Banks Synchronous DRAM LVTTLDocumento11 páginas128mbit SDRAM: 2M X 16bit X 4 Banks Synchronous DRAM LVTTLThiago Cristiano TavaresAinda não há avaliações

- Hanbit Hmn1288D: Non-Volatile Sram Module 1mbit (128K X 8-Bit), 32Pin-Dip, 5V Part No. Hmn1288DDocumento9 páginasHanbit Hmn1288D: Non-Volatile Sram Module 1mbit (128K X 8-Bit), 32Pin-Dip, 5V Part No. Hmn1288DDeepa DevarajAinda não há avaliações

- 000 0 Hy628100bllg 70Documento9 páginas000 0 Hy628100bllg 70Deepa DevarajAinda não há avaliações

- 2114 SramDocumento4 páginas2114 SramKarloz IbarraAinda não há avaliações

- 24 LC 2561Documento12 páginas24 LC 2561ricardo_MassisAinda não há avaliações

- 32kx8bit CMOS SRAM: HY62256B SeriesDocumento9 páginas32kx8bit CMOS SRAM: HY62256B SeriesShiwam IsrieAinda não há avaliações

- 24AA00/24LC00/24C00: 128 Bit I C Bus Serial EEPROMDocumento18 páginas24AA00/24LC00/24C00: 128 Bit I C Bus Serial EEPROMJuliano GriguloAinda não há avaliações

- OpAmp - MCP6241Documento28 páginasOpAmp - MCP6241Ludwig SchmidtAinda não há avaliações

- Cmos 24aa256 & 24LC256Documento12 páginasCmos 24aa256 & 24LC256Someguy123551234512Ainda não há avaliações

- MemoriaDocumento7 páginasMemoriaEduardo TaglialavoreAinda não há avaliações

- Hanbit Hmn328D: Non-Volatile Sram Module 256kbit (32K X 8-Bit), 28pin Dip, 5V Part No. Hmn328DDocumento9 páginasHanbit Hmn328D: Non-Volatile Sram Module 256kbit (32K X 8-Bit), 28pin Dip, 5V Part No. Hmn328DDeepa DevarajAinda não há avaliações

- ¡ Semiconductor: MSM80C88A-10RS/GS/JSDocumento37 páginas¡ Semiconductor: MSM80C88A-10RS/GS/JSZarate BismkAinda não há avaliações

- 24 LC 16Documento32 páginas24 LC 16Jos RoAinda não há avaliações

- Max3160 Max3162Documento23 páginasMax3160 Max3162jb2015831Ainda não há avaliações

- 24LC04BDocumento22 páginas24LC04BcarlosAinda não há avaliações

- 450 Μa, 5 Mhz Rail-To-Rail Op Amp: Features DescriptionDocumento32 páginas450 Μa, 5 Mhz Rail-To-Rail Op Amp: Features DescriptionYusuf UçkunAinda não há avaliações

- CD4553 Datasheet OKDocumento13 páginasCD4553 Datasheet OKCong ThoAinda não há avaliações

- THC63LVDM83R/THC63LVDM63R: General Description FeaturesDocumento13 páginasTHC63LVDM83R/THC63LVDM63R: General Description Featureshenry96sAinda não há avaliações

- Cmos Sram K6F2016U4E Family: Document TitleDocumento9 páginasCmos Sram K6F2016U4E Family: Document TitleSash BremecAinda não há avaliações

- IC-ON-LINE - CN In74hc164a 4331941Documento6 páginasIC-ON-LINE - CN In74hc164a 4331941enriquevagoAinda não há avaliações

- MC 14521Documento12 páginasMC 14521rrebollarAinda não há avaliações

- Tle 6220 PDFDocumento17 páginasTle 6220 PDFFabio JuniorAinda não há avaliações

- 24 LC 64Documento12 páginas24 LC 64achuthkumarAinda não há avaliações

- MC6821PDocumento10 páginasMC6821Pbobyof91Ainda não há avaliações

- 8K X 8 Bit Fast Static RAM MCM6264C: MotorolaDocumento8 páginas8K X 8 Bit Fast Static RAM MCM6264C: Motorolajackiie16Ainda não há avaliações

- Dual Retriggerable Monostable Multivibrator: Order CodesDocumento12 páginasDual Retriggerable Monostable Multivibrator: Order Codeswrite2skAinda não há avaliações

- 7214Documento12 páginas7214Dan EsentherAinda não há avaliações

- Memoria Ram 6264Documento14 páginasMemoria Ram 6264DOMINGOS ALADIRAinda não há avaliações

- 2M X 32 Sdram: 512K X 32bit X 4 Banks Synchronous DRAM LVTTL (3.3V)Documento12 páginas2M X 32 Sdram: 512K X 32bit X 4 Banks Synchronous DRAM LVTTL (3.3V)vsc2012Ainda não há avaliações

- LTC2440 PDFDocumento28 páginasLTC2440 PDFyusufwpAinda não há avaliações

- 24lc08 EepromDocumento27 páginas24lc08 EepromIsmael Minchola CarhuasAinda não há avaliações

- 25LC160Documento21 páginas25LC160João JoséAinda não há avaliações

- 24 LC 32Documento14 páginas24 LC 32Shuchi Raju AgrawalAinda não há avaliações

- 1K 2.5V Dual Mode I C Serial EEPROMDocumento26 páginas1K 2.5V Dual Mode I C Serial EEPROMbalck_virusAinda não há avaliações

- Max7490 Max7491Documento18 páginasMax7490 Max7491xo9o6Ainda não há avaliações

- LTC4151 I2C Current and Voltage MonitorDocumento18 páginasLTC4151 I2C Current and Voltage MonitorNegru P. PlantatieAinda não há avaliações

- 24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMDocumento4 páginas24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMcabalaestebanAinda não há avaliações

- 7473Documento8 páginas7473Merényi OszkárAinda não há avaliações

- SN754410 Quadruple Half-H Driver: 1,2EN 1A 1Y V 4A 4Y Heat Sink and Ground 3Y 3A 3,4EN Heat Sink and GroundDocumento10 páginasSN754410 Quadruple Half-H Driver: 1,2EN 1A 1Y V 4A 4Y Heat Sink and Ground 3Y 3A 3,4EN Heat Sink and GroundFrankin Esteban Carmona AguilarAinda não há avaliações

- Cmos Sram K6T1008C2E Family: Document TitleDocumento11 páginasCmos Sram K6T1008C2E Family: Document TitleOmar LeonAinda não há avaliações

- Description Features: CMOS Low-Power Monostable/Astable MultivibratorDocumento15 páginasDescription Features: CMOS Low-Power Monostable/Astable Multivibratorதினேஷ் குமார்Ainda não há avaliações

- CD54HC14, CD74HC14, CD54HCT14, CD74HCT14: Features DescriptionDocumento16 páginasCD54HC14, CD74HC14, CD54HCT14, CD74HCT14: Features DescriptionAndrea DispoAinda não há avaliações

- D D D D D D D D D D D D: CD4066B Cmos Quad Bilateral SwitchDocumento20 páginasD D D D D D D D D D D D: CD4066B Cmos Quad Bilateral SwitchAnna Kaye Sapanhila AninAinda não há avaliações

- Dual Quick-PWM Step-Down Controller With Low-Power LDO and RTC Regulator For MAIN SuppliesDocumento24 páginasDual Quick-PWM Step-Down Controller With Low-Power LDO and RTC Regulator For MAIN SuppliesReklama BielskoAinda não há avaliações

- 4536BDocumento17 páginas4536BpandaypiraAinda não há avaliações

- CD40160BMS, CD40161BMS, CD40162BMS, CD40163BMS: CMOS Synchronous Programmable 4-Bit Counters FeaturesDocumento13 páginasCD40160BMS, CD40161BMS, CD40162BMS, CD40163BMS: CMOS Synchronous Programmable 4-Bit Counters FeaturesIonut TomaAinda não há avaliações

- ADC0802, ADC0803 ADC0804: Features DescriptionDocumento17 páginasADC0802, ADC0803 ADC0804: Features DescriptionSuryananda PadmadinataAinda não há avaliações

- 2.5V To 6.0V Micropower CMOS Op Amp: FeaturesDocumento42 páginas2.5V To 6.0V Micropower CMOS Op Amp: Featuresinside121Ainda não há avaliações

- 32x8 SRAM DatasheetDocumento12 páginas32x8 SRAM DatasheetAhmet AyanAinda não há avaliações

- Max232 Maxim IC DatasheetDocumento7 páginasMax232 Maxim IC Datasheetcyanide0007Ainda não há avaliações

- Ad 5933Documento2 páginasAd 5933Kaustuv MishraAinda não há avaliações

- How To Make A Powerpoint Presentation and How Not To: Amit Patra Department of Electrical Engineering IIT KharagpurDocumento4 páginasHow To Make A Powerpoint Presentation and How Not To: Amit Patra Department of Electrical Engineering IIT KharagpurKaustuv MishraAinda não há avaliações

- Embedded Sytem RoutroyDocumento16 páginasEmbedded Sytem RoutroyKaustuv MishraAinda não há avaliações

- Optimal Reception of Digital SignalsDocumento40 páginasOptimal Reception of Digital SignalsKaustuv Mishra100% (1)

- Line Follower Robot PresentationDocumento25 páginasLine Follower Robot Presentationmirrayhan0867% (6)

- Intel® 64 and IA-32 Architectures Software Developer's ManualDocumento132 páginasIntel® 64 and IA-32 Architectures Software Developer's Manualaqua01Ainda não há avaliações

- Sdram PDFDocumento9 páginasSdram PDFMayank JaiswalAinda não há avaliações

- 21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Documento4 páginas21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Rohan RAinda não há avaliações

- Sensor de Temperatura Datasheet - 1631ADocumento15 páginasSensor de Temperatura Datasheet - 1631ARick VilcaAinda não há avaliações

- Questions: B. Write Notes On: FpgaDocumento2 páginasQuestions: B. Write Notes On: FpgaunnidigiAinda não há avaliações

- OptiPlex XE3 Spec SheetDocumento4 páginasOptiPlex XE3 Spec SheetIrving ChamosaAinda não há avaliações

- Computer One Liner Facts-01 Secured by Vivek (Uim)Documento2 páginasComputer One Liner Facts-01 Secured by Vivek (Uim)ravivivekAinda não há avaliações

- DDI0243C Adk r3p0 TRMDocumento226 páginasDDI0243C Adk r3p0 TRMdraksunilAinda não há avaliações

- Ulcreforr.: AnsmacrDocumento4 páginasUlcreforr.: AnsmacrarcAinda não há avaliações

- Homework6 AnsDocumento12 páginasHomework6 Ansnada abdelrahmanAinda não há avaliações

- 10G 40G KintexUltraScale ReferenceDesignDocumento2 páginas10G 40G KintexUltraScale ReferenceDesignlitoduterAinda não há avaliações

- Beep CodesDocumento5 páginasBeep CodesAkibo Tunde Williamson DaviesAinda não há avaliações

- E-Frog Game: Senior Design I EEL 4914C Group #6Documento111 páginasE-Frog Game: Senior Design I EEL 4914C Group #6Darrius Dela PeñaAinda não há avaliações

- Internal Memory: Presented By: SELINA YOUSAF ROLL NO: 0632-BH-MB-19 Section: H1Documento10 páginasInternal Memory: Presented By: SELINA YOUSAF ROLL NO: 0632-BH-MB-19 Section: H1Selina YousafAinda não há avaliações

- 2 Pic18f452Documento29 páginas2 Pic18f452Mohan NatrajanAinda não há avaliações

- Addressing ModesDocumento12 páginasAddressing ModesAbdul Rafay HammadAinda não há avaliações

- 3vsb Should Be Volts Motherboard - Google SearchDocumento2 páginas3vsb Should Be Volts Motherboard - Google Searchoff emAinda não há avaliações

- PIC16C773Documento202 páginasPIC16C773Luis Oliveira SilvaAinda não há avaliações

- Awrdiff 1 1350 1 1351Documento135 páginasAwrdiff 1 1350 1 1351ursvenkatAinda não há avaliações

- Expt05 - BCD To 7-Segment DecoderDocumento3 páginasExpt05 - BCD To 7-Segment DecoderDvizma SinhaAinda não há avaliações

- Digital Fabrication in Architecture PDFDocumento192 páginasDigital Fabrication in Architecture PDFAndrada Iulia NeagAinda não há avaliações

- Diploma Engineering: Laboratory ManualDocumento101 páginasDiploma Engineering: Laboratory ManualShivam MotaAinda não há avaliações

- Storage Elements Final 4Documento18 páginasStorage Elements Final 4Menard NavaAinda não há avaliações

- CHP 6Documento16 páginasCHP 6juanm01Ainda não há avaliações

- A/D Converter For Robots: Tilo GockelDocumento1 páginaA/D Converter For Robots: Tilo GockelAg Cristian100% (1)

- Assignment 3 - 2 Microcontrollers With DatasheetsDocumento2 páginasAssignment 3 - 2 Microcontrollers With Datasheetsapi-42328551276% (45)

- My Expectation in ICT-SimonDocumento4 páginasMy Expectation in ICT-SimonSimon Lance DuranAinda não há avaliações

- Lab Manual EC1010 Digital Systems LabDocumento51 páginasLab Manual EC1010 Digital Systems Labsudipta2580Ainda não há avaliações

- DLD Lab 02 - Combinational LogicDocumento13 páginasDLD Lab 02 - Combinational LogicImran ZubairAinda não há avaliações