Escolar Documentos

Profissional Documentos

Cultura Documentos

Semiconductor Memories

Enviado por

Gowtham SpDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Semiconductor Memories

Enviado por

Gowtham SpDireitos autorais:

Formatos disponíveis

CHAPTER 1

INTRODUCTION TO ADVANCED

SEMICONDUCTOR MEMORIES

1.1. SEMICONDUCTOR MEMORIES OVERVIEW

The goal of Advanced Semiconductor Memories is to complement the material

already covered in Semiconductor Memories. The earlier book covered the following topics: random access memory technologies (SRAMs and DRAMs) and

their application to specific architectures; nonvolatile technologies such as the

read-only memories (ROMs), programmable read-only memories (PROMs),

and erasable PROMs in both ultraviolet erasable (UVPROM) and electrically

erasable (EEPROM) versions; memory fault modeling and testing; memory

design for testability and fault tolerance; semiconductor memory reliability;

semiconductor memories radiation effects; advanced memory technologies; and

high-density memory packaging technologies [1]. This section provides a

general overview of the semiconductor memories topics that are covered in

Semiconductor Memories.

In the last three decades of semiconductor memories' phenomenal growth,

the DRAMs have been the largest volume volatile memory produced for use

as main computer memories because of their high density and low cost per bit

advantage. SRAM densities have generally lagged a generation behind the

DRAM. However, the SRAMs offer low-power consumption and high-performance features, which makes them practical alternatives to the DRAMs.

Nowadays, a vast majority of SRAMs are being fabricated in the NMOS and

CMOS technologies (and a combination of two technologies, also referred to

as the mixed-MOS) for commodity SRAMs.

1

INTRODUCTION TO ADVANCED SEMICONDUCTOR

MOS Memory Market ($M)

MEMORIES

Non-Memory IC Market ($M)

Memory % of Total IC Market

300,000

40%

250,000

30%

200,00U

"o

Q

15

</>

150,000

20%

2

a.

100,000

2

10%

50,000

0

MOS Memory Market ($M)

Non-Memory IC Market ($M)

Memory % of Total IC Market

96

97

98

99

00

01*

02*

03*

04* 05*

36,019 29,335 22,994 32,288 49,112

51,646 56,541 70,958 94,541 132,007

78,923 90,198 86,078 97,930 126,551 135,969 148,512 172,396 207,430 262,172

31% . 25% 21% 25% 28%

28%

28% 29% 31% 33%

0%

Year

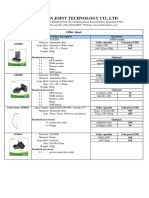

Figure 1.1

Semiconductor memory market as a percentage of the total IC market [2].

In 1995, semiconductor memories accounted for 42% of the total IC market,

but following 1995's strong growth, memory prices collapsed for the next three

years. In 1998, memory devices represented only 2 1 % of the total IC market.

During the 1990s, semiconductor memory sales averaged approximately 30%

of total IC sales. It is forecasted that the memory portion of total IC sales will

gradually increase through year 2005. Figure 1.1 shows the semiconductor

memory market as a percentage of the total IC market [2].

In high-density and high-speed applications, various combinations of bipolar and MOS technologies are being used. In addition to MOS and bipolar

memories, referred to as the "bulk silicon" technologies, silicon-on-insulator

(SOI) isolation technologies have been developed for improved radiation

hardness.

SRAM density and performance are usually enhanced by scaling down the

device geometries. Advanced SRAM designs and architectures for 4 to 16-Mb

chips with submicron feature sizes have been developed and currently available

as commodity chips. Application-specific memory designs include first-in-firstout (FIFO) buffer memory, in which the data are transferred in and out

serially. The dual-port RAMs allow two independent devices to have simultaneous read and write access to the same memory. The content addressable

memories (CAMs) are designed and used both as the embedded modules on

SEMICONDUCTOR MEMORIES OVERVIEW

larger VLSI chips, and as stand-alone memory for specific system applications.

A major improvement in DRAM evolution has been the switch from

three-transistor (3T) designs to one-transistor (IT) cell design, enabling production of 4- to 16-Mb density chips that use advanced 3-D trench capacitor

and stacked capacitor cell structure. Currently, 64-Mb to 1-Gb DRAM chips

are in production, and multigigabit density chips are being developed. The

technical advances in multimegabit DRAMs have resulted in greater demand

for application-specific products such as the pseudostatic DRAM (PSRAM),

which uses dynamic storage cells but contains all refresh logic on-chip that

enables it to function similarly to an SRAM. Video DRAMs (VDRAMs) have

been produced for use as the multiport graphic buffers. Some other examples

of high-speed DRAM innovative architectures are synchronous DRAMs

(SDRAMs), cache DRAMs (CDRAMs), and Rambus DRAMs (RDRAMs).

Nonvolatile memories (NVMs) have also experienced tremendous growth

since the introduction in 1970 of a floating polysilicon gate-based erasable

program read-only memory (EPROM), in which hot electrons are injected into

the floating gate and removed either by ultraviolet internal photoemission

or by Fowler-Nordheim tunneling. The EPROMs (also referred to as the

UVEPROMs) are erased by removing them from the target system and

exposing them to ultraviolet light. An alternative to EPROM (or UVEPROM)

has been the development of electrically erasable PROMs (EEPROMs), which

offer in-circuit programming flexibility. Several variations of this technology

include metal-nitride-oxide-semiconductor (MNOS), silicon-oxide-nitrideoxide-semiconductor (SONOS), floating gate tunneling oxide (FLOTOX),

and textured polysilicon. The FLOTOX is most commonly used EEPROM

technology. An interesting NVM architecture is the nonvolatile SRAM, a

combination of EEPROM and SRAM in which each SRAM has a corresponding "shadow" EEPROM cell.

Flash memories based on EPROM or EEPROM technologies are devices

for which contents of all memory array cells can be erased simultaneously,

unlike the EEPROMs that have select transistors incorporated in each cell to

allow for the individual byte erasure. Therefore, the flash memories can be

made roughly two or three times smaller than the floating gate EEPROM cells.

Flash memories are available in 8- to 512-Mb densities as production devices,

and even higher densities in development.

DRAMs are currently (and predicted to be in the future) the largest memory

segment in terms of dollar sales. After DRAMs the SRAMs and flash markets

represent the next two largest memory segments. In year 2000, the flash

memory market surpassed the SRAM market and became the second-largest

memory market segment. Both DRAM and flash market shares are expected

to continue growing through 2005, although flash memory at a much faster

pace. The remaining memory segments are predicted to remain stable.

INTRODUCTION TO ADVANCED SEMICONDUCTOR MEMORIES

Figure 1.2a shows a comparison of different MOS technologies market share

projected to year 2005 [2]. It is predicted that in year 2005, the DRAMs will

account for just 60% of the memory market, whereas flash memory sales is

forecast to account for 29% of the total memory market. Figure 2.2b shows

percentages for each MOS memory technology market for the year 2000 and

predicted values for the year 2005.

Semiconductor Memories reviewed various memory failure modes and mechanisms, fault modeling, and electrical testing [1]. A most commonly used fault

model is the single-stuck-at fault (SSF), which is also referred to as the classical

standard fault model. However, many other fault models have also been

developed for transition faults (TFs), address faults (AFs), bridging faults

(BFs), coupling faults (CFs), pattern-sensitive faults (PSFs), and the dynamic

(or delay) faults. A large percentage of physical faults occurring in the ICs can

be considered as the bridging faults (BFs), consisting of shorts between the two

or more cells or lines. Another important category of faults that can cause the

RAM cell to function erroneously is the coupling or PSFs.

In general, the memory electrical testing consists of the dc and ac parametric

tests and functional tests. For RAMs, various functional test algorithms have

been developed for which the test time is a function of the number of memory

bits (n) and range in complexity from O(n) to O(n2). The selection of a

particular set of test patterns for a given RAM is influenced by the type of

failure modes to be detected, memory bit density that influences the test time,

and the memory automated test equipment (ATE) availability.

Advanced megabit memory architectures are being designed with special

test features to reduce the test time by the use of multibit test (MBT), line mode

test (LMT), and built-in self-test (BIST). Application-specific memories such as

the FIFOs, video RAMs, synchronous static and dynamic RAMs, and doublebuffered memories (DBMs) have complex timing requirements and multiple

setup modes that require a suitable mix of sophisticated test hardware, design

for testability (DFT), and BIST approach.

In general, the memory testability is a function of variables such as circuit

complexity and design methodology. Therefore, the DFT techniques, RAM

and ROM BIST architectures, memory error detection and correction

(EDAC), and the memory fault tolerance are important design considerations.

Structured design techniques are based upon the concept of providing uniform

design to increase controllability and observability. The commonly used

methodologies include the level-sensitive scan design (LSSD), scan path,

scan/set logic, random access scan, and the boundary scan testing (BST). The

RAM BIST implementation strategies include the use of algorithmic test

sequence (ATS), the 13-N March algorithms with a data-retention test, a

fault-syndrome-based strategy for detecting the PSFs, and built-in logic block

observation (BILBO) technique. For the embedded memories, various DFT

SEMICONDUCTOR MEMORIES OVERVIEW

(a)

j'jl DRAM ($M)

QTSRAM ($M)

E3 Flash ($M)

ffother Memory ($M)

80,000

60,000

2

o

r

O

40,000 -

|

2

20,000 -

DRAM SM)

SRAM <$M)

Flash <SM>

Other Memory ($M)

96

97

98

25,132

4.745

2.611

3,531

19,796

3.842

2,702

2.993

14,011

3,895

2,493

2,595

00

20,715

4.662

4,561

2.350

29,176

6.291

10.446

or

27.300

7,075

14,400

2.871

02"

03*

04"

05"

29,935

7.676

16,235

2,695

38,615

8.9O4

20,760

2,659

53,290

10.6B5

27.845

2.721

77.270

ia356

38,600

2,701

Year

(b)

2005 MOS Memory Market

(S132.0B)

2000 MOS Memory Market

($49.1 B)

EEPROM

"3% 1

Flash

21%

SRAM

HUM

2%

10%

All Other

2%

EPROM

1%

SRAM

13%

Flash

29%

DRAM

59%

DRAM

60%

Figure 1.2 (a) Comparison of different MOS memory technologies market share, (b) Percentages

for each MOS memory technology market for year 2000 and predicted values for year 2005 [2].

and BIST techniques have been developed such as the scan-path-based flagscan register (FLSR) and the random-pattern-based circular self-test path

(CSTP). Advanced BIST architectures have been implemented to allow parallel

testing with on-chip test circuits. The current generation megabit memory

chips include spare row and columns (redundancies) in the memory array to

INTRODUCTION TO ADVANCED SEMICONDUCTOR MEMORIES

compensate for the fault cells. In addtion, to improve the memory chip yield,

techniques such as built-in self-diagnosis (BISD) and built-in self-repair (BISR)

are used.

The errors in semiconductor memories can be broadly categorized as the

hard failures caused permanent physical damage to the device and soft errors

caused by alpha particles or the ionizing dose radiation environments. The

most commonly used error-correcting codes (ECC) that are used to correct

hard and soft errors are the single-error correction and double-error detection

(SEC-DED) codes, also referred to as the Hamming Codes. Multimegabit

DRAM chips have been developed that use redundant word and bit lines in

conjunction with ECC to produce optimized fault tolerance effect. To recover

from the soft errors (transient effects), memory scrubbing techniques are often

used, which are based upon the probabilistic or deterministic models. These

techniques can be used to calculate the reliability rate R(t) and mean time to

failure (MTTF) of the memory system.

Semiconductor Memories reviewed general reliability issues for semiconductor devices such as the memories, RAM failure modes and mechanisms,

nonvolatile memory reliability, reliability modeling and failure rate prediction,

design for reliability, and reliability test structures [1]. The general reliability

issues pertaining to semiconductor devices in bipolar and MOS technologies

are applicable to memories also. In addition, there are special reliability issues

and failure modes, which are of special concern for the RAMs. These issues

include gate oxide reliability defects, hot-carrier degradation, the DRAM

capacitor charge-storage and data-retention properties, and DRAM soft-error

failures. The memory gate dielectric integrity and reliability are affected by all

processes involved in the gate oxide growth.

The reduced MOS transistor geometries from scaling of the memory devices

has made them more susceptible to hot-carrier degradation effects. Nonvolatile

memories, just like volatile memories, are also susceptible to some specific

failure mechanisms. In the floating gate technologies such as the EPROM and

EEPROMs, data retention characteristics and number of write/erase cycles

without degradation (endurance) are the most critical reliability concerns.

Reliability failure modeling is the key to the failure rate prediction, and there

are many statistical distributions that are used to model various reliability

parameters. The method of accelerated stress aging for semiconductor devices

such as memories is commonly used to ensure long-term reliability. An

approach commonly used by the memory manufacturers in conjunction with

the end-of-line product testing has been the use of reliability test structures and

process (or yield) monitors incorporated at the wafer level and "drop-in" test

sites on the chip. The purpose of reliability testing is to quantify the expected

failure of a device at various points in its life cycle.

SEMICONDUCTOR MEMORIES OVERVIEW

The space radiation environment poses a certain radiation risk to all

electronic components on earth-orbiting satellites and the planetary mission

spacecrafts. The cumulative effect of ionization damage from charged particles

present in the natural space environment, such as the electrons and protons on

semiconductor memories, can be significant. Ionizing radiation damage causes

changes in memory circuit parameters such as standby power supply currents,

I/O voltage threshold levels and leakage currents, critical path delays, and

timing specification degradations. The single-event phenomenon (SEP) in the

memories is caused by high-energy particles such as those present in the cosmic

rays passing through the device to cause (a) single-event upsets (SEUs) or soft

errors and (b) single-event latchup (SEL), which may result in hard errors. The

impact of SEU on the memories, because of their shrinking dimensions and

increasing densities, has become a significant reliability concern. The nonvolatile MOS memories are also subject to radiation degradation effects.

The memory circuits can be designed for total dose radiation hardness by

using optimized processes (e.g., hardened gate oxides and field oxides) and

good design practices. The bulk CMOS memories have been hardened to SEU

by using an appropriate combination of processes and design techniques.

Radiation sensitivity of unhardened memory devices can vary from lot to lot;

and for space applications, radiation testing is required to characterize the lot

radiation tolerance. Semiconductor Memories discussed the following topics in

detail: radiation-hardening techniques, radiation-hardening design issues, radiation testing, radiation dosimetry, wafer level testing, and test structures [1].

Advanced semiconductor memories technologies include ferroelectric RAMs

(FRAMs or FeRAMs), magnetoresistive RAMs (MRAMs), analog memories,

and quantum-mechanical switch memories. These technologies were briefly

reviewed in Semiconductor Memories.

The increasing requirements for denser memories have led to further

compaction of standard packaging approach to hybrid manufacturing techniques and multichip modules (MCMs). For the assembly of MCMs, various

interconnect technologies have been developed such as the wire-bonding, tape

automated bonding (TAB), flip-chip bonding, and high-density interconnect

(HDI). An extension of 2-D planar technology has been the 3-D concept, in

which the memory chips are mounted vertically prior to the attachment of a

suitable interconnect. The 3-D approach can provide higher packaging densities because of (a) reduction in the substrate size, module weight, and volume,

(b) lower line capacitance and drive requirements, and (c) reduced signal

propagation delay times. Semiconductor Memories reviewed commonly used

memory packages, memory hybrids and 2-D MCMs, memory stacks and 3-D

MCMs, memory MCM testing and reliability issues, memory cards, and

high-density memory packaging future directions [1].

INTRODUCTION TO ADVANCED SEMICONDUCTOR MEMORIES

1.2. ADVANCED SEMICONDUCTOR MEMORY DEVELOPMENTS

This book, Advanced Semiconductor Memories, reviews in detail future advances in SRAMs, high-performance DRAMs, application-specific DRAM

designs and architectures, nonvolatile memory technologies, embedded memory designs and applications, and future gigabit-to-terabit memory directions.

These advanced developments are briefly summarized in this section.

Advanced SRAM technology developments are reviewed in Chapter 2.

SRAMs are currently available for both asynchronous and synchronous

designs in a wide variety of speeds and architectures. However, synchronous

designs are preferred and use one or more external clock signals to control the

SRAM operations, and they result in improved timing controls. This allows the

reduction of the device access times and cycle times to match the clock cycles

of the fastest PC and RISC processors available. The synchronous SRAM

(SSRAM) data buses are usually flow-through or pipelined. In the communication networks, SRAMs are being used as data buffers between the input and

output ports, and they are also being used as high-speed lookup tables

containing addresses and other information to route data stream from the data

source to destination.

SRAM speed has been enhanced by scaling down the device geometries, as

well as by improvement in processes and circuit design techniques for the

optimization of chip architecture. For low-voltage SRAMs, the designers are

using various techniques to minimize the power consumption. Fast SRAMs

have applications in cache memory system designs. Some examples of highperformance SRAM architectures are described, such as the flow-through

SSRAMs, zero bus turnaround (ZBT) SRAMs, No Turnaround Random

Access Memory (NfRAM) pipelined, quad-data-rate (QDR) SRAMs and

double-data-rate (DDR) SRAMs.

BiCMOS technology is more important in applications that require compatibility with high-performance microprocessor clock speeds. However, BiCMOS process is more complex because of the additional steps required,

compared to a standard CMOS process. The silicon-on-insulator (SOI) technology in SRAM applications offers significant performance advantages due to

the reduction in device junction capacitance. The major advantages of the SOI

technology include latchup free operation and improved soft-error rate (SER)

performance. SOI technology SRAMs are finding applications in critical

military and space applications with high total dose radiation and transient

survivability requirements (see Semiconductor Memories, Chapter 7).

The basic SRAM performance can often be improved by the addition of

some extra logic control circuitry to provide specialty SRAMs. For example,

in systems with multiple processors or devices requiring simultaneous access to

the SRAM, multiport memories can be used. An extension of this concept is

ADVANCED SEMICONDUCTOR MEMORY DEVELOPMENTS

first-in-first-out (FIFO) memories available in various configurations for the

use as buffers for multiprocessors and serial communication networks. A

specialty device is content addressable memory (CAM) that can output an

address (or addresses) when data are presented to certain inputs. Design and

architecture examples of three types of specialty memories are presented:

multiport RAMs, FIFOs, and CAMs.

Semiconductor Memories provided an introduction to the DRAM technology evolution, as well as technology developments in advanced architectures

[1]. Chapter 3 (High-Performance Dynamic Random Access Memories) in the

present book provides a detailed overview of further DRAM technology

advances, scaling issues, and future trends. The new-generation DRAMs use

various refresh schemes, as well as provide several modes for accessing data in

the storage cells. For scaling to 64-Mb and higher densities, it is necessary to

increase the cell's storage capacity by using 3-D cell structures, along with

trench or stacked capacitors. Enhanced DRAM (EDRAM) can be used to

replace standard, slow full-page mode (FPM) or EDO DRAM for some higher

performance applications that require large amounts of very fast memory.

Extended-Data-Out (EDO) DRAMs have the advantage over conventional

FPM memory is that it allows for a shorter page mode cycle time (or faster

data rate) while accessing data within a single page in memory. An example of

64-Mb EDO DRAM available from Infineon Technologies is discussed.

Single-data-rate synchronous DRAMs (SDRAMs) and synchronous graphic

RAMs (SGRAMs) use the same basic memory cell and the same word-line

drivers as the EDO DRAMs. However, their performance is limited by the

interface requirements. Therefore, the double-data-rate (DDR) SDRAM/

SGRAM were introduced as an architectural enhancement by incorporating

several major features. An example of architecture and functional operations

of a commercially available 256-Mb SDRAM from Micron Technology is

presented.

The enhanced SDRAM (ESDRAM) is an evolutionary modification to the

JEDEC standard for 16-Mb SDRAM, which incorporates changes to a

standard DRAM to reduce latency, increase the bandwidth, and allow for

concurrent operations to the same bank. An example of 16-Mb ESDRAM

from Enhanced Memory Systems, Inc., is discussed. Cache DRAM (CDRAM)

introduced by Mitsubishi Corporation is an SDRAM with an on-chip cache in

the form of a separate SRAM array integrated with the DRAM array.

However, in CDRAM (unlike the EDRAM), the SRAM and DRAM operations can be separately controlled. An example of 16-Mb CDRAM from

Mitsubishi Corporation is provided.

The virtual channel memory (VCM) memory core technology was developed by NEC Incorporated, to improve the memory data throughput efficiency

and targeted for multiple users, multitasking, and interleaved access environ-

10

INTRODUCTION TO ADVANCED SEMICONDUCTOR MEMORIES

ment. Another example of advanced memory architecture is a 64-Mb fast-cycle

RAM (FCRAM) that involves basic changes in the DRAM core concept by

operating the memory like a synchronous SRAM using the dynamic core.

Another example of 256-Mb DRAM architecture is given that provides up to

x 32-bit-wide organization and uses an exchangeable, hierarchical data line

scheme to minimize the number of sense amplifier circuits.

Major gigabit DRAM scaling issues are discussed, using several examples of

1-Gb SDRAM cells and architectures that have been recently developed.

In gigabit DRAM scaling, one of the major issues is the reduction of array

power consumption without degrading the operating margin of the memory

device and other characteristics. Multivalued and multilevel RAMs

(MLDRAMs) schemes have been proposed, in which the amount of voltage

placed across the capacitor is varied to represent the multiple states. If the

number of states in a single memory cell is doubled, then the storage capacity

of the memory cell can be doubled. Some of the proposed MLDRAM designs

are reviewed, including a 4-Gb DRAM with multilevel storage memory cells

that utilize data storage at four levels, where each level corresponds to a 2-bit

data storage in a single memory cell. This approach can reduce the effective

cell size by 50%.

SOI DRAMs are under development for which the major advantages

include a superior SER, better static data retention time characteristics, and

potential for higher integration density than the bulk-Si-based DRAMs. An

overview of various isolation processes used for SOI and feature comparison of

the bulk-Si, partially depleted (PD) and fully depleted (FD) SOI transistors is

provided.

The technical advances in multimegabit DRAMs have resulted in greater

demand for memory designs incorporating specialized performance requirements for applications, such as the high-end desktops/workstations, PC servers/mainframes, 3-D graphics, network routers and switches. Some earlier

examples of these application specific DRAMs, such as the pseudostatic

DRAMs (PSRAMs), or virtual static DRAMs (VSRAMs) were discussed in

Semiconductor Memories [1]. Chapter 4 in the present book describes latest

developments in application specific memory architectures and designs in more

details, such as the Video RAMs, SGRAMs, DDR SGRAMs, Rambus

Technology, Synchronous Link DRAMs (SLDRAMs), and 3-D RAMs.

The video RAM (VRAM) was developed to increase the bandwidth of raster

graphics display frame buffers. An example of the architecture of a 4-Mb

VRAM is provided. A further improvement was SGRAMs that are very similar

to the SDRAMs, except that they have several additional functions to improve

their effectiveness in graphic systems design. Examples of a 64-Mb DDR

SGRAM from Fujitsu Semiconductor, and a 256-Mb fast-cycle RAM

(FCRAM) are provided.

ADVANCED SEMICONDUCTOR MEMORY DEVELOPMENTS

11

Direct RDRAM is a high-speed memory for graphic applications and offers

double the word width of the original RDRAM, offering storage capabilities of

64/72 Mb, 128/144 Mb, and 256/288 Mb. Concurrent RDRAMs perform two

bank operations simultaneously, to allow high transfer rates using interleaved

transactions. These memories can operate at speeds of 600 MHz, achieving

data transfer speeds of 1.2 Gbytes/s. Various Rambus technologies and

architectures including command sets, protocol formats, and functional blocks

are discussed. SLDRAM is a new memory interface specification developed

through the cooperative efforts of leading semiconductor memory manufacturers with a goal to meet the high data bandwidth requirements of emerging

processor architectures, as described in IEEE Standard PI596.4. An example

of a very-high-speed, packet-oriented, pipelined, 4-Mb x 18 synchronous

SLDRAM available from Micron Technology, Inc., is provided.

Mitsubishi Corporation pioneered the introduction of a family of 3-D RAM

for high-performance 3-D graphics hardware. The architecture and various

functional blocks of this 3-D RAM family are discussed. Currently, in application-specific, high-performance memory designs, the competing technologies

are SDRAM, DDRSDRAM, Rambus DRAM, and SLDRAMs. An overview

of various memory system design considerations, such as the peak bandwidth

performance comparison, granularity, and latency, is provided.

Figure 1.3 provides a flow chart of various types of some commonly used

RAMs.

RAM

Conventional

DRAM

DRAM

FPM

DRAM

High-spaed DRAM

Synchronous-type

DRAM

DDR SDRAM

DirectRDRAM

Next-generation

High-speed DRAM

SynchLink DRAM

Graphics

Memory

SRAM

Conventional

Dual Port

Graphics Buffer

Synchronous

type

SGRAM

DDR SGRAM

SSRAM

DDR SSRAM

Conventional

SRAM

Synchronous-type

SRAM

Figure 1.3

A flow chart of various types of some commonly used high speed RAMs.

12

INTRODUCTION TO ADVANCED SEMICONDUCTOR MEMORIES

Nonvolatile memories (NVMs) are characterized by their ability to retain

the stored data even with the device power off for indefinite periods of time, as

compared to the volatile memories (such as the SRAMs and DRAMs) that lose

the stored information under these conditions. Some examples of the NVMs

are ROMs, PROMs, EPROMs, and EEPROMs designs and technologies.

Special memories are also available such as nonvolatile random access memory

(NOVRAM) or shadow RAM configurations that combine on the same chip,

a SRAM array, and a backup EEPROM array of equal bits. In recent years,

an area of interest in advanced nonvolatile memories has been the development

of thin-film ferroelectric (FE) technology to build ferroelectric RAMs (FRAMs)

as substitutes for the NOVRAMs, These NVM technologies were briefly

discussed in Semiconductor Memories, Chapter 3 [1].

Serial EEPROMs are considered low-cost solution for the applications that

do not require the high capability or short access times of traditional NOR

and NAND type of architectures. The flash memory architecture has split

along two main paths: traditional random access devices based on the NOR

designs and byte-serial devices based on the NAND/AND architectures that

have closer resemblance to the solid-state disk drives. Each of these approaches

is suited for different applications, and finding wider usage throughout the

industry. Chapter 4 of the present book provides a detailed overview of the

EPROM/EEPROM and FRAM (or FeRAM) technology developments and

architectures.

In the growth of multipurpose flash memory market, the demands for all

densities of flash are rising simultaneously, including that of low-density flash

devices. In general, the flash memory technology can be divided into two broad

categories: (a) NOR-based flash targeted toward the program code/data

storage applications and (b) NAND-based flash ideal for mass storage applications. The NAND-based flash memories of 256-Mb and higher densities are

already in mass production, with 512-Mb and higher densities also being

targeted by the suppliers. The NOR-type flash memories are available with

typical access times of 35 ns for 1-Mb memory devices and 45 ns for 128-Mb

capacities. The latest approach to provide high storage densities in flash

memories is the use of multilevel cell (MLC) charge storage per cell techniques.

The EPROM/EEPROM technology is based on the charge storage in

discrete trapping centers of an appropriate dielectric layer, or on a completely

electrically isolated gate referred to as the "floating-gate" device. The floatinggate cell theory and operations, along with charge transport mechanisms such

as the channel hot electron (CHE) injection and Fowler-Nordheim tunneling,

are presented.

The EPROM cell developments over last two decades include T-cell, X-cell,

staggered virtual ground array (SVG) array cell, alternate metal ground

(AMG) array cell, and so on. The EEPROM/flash memory cell arrays include

ADVANCED SEMICONDUCTOR MEMORY DEVELOPMENTS

13

various NOR cell structures and NAND flash cells. An EEPROM technology

that was developed earlier is the metal-nitride-oxide-silicon (MNOS) and

(poly)silicon-oxide-nitride-oxide-semiconductor (SONOS), and floatinggate tunnel oxide (FLOTOX) cells that were briefly discussed in Semiconductor

Memories [1].

Chapter 5 in the present book reviews the latest developments in EEPROM/flash cells and array structures. Four major flash architectures are

reviewed: NOR, NAND, DINOR, and AND along with representative memory devices currently available from vendors, such as a 32-Mb simultaneous

read/write NOR-based flash memory from Advanced Microdevices, Inc.

(AMD), 32-Mb dual-plane flash memory from Intel Corp., 256-Mb UltraNAND flash memory from Samsung, Inc., and 16-Mb DINOR flash memory

from Mitsubishi, Inc. The new developments include a proposed 3.3-V, 16-Mb

nonvolatile memory using NAND flash architecture, which has operation

virtually identical to that of a DRAM.

The latest development in flash memory is the concept of multilevel (ML)

that refers to the storage of more than one bit per cell, in order to increase the

device density and reduce the cost per bit. In principle, the ML concept can be

coupled with various types of memory architectures, such as the NOR and

NAND to implement a 2-bit/cell scheme. However, there are several ML

programming, sensing, and reliability issues that need to be addressed in each

of these architectures. An example of this approach is Intel's multilevel

NOR-based architecture, which is currently capable of storing two bits per

memory cell but may be scalable to three bits per cell. An overview of Intel's

3-V StrataFlash NOR-based memory, a proposed multilevel 64-Mb NAND

flash memory design, a 512-Mb NAND flash memory from Toshiba Corp., and

a 256-Mb multilevel cell AND flash memory from Hitachi Corp. is provided.

Semiconductor Memories reviewed general reliability issues such as the gate

oxide breakdown, electromigration, hot-carrier degradation, metallization corrosion, and so on, which are generic among various semiconductor technologies [1]. However, there are a number of failure modes and mechanisms that

are specific to the EPROM/EEPROMs such as data-retention characteristics

and the number of write/erase cycles without degradation (endurance), which

are critical reliability concerns. The major issues concerning yield and reliability of flash memories are flash overerase, program/read disturbs, program/read

endurance, flash data retention failures, and flash hot carrier reliability effects.

In general, the reliability of MLMs is more critical than that of the

conventional two-level logic (1 bit/cell) because of the requirements for a larger

threshold (Vt) window (to keep adequate spacing among the stored levels)

and/or reduced spacing between the adjacent levels (to limit the increase in Vt

window). Chapter 5 in the present book reviews the major reliability and yield

issues for flash memories.

14

INTRODUCTION TO ADVANCED SEMICONDUCTOR MEMORIES

FRAM is a RAM-based device that uses the ferroelectric (FE) effect as the

charge storage mechanism, based on the ability of material to store an

electrical polarization in the absence of an applied electric field; that is, a

ferroelectric memory stores data within a crystalline structure. In FRAM, the

memory readout is a destructive operation, and therefore each read access is

accompanied by a precharge operation that restores the memory state. A write

operation is very similar to a read operation and requires no system overhead.

Some of the most widely used FE materials are PZT (PbZr^Tii _A-O3) and SBT

(SrBi 2 Ta 2 O 9 ).

An example of the FRAM is 256-Kb device that uses a two-transistor,

two-capacitor (2T2C) memory cell design from Ramtron Corp. The new

developments include one-transistor, one-capacitor (1T1C) memory cell design

suitable for 1-Mb and higher-density designs. A proposed DRAM-like FeRAM

cell array, referred to as the depletion FeRAM (DeFeRAM), and a 4-Mb

FRAM with 1T1C cell design are discussed. A new chain FRAM (CFRAM)

architecture has been proposed, which can realize 4F 2 size memory cell and

random access; and when 16 cells are connected in series, the chip size can be

reduced to 63% to that of a conventional FRAM.

Metal-ferroelectric semiconductor (MFS) devices that are considered candidates for high-density NVM applications are based on the principle that

information can be stored as a polarization direction rather than as a charge

on a capacitor. Ferroelectric films used as memory storage elements have

significant reliability concerns, such as the aging/fatigue effects, thermal stability, effects of electric fields, and so on. These are briefly reviewed in Chapter 5.

As the processor performance has increased from several hundred megahertz to 1 GHz and beyond, idle wait time in relatively slower DRAMs

has increased, leading to a memory-processor performance gap. The fastest

growing trend in advanced semiconductor memory is the embedded memories designs and applications. Memory technology for embedded memory

has a wide variation, ranging from small blocks of ROMs, hundreds of

kilobytes for the cache RAMs, high density (several megabits) of DRAMs, and

small to medium density nonvolatile memory blocks of EEPROMs and flash

memories. Embedded SRAM is one of the most frequently used memory

embedded in logic chips. Chapter 6 discusses embedded memory designs and

applications.

Currently, the two major approaches for embedded memories development

are fabricating memory in a logic-based process versus fabricating logic in a

DRAM-based process technology. A recent trend driving the integration of

DRAM into logic chips is the need to reduce power by eliminating the need

for off-chip drivers and improving performance. Another advantage is noise

reduction. A key advantage of the embedded memory approach is the higher

packaging density and board space savings, which is a desirable feature for

ADVANCED SEMICONDUCTOR MEMORY DEVELOPMENTS

15

applications such as the notebook computers and portable communication

devices. The relative tradeoffs between the two approaches have spawned

arguments regarding which technology should be preferred over the other.

In a PC system, the major goal of using a cache memory is to increase the

DRAM subsystem performance by reducing the latency and increasing bandwidth. Cache memory design tradeoffs are reviewed, and an example of cache

architecture implementation for a popular TI DSP is provided.

The demand for embedded memories is on the rise in current generation of

ultra-large-scale integration (ULSI) and system-on-chip (SOC) level designs

that require large amounts of SRAM, multiport RAM, DRAM, ROM, and

EEPROM flash memories. Examples of some of the advanced SRAM macros

are provided, such as one-transistor (IT) and four-transistor (4T) cell designs.

In general, an ASIC with embedded memory will provide better system

performance and a smaller part count as compared to a design that uses

external memory.

An example of early embedded DRAM development is Toshiba's

dRAMASIC process, based on two approaches, one of which utilizes onetransistor, one-capacitor (1T1C) architecture for providing high-density embedded DRAMs, and the other based on three-transistor cell that provides

capability for implementation of low-density embedded DRAMs. Compiled

DRAM macros of various densities, speeds, databus widths, dual-port configurations, and other features implemented in a merged DRAM/logic process

are available from various companies. The latest developments include a

1-GHz eDRAM macro cell to serve large-capacity, on-chip L2 cache memory

for gigahertz-level SOC designs.

The embedding of DRAMs in a logic technology requires some additional

steps to the standard logic process flow. Two examples of merged logic

processor-DRAM architectures are discussed in detail: (1) Mitsubishi MR32/

D, a 32-bit RISC processor with DSP functions that uses 2 MB of DRAM plus

4 KB of cache SRAM on the same die and (2) a multimedia-oriented RISC

processor that has a high-data-rate system and uses a concurrent RDRAM

controller in a superscalar architecture.

The alternative approach of DRAM technology with embedded logic

architecture is mainly utilized by companies such as Mitsubishi, Samsung,

Toshiba, and Infineon Technologies, which have DRAM manufacturing heritage and add some masking steps to include logic in their DRAM processes.

Multimedia accelerators that require high data transfer rates between the frame

buffers and the data processing units utilize embedded DRAM-logic approach.

An example of Oki Electric Company's multimedia accelerator, which integrates the MPEG-1 video/audio decoder, the 2-D graphic user interface (GUI)

engine, and a R AMD AC (135-MHz, true color digital/analog converter), is

provided.

16

INTRODUCTION TO ADVANCED SEMICONDUCTOR MEMORIES

The University of California, Berkeley, approach for intelligent RAM

(IRAM) supports designing the processor in a memory process, which has

several advantages as well as disadvantages that are discussed. Another

approach that has been proposed to implement processor-in-memory architecture is computational RAM (C-RAM) with a goal to make an effective use of

internal memory bandwidth by pitch-matching simple process elements to

memory columns. O R A M can function either as a conventional memory chip

or as a single-instruction stream, multiple-instruction data stream (SIMD)

computer.

The most popular examples of embedded flash memory devices are PLDs,

FPGAs, DSPs, and microcontrollers. The embedded system designers prefer to

use flash-based processors, which can be quickly programmed before transferring their code to a more cost-effective ROM-based chip for high volume

production. The use of embedded flash and EEPROM technologies in microcontrollers available from various suppliers is discussed.

There is a growing need worldwide for small, inexpensive, rugged, and easily

transportable forms of nonvolatile data storage. Flash card technology meets

those requirements, and the use of flash cards is expected to grow exponentially

over the next decade. Various flash card technologies are reviewed, such as the

Advanced Technology Attachment (ATA), CompactFlash Cards, MultiMedia Cards, and single-chip flash disk.

1.3. FUTURE MEMORY DIRECTIONS

Chapter 7 discusses mostly volatile and nonvolatile memory technologies that

are in research and development, along with their future directions and potential

for gigabit-to-terabit scaling. An example is magnetoresistive RAMs (MRAMs)

that are nonvolatile magnetic storage devices based on the principle that a

material's magnetoresistance will change due to the presence of magnetic field.

The MRAM technology has some attractive features such as the nondestructive

readout (NDRO), high radiation tolerance, higher write/erase endurance

compared to the FRAMs, and virtually unlimited power-off capabilities. Earlier

MRAMs were based on the anisotropic magnetoresistance (AMR) effect, which

has allowed realization of smaller elements with larger M-R effect and, therefore,

a higher output signal. Some companies such as Honeywell, Nonvolatile

Electronics, Inc. (NVE), have demonstrated working MRAM chips ranging from

64-Kb to 256-Kb densities. Many other companies such as Motorola, IBM,

Infineon Technologies, Toshiba, and so on, are also actively developing MRAMs.

The resonant tunneling diode (RTD) consists of an emitter region and

collector region, and a double tunnel barrier structure, which contains a

quantum well. Both tunnel diodes and RTDs exploit negative differential

FUTURE MEMORY DIRECTIONS

17

resistance (NDR) characteristics of quantum-mechanical resonant tunneling

currents. RTDs are of interest for use in multistate and compact memory, as

well as in tunneling-based SRAM (TSRAM) cell designs and applications. A

fully decoded 1-Kbit TSRAM prototype with DRAM-type high-speed signalto-noise ratio sensing circuitry has been designed. An RTD-based sense

amplifier circuit called a quantum MOS (QMOS) has been proposed that

shows a good noise immunity and 20% faster sensing time as compared to the

conventional CMOS design sense amplifier. RTDs based on IIIV compound

materials can achieve high peak current densities and appear to be the most

likely candidates for advanced TSRAM designs and applications.

In single-electron devices, the operating principle relies on the Coulomb

repulsive force between electrons. These devices are expected to operate even

at very small physical dimensions (atomic scale), making ultra-large-scale

integration possible. Another potential advantage is ultra-low-power operation, because the device uses a very small number of electrons to perform

basic operation. The majority of research in single-electron devices has been

done at very low temperature, because room temperature operation requires

very large Coulomb energy, accomplished only with sub-10-nm structures,

which imposes lithographic limitations.

Single-electron phenomena have also been observed at room temperature,

and demonstration has included the concept of the floating-dot memory cell,

in which nano-Si particles can replace the floating gate of the memory device.

However, many major challenges need to be overcome before the commercial

production of single-electron memory becomes feasible. Various single-electron

memory configurations are under development, such as the SET flip-flop,

electron-trap memory, SET ring memory, random background charge-independent memory, and single/multiple island memories.

In a nanocrystal memory, the charge storage in a distributed floating gate

offers several attractive characteristics such as the faster write times, operation

at lower power than those for the EEPROMs, and better endurance characteristics than that for the flash EEPROMs. A 128-Mb single-electron memory

prototype chip has been developed by Hitachi Central Laboratory, Japan,

using the Coulomb blockade effect based on the electron repulsion within an

ultrathin layer of polycrystalline material.

The phase change memory technology stores information using structural

phase changes in certain thin film alloys that typically utilize one or more

elements from column VI of the periodic table (e.g., germanium and antimonium). These phase change alloys are referred to as the chalcogenide

materials. The phase change technology uses a thermally activated, rapid,

reversible change in the structure of an alloy to store the data. Semiconductor

memory elements using chalcogenide materials have been fabricated as technology demonstrators. Air Force Research Laboratories (AFRL) is funding

18

INTRODUCTION TO ADVANCED SEMICONDUCTOR MEMORIES

development for a 64-Kb memory cell array as a characterization test chip,

with plans for future migration to higher densities.

A new area of research is protonic nonvolatile memories that are based on

the observation that hydrogen ions (protons) can be used as the primary

carriers of information in a silicon-silicon oxide-silicon (Si-SiO 2 -Si) device,

creating a memory function. Several patents have been granted based on this

memory function concept.

Chapter 7, Section 7.7 provides a few examples of the following new memory

technology developments:

A proposed novel thyristor-based SRAM cell, called T-RAM, which has

a cell area less than one-tenth the area of a conventional SRAM cell. It

can provide DRAM densities, while the potential for speed is comparable

to current generation of SRAMs.

An integrated content addressable read-only memory (CAROM) data

storage system that uses data compression algorithm, which promises

CD-ROM density, in an arbitrarily shaped data package without moving

parts. A company, Autosophy, Inc., is planning to etch these arrays on foil,

similar to active LCD production, which could result in foldable devices

with hundreds of megabyte capacity that can fit in PC cards or other

small cartridges.

Work (by IBM Research Group in Zurich, Switzerland) on development

of a prototype called Millipede, which can store an amazing amount of

data (e.g., 500 Gb/in.2) as microscopic indentations on a flat polymer

surface. This technology is similar to the operation of a phonographic

stylus and is derived from the atomic force microscopy.

Holographic data storage that is considered a promising technology for

achieving random access volumetric storage, offering orders of magnitude

greater density than the surface storage. A unique advantage of holographic memories from the space applications perspective is their inherent

radiation hardness. A holographic random access memory (HRAM)

design has been proposed that can lead to the implementation of compact

and inexpensive modules that can be used to construct large read-write

memories. The greatest challenge for HRAM development is to improve

its slow recording rate by several orders of magnitude.

REFERENCES

1. Ashok K. Sharma, Semiconductor Memories: Technology, Testing and Reliability,

IEEE Press, New York, 1997.

2. B. McClean, B. Matas, and T. Yancey, The McClean Report: 2001 Edition, IC

Insights, 2001.

Você também pode gostar

- Fusion: Combining Distinct Entities into a New WholeDocumento3 páginasFusion: Combining Distinct Entities into a New WholeGowtham SpAinda não há avaliações

- Spanish Language Influences On Written English: Betty Rizzo and Santiago VillafaneDocumento10 páginasSpanish Language Influences On Written English: Betty Rizzo and Santiago VillafaneGowtham SpAinda não há avaliações

- Relative Atomic Mass - WikipediaDocumento2 páginasRelative Atomic Mass - WikipediaGowtham SpAinda não há avaliações

- Very Large Scale IntegrationDocumento3 páginasVery Large Scale IntegrationGowtham SpAinda não há avaliações

- Writing For The Web GuideDocumento16 páginasWriting For The Web GuideJuliusNeilPialaAinda não há avaliações

- Semiconductor fundamentals and applications explainedDocumento2 páginasSemiconductor fundamentals and applications explainedGowtham SpAinda não há avaliações

- 200 Prep Questions: Downloads/200 - PMP - Sample - Questions PDFDocumento1 página200 Prep Questions: Downloads/200 - PMP - Sample - Questions PDFGowtham SpAinda não há avaliações

- Scientific Writing in APA StyleDocumento38 páginasScientific Writing in APA StyleelentscheAinda não há avaliações

- Ultimate Guide On BloggingDocumento37 páginasUltimate Guide On BloggingHau IuliaAinda não há avaliações

- Programming TipsDocumento2 páginasProgramming TipsGowtham SpAinda não há avaliações

- Standard Atomic Weight - WikipediaDocumento2 páginasStandard Atomic Weight - WikipediaGowtham SpAinda não há avaliações

- Chemical Element - WikipediaDocumento2 páginasChemical Element - WikipediaGowtham SpAinda não há avaliações

- Diode - WikipediaDocumento3 páginasDiode - WikipediaGowtham SpAinda não há avaliações

- Capacitor - WikipediaDocumento2 páginasCapacitor - WikipediaGowtham SpAinda não há avaliações

- Lambda-CDM Model - WikipediaDocumento2 páginasLambda-CDM Model - WikipediaGowtham SpAinda não há avaliações

- Big Bang - WikipediaDocumento2 páginasBig Bang - WikipediaGowtham SpAinda não há avaliações

- Planck Time - WikipediaDocumento2 páginasPlanck Time - WikipediaGowtham SpAinda não há avaliações

- Hubble Space Telescope - WikipediaDocumento3 páginasHubble Space Telescope - WikipediaGowtham SpAinda não há avaliações

- Speed of Light - WikipediaDocumento3 páginasSpeed of Light - WikipediaGowtham SpAinda não há avaliações

- SunDocumento3 páginasSunGowtham SpAinda não há avaliações

- Publication Nemani Gowtham PDFDocumento6 páginasPublication Nemani Gowtham PDFGowtham SpAinda não há avaliações

- UranusDocumento4 páginasUranusGowtham SpAinda não há avaliações

- BaggerDocumento2 páginasBaggerGowtham SpAinda não há avaliações

- Pluto - WikipediaDocumento4 páginasPluto - WikipediaGowtham SpAinda não há avaliações

- CurrencyDocumento3 páginasCurrencyGowtham SpAinda não há avaliações

- Comparative Study On Low-Power High-Performance Standard-Cell Flip-FlopsDocumento9 páginasComparative Study On Low-Power High-Performance Standard-Cell Flip-FlopsGowtham SpAinda não há avaliações

- Universe - WikipediaDocumento4 páginasUniverse - WikipediaGowtham SpAinda não há avaliações

- BaggerDocumento2 páginasBaggerGowtham SpAinda não há avaliações

- Reserach Proposal-Radioisotope Thermoelectric Generator Application For LocomotivesDocumento4 páginasReserach Proposal-Radioisotope Thermoelectric Generator Application For LocomotivesGowtham SpAinda não há avaliações

- Recent Trends in Low Power VLSI DesignDocumento15 páginasRecent Trends in Low Power VLSI DesignGowtham SpAinda não há avaliações

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (119)

- Writing Emails Part 1 Informal British English Teacher Ver2Documento7 páginasWriting Emails Part 1 Informal British English Teacher Ver2Madalina MandiucAinda não há avaliações

- Tiger AnddragonDocumento61 páginasTiger AnddragonAdil SiddiquiAinda não há avaliações

- DVOR Principle 코이카 양식Documento71 páginasDVOR Principle 코이카 양식Undral Batbayar100% (1)

- Hardware Devices Used in Virtual Reality TechnologiesDocumento6 páginasHardware Devices Used in Virtual Reality TechnologiesTheMoon LightAinda não há avaliações

- Evolution of Computers: A Brief HistoryDocumento15 páginasEvolution of Computers: A Brief HistoryshinAinda não há avaliações

- Automation & Control Esst en 200804Documento356 páginasAutomation & Control Esst en 200804Sveinn Rúnar JúlíussonAinda não há avaliações

- PC 5400 PC 5500Documento53 páginasPC 5400 PC 5500ArturHeiseAinda não há avaliações

- Optimization Module For Abaqus/CAE Based On Genetic AlgorithmDocumento1 páginaOptimization Module For Abaqus/CAE Based On Genetic AlgorithmSIMULIACorpAinda não há avaliações

- Smarter Washing Solutions: Modular Wash RangeDocumento5 páginasSmarter Washing Solutions: Modular Wash RangeSujesh AnAinda não há avaliações

- Mobile Phone: Service ManualDocumento129 páginasMobile Phone: Service ManualAlexAinda não há avaliações

- Motorship Oct 2023Documento56 páginasMotorship Oct 2023Sahil PakhaliAinda não há avaliações

- Introducing The Phenomenon To Be Discussed: Stating Your OpinionDocumento8 páginasIntroducing The Phenomenon To Be Discussed: Stating Your OpinionRam RaghuwanshiAinda não há avaliações

- Designing of 3 Phase Induction Motor Blackbook DoneDocumento30 páginasDesigning of 3 Phase Induction Motor Blackbook Donetryd0% (1)

- Vehicle Tracker Offer SheetDocumento1 páginaVehicle Tracker Offer SheetBihun PandaAinda não há avaliações

- An Introduction to Heisenberg Groups in Analysis and GeometryDocumento7 páginasAn Introduction to Heisenberg Groups in Analysis and Geometrynitrosc16703Ainda não há avaliações

- Food Conformity BA 550-13Documento9 páginasFood Conformity BA 550-13puipuiesperaAinda não há avaliações

- Topic 3Documento28 páginasTopic 3Ashraf YusofAinda não há avaliações

- GulliverDocumento8 páginasGulliverCris LuAinda não há avaliações

- Bicycle Repair ManualDocumento162 páginasBicycle Repair Manualrazvancc89% (9)

- 1729Documento52 páginas1729praj24083302Ainda não há avaliações

- T38N/T48N: Suffix Code Instruction ManualDocumento1 páginaT38N/T48N: Suffix Code Instruction ManualaliAinda não há avaliações

- Marketing Assignment (Cool Air India)Documento10 páginasMarketing Assignment (Cool Air India)Mandira PantAinda não há avaliações

- Sample of Application Letter (Updated)Documento4 páginasSample of Application Letter (Updated)Mizpah Sarah BautistaAinda não há avaliações

- Hemispherical Head Design ToolDocumento1 páginaHemispherical Head Design Toolnaveen_86Ainda não há avaliações

- 07-02-2023 MS QLNDocumento3 páginas07-02-2023 MS QLNSummaaaaAinda não há avaliações

- Trends in Structural Systems and Innovations for High-Rise Buildings over the Last DecadeDocumento53 páginasTrends in Structural Systems and Innovations for High-Rise Buildings over the Last DecadeNarasimhaReddy PangaAinda não há avaliações

- Clinical TeachingDocumento29 páginasClinical TeachingJeonoh Florida100% (2)

- CH - 1Documento4 páginasCH - 1Phantom GamingAinda não há avaliações

- Analisis Efektivitas Inklusi Keuangan Di BMT Syariah Riyal: PendahuluanDocumento25 páginasAnalisis Efektivitas Inklusi Keuangan Di BMT Syariah Riyal: PendahuluanEma Rina SafitriAinda não há avaliações

- Katja Kruckeberg, Wolfgang Amann, Mike Green-Leadership and Personal Development - A Toolbox For The 21st Century Professional-Information Age Publishing (2011)Documento383 páginasKatja Kruckeberg, Wolfgang Amann, Mike Green-Leadership and Personal Development - A Toolbox For The 21st Century Professional-Information Age Publishing (2011)MariaIoanaTelecan100% (1)