Escolar Documentos

Profissional Documentos

Cultura Documentos

Design and FPGA Implementation of Channelizer & Frequency Hopping For Advanced SATCOM System

Enviado por

Editor IJRITCCTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Design and FPGA Implementation of Channelizer & Frequency Hopping For Advanced SATCOM System

Enviado por

Editor IJRITCCDireitos autorais:

Formatos disponíveis

International Journal on Recent and Innovation Trends in Computing and Communication

ISSN 2321 8169

16

Volume: 1 Issue: 1

___________________________________________________________________________

Design and FPGA Implementation of Channelizer & Frequency Hopping for

Advanced SATCOM System

Mahesh Kumar, Durga Digdarsini, T.V.S. Ram

Space Applications Centre (SAC), Indian Space Research Organization (ISRO)

Ahmedabad, Gujarat, India

maheshk@sac.isro.gov.in, digdarsini@sac.isro.gov.in, tvsram@sac.isro.gov.in

Abstract Advanced satellite communication systems should be capable of preventing unauthorized access or exploitation of

communication services by adversaries. This can be achieved by use of wideband multi-channel digital transceivers which employ

channelizer to extract the channel of interest from digitized RF bands for further baseband processing. Various anti-jamming

techniques like Frequency hopping are used to prevent the systems from intentional jamming by the hostile systems. This paper

presents an efficient channelizer architecture which supports wideband as well as narrowband channels with programmable

channel bandwidth followed by frequency hopping for the proposed SATCOM system. The target design is a flexible

channelization unit which divides the incoming data links of 11 MHz bandwidth into two data links in granularity of 0.5 MHz

depending upon user requirements. First link is further sub-channelized into two sub-links each having a bandwidth of 25 KHz

that is frequency hopped at a user programmable rate with desired random sequence. The same channelizer can be well applicable

in any software defined radio receiver platforms due to flexibility of the design. Proposed design is tested on target hardware Xilinx

Virtex-IV FPGA xc4vsx35-10ff668. The design and implementation of the channelizer and frequency hopping technique are

discussed in detail.

Keywords-channelizer, frequency hopping, ddc, cic, fpga.

_____________________________________________________*****______________________________________________________

I. INTRODUCTION

Satellite based communication system serves well for

providing personal communication globally. These systems

are prone to intentional jamming by the unauthorized

systems. Hence, advanced satellite communication systems,

which incorporate various anti-jamming techniques like

frequency hopping to combat jamming, are required for

applications requiring a robust communication free from any

interception of communication signals by the jammer. These

systems incorporate wideband multi-channel transceivers

capable of supporting multiple channels per RF band.

Typically a channelizer is used to extract the independent

communication channels from digitized RF bands. There are

mainly three predominant architectures available for

channelization, namely Poly-phase

FFT filter banks

(PFFB), Frequency Domain Filtering and Digital Down

Conversion (DDC) technique [1]. Although PFFB

channelization technique is efficient in terms of

computational complexity, it is limited to channel structures

consisting of equally spaced channels. In general, number of

channels must be equal to the decimation rate and sampling

rate must be power of two times the baseband bandwidth.

This technique is not well suited for transceivers supporting

flexible channel architectures. Frequency Domain Filtering

and Digital Down- Conversion (DDC) channelization

techniques offer similar capability in terms of flexibility for

any type of channel spacing and bandwidth but Frequency

domain filtering approach makes use of FFT which are

computation intensive. Also, mixing operation is performed

on the block of data vs. continuous time processing which

makes zero carrier offsets for individual block of data,

creating a rotating phase offset between each block if the

carrier cycle at the A/D sample rate is not an integer number

of block size. Hence, DDC based channelization technique is

employed for supporting flexible channel architectures for

the proposed system. This paper will explain the design and

FPGA implementation of a flexible channelization unit based

on DDC technique which supports both wideband as well as

narrowband channelization with programmable channel

bandwidth followed by frequency hopping which is the most

crucial elements in any advanced satellite communication

systems. The flexibility incorporated in the design makes it

also applicable for any wideband transceiver for software

defined radio platform.

The remainder of this paper is outlined as follows.

Section II discusses the system architecture and the

frequency plan of proposed SATCOM system. In Section III,

the design and implementation of the channelizer is

described. Section IV, illustrates the design and

implementation of frequency hopping technique. Section V

shows the hardware test setup with specifications used in the

design and analysis of results followed by Section VI which

concludes the paper.

1

IJRITCC | JAN 2013, Available @ http://www.ijritcc.org

___________________________________________________________________________

ISSN 2321 8169

International Journal on Recent and Innovation Trends in Computing and Communication

16

Volume: 1 Issue: 1

___________________________________________________________________________

II. PROPOSED SYSTEM ARCHITECTURE

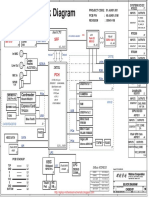

The basic block diagram for the proposed wideband

satellite communication system is presented in Figure 1. It

comprises RF Front-end (consists of antenna section for

transmission & reception of RF signals, RF to IF downconverter for converting RF down to Intermediate

Frequencies) and the digital subsystem for further digital

signal processing.

In this paper, receiver side of onboard system is

emphasized to show the capabilities of flexible channelizer

which extracts the channel of interest from digitized RF

bands for further baseband processing in FPGA. This process

is reversed on the transmit side where individual channels

are combined and retransmitted. A single channelization unit

supports multiple channels which can be wideband or

narrowband channels. The channelized narrowband signals

are frequency hopped at user programmable rate depending

upon the system specifications.

FH outputs to

transmit section

RF signal

In

RF to IF

converters

ADC

FPGA Based

Digital

Subsystem

(Channelization

&

Frequency

Hopping)

Figure 1: Basic block diagram of proposed SATCOM System

Amplitude

in db

The flexible frequency plan for the proposed SATCOM

system is presented in Figure 2 for hardware proof of

concept (POC). Incoming data links occupies a total of 11

MHz bandwidth which is divided into two wideband

channels in granules of 0.5 MHz depending upon the user

requirements. These wideband channels are further subchannelized into two narrowband channels in granules of 25

KHz which can reside anywhere inside a wideband channel.

Implementation of individual blocks of channelizer

architecture in FPGA with the specifications as described in

Table I is discussed in the next section.

11 MHz

1 MHz

Wideband

channels

1 MHz

Narrowband

channels

5 5.125 5.250

15 15.125 15.250

Frequency in MHz

Figure 2: Frequency plan

TABLE I.

SPECIFICATIONS OF TEST INPUTS

Parameter

No. of Wideband Channels

Specifications

2

No. of Narrowband Channels

Wideband Channel Center Frequencies

(CH1,CH2)

Narrowband Channel Center Frequencies

(subCH1,subCH2)

5 MHz,

15 MHz

5.125 MHz,

5.250 MHz

Wideband Channel BWs

1 MHz

Narrowband Channel BWs

25 KHz

Signal Power

-5 dBm

III.

DESIGN OF CHANNELIZER USING DDC

The proposed channelizer architecture is based on the

Digital Down Conversion (DDC) technique which is an

integral part of any digital communication receiver. In this

technique, the incoming digitized RF wideband signal is

shifted from its carrier frequency down to baseband through

mixing with a synthesized carrier at or near the carrier

frequency of that signal. The resulting signal is then filtered

and decimated to extract the channel of interest [2]. This

technique reduces the amount of effort to a great extent for

subsequent processing of the signal without loss of any

information. Figure 3 illustrates the basic block diagram of a

typical DDC.

RF

Wideband

ADC

Complex

multiplier

Low pass

Filter

Decimator

Baseband

Complex

Oscillator

Channelizer block

Figure 3: Basic DDC Architecture

The advantage of using DDC approach is the flexibility

in choosing the carrier frequency and channel bandwidth.

The Cascaded Integrator Comb (CIC) filter is used

instead of low pass FIR filter and decimator is proposed in

channelizer architecture for extracting wideband channels as

well as narrowband channels. CIC Filter inherently provides

decimation in addition to low pass filtering so that the

processing requirements for subsequent stages are relaxed.

The filter bandwidth can be programmed to the user

requirements by only changing the decimation factor. Postfiltering is done to compensate for the pass band droop. The

advantage of CIC filter is that it supports multiplier less filter

2

IJRITCC | JAN 2013, Available @ http://www.ijritcc.org

___________________________________________________________________________

ISSN 2321 8169

International Journal on Recent and Innovation Trends in Computing and Communication

16

Volume: 1 Issue: 1

___________________________________________________________________________

architecture which reduces the hardware complexity in any

FPGA based design.

Figure 4 shows the wideband and narrowband

channelizer architecture utilizing DDC technique [2]. First,

the wideband signal is filtered and decimated down to the

desired channel bandwidth through wideband channelizer.

The decimated signal is then passed to narrowband

channelizer to extract the narrowband channel of interest.

Although, both channelizers have similar architecture but

narrowband channelizer works at a low processing rate than

that of wideband channelizer.

Mixer

A/D

Cascaded

Integrator

Cascaded

Comb

PFIR

digitized multiplexed input data. The sine signal is used to

generate the in Phase component while the cosine generates

the quadrature component of the complex signal. The DDS

has to be clocked at the sample frequency so that sine and

cosine data are presented to the mixers at the same rate as

that of input data. Figure 5 illustrates a typical DDS

architecture. Quarter Wave Symmetry is utilized to reduce

the size of Sine/Cosine lookup table for FPGA

implementation to minimize no. of block memories. Phase

dithering is employed to get better frequency response. Table

III summarizes the DDS specifications for the frequency

plan mentioned in Figure 2.

Phase

Accumulator

Wideband

I

Multiplexed

Input

Phase

Increment

Mixer

DDS

Cascaded

Integrator

Mixer

Cascaded

Comb

Wideband Channelizer

Frequency

Tuning Word

Wideband

I

Wideband

Q

PFIR

Cascaded

Integrator

Cascaded

Comb

Narrowband

I

PFIR

R

e

g

R

e

g

clk

clk

Mixer

DDS

Frequency

Tuning Word

Cascaded

Integrator

Cascaded

Comb

PFIR

Narrowband

Q

Figure 4: Wideband and Narrowband Channelizer Architecture using DDC

Technique

Implementation of Mixer

The Mixer multiplies the multiplexed input data samples

with the synthesized carriers at or near the carrier frequency

of the channel of interest to bring the desired channel to the

baseband level. The output of the mixer contains both the

sum and difference frequency components at incoming

sample frequency. The mixer used in this design is desired to

run at the sample frequency of ADC for hardware proof of

concept. The following Table II summarizes the mixer

specifications.

TABLE II.

MIXER SPECIFICATIONS

Parameter

Input Data Bits

Carrier Bits

Sample Frequency of ADC

Center Frequency of CH1

Center Frequency of CH2

Center Frequency of subCH1

Center Frequency of subCH2

Specifications

14 bits

10 bits

125 MHz

5 MHz

15 MHz

125 KHz

250 KHz

Dither

Phase

Offset Sequence

DDS SPECIFICATIONS

Parameter

Sample Frequency

Phase Increment Word length

Output Bit Width

Carrier Frequency for CH1

Carrier Frequency for CH2

Carrier Frequency for subCH1

Carrier Frequency for subCH2

Narrowband Channelizer

A.

Sine/

Cosine

Lookup

Table

Figure 5: Architecture of DDS in FPGA

TABLE III.

Wideband

Q

Q

u

a

n

t

i

z

e

r

Specifications

125 MHz

32 bits

10 bits

5 MHz

15 MHz

125 KHz

250 KHz

C.

Implementation of CIC and Post FIR filter

In DDC architectures, two major functions namely low

pass filtering and decimation are necessary for further signal

processing. Low pass filtering is required immediately after

Mixer to remove the unwanted signal frequencies that would

arise due to mixing function and the decimation is essential

for reducing the incoming sample rate to the minimum

required to relax the signal processing requirements for

subsequent stages.

CIC filter is an efficient way of performing decimation

along with filtering. Figure 6 shows the CIC filter structure

consisting of N cascaded integrator stages clocked at sample

frequency fs, followed by a rate change by a factor R,

followed by N cascaded comb stages running at (fs/R) where

N is the number of stages or the filter order [3][4]. CIC

filters are hardware efficient filter structures as they use only

shifters and adders to perform the filtering function as shown

in Figure 6.

B.

Implementation of Direct Digital Synthesizer

The Direct Digital Synthesizer (DDS) is designed to

generate the sine and cosine carriers required to mix with the

3

IJRITCC | JAN 2013, Available @ http://www.ijritcc.org

___________________________________________________________________________

ISSN 2321 8169

International Journal on Recent and Innovation Trends in Computing and Communication

16

Volume: 1 Issue: 1

R

e

g

R

e

g

R

e

g

Decimate by R

___________________________________________________________________________

R

e

g

R

e

g

R

e

g

is known to the transmitter and receiver. A pseudo-random

code generator is used as a driver for a frequency synthesizer

(DDS) at the transmitter to pseudo-randomly hop the carrier

frequency of the narrowband signal extracted through the

narrowband channelizer unit as shown in Figure 7.

The present filter has a frequency response given by

H(f) = [sin(fR)/sin(f)]

----- (eq.1)

Where f is the normalized frequency relative to the input

sample rate and R is decimation rate.

The filter passband bandwidth is controlled by the

decimation factor R which can be user programmed to

provide the flexible bandwidth. The filter parameters for the

frequency plan mentioned in Figure 2 are described in Table

IV.

TABLE IV.

CIC FILTER SPECIFICATIONS

Parameter

Input Sample Frequency

No. of Stages (N)

Differential Delay (M)

Rounding

Specifications

125 MHz

3

1

Convergent

Post finite impulse response (PFIR) filter is required after

the CIC filter stage to compensate for the passband droop. It

can be single rate or multi-rate filter structures. The filter

length for each filter ranges from 0 to 1024 taps. The

coefficient precision may also be customized and ranges

from 1 to 32 bits. The full-precision results are not passed

between adjacent processing stages, bias-free convergent

rounding is employed for this process.

As per the frequency plan in Figure 2, the wideband

channel present at 5 MHz and 15 MHz are extracted through

wideband channelizer and the narrowband channelizer filters

out the narrowband channels present at 5.125MHz and 5.250

MHz each having 25 KHz bandwidth. The narrowband

channels are then frequency hopped to user programmable

rate.

IV.

DESIGN OF FREQUENCY HOP UNIT

Advanced satellite communication system demands

prevention from any jamming scenario. The hostile systems

try to intercept the transmitted signal and disrupt the

communication channel. Frequency hopping (FH) technique

is an efficient anti-jamming technique employed in

SATCOM systems as it is relatively easy to operate over

large spectral bands [7].

Frequency Hopping indicates that transmitter and

receiver change frequency rapidly in a defined pattern which

Frequency

hopped signal

Frequency synthesizer

Figure 6: CIC Decimator Filter Architecture

Code

Clock

Random sequence

generator

Narrowband

signal

Figure 7: Frequency Hop Unit

The hopping code selection is very critical in any

communication systems. It should have a large period, large

seed and random appearance to provide design secrecy. It

should possess large linear complexity so that jammer

intervention is negligible. The minimum hopping rate is

decided based upon the jammer location w.r.t. transmitter

and receiver [5].

In this design, slow frequency hopping method is used

where hop period is long with respect to a data bit period.

Each narrowband channelizer output is frequency hopped as

per the specifications mentioned in Table V.

TABLE V.

SPECIFICATIONS FOR FREQUENCY HOP

Parameter

Hop Rate

Input Channel Bandwidth

Total Output Bandwidth

No of Channels

Hopping Sequence

V.

Specifications

500 Hops/s

25kHz

1000 kHz

2

Programmable

RESULTS AND DISCUSSIONS

A Simulink model is developed for proof of concept of

the proposed channelizer architecture with specifications

mentioned in Table I. It consists of wideband transmitters

generating two channels of 1MHz modulation bandwidth at

5MHz and 15MHz IFs. The combined channel output

spectrum fed to the two channel receiver containing the

proposed channelizer which extracts individual channels

from the combined spectrum resulting in zero BER as shown

in Figure8. Similar model is designed and tested for

narrowband channelizer. Various design parameters are

simulated using Simulink model so that hardware

implementation becomes easier.

4

IJRITCC | JAN 2013, Available @ http://www.ijritcc.org

___________________________________________________________________________

ISSN 2321 8169

International Journal on Recent and Innovation Trends in Computing and Communication

16

Volume: 1 Issue: 1

___________________________________________________________________________

channelizers followed by FH unit. Both channelizers include

synthesized carrier from DDS, Mixer output, CIC filter

output followed by channelized output at baseband. FH unit

includes frequency tuning word generated from PRBS

generator and frequency hopped Narrowband signal output.

The hardware test setup is shown in Figure 11 which

involves VSG for input signal generation and target FPGA

board for processing of the signals. The channelizer and FH

outputs from FPGA are passed through DAC of the board

and results are observed using spectrum analyzer.

Figure 8: Channelizer Design in Simulink

The entire design is implemented using Verilog HDL

2001 without the use of any FPGA IP core so that the design

becomes platform independent and portable to any FPGA

like Xilinx or Actel. However, FPGA implementation is

done using XilinxISE9.2i and functional simulation is

carried out in Questa Sim 10.0b targeting Xilinx Virtex-4

FPGA xc4vsx35-10ff668 for hardware POC.

Figure 11 Hardware Test Setup

Figure 9: Functional Simulation Results for Wideband Channelizer

Figure 12 shows the multi-channel wideband spectrum

containing two 1MHz bandwidth signals input to the

channelizer which extracts the individual wideband channels.

For better visualization and comparison, the extracted

channel is frequency translated to the same center frequency

as shown in Figure 13. The channelizer design is tested by

varying input channel bandwidth to validate the flexibility of

channel bandwidth. Figure 14 shows the channelizer output

w.r.t. changing input channel bandwidth to 2 MHz.

Narrowband signal is also generated from VSG as per the

specifications mentioned in Table I and passed to the same

channelizer which extracts the narrowband channel of 25

KHz bandwidth as shown in Figure 15.

Ref

-5

dBm

Att

30

dB

* RBW

30

* VBW

100

SWT

10

kHz

Marker

[T1]

Hz

s

-24.02

dBm

15.000000000

MHz

Marker

[T1]

-10

AP

-20

dBm

5.000000000

MHz

CLRWR

-25.07

-30

-40

PRN

-50

Figure 10: Functional Simulation Results for Narrowband Channelizer and

FH

-60

-70

The Multichannel modulated signal as per frequency plan

in Figure 2 generated from Vector Signal Generator (VSG) is

passed through ADC of the FPGA based development board

and the output is captured in Logic Analyzer. This data is

stored in ROM of FPGA which is used as an input for

simulation of the entire design. Results from Questa Sim are

presented in Figure 9 and Figure 10 which show output

signals from various stages of wideband and narrowband

-80

-90

-100

Center

Date:

10

MHz

1.JAN.2000

1.5

MHz/

Span

15

MHz

00:22:38

Figure 12: Multichannel Signal from VSG

5

IJRITCC | JAN 2013, Available @ http://www.ijritcc.org

___________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

ISSN 2321 8169

16

Volume: 1 Issue: 1

___________________________________________________________________________

Ref

-40

dBm

Att

10

dB

* RBW

30

* VBW

300

SWT

kHz

1.15

Marker

[T1]

Hz

-70.92

dBm

5.000000000

MHz

-40

A

-50

1

AP

CLRWR

-60

-70

-80

PRN

-90

-100

-110

-120

-130

A hardware efficient architecture of DDC based

channelizer with frequency hopping applicable to advanced

satellite communication system is presented in this paper.

Channelization helps in extracting narrowband signal

embedded in wideband signal in presence of interferer where

Frequency hopping provides anti jamming margin for

SATCOM systems. The same flexible channelizer

architecture can also be applied to software defined radio

platform. Proposed hardware architecture occupies only 13%

area of total slices on target hardware Xilinx Virtex-IV

FPGA xc4vsx35-10ff668. The design is made platform

independent and can be ported on any target FPGA.

-140

Center

Date:

MHz

500

1.JAN.2000

kHz/

Span

MHz

03:48:56

Figure13: Extracted 1 MHz Wideband Channel

Ref

-40

dBm

Att

10

dB

* RBW

30

* VBW

300

SWT

kHz

Marker

[T1]

Hz

-75.54

dBm

5.000000000

MHz

1.15

ACKNOWLEDGMENT

The author would like to thank Saket Buch, Abhishek

Kakkar, and Sumitesh Sarkar for their invaluable

contribution for generation of specifications of the proposed

system.

-40

A

-50

1

AP

CLRWR

-60

-70

1

-80

PRN

-90

-100

-110

-120

-130

-140

Center

Date:

MHz

1.JAN.2000

500

kHz/

Span

MHz

03:50:24

Figure14: Extracted 2 MHz Wideband Channel

Ref -20 dBm

Att

10 dB

* RBW

3 kHz

* VBW

10 Hz

SWT 8.4 s

-20

Marker 1 [T1]

-40.49 dBm

237.250000000 kHz

Delta 2 [T1]

REFERENCES

[1] Lee Pucker Channelization Techniques for Software

Defined Radio, Spectrum Signal Processing Inc.

[2] Xilinx, Inc., Digital Down converter V1.0.

[3] Xilinx, Inc. Cascaded Integrator Comb Filter V3.0.

[4] Arnaud Santraine, S. Leprince, and Fred Taylor. Multiplier

Free Bandpass Channelizer for undersampled Applications,

IEEE Signal Processing Letters, Vol.11, No.11, Nov 2004.

[5] E. B. Felstead, "Follower Jammer Considerations for

Frequency Hopped Spread Spectrum," Communication

Research Center, Canadian Crown Copyright, 1998.

[6] J. Proakis and D. Manolakis, Digital Signal Processing

Principles, Algorithms, and Applications, Prentice Hall,

1996.

[7] B. SKLAR, Digital Communications, Fundamentals and

Applications, Prentice Hall, Second Edition.

[8] P.P. Vaidyanathan, Multirate Systems and Filter Banks,

Prentice-Hall, 1993.

0.24 dB

25.000000000 kHz

-30

1 AP

CLRWR

1

-40

-50

-60

PRN

-70

-80

-90

-100

-110

-120

Center 250 kHz

Date:

1.JAN.2000

12.5 kHz/

Span 125 kHz

02:21:25

Figure15: Extracted 25 KHz Narrowband Channel

VI.

CONCLUSION

6

IJRITCC | JAN 2013, Available @ http://www.ijritcc.org

___________________________________________________________________________

Você também pode gostar

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (120)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Operate A Personal Computer PDFDocumento56 páginasOperate A Personal Computer PDFEdgar G. Dela Rosa0% (1)

- Crack Your Angular Interview PDFDocumento67 páginasCrack Your Angular Interview PDFAmir Karacic100% (2)

- ExpertsDocumento6 páginasExpertsShamsuddin HasnaniAinda não há avaliações

- Advance Embedded System Design: Shibu K VDocumento73 páginasAdvance Embedded System Design: Shibu K VBhavya Reddy75% (4)

- Image Restoration Techniques Using Fusion To Remove Motion BlurDocumento5 páginasImage Restoration Techniques Using Fusion To Remove Motion Blurrahul sharmaAinda não há avaliações

- Performance Analysis of Image Restoration Techniques at Different NoisesDocumento4 páginasPerformance Analysis of Image Restoration Techniques at Different NoisesEditor IJRITCCAinda não há avaliações

- Regression Based Comparative Study For Continuous BP Measurement Using Pulse Transit TimeDocumento7 páginasRegression Based Comparative Study For Continuous BP Measurement Using Pulse Transit TimeEditor IJRITCCAinda não há avaliações

- A Review of 2D &3D Image Steganography TechniquesDocumento5 páginasA Review of 2D &3D Image Steganography TechniquesEditor IJRITCCAinda não há avaliações

- A Review of Wearable Antenna For Body Area Network ApplicationDocumento4 páginasA Review of Wearable Antenna For Body Area Network ApplicationEditor IJRITCCAinda não há avaliações

- IJRITCC Call For Papers (October 2016 Issue) Citation in Google Scholar Impact Factor 5.837 DOI (CrossRef USA) For Each Paper, IC Value 5.075Documento3 páginasIJRITCC Call For Papers (October 2016 Issue) Citation in Google Scholar Impact Factor 5.837 DOI (CrossRef USA) For Each Paper, IC Value 5.075Editor IJRITCCAinda não há avaliações

- Channel Estimation Techniques Over MIMO-OFDM SystemDocumento4 páginasChannel Estimation Techniques Over MIMO-OFDM SystemEditor IJRITCCAinda não há avaliações

- Modeling Heterogeneous Vehicle Routing Problem With Strict Time ScheduleDocumento4 páginasModeling Heterogeneous Vehicle Routing Problem With Strict Time ScheduleEditor IJRITCCAinda não há avaliações

- Channel Estimation Techniques Over MIMO-OFDM SystemDocumento4 páginasChannel Estimation Techniques Over MIMO-OFDM SystemEditor IJRITCCAinda não há avaliações

- Comparative Analysis of Hybrid Algorithms in Information HidingDocumento5 páginasComparative Analysis of Hybrid Algorithms in Information HidingEditor IJRITCCAinda não há avaliações

- A Review of Wearable Antenna For Body Area Network ApplicationDocumento4 páginasA Review of Wearable Antenna For Body Area Network ApplicationEditor IJRITCCAinda não há avaliações

- A Review of 2D &3D Image Steganography TechniquesDocumento5 páginasA Review of 2D &3D Image Steganography TechniquesEditor IJRITCCAinda não há avaliações

- Safeguarding Data Privacy by Placing Multi-Level Access RestrictionsDocumento3 páginasSafeguarding Data Privacy by Placing Multi-Level Access Restrictionsrahul sharmaAinda não há avaliações

- Importance of Similarity Measures in Effective Web Information RetrievalDocumento5 páginasImportance of Similarity Measures in Effective Web Information RetrievalEditor IJRITCCAinda não há avaliações

- Diagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmDocumento5 páginasDiagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmEditor IJRITCCAinda não há avaliações

- Itimer: Count On Your TimeDocumento4 páginasItimer: Count On Your Timerahul sharmaAinda não há avaliações

- Network Approach Based Hindi Numeral RecognitionDocumento4 páginasNetwork Approach Based Hindi Numeral RecognitionEditor IJRITCCAinda não há avaliações

- Fuzzy Logic A Soft Computing Approach For E-Learning: A Qualitative ReviewDocumento4 páginasFuzzy Logic A Soft Computing Approach For E-Learning: A Qualitative ReviewEditor IJRITCCAinda não há avaliações

- Predictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth KotianDocumento3 páginasPredictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth Kotianrahul sharmaAinda não há avaliações

- Prediction of Crop Yield Using LS-SVMDocumento3 páginasPrediction of Crop Yield Using LS-SVMEditor IJRITCCAinda não há avaliações

- A Study of Focused Web Crawling TechniquesDocumento4 páginasA Study of Focused Web Crawling TechniquesEditor IJRITCCAinda não há avaliações

- Hybrid Algorithm For Enhanced Watermark Security With Robust DetectionDocumento5 páginasHybrid Algorithm For Enhanced Watermark Security With Robust Detectionrahul sharmaAinda não há avaliações

- Vehicular Ad-Hoc Network, Its Security and Issues: A ReviewDocumento4 páginasVehicular Ad-Hoc Network, Its Security and Issues: A Reviewrahul sharmaAinda não há avaliações

- 44 1530697679 - 04-07-2018 PDFDocumento3 páginas44 1530697679 - 04-07-2018 PDFrahul sharmaAinda não há avaliações

- Efficient Techniques For Image CompressionDocumento4 páginasEfficient Techniques For Image CompressionEditor IJRITCCAinda não há avaliações

- 45 1530697786 - 04-07-2018 PDFDocumento5 páginas45 1530697786 - 04-07-2018 PDFrahul sharmaAinda não há avaliações

- A Clustering and Associativity Analysis Based Probabilistic Method For Web Page PredictionDocumento5 páginasA Clustering and Associativity Analysis Based Probabilistic Method For Web Page Predictionrahul sharmaAinda não há avaliações

- 41 1530347319 - 30-06-2018 PDFDocumento9 páginas41 1530347319 - 30-06-2018 PDFrahul sharmaAinda não há avaliações

- A Content Based Region Separation and Analysis Approach For Sar Image ClassificationDocumento7 páginasA Content Based Region Separation and Analysis Approach For Sar Image Classificationrahul sharmaAinda não há avaliações

- Space Complexity Analysis of Rsa and Ecc Based Security Algorithms in Cloud DataDocumento12 páginasSpace Complexity Analysis of Rsa and Ecc Based Security Algorithms in Cloud Datarahul sharmaAinda não há avaliações

- Privacy-Preserving and Truthful Detection of Packet Dropping Attacks in Wireless Ad Hoc NetworksDocumento6 páginasPrivacy-Preserving and Truthful Detection of Packet Dropping Attacks in Wireless Ad Hoc NetworksLeMeniz InfotechAinda não há avaliações

- VideoEditorBusiness - Fac K ING - Info.20230524 091030.3992Documento8 páginasVideoEditorBusiness - Fac K ING - Info.20230524 091030.3992scribibiAinda não há avaliações

- WAEC Online E - Registration ManualDocumento20 páginasWAEC Online E - Registration ManualHector Ngodo100% (1)

- Gujarat Technological University: CreditsDocumento4 páginasGujarat Technological University: CreditsNiket RathodAinda não há avaliações

- Scantron INSIGHT 30 Datasheet From AXIS IT BangladeshDocumento4 páginasScantron INSIGHT 30 Datasheet From AXIS IT BangladeshkmmhasanAinda não há avaliações

- TL-WN722N (EU&US) 3.0 Datasheet PDFDocumento4 páginasTL-WN722N (EU&US) 3.0 Datasheet PDFThe Kronos Place100% (1)

- MCSA AssaignmentDocumento4 páginasMCSA AssaignmentTinaAinda não há avaliações

- File Handling in CLDocumento12 páginasFile Handling in CLNaresh KuppiliAinda não há avaliações

- Tm1 Install InstructionsanuDocumento10 páginasTm1 Install InstructionsanuranusofiAinda não há avaliações

- Evolution of Microprocessor - Types and ApplicationsDocumento9 páginasEvolution of Microprocessor - Types and ApplicationsAnonymous U8awvgZ3pDAinda não há avaliações

- Lesson PlanDocumento3 páginasLesson PlanEtty MarlynAinda não há avaliações

- ARTICLE Access ControlDocumento2 páginasARTICLE Access ControlFatima Sarpina HinayAinda não há avaliações

- Classical Waterfall Model:: Mid Questions and Answers - 4sets PDF By: Venu GopalDocumento22 páginasClassical Waterfall Model:: Mid Questions and Answers - 4sets PDF By: Venu Gopalspider dogAinda não há avaliações

- CADIZ-CP Block Diagram: Intel CPUDocumento57 páginasCADIZ-CP Block Diagram: Intel CPUvnenovAinda não há avaliações

- A. Introduction To JavascriptDocumento5 páginasA. Introduction To JavascriptMikki BalateroAinda não há avaliações

- Windows 7 Tweak GuideDocumento0 páginaWindows 7 Tweak GuideDaymyenAinda não há avaliações

- Cloud Computing For Green Construction ManagementDocumento4 páginasCloud Computing For Green Construction ManagementOkino CharlesAinda não há avaliações

- 8051 Instruction SetDocumento23 páginas8051 Instruction SetPrinceDineshAinda não há avaliações

- Print Variable DataDocumento24 páginasPrint Variable DataAndrew TurnerAinda não há avaliações

- Library Management System Using QR Code A Project SynopsisDocumento13 páginasLibrary Management System Using QR Code A Project SynopsisSaqlain AjmrtyAinda não há avaliações

- MPI 2019 AssessmentDocumento10 páginasMPI 2019 AssessmentkumarklAinda não há avaliações

- Xpressfeed Loader Environment Checklist v5Documento9 páginasXpressfeed Loader Environment Checklist v5Anila KhwajaAinda não há avaliações

- A0010 DinstarDAGCommandManualvxworksv2.0 PDFDocumento26 páginasA0010 DinstarDAGCommandManualvxworksv2.0 PDFErik Joel Manrique AlvaAinda não há avaliações

- Registered Jack - Wikipedia, The Free EncyclopediaDocumento5 páginasRegistered Jack - Wikipedia, The Free EncyclopediaManitAinda não há avaliações

- E57 1 PDFDocumento27 páginasE57 1 PDFAzrin RahmanAinda não há avaliações

- Introduction To AVR TimersDocumento20 páginasIntroduction To AVR TimersTarun GuptaAinda não há avaliações