Escolar Documentos

Profissional Documentos

Cultura Documentos

La Arquitectura Von Neumann

Enviado por

Rampages FelinhoDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

La Arquitectura Von Neumann

Enviado por

Rampages FelinhoDireitos autorais:

Formatos disponíveis

La arquitectura Von Neumann, tambin conocida como modelo de Von Neumann o

arquitectura Princeton, es una arquitectura de computadoras basada en la descrita en

1945 por el matemtico y fsico John von Neumann y otros, en el primer borrador de

un informe sobre el EDVAC.[1] Este describe una arquitectura de diseo para un

computador digital electrnico con partes que constan de una unidad de procesamiento

que contiene una unidad aritmtico lgica y registros del procesador, una unidad de

control que contiene un registro de instrucciones y un contador de programa, una

memoria para almacenar tanto datos como instrucciones, almacenamiento masivo

externo, y mecanismos de entrada y salida.[1] [2] El significado ha evolucionado hasta ser

cualquier computador de programa almacenado en el cual no pueden ocurrir una

extraccin de instruccin y una operacin de datos al mismo tiempo, ya que comparten

un bus en comn. Esto se conoce como el cuello de botella Von Neumann y muchas

veces limita el rendimiento del sistema.[3]

El diseo de una arquitectura Von Neumann es ms simple que la arquitectura Harvard

ms moderna, que tambin es un sistema de programa almacenado, pero tiene un

conjunto dedicado de direcciones y buses de datos para leer datos desde memoria y

escribir datos en la misma, y otro conjunto de direcciones y buses de datos para ir a

buscar instrucciones.

Un computador digital de programa almacenado es una que mantiene sus instrucciones

de programa, as como sus datos, en memoria de acceso aleatorio (RAM) de lecturaescritura. Las computadoras de programa almacenado representaron un avance sobre los

ordenadores controlados por programas de la dcada de 1940, como la Colossus y la

ENIAC, que fueron programadas ajustando interruptores e insertando parches,

conduciendo datos de la ruta y para controlar las seales entre las distintas unidades

funcionales. En la gran mayora de las computadoras modernas, se utiliza la misma

memoria tanto para datos como para instrucciones de programa, y la distincin entre

Von Neumann vs. Harvard se aplica a la arquitectura de memoria cach, pero no a la

memoria principal.

Definicin formal

Las computadoras son mquinas de arquitectura von Neumann cuando:

1. Tanto los programas como los datos se almacenan en una memoria en comn.

Esto hace posible la ejecucin de comandos de la misma forma que los datos.

2. Cada celda de memoria de la mquina se identifica con un nmero nico,

llamado direccin.

3. Las diferentes partes de la informacin (los comandos y los datos) tienen

diferente modos de uso, pero la estructura no se representa en memoria de

manera codificada.

4. Cada programa se ejecuta de forma secuencial que, en el caso de que no haya

instrucciones especiales, comienza con la primera instruccin. Para cambiar esta

secuencia se utiliza el comando de control de transferencia.

Estructura clsica de las mquinas von

Neumann[editar]

Una mquina Von Neumann, al igual que prcticamente todos los computadores

modernos de uso general, consta de cuatro componentes principales:

1. Dispositivo de operacin (DO), que ejecuta instrucciones de un conjunto

especificado, llamado sistema (conjunto) de instrucciones, sobre porciones de

informacin almacenada, separada de la memoria del dispositivo operativo

(aunque en la arquitectura moderna el dispositivo operativo consume ms

memoria -generalmente del banco de registros-), en la que los operandos son

almacenados directamente en el proceso de clculo, en un tiempo relativamente

corto

2. Unidad de control (UC), que organiza la implementacin consistente de

algoritmos de decodificacin de instrucciones que provienen de la memoria del

dispositivo, responde a situaciones de emergencia y realiza funciones de

direccin general de todos los nodos de computacin. Por lo general, el DO y la

UC conforman una estructura llamada CPU. Cabe sealar que el requisito es

consistente, el orden de la memoria (el orden del cambio de direccin en el

contador de programa) es fundamental a la hora de la ejecucin de la

instruccin. Por lo general, la arquitectura que no se adhiere a este principio no

se considera von Neumann

3. Memoria del dispositivo un conjunto de celdas con identificadores nicos

(direcciones), que contienen instrucciones y datos.

4. Dispositivo de E/S (DES), que permite la comunicacin con el mundo exterior

de los computadores, son otros dispositivos que reciben los resultados y que le

transmiten la informacin al computador para su procesamiento.

Primeras computadoras basadas en arquitectura von

Neumann

La primera saga se basaba en un diseo que fue utilizado por muchas universidades y

empresas para construir sus computadoras.12 Entre estas, solo ILLIAC y ORDVAC

tenan un conjunto de instrucciones compatible.

Mquina Experimental de Pequea Escala de Mnchester (SSEM), apodada

"Baby" (Universidad de Manchester, Inglaterra) hizo su primera ejecucin

exitosa de un programa almacenado el 21 de junio de 1948.

EDSAC (Universidad de Cambridge, Inglaterra) fue el primer computador

electrnico prctico de programa almacenado (mayo de 1949)

Manchester Mark I (Universidad de Manchester, Inglaterra) Desarrollado a

partir de la SSEM (junio de 1949)

CSIRAC (Consejo de Investigacin Cientfica e Industrial) Australia (noviembre

de 1949)

EDVAC (Laboratorio de Investigacin Balstica, Laboratorio de Informtica de

Aberdeen Proving Ground, 1951)

ORDVAC (U-Illinois) en Aberdeen Proving Ground, Maryland (completado en

noviembre de 1951)13

IAS machine en Princeton University (enero 1952)

MANIAC I en Laboratorio Cientfico Los lamos (marzo de 1952)

ILLIAC en la Universidad de Illinois, (setiembre de 1952)

AVIDAC en Laboratorios Argonne National (1953)

ORACLE en Laboratorio Nacional de Oak Ridge (junio de 1953)

JOHNNIAC en RAND Corporation (enero de 1954)

BESK en Estocolmo (1953)

BESM-1 en Mosc (1952)

DASK en Dinamarca (1955)

PERM en Mnich (1956?)

SILLIAC en Sdney (1956)

WEIZAC en Rehovoth (1955)

Primeras computadoras de programa almacenado

La informacin de la fecha en la siguiente cronologa es difcil de establecer en el orden

correcto. Algunas fechas son de la primera ejecucin de un programa de pruebas,

algunas fechas son de la primera vez que el equipo se demostr o complet, y algunas

fechas son de la primera entrega o instalacin.

La IBM SSEC tena la capacidad para tratar instrucciones como datos, y se

demostr pblicamente el 27 de enero de 1948. Esta capacidad fue reivindicada

en una patente estadounidense.14 Sin embargo, fue parcialmente

electromecnica, no totalmente electrnica. En la prctica, las instrucciones eran

ledas desde una cinta de papel debido a su memoria limitada.15

La Manchester SSEM (la beb) fue la primera computadora completamente

electrnica que ejecutaba un programa almacenado. Se corri un programa de

factoraje durante 52 minutos el 21 junio de 1948, despus de ejecutar un simple

programa de divisin y un programa para demostrar que dos nmeros eran

primos entre s.

La ENIAC fue modificada para funcionar como un computador primitivo con

programa almacenado de solo lectura (usando la tabla de funciones de programa

ROM) y se demostr como tal el 16 de septiembre de 1948, ejecutando un

programa de Adele Goldstine para von Neumann.

La BINAC corri algunos programas de prueba en febrero, marzo y abril de

1949, aunque no se termin hasta septiembre de 1949.

La Manchester Mark I desarrollada basada en el proyecto SSEM. En abril de

1949, con el fin de para ejecutar programas, se hizo disponible una versin

intermedia de la Mark 1, pero no se termin hasta octubre de 1949.

La EDSAC corri su primer programa el 6 de mayo de 1949.

La EDVAC fue presentada en agosto de 1949, pero tuvo problemas que la

mantena de su puesta en funcionamiento regular hasta 1951.

La CSIR Mark I corri su primer programa en noviembre de 1949.

La SEAC fue demostrada en abril de 1950.

La Pilot ACE corri su primer programa el 10 de mayo 1950 y fue demostrada

en diciembre de 1950

La SWAC se complet en julio de 1950.

La Computadora Whirlwind se complet en diciembre de 1950 y estuvo en uso

real en abril de 1951.

La ERA 1101 (ms tarde la ERA 1101/UNIVAC 1101 comercial) se instal en

diciembre de 1950.

Cuello de botella de von Neumann (von Neumann bottleneck)

El canal de transmisin de los datos compartido entre CPU y memoria genera un cuello

de botella de Von Neumann, un rendimiento limitado (tasa de transferencia de datos)

entre la CPU y la memoria en comparacin con la cantidad de memoria. En la mayora

de computadoras modernas, la velocidad de comunicacin entre la memoria y la CPU es

ms baja que la velocidad a la que puede trabajar esta ltima, reduciendo el rendimiento

del procesador y limitando seriamente la velocidad de proceso eficaz, sobre todo cuando

se necesitan procesar grandes cantidades de datos. La CPU se ve forzada a esperar

continuamente a que lleguen los datos necesarios desde o hacia la memoria. Puesto a

que la velocidad de procesamiento y la cantidad de memoria han aumentado mucho ms

rpidamente que el rendimiento de transferencia entre ellos, el cuello de botella ha

vuelto ms que un problema, un problema cuya gravedad aumenta con cada nueva

generacin de CPU.

El trmino cuello de botella de von Neumann fue acuado por John Backus en su

conferencia de la concesin del Premio Turing ACM de 1977. Segn Backus:

Seguramente debe haber una manera menos primitiva de realizar grandes cambios en la

memoria, que empujando tantas palabras hacia un lado y otro del cuello de botella de von

Neumann. No solo es un cuello de botella para el trfico de datos, sino que, ms importante, es

un cuello de botella intelectual que nos ha mantenido atados al pensamiento de "una palabra a la

vez" en vez de fomentarnos el pensar en unidades conceptuales mayores. Entonces la

programacin es bsicamente la planificacin del enorme trfico de palabras que cruzan el

cuello de botella de von Neumann, y gran parte de ese trfico no concierne a los propios datos,

sino a dnde encontrar stos.[18] [19]

El problema de rendimiento puede ser aliviado (hasta cierto punto) utilizando diversos

mecanismos. Ofreciendo una memoria cach entre la CPU y la memoria principal,

proporcionando cachs separadas o vas de acceso independientes para datos e

instrucciones (la llamada arquitectura Harvard modificada), utilizando algoritmos y

lgica de predictor de saltos y proporcionando una limitada pila de CPU u otro en el

chip de memoria reutilizable para reducir el acceso a memoria, son cuatro de las

maneras que se dispone para aumentar el rendimiento. El problema tambin se puede

eludirse, cierta medida, usando computacin paralela, utilizando por ejemplo la

arquitectura de acceso a memoria no uniforme (NUMA), este enfoque es

comnmente empleado por las supercomputadoras. Est menos claro si el cuello de

botella intelectual que criticaba Backus ha cambiado mucho desde 1977. La solucin

que propuso Backus no ha tenido influencia importante.[cita requerida] La moderna

programacin funcional y la programacin orientada a objetos se preocupan mucho

menos de "empujar un gran nmero de palabras hacia un lado a otro" que los lenguajes

anteriores como era Fortran, pero internamente, esto sigue siendo lo que las

computadoras pasan gran parte del tiempo haciendo, incluso las supercomputadoras

altamente paralelas.

A partir de 1996, un estudio de referencia de base de datos se encontr que tres de cada

cuatro ciclos de CPU se dedican a la espera de memoria. Los investigadores esperan que

el aumento del nmero de instrucciones simultneas arroye con el multihilo o el

multiprocesamiento de un solo chip har de este cuello de botella an peor. [20]

Procesadores no von Neumann

El National Semiconductor (Semiconductor nacional) COP8 se introdujo en 1986; tiene

una arquitectura Harvard modificada.[21] [22]

Tal vez el tipo ms comn de estructura no von Neumann se utiliza en las computadoras

modernas es la memoria de contenido direccionable (CAM).

Arquitectura de von Neumann: Tradicionalmente los sistemas con microprocesadores se

basan en esta arquitectura, en la cual la unidad central de proceso (CPU), est conectada

a una memoria principal nica (casi siempre slo RAM) donde se guardan las

instrucciones del programa y los datos. A dicha memoria se accede a travs de un sistema

de buses nico (control, direcciones y datos).

En un sistema con arquitectura Von Neumann el tamao de la unidad de datos o

instrucciones est fijado por el ancho del bus que comunica la memoria con la CPU. As un

microprocesador de 8 bits con un bus de 8 bits, tendr que manejar datos e instrucciones

de una o ms unidades de 8 bits (bytes) de longitud. Si tiene que acceder a una instruccin

o dato de ms de un byte de longitud, tendr que realizar ms de un acceso a la memoria.

El tener un nico bus hace que el microprocesador sea ms lento en su respuesta, ya que

no puede buscar en memoria una nueva instruccin mientras no finalicen las

transferencias de datos de la instruccin anterior.

Las principales limitaciones que nos encontramos con la arquitectura Von Neumann son:

La limitacin de la longitud de las instrucciones por el bus de datos, que hace que

el microprocesador tenga que realizar varios accesos a memoria para buscar

instrucciones complejas.

La limitacin de la velocidad de operacin a causa del bus nico para datos e

instrucciones que no deja acceder simultneamente a unos y otras, lo cual impide

superponer ambos tiempos de acceso

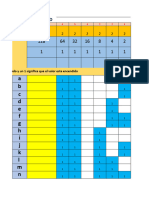

Los ordenadores con arquitectura Von Neumann constan de las siguientes partes:

La arquitectura Von Neumann realiza o emula los siguientes pasos secuencialmente:

1) Obtiene la siguiente instruccin desde la memoria en la direccin indicada por el

contador de programa y la guarda en el registro de instruccin.

2) Aumenta el contador de programa en la longitud de la instruccin para apuntar a la

siguiente.

3) Descodifica la instruccin mediante la unidad de control. sta se encarga de coordinar el

resto de componentes del ordenador para realizar una funcin determinada.

4) Se ejecuta la instruccin. sta puede cambiar el valor del contador del programa,

permitiendo as operaciones repetitivas.

5) Regresa al paso N 1.

Conclusin:

* La mayora de las computadoras todava utilizan la arquitectura Von Neumann, propuesta

a principios de los aos 40 por John Von Neumann.

* La arquitectura Von Neumann describe a la computadora con 4 secciones principales: la

unidad lgica y aritmtica (ALU), la unidad de control, la memoria, y los dispositivos de

entrada y salida (E/S).

* En este sistema, la memoria es una secuencia de celdas de almacenamiento numeradas,

donde cada una es un bit, o unidad de informacin.

La instruccin es la informacin necesaria para realizar, lo que se desea, con la

computadora.

Las celdas contienen datos que se necesitan para llevar a cabo las instrucciones, con la

computadora.

* El tamao de cada celda y el nmero de celdas vara mucho de computadora a

computadora, y las tecnologas empleadas para la memoria han cambiado bastante; van

desde los rels electromecnicos, tubos llenos de mercurio en los que se formaban los

pulsos acsticos, matrices de imanes permanentes, transistores individuales a circuitos

integrados con millones de celdas en un solo chip.

Arquitectura Harvard: Este modelo, que utilizan los Microcontroladores PIC, tiene la

unidad central de proceso (CPU) conectada a dos memorias (una con las instrucciones y

otra con los datos) por medio de dos buses diferentes.

Una de las memorias contiene solamente las instrucciones del programa (Memoria de

Programa), y la otra slo almacena datos (Memoria de Datos).

Ambos buses son totalmente independientes lo que permite que la CPU pueda acceder de

forma independiente y simultnea a la memoria de datos y a la de instrucciones. Como los

buses son independientes estos pueden tener distintos contenidos en la misma direccin y

tambin distinta longitud.

Tambin la longitud de los datos y las instrucciones puede ser distinta, lo que optimiza el

uso de la memoria en general.

Para un procesador de Set de Instrucciones Reducido, o RISC (Reduced Instruccin

Set Computer), el set de instrucciones y el bus de memoria de programa pueden

disearse de tal manera que todas las instrucciones tengan una sola posicin de memoria

de programa de longitud.

Adems, al ser los buses independientes, la CPU puede acceder a los datos para

completar la ejecucin de una instruccin, y al mismo tiempo leer la siguiente instruccin a

ejecutar.

Ventajas de esta arquitectura:

* El tamao de las instrucciones no esta relacionado con el de los datos, y por lo tanto

puede ser optimizado para que cualquier instruccin ocupe una sola posicin de memoria

de programa, logrando as mayor velocidad y menor longitud de programa.

* El tiempo de acceso a las instrucciones puede superponerse con el de los datos,

logrando una mayor velocidad en cada operacin.

Você também pode gostar

- 1 Modulo IV Submódulo 1 Clasifica Los Elementos Básicos de La Red Lan PresentaciónDocumento2 páginas1 Modulo IV Submódulo 1 Clasifica Los Elementos Básicos de La Red Lan PresentaciónGueraAinda não há avaliações

- Ejemplos Python BásicoDocumento30 páginasEjemplos Python BásicoJuan Manuel CarreonAinda não há avaliações

- Formas InternasDocumento4 páginasFormas InternasDaniel AlfonsoAinda não há avaliações

- Tarea Semana 5 Fundamentos de Redes y Seguridad.Documento4 páginasTarea Semana 5 Fundamentos de Redes y Seguridad.Cristhian MontecinosAinda não há avaliações

- Configuración de OSPFv2 en Área Única - InstructionesDocumento2 páginasConfiguración de OSPFv2 en Área Única - InstructionesSara Romero100% (1)

- Transaccion SQVI: Quick ViewerDocumento7 páginasTransaccion SQVI: Quick ViewerNeeraj MishraAinda não há avaliações

- Notas HTML Css JSDocumento29 páginasNotas HTML Css JSenzoenlawebAinda não há avaliações

- Codigo Binario. AngelDocumento17 páginasCodigo Binario. Angelk898zfwgcpAinda não há avaliações

- 7KG85010AA012AA0 Datasheet EsDocumento3 páginas7KG85010AA012AA0 Datasheet EsFernando Jimenez RondonAinda não há avaliações

- SofwaresDocumento4 páginasSofwaresdyalnAinda não há avaliações

- Instrucciones Básicas AssemblerDocumento3 páginasInstrucciones Básicas AssemblerEric Santiago Joya AlvarezAinda não há avaliações

- Rubrica Arquitectura de La CPUDocumento1 páginaRubrica Arquitectura de La CPUMatt HardyAinda não há avaliações

- Curso de La TerminalDocumento27 páginasCurso de La TerminalIsmael CiprianAinda não há avaliações

- PDF Report 4Documento7 páginasPDF Report 4victor ChinoAinda não há avaliações

- Tarea 5-1Documento2 páginasTarea 5-1Luismi GarciaAinda não há avaliações

- 374 TP 2022-1Documento9 páginas374 TP 2022-1bea roseAinda não há avaliações

- Impresora Zebra SOP PDFDocumento20 páginasImpresora Zebra SOP PDFBerenice GarcíaAinda não há avaliações

- Procesadores de TextoDocumento28 páginasProcesadores de TextoChristian PerezAinda não há avaliações

- 1ir 6 A Perez Francisco T2.3Documento7 páginas1ir 6 A Perez Francisco T2.3Usiel PerezAinda não há avaliações

- Tarea 6 LengynfierroDocumento14 páginasTarea 6 LengynfierroLenin CabañasAinda não há avaliações

- Actividad 4Documento3 páginasActividad 4Efren Jesus .Florez CampoAinda não há avaliações

- Temario Ipasolink 200+TEDocumento3 páginasTemario Ipasolink 200+TEJavier DávilaAinda não há avaliações

- Ejercicio Simulación Programación PLC en Aplicativo Móvil PLC TrainerDocumento5 páginasEjercicio Simulación Programación PLC en Aplicativo Móvil PLC TrainerJaqueline QuiñonesAinda não há avaliações

- Instalar Anaconda y Asociar A PycharmDocumento12 páginasInstalar Anaconda y Asociar A PycharmDevid James Russian Romero ApoloAinda não há avaliações

- Fundamentos de Bases de DatosDocumento46 páginasFundamentos de Bases de DatosRamiro HerreraAinda não há avaliações

- Computacion Tipos de Sistemas OperativosDocumento6 páginasComputacion Tipos de Sistemas OperativosJORGE AARON ASAinda não há avaliações

- Reutilizacion de CodigoDocumento15 páginasReutilizacion de CodigoEduardo CortesAinda não há avaliações

- Requisitos Hardware Sage50Documento19 páginasRequisitos Hardware Sage50xisco boschAinda não há avaliações

- S01.s2-Redes de ConmutaciónDocumento27 páginasS01.s2-Redes de ConmutaciónBilly Omar Muñoz PeinadoAinda não há avaliações

- Lab de Redes Practica 5 Maria SosaDocumento4 páginasLab de Redes Practica 5 Maria SosaMaria SosaAinda não há avaliações