Escolar Documentos

Profissional Documentos

Cultura Documentos

Tipos de Arbitros

Enviado por

Adriana Segura0 notas0% acharam este documento útil (0 voto)

134 visualizações2 páginasClasificación de tipos de árbitros de bus

Título original

Tipos de arbitros

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

DOCX, PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoClasificación de tipos de árbitros de bus

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato DOCX, PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

134 visualizações2 páginasTipos de Arbitros

Enviado por

Adriana SeguraClasificación de tipos de árbitros de bus

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato DOCX, PDF, TXT ou leia online no Scribd

Você está na página 1de 2

TIPOS DE RBITROS DEL BUS

1. Basados en el algoritmo de asignacin

a. FIFO: Las peticiones de asignacin se atienden en el mismo

orden en que llegan.

b. Prioridad Fija: El algoritmo da a cada procesador una

prioridad fija, o sea, si varios procesadores solicitan asignacin

del recurso (bus), entonces el acceso al recurso lo tendr el

que tenga mayor prioridad.

c. Prioridad Rotativa o Roud Robin: Las prioridades de los

procesadores va cambiando dinmicamente de forma rotativa

debido a que el procesador que termina de usar el recurso

asignado, pasa a tener la prioridad ms baja de todos y no

volver a tener acceso al recurso hasta que hayan accedido a

este todos los procesadores que lo hubieran solicitado.

d. LRU (ultimo usado recientemente): Aqu tambin la

prioridad cambia dinmicamente. La mxima prioridad la

obtiene, dentro de los procesadores que hayan solicitado el

acceso al bus, aquel que hace ms tiempo que no ha utilizado

el recurso. Para que esto se lleve a cabo es necesario que se

cambien las prioridades despus de cada asignacin.

e. Random (acceso aleatorio): En este algoritmo, la asignacin

del recurso se hace al azar o de forma aleatoria entre todas las

peticiones de uso de este.

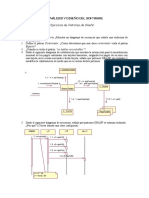

2. Basados en la distribucin fsica

a. Centralizado: Este rbitro tiene todo su hardware centralizado

en una posicin fsica y recibe todas las peticiones de los

procesadores y de el salen las asignaciones necesarias.

b. Distribuido: La mayor parte de la lgica de control necesaria

para arbitrar los recursos se encuentra distribuida entre los

procesadores. Cada rbitro recibe las peticiones de su

procesador asociado, adems de otras seales necesarias

provenientes de los dems rbitros de los procesadores, y

asigna el recurso en cuestin a su procesador segn la lgica

del sistema.

c. Semidistribuido: En este, parte de la lgica de control esta

distribuida en los componentes del sistema y, parte en una

unidad central. Se coloca en una unidad central el hardware

que ha de realizar las funciones de comunicacin entre varios

procesadores y en los mdulos separados, las funciones

exclusivas de cada procesador.

3. Basados en el nmero de recursos que controlan

a. De un solo recurso: Manejan un recurso solamente (por

ejemplo, el bus comn del sistema), es decir, pueden recibir un

mximo de N peticiones simultneas, siendo N el nmero de

procesadores, pero solo puede hacer una asignacin a la vez.

b. De varios recursos: Es por lo general global al sistema. En un

sistema con N procesadores y M mdulos de memoria,

conectados entre s por B buses, el rbitro recibe hasta un

mximo de N peticiones simultneas y gestiona B asignaciones

de recursos o buses.

4. Basados en la sincronizacin

a. Sncronos: Son aquellos que funcionan con la misma seal de

reloj de los elementos para los cuales sirve de rbitro y se

encargan de la sincronizacin de todos ellos. Las peticiones de

uso de un recurso se hacen a intervalos de tiempo fijos o

regulares.

b. Asncronos: Son aquellos que controlan componentes que

funcionan asincrnicamente, o sea, con diferentes seales de

reloj. Las peticiones de uso de un recurso se hacen a intervalos

de tiempo variables o irregulares.

5. Basados en su implementacin fsica

a. Software: Se construye con el mnimo soporte digital posible,

siendo el sistema operativo el encargado de realizar todas las

funciones de arbitraje.

b. Hardware: El rbitro, incluyendo la circuitera de ejecucin del

algoritmo, se implementa fsicamente con tecnologa digital.

c. Microprogramado: El rbitro se construye por completo, en

hardware, pero el algoritmo de ejecucin se encuentra grabado

como un microprograma en una memoria ROM.

d. De algoritmo Programable: Es un rbitro que puede

ejecutar varios algoritmos de asignacin.

Você também pode gostar

- DOMOTICA CON Arduino PDFDocumento44 páginasDOMOTICA CON Arduino PDFjdrsant100% (5)

- Codesys Manual ABB 1Documento85 páginasCodesys Manual ABB 1jjurado183Ainda não há avaliações

- ProgramaDocumento2 páginasProgramaAdriana SeguraAinda não há avaliações

- 9.1.4.7 Packet Tracer - Subnetting Scenario 2 InstructionsDocumento5 páginas9.1.4.7 Packet Tracer - Subnetting Scenario 2 InstructionsAdriana SeguraAinda não há avaliações

- Antro Polo GiaDocumento4 páginasAntro Polo GiaAdriana SeguraAinda não há avaliações

- Informe EdaDocumento18 páginasInforme EdaAdriana SeguraAinda não há avaliações

- Ejemplo 2Documento1 páginaEjemplo 2Adriana SeguraAinda não há avaliações

- Bases Ronda Concur Sables OficialDocumento14 páginasBases Ronda Concur Sables OficialAdriana SeguraAinda não há avaliações

- Plantilla 12 - 2003 - Valor CreativoDocumento2 páginasPlantilla 12 - 2003 - Valor CreativoAdriana SeguraAinda não há avaliações

- Anahi CantuñaDocumento2 páginasAnahi CantuñaAdriana SeguraAinda não há avaliações

- Códigos de Error de Actualización Del Sistema Xbox 360Documento6 páginasCódigos de Error de Actualización Del Sistema Xbox 360daniel 666Ainda não há avaliações

- Lab 07 Ace1 2018-ADocumento11 páginasLab 07 Ace1 2018-AAngelo Aco MendozaAinda não há avaliações

- Presentacion Semiconductores Unidad 2Documento28 páginasPresentacion Semiconductores Unidad 2REYES APOLONIO CASTRO CORRALAinda não há avaliações

- Temario Excel Profesional BasicoDocumento8 páginasTemario Excel Profesional BasicoDanny SaldañaAinda não há avaliações

- Manual VP-10 - ES - E01Documento82 páginasManual VP-10 - ES - E01Pedro Domingo Herrera PérezAinda não há avaliações

- RUCKUS R750 Data Sheet - SpanishDocumento6 páginasRUCKUS R750 Data Sheet - SpanishSergio HernandezAinda não há avaliações

- Resumen de Windows 10 y UbuntuDocumento7 páginasResumen de Windows 10 y UbuntuLynBCAinda não há avaliações

- Instalación S.O en Virtual BoxDocumento6 páginasInstalación S.O en Virtual BoxBelen Stefania Solorzano GomezAinda não há avaliações

- A Short Tour of UMLDocumento12 páginasA Short Tour of UMLYazmin Alberto Patiño - 603Ainda não há avaliações

- 10 EthernetDocumento21 páginas10 EthernetAlan MourentanAinda não há avaliações

- Tarea 20. Gráfica de La Curva de Transconductancia para El MOSFET Tipo Enriquecimiento Canal N Con Polarización Por Divisor de VoltajeDocumento4 páginasTarea 20. Gráfica de La Curva de Transconductancia para El MOSFET Tipo Enriquecimiento Canal N Con Polarización Por Divisor de VoltajeALEJANDRO LOPEZ AYALAAinda não há avaliações

- ProyectoDocumento4 páginasProyectoRafael BejaranoAinda não há avaliações

- Parcial Redes 2Documento5 páginasParcial Redes 2ANDRES FELIPE BARBOSA SALAMANCAAinda não há avaliações

- Manual Introduccion A La ComputaciónDocumento8 páginasManual Introduccion A La ComputaciónmaryjarAinda não há avaliações

- Unidades de Medida InformaticaDocumento2 páginasUnidades de Medida InformaticaLester TambitoAinda não há avaliações

- Guia 4 MicroDocumento3 páginasGuia 4 MicroD.Aleja ortizAinda não há avaliações

- Practica Numero 8. PIC Puertos Como Entradas y SalidasDocumento10 páginasPractica Numero 8. PIC Puertos Como Entradas y SalidasRoiberth GonzálezAinda não há avaliações

- Caracteristicas de Los EquiposDocumento12 páginasCaracteristicas de Los Equiposandres castilloAinda não há avaliações

- WINDOWSDocumento5 páginasWINDOWSyerson barretoAinda não há avaliações

- Investigaciones de Windows XPDocumento2 páginasInvestigaciones de Windows XPValeria Mora GarciaAinda não há avaliações

- Sistemas Operativos. Introducción. Actividades. SolucionesDocumento5 páginasSistemas Operativos. Introducción. Actividades. SolucionesCarlos CastroAinda não há avaliações

- Sesión UNAM OPR14082023Documento52 páginasSesión UNAM OPR14082023OMAR PEREZAinda não há avaliações

- SBES - Preparation.2022 SPDocumento58 páginasSBES - Preparation.2022 SPJuan Eduardo SchebelaAinda não há avaliações

- Instructivo Configuracion de Servicios E1-ETH Nokia MPR-MSSDocumento17 páginasInstructivo Configuracion de Servicios E1-ETH Nokia MPR-MSSmaximusandAinda não há avaliações

- 2) Punta LogicaDocumento2 páginas2) Punta LogicaNelson Barrera LombanaAinda não há avaliações

- Victor Gonzalez A00124162-Conceptos BasicosDocumento4 páginasVictor Gonzalez A00124162-Conceptos Basicosvíctor jose balbuena de los santosAinda não há avaliações

- Electronica GeneralDocumento6 páginasElectronica GeneralXavi JumboAinda não há avaliações

- Ejercicios Patrones 2005Documento10 páginasEjercicios Patrones 2005JudithAinda não há avaliações