Escolar Documentos

Profissional Documentos

Cultura Documentos

El Algoritmo CORDIC

Enviado por

miteratosTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

El Algoritmo CORDIC

Enviado por

miteratosDireitos autorais:

Formatos disponíveis

Descripcin en VHDL de arquitecturas para implementar el algoritmo CORDIC

Captulo 1

El algoritmo CORDIC

CORDIC es un acrnimo de COordinate Rotation DIgital Computer que en castellano

significa Computadora Digital para Rotacin de Coordenadas. El algoritmo original fue propuesto

por Jack Volder en el ao 1959 [1], con el propsito de calcular funciones trigonomtricas

mediante la rotacin de vectores. La rotacin de vectores puede utilizarse a su vez para conversin

de sistemas de coordenadas (cartesiano a polar y viceversa), magnitud de vectores y como parte de

funciones matemticas mas complejas como ser la Transformada Rpida de Fourier (Fast Fourier

Transform, FFT) y la Transformada Coseno Discreta (Discrete Cosine Transform, DCT).

1.1 Fundamento terico

El algoritmo CORDIC, proporciona un mtodo iterativo para rotar vectores ciertos ngulos

determinados y se basa exclusivamente en sumas y desplazamientos. El algoritmo original tal como

fue propuesto inicialmente, describe la rotacin de un vector bidimensional en el plano cartesiano.

Su funcionamiento se deduce de la frmula general para rotacin de vectores como se muestra a

continuacin

x' = x cos y sen

(1.1)

y ' = y cos + x sen

Figura 1.1

Descripcin en VHDL de arquitecturas para implementar el algoritmo CORDIC

La frmula (1.1) se deduce a partir de las identidades trigonomtricas conocidas, en donde

x = r cos

V :

y = r sen

(1.2.a)

x' = r cos

V ':

y ' = r sen

(1.2.b)

Si r = 1 y = entonces = + . Utilizando las identidades para el seno y el coseno

de la suma de ngulos se tiene

sen( + ) = sen cos + cos sen

cos( + ) = cos cos sen sen

(1.3)

Si se sustituye = + en (1.2.b), aplicando (1.3) y (1.2.a), se obtiene

x' = cos( + ) = cos cos sen sen = x cos y sen

y ' = sen( + ) = sen cos + cos sen = x sen + y cos

Con lo que se obtiene la frmula general (1.1), la cual se puede reagrupar considerando que

cos 0 [4] de forma tal que

x' = cos ( x y tg )

(1.4)

y ' = cos ( y + x tg )

Si adems

cos = cos 2 =

1

=

1

cos 2

1

=

1

cos 2

1

sen + cos

cos 2

2

1

cos sen 2

+

cos 2 cos 2

2

1

1 + tg 2

entonces la ecuacin (1.4) puede expresarse como

x' =

y' =

x y tg

1 + tg 2

(1.5)

y + x tg

1 + tg 2

En el algoritmo CORDIC, las rotaciones de vectores son reemplazadas por pseudorotaciones

[7] como se muestra en la figura 1.2.

Descripcin en VHDL de arquitecturas para implementar el algoritmo CORDIC

Figura 1.2

Mientras que una rotacin real no cambia la magnitud del vector V una vez rotado, una

pseudorotacin incrementa su magnitud en

V ' ' = V 1 + tg 2

(1.6)

1 + tg 2 respecto del vector

original V. La pseudorotacin por el ngulo est caracterizada por las ecuaciones

El vector pseudorotado V incrementa su magnitud en

x' ' = x y tg

(1.7)

y ' ' = y + x tg

La rotacin de un ngulo puede descomponerse en una suma de rotaciones mas pequeas. Si

se asume inicialmente que x = x0, y = y0 y z = z0, luego de n iteraciones para una rotacin real se

obtiene,

n 1

n 1

x n' = x cos i y sen i

i =0

i =0

n 1

n 1

y n' = y cos i + x sen i

i =0

i =0

(1.8)

n 1

z n' = z i

i =0

mientras que para una pseudorotacin,

n 1 n 1

n 1

x n' ' = x cos i y sen i 1 + tg 2 i

i =0 i =0

i =0

n 1

n 1 n 1

y n' ' = y cos i + x sen i 1 + tg 2 i

i =0

i =0 i =0

n 1

z n' ' = z i

i =0

(1.9)

Descripcin en VHDL de arquitecturas para implementar el algoritmo CORDIC

, en donde

n 1

i =0

A las ecuaciones 1.8 y 1.9 se agrega una tercera ecuacin para zn que se denomina

acumulador angular [7] porque incluye las rotaciones efectuadas hasta el momento.

En la figura 1.3 se muestra un vector V rotado sobre otro vector V mediante rotaciones

menores.

Figura 1.3

Si los ngulos de rotacin se restringen de forma tal que tg = 2 i , i , la multiplicacin

por la tangente, se reduce a una operacin de desplazamiento. Los diversos ngulos pueden

obtenerse realizando una serie de rotaciones elementales cada vez mas pequeas [Anexo A]. En

cada iteracin, en lugar de determinar si se debe rotar o no, se elige el sentido de rotacin. Partiendo

de las ecuaciones dadas en (1.4), y considerando que cos( i ) = cos( i ) , una iteracin puede

expresarse como

(

= K (y

xi +1 = K i xi y i d i 2 i

y i +1

+ xi d i 2

en donde, K i = cos i = cos arctg 2 i =

)

)

(1.10)

1

1 + tg i

2

1

1 + 2 2i

y d i = 1 dependiendo del sentido

de rotacin.

El factor de expansin K i debe ser multiplicado por las ecuaciones correspondientes a las

pseudorotaciones para obtener la rotacin real.

El ngulo final de una rotacin est determinado por la suma algebraica, segn el sentido de

rotacin, de los ngulos de las rotaciones elementales. Si se elimina K i de las ecuaciones iterativas,

se obtiene un algoritmo basado en sumas y desplazamientos. El factor K i puede aplicarse al final

del proceso como una constante K n , definida como sigue

Descripcin en VHDL de arquitecturas para implementar el algoritmo CORDIC

K n = lim K i 0,6073

n

i =0

El valor exacto de K n depende del nmero de iteraciones. Se define adems

An =

n 1

n 1

1

1

=

= 1 + 2 2i 1,6467

K n i =0 K i i =0

Como se explic anteriormente, en cada paso de iteracin, en lugar de decidir si rotar o no,

se decide el signo o sentido de la rotacin a efectuar. Por lo tanto cada ngulo final se puede

representar mediante un vector de signos, en donde cada componente corresponde a un ngulo de la

secuencia de ngulos elementales. Dichos ngulos elementales se almacenan en una tabla de

bsqueda (Lookup Table, LUT). Con esto ltimo, se modifica el acumulador angular para dar lugar

a la ecuacin,

( )

z i +1 = z i d i arctg 2 i

(1.11)

Dependiendo del sistema angular con el que se trabaje, se almacenan en la tabla las

arcotangentes correspondientes en ese sistema.

El algoritmo CORDIC se opera normalmente en dos modos. El primero, se denomina

rotacin (rotation) que rota el vector de entrada un ngulo especfico que se introduce como

parmetro. El segundo modo, denominado vectorizacin (vectoring), rota el vector de entrada hacia

el eje X, acumulando el ngulo necesario para efectuar dicha rotacin.

En el caso de una rotacin, el acumulador angular se inicializa con el ngulo a rotar. La

decisin sobre el sentido de rotacin en cada paso de iteracin, se efecta para minimizar la

magnitud del ngulo acumulado. Por ello, el signo que determina el sentido de rotacin, se obtiene

del valor de dicho ngulo en cada paso. Para el modo rotacin, las ecuaciones son

xi +1 = xi y i d i 2 i

y i +1 = y i + xi d i 2 i

(1.12)

( )

z i +1 = z i d i arctg 2

1 , si z i < 0

en donde, d i =

1 , si z i 0

partiendo de las ecuaciones (1.9), luego de n etapas, cuando z n 0 1 entonces

n 1

i =0

= z para

x = x0, y = y0, z = z0 [7] se obtiene

De aqu en ms se utiliza

wn para una variable de la forma wn' ' , a los efectos de simplificar las expresiones.

Descripcin en VHDL de arquitecturas para implementar el algoritmo CORDIC

x n = An ( x0 cos z 0 y 0 sen z 0 )

y n = An ( y 0 cos z 0 + x0 sen z 0 )

zn = 0

(1.13)

n 1

An = 1 + 2 2i

i =0

Para una vectorizacin, el ngulo ingresado se rota para alinearlo con el eje X. Para obtener

este resultado, en lugar de minimizar la magnitud del acumulador angular, se minimiza la magnitud

del componente y, ya que si y = 0 entonces el vector se encuentra sobre el eje X. Asimismo se

utiliza el signo del componente y para determinar la direccin de rotacin. Si el acumulador angular

se inicializa con cero, al final del proceso contendr el ngulo de rotacin adecuado. Por lo tanto se

pueden deducir las siguientes ecuaciones

xi +1 = xi y i d i 2 i

y i +1 = y i + xi d i 2 i

(1.14)

( )

z i +1 = z i d i arctg 2

1 , si y i 0

en donde, d i =

1 , si y i < 0

y

n 1

partiendo de las ecuaciones (1.9), luego de n etapas cuando y n 0 entonces tg i = para

x

i =0

x = x0, y = y0, z = z0 [7] se obtiene

x n = An x02 + y 02

yn = 0

y

z n = z 0 + arctg 0

x0

(1.15)

n 1

An = 1 + 2 2i

i =0

debido a que los

2

2

ngulos elementales convergen slo dentro de esos lmites [Anexo A] [4]. Para tratar ngulos que

caen fuera de ese rango, se puede reducir al primer o cuarto cuadrante.

El algoritmo CORDIC est restringido a ngulos tales que

1.2 Clculo del seno y del coseno

El modo rotacin del algoritmo CORDIC puede utilizarse para calcular el seno y el coseno

de un ngulo en forma simultnea. Si se inicializa y0 = 0, de la frmula (1.13) se obtiene

Descripcin en VHDL de arquitecturas para implementar el algoritmo CORDIC

x n = An x0 cos z 0

y n = An x0 sen z 0

zn = 0

(1.16)

n 1

An = 1 + 2 2i

i =0

Si adems x0 =

1

, de (1.16) se tiene que

An

x n = cos z 0

y n = sen z 0

(1.17)

zn = 0

que calcula el seno y el coseno del ngulo inicial z0 .

1.3 Transformacin de coordenadas polares a cartesianas y viceversa

La transformacin T, que hace corresponder coordenadas polares a cartesianas, se define

como

x = r cos

T :

y = r sen

Si se reemplaza en (1.13),

(1.18)

1

r

An

y0 = 0

z0 =

x0 =

(mdulo)

(fase)

se obtiene la transformacin T.

La transformacin de coordenadas cartesianas a polares se puede llevar a cabo utilizando la

transformacin inversa T

r = x 2 + y 2

T ':

y

= arctg

x

(1.19)

Utilizando el modo vectorizacin de CORDIC, se puede sustituir en (1.15)

x0 = x

y0 = y

z0 = 0

Descripcin en VHDL de arquitecturas para implementar el algoritmo CORDIC

Sin embargo el algoritmo tambin computa la constante An que puede ser eliminada

multiplicando por su inverso, lo cual agrega cierta complejidad al algoritmo inicial ya que se precisa

de un multiplicador con el mismo ancho en bits que el resultado.

1.4 Arcotangente y mdulo de un vector

El arcotangente se puede calcular utilizando el modo vectorizacin de CORDIC.

Si se inicializa z0 = 0 y se sustituye en (1.15), se obtiene el trmino zn

x n = An x02 + y 02

yn = 0

y

z n = z 0 + arctg 0

x0

(1.20)

n 1

An = 1 + 2 2i

i =0

El trmino xn representa el mdulo de un vector en el espacio bidimensional en donde x0 e y0

son sus componentes. Nuevamente para eliminar a la constante An se debe agregar al algoritmo un

multiplicador.

1.5 CORDIC generalizado

El algoritmo CORDIC bsico puede ser generalizado para proveer una herramienta an mas

potente para el clculo de funciones. Esta generalizacin fue propuesta por Walther [5]. Se define

xi +1 = xi y i d i 2 i

y i +1 = y i + xi d i 2 i

(1.21)

( )

z i +1 = z i d i f 2 i

La nica diferencia que presenta este algoritmo con el bsico, es la introduccin del

parmetro en la ecuacin correspondiente al componente x y la funcin f(.) que adquiere

significado segn el sistema que se utilice. El parmetro y la funcin f(.) pueden asumir uno de

los tres valores que se muestran a continuacin

=1

=0

y

y

= 1 y

f ( x) = arctg( x )

f ( x) = x

Rotacin Circular (CORDIC bsico)

Rotacin Lineal

f ( x) = tgh 1 (x )

Rotacin Hiperblica

1.5.1 Caso lineal

Si se parte de (1.21) con = 0 y f ( x) = x se obtiene

Descripcin en VHDL de arquitecturas para implementar el algoritmo CORDIC

xi +1 = xi

y i +1 = y i + xi d i 2 i

(1.22)

z i +1 = z i d i 2 i

1 , si z i < 0

Para el modo rotacin, donde d i =

1 , si z i 0

la rotacin lineal produce

x n = x0

y n = y 0 + x0 z 0

(1.23)

zn = 0

Por lo tanto a partir de estas ecuaciones puede obtenerse el producto de dos valores a.b,

sustituyendo

x0 = a

y0 = 0

z0 = b

1 , si y i 0

En modo vectorizacin, donde d i =

1 , si y i < 0

la rotacin lineal produce

x n = x0

yn = z0

y0

x0

(1.24)

zn = 0

Por lo tanto a partir de estas ecuaciones puede obtenerse el cociente de dos magnitudes a/b,

sustituyendo

x0 = b

y 0 = a

z0 = 0

1.5.2 Caso hiperblico

Si se parte de (1.21) con = -1 y f ( x) = tgh 1 ( x ) se obtiene

xi +1 = xi + y i d i 2 i

y i +1 = y i + xi d i 2 i

(1.25)

( )

z i +1 = z i d i tgh 1 2 i

Descripcin en VHDL de arquitecturas para implementar el algoritmo CORDIC

1 , si z i < 0

Para el modo rotacin, donde d i =

1 , si z i 0

la rotacin hiperblica produce

x n = An ( x0 cosh z 0 + y 0 senh z 0 )

y n = An ( y 0 cosh z 0 + x0 senh z 0 )

zn = 0

(1.26)

n 1

An = 1 2 2i 0,80

i =0

1 , si y i 0

Para el modo vectorizacin, donde d i =

1 , si y i < 0

la rotacin hiperblica produce

x n = An x02 y 02

yn = 0

y

z n = z 0 + tgh 1 0

x0

(1.27)

n 1

An = 1 2 2i

i =0

Las rotaciones elementales en el sistema hiperblico no convergen. Sin embargo Walther [5]

demostr que se pueden conseguir los resultados esperados si se repiten algunas de las iteraciones

efectuadas [6].

Las funciones trigonomtricas hiperblicas equivalentes a las funciones trigonomtricas

circulares pueden obtenerse de manera similar a partir de la ecuacin 1.26.

1.6 Arquitecturas para implementar el algoritmo CORDIC

1.6.1 La arquitectura Bit-Paralela Iterativa

Cuando el algoritmo CORDIC se implementa en hardware, una de las arquitectura

correspondientes es la arquitectura bit-paralela iterativa [3]. La denominacin de paralela se debe a

la forma en que se opera con las componentes X, Y y Z. En esta arquitectura cada etapa del

algoritmo consiste de un registro para almacenar la salida, una unidad de desplazamiento y un

sumador algebraico. Al comenzar el clculo, los valores iniciales para x0 , y 0 y z 0 ingresan en

forma paralela a los registros a travs del multiplexor. El bit ms significativo del componente Z Y

en cada paso de iteracin determina la operacin a efectuar por el sumador algebraico en modo

rotacin o vectorizacin respectivamente. Las seales correspondientes a los componentes X e Y son

desplazadas y luego restadas o sumadas a las seales sin desplazar, correspondientes al componente

opuesto. El componente Z combina los valores almacenados en el registro con valores que obtiene

de una tabla de bsqueda (Lookup Table, LUT) de arcotangentes precalculadas con una cantidad de

10

Descripcin en VHDL de arquitecturas para implementar el algoritmo CORDIC

entradas proporcional a la cantidad de iteraciones. Esta tabla de bsqueda puede ser implementada

como una memoria ROM. La direccin de memoria cambia acorde al nmero de iteracin. Para n

iteraciones el valor a calcular puede ser obtenido en la salida. Se requiere de un controlador que

puede ser implementado como una mquina de estados para controlar los multiplexores, la cantidad

de desplazamientos y el direccionamiento de las constantes precalculadas. Esta representacin tiene

como ventaja el uso eficiente de hardware, debido a que los recursos (registros, multiplexores,

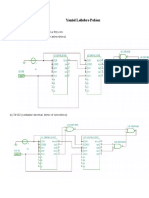

unidades de desplazamiento y sumadores) son reutilizados en cada iteracin. En la figura 1.4 se

muestra el esquema correspondiente a la arquitectura descripta. La seal Modo especifica el modo

de operacin (Rotacin o Vectorizacin). Se considera adems en el esquema que las componentes

tienen un ancho de m bits. Sin embargo se puede ampliar el ancho en bits de los buses internos para

obtener una mejor exactitud [6].

Figura 1.4

1.6.2 La arquitectura Bit-Paralela Desplegada

En lugar de almacenar el resultado de cada paso de iteracin en registros y volver a utilizar

los mismos recursos, el diseo puede desplegarse [3] como muestra la Figura 1.5. El diseo se

separa en etapas correspondientes a cada iteracin. Cada etapa est compuesta por los mismos

componentes, dos unidades de desplazamiento y dos sumadores algebraicos. Por consiguiente la

salida de una etapa corresponde a la entrada de la siguiente etapa. Los valores iniciales para x0 , y 0

y z 0 se ingresan en paralelo a la primera etapa.

Este diseo introduce dos ventajas importantes. Las unidades de desplazamiento as como

las constantes correspondientes a cada iteracin pueden ser cableadas. La segunda ventaja radica en

que el circuito es puramente combinatorio, y por lo tanto no se necesita de una unidad de control,

simplificando enormemente el diseo. La desventaja que presenta esta arquitectura es la enorme

cantidad de espacio que requiere su implementacin.

11

Descripcin en VHDL de arquitecturas para implementar el algoritmo CORDIC

En el esquema se supone un ancho de palabra de m bits. La seal Modo indica el modo de

operacin al igual que en el caso iterativo.

Figura 1.5

1.6.3 La arquitectura Bit-Serie Iterativa

En un diseo en serie, se procesa un bit por vez, con lo cual las interconexiones se reducen

al ancho de un bit [1] [3]. El desempeo de esta arquitectura se puede calcular como

=

velocidad de reloj

nmero de iteraciones ancho de palabra

La arquitectura resultante se muestra en la Figura 1.6. Cada etapa del algoritmo consiste en

un multiplexor, un registro de desplazamiento y un sumador algebraico bit-serie. El sumador

algebraico se implementa como un sumador completo en el que una resta se lleva a cabo sumando

el complemento a dos del valor a restar. La operacin a efectuar por el sumador algebraico se

obtiene del bit de signo del componente z para el modo rotacin. Para el modo vectorizacin, del bit

de signo se obtiene del componente y.

12

Descripcin en VHDL de arquitecturas para implementar el algoritmo CORDIC

Figura 1.6

La operacin de desplazamiento (multiplicacin por 2 i ) se lleva a cabo leyendo el bit i 1

considerado a partir del extremo derecho del registro de desplazamiento. Se puede usar un

multiplexor para cambiar la posicin de acuerdo a la iteracin actual. Los valores iniciales para x0 ,

y 0 y z 0 ingresan al registro de desplazamiento por el extremo izquierdo en el esquema. Cuando el

primer bit que fue ingresado al registro es procesado por el sumador algebraico, el multiplexor

permite nuevamente el ingreso de los bits sumados al registro de desplazamiento. Por ltimo,

cuando se han completado todas las iteraciones los multiplexores permiten el ingreso de un nuevo

valor al registro de desplazamiento y el valor calculado se obtiene en la salida. Alternativamente la

carga y lectura del registro de desplazamiento puede efectuarse en paralelo para simplificar el

diseo. La desventaja que presenta esta arquitectura con respecto a las que procesan los vectores de

entrada en forma paralela es que se introduce un retardo proporcional al ancho de palabra en cada

etapa, ocasionado por los desplazamientos. Por otra parte se requiere de hardware de control mas

complejo. La ventaja que presenta esta arquitectura es que los buses de interconexin entre los

componentes son del ancho de un bit y el registro de desplazamiento est integrado con el registro

intermedio, minimizando espacio al momento de su implementacin.

13

Você também pode gostar

- G.Guzman - IMA - 3B - Actividad 4 - Ecuaciones ParamétricasDocumento9 páginasG.Guzman - IMA - 3B - Actividad 4 - Ecuaciones ParamétricasjulioAinda não há avaliações

- Trabajo de Investigación Formativa Sobre La Aplicación de Funciones Vectoriales de Variable Real A La Ingeniería CivilDocumento11 páginasTrabajo de Investigación Formativa Sobre La Aplicación de Funciones Vectoriales de Variable Real A La Ingeniería CivilJeanet QuispeAinda não há avaliações

- UNIDAD 02 Ejercicios Robotica I ExtDocumento11 páginasUNIDAD 02 Ejercicios Robotica I ExtPablo DuqueAinda não há avaliações

- Método de BOWDITCH para la compensación de itinerarios topográficosDocumento28 páginasMétodo de BOWDITCH para la compensación de itinerarios topográficosGonzaloUrrutia100% (2)

- Transformaciones Geometricas 3DDocumento27 páginasTransformaciones Geometricas 3DIsai Isra Gomez ReyAinda não há avaliações

- DINAMICADocumento7 páginasDINAMICALeonardo LoeraAinda não há avaliações

- 5Documento7 páginas5Areli Cervantes OlguinAinda não há avaliações

- TEORÍA DE GREEN Y STOKESDocumento8 páginasTEORÍA DE GREEN Y STOKESDeyvi GarciaAinda não há avaliações

- Capitulo 1 TrigonometriaDocumento44 páginasCapitulo 1 TrigonometriaPaulaFigueroaAinda não há avaliações

- Matematica ChatgptDocumento4 páginasMatematica ChatgptJavier Alejandro Madero TorresAinda não há avaliações

- Proyecto de IntegralesDocumento12 páginasProyecto de IntegralesAnthony GuzmanAinda não há avaliações

- Tema 6. Integral de Linea-A PDFDocumento10 páginasTema 6. Integral de Linea-A PDFLuis Antonio Trujillo VazquezAinda não há avaliações

- ToroDocumento46 páginasToroElsa VelazquezAinda não há avaliações

- Mvi SPDocumento55 páginasMvi SPMauricio Alexander Martinez ArredondoAinda não há avaliações

- Calculo Iii 7.2Documento10 páginasCalculo Iii 7.2Anthony Gonzales SotoAinda não há avaliações

- Implementación VHDL algoritmo CORDICDocumento13 páginasImplementación VHDL algoritmo CORDICGerman ItuAinda não há avaliações

- Tema 7 Mat 102 1-2023 G - C. CivilDocumento18 páginasTema 7 Mat 102 1-2023 G - C. CivilLoopCast 123Ainda não há avaliações

- Coreccion AngularDocumento12 páginasCoreccion AngularJhamil Bizarro RivasAinda não há avaliações

- UntitledDocumento10 páginasUntitledJair CruzAinda não há avaliações

- Algoritmo BresenhamDocumento7 páginasAlgoritmo BresenhamMahurem0% (1)

- Taller de Calculo Vectorial Tercer CorteDocumento8 páginasTaller de Calculo Vectorial Tercer CorteRAFAEL JOSE PINEDA HERRERAAinda não há avaliações

- Calculo Coordenadas PolaresDocumento7 páginasCalculo Coordenadas PolaresdanilCortezAinda não há avaliações

- Algunos Tensores de Segundo OrdenDocumento19 páginasAlgunos Tensores de Segundo OrdenAMYNNXXXXAinda não há avaliações

- Informe Laboratorio FisicaDocumento13 páginasInforme Laboratorio FisicaClement Holguin100% (2)

- Rodamiento Puro Por VideoanalisisDocumento11 páginasRodamiento Puro Por VideoanalisisLENNI DAYARA HERNANDEZ GARCIAAinda não há avaliações

- Cálculo de desplazamientos en vigas sometidas a flexión usando el método de los parámetros de origenDocumento8 páginasCálculo de desplazamientos en vigas sometidas a flexión usando el método de los parámetros de origenjuankalozAinda não há avaliações

- 01 - Movimientos de Especial Interés - ContenidosDocumento8 páginas01 - Movimientos de Especial Interés - ContenidosLuckyAinda não há avaliações

- 00a. Isoclinas y Campo de DireccionesDocumento20 páginas00a. Isoclinas y Campo de DireccionesCarmen723Ainda não há avaliações

- Coordenadas PolaresDocumento23 páginasCoordenadas PolaresGavi SitaAinda não há avaliações

- AndyDocumento20 páginasAndyedwiin fdzAinda não há avaliações

- CircunferenciaDocumento7 páginasCircunferenciaAlexis FloresAinda não há avaliações

- Modulo 3 Discusion Matematica Del ConductorDocumento17 páginasModulo 3 Discusion Matematica Del ConductorMaloni Alcantara JimenezAinda não há avaliações

- Aplicaciones básicas de la integral de Riemann: áreas, volúmenes y longitudesDocumento13 páginasAplicaciones básicas de la integral de Riemann: áreas, volúmenes y longitudesEduardo MontañaAinda não há avaliações

- Unidad II Graficación 2DDocumento6 páginasUnidad II Graficación 2Dsamdiaz10Ainda não há avaliações

- Método de W. Fuchssteiner-Darmstadt para el análisis de escaleras helicoidalesDocumento41 páginasMétodo de W. Fuchssteiner-Darmstadt para el análisis de escaleras helicoidalesGonsalo TerrazasAinda não há avaliações

- 2 Construccion de Las Ecuaciones de Movimiento CircularDocumento2 páginas2 Construccion de Las Ecuaciones de Movimiento CircularSebastianGonzalezSAinda não há avaliações

- Integrales Triples - PresentaciónDocumento41 páginasIntegrales Triples - PresentaciónRICH ALBERT SARMIENTO ARRIAGAAinda não há avaliações

- Movimiento en Un Plano y en El Espacio Problemas Resueltos PDFDocumento31 páginasMovimiento en Un Plano y en El Espacio Problemas Resueltos PDFGIOVANNI VIDAL MORALESAinda não há avaliações

- 1.2. EjerciciosDocumento5 páginas1.2. EjercicioscxbxzAinda não há avaliações

- La Integral de LineaDocumento19 páginasLa Integral de LineaKerlly Corsio SaldañaAinda não há avaliações

- Curvas de PersecuciónDocumento8 páginasCurvas de PersecuciónMilton NicolayAinda não há avaliações

- Problema 8 Cinematica 19-04-2021Documento7 páginasProblema 8 Cinematica 19-04-2021Martina MaldonadoAinda não há avaliações

- Cantidad de Movimiento Angular en Un Sistema de ParticulasDocumento7 páginasCantidad de Movimiento Angular en Un Sistema de ParticulasVidal RicanoAinda não há avaliações

- Matrices en Videojuegos 2Documento6 páginasMatrices en Videojuegos 2Papulo “Papulo”Ainda não há avaliações

- Curvatura y TorsionDocumento3 páginasCurvatura y TorsionAntony MitmaAinda não há avaliações

- Problemas Propuestos y Resueltos Cinematica Movimiento Circular 1 2Documento6 páginasProblemas Propuestos y Resueltos Cinematica Movimiento Circular 1 2Lucia Santos SaizAinda não há avaliações

- Curvas paramétricas y longitud de arcoDocumento19 páginasCurvas paramétricas y longitud de arcoedisonAinda não há avaliações

- Teorema de Stokes y Green: comparación entre sus formulacionesDocumento6 páginasTeorema de Stokes y Green: comparación entre sus formulacionesMilton Bojorque CampoverdeAinda não há avaliações

- Movimiento en El Plano y en El EspacioDocumento31 páginasMovimiento en El Plano y en El EspacioRichard Zerpa0% (1)

- Coordenadas Polares y CartesianasDocumento6 páginasCoordenadas Polares y CartesianasHeidel MoraAinda não há avaliações

- Práctica Domiciliaria 2 PDFDocumento5 páginasPráctica Domiciliaria 2 PDFSebastian AlarconAinda não há avaliações

- Hist ArteDocumento35 páginasHist ArtemiteratosAinda não há avaliações

- Reseña Lineas de SangreDocumento12 páginasReseña Lineas de SangremiteratosAinda não há avaliações

- Origami CP Robert LangDocumento28 páginasOrigami CP Robert Langmiteratos100% (1)

- VampirosDocumento10 páginasVampirosmiteratosAinda não há avaliações

- Embarazo adolescente en ChileDocumento54 páginasEmbarazo adolescente en ChileArelycannobbioAinda não há avaliações

- La Historia Entre SusurrosDocumento1 páginaLa Historia Entre SusurrosmiteratosAinda não há avaliações

- Pere Olivera-Tratamiento Del Papel PDFDocumento3 páginasPere Olivera-Tratamiento Del Papel PDFSka DragonAinda não há avaliações

- AnimalismoDocumento2 páginasAnimalismomiteratosAinda não há avaliações

- La Historia Entre SusurrosDocumento1 páginaLa Historia Entre SusurrosmiteratosAinda não há avaliações

- Python Reparando BugsDocumento4 páginasPython Reparando BugsmiteratosAinda não há avaliações

- Mujeres en Las Sombras - Un Estudio Sobre El Aborto en ChileDocumento31 páginasMujeres en Las Sombras - Un Estudio Sobre El Aborto en ChilePaulina Villalobos MontesinosAinda não há avaliações

- Dejar de FumarDocumento61 páginasDejar de FumarmiteratosAinda não há avaliações

- Ec DiferencialesDocumento83 páginasEc DiferencialesRafael SanabriaAinda não há avaliações

- Muertes y Definiciones TanatologiaDocumento38 páginasMuertes y Definiciones Tanatologiaapi-375516979% (14)

- Ritual Romano de Exorcismos PDFDocumento51 páginasRitual Romano de Exorcismos PDFMagdalena GarciaAinda não há avaliações

- Como Hackear Servidores Paso A PasoDocumento68 páginasComo Hackear Servidores Paso A PasoJulio Cesar85% (48)

- Post-Tarea Grupo 25Documento26 páginasPost-Tarea Grupo 25DEIBY DIAZAinda não há avaliações

- Tutorial de MultisimDocumento52 páginasTutorial de Multisimdabalejo100% (1)

- Identificación de La GuíaDocumento9 páginasIdentificación de La Guíajohn garciaAinda não há avaliações

- Conver de Cod BCD A 7 SegDocumento18 páginasConver de Cod BCD A 7 SegPedro LandaetaAinda não há avaliações

- VHDL - Práctica 1 (Tutorial Software)Documento24 páginasVHDL - Práctica 1 (Tutorial Software)LuisAinda não há avaliações

- Práctica #1. Introducción Al Entorno ISE® de Xilinx: 1. Datos de La PracticaDocumento15 páginasPráctica #1. Introducción Al Entorno ISE® de Xilinx: 1. Datos de La PracticaGiusseppe GuevaraAinda não há avaliações

- Informe Practica 2.2Documento9 páginasInforme Practica 2.2Oscar RodriguezAinda não há avaliações

- Circuitos CombinacionalesDocumento9 páginasCircuitos Combinacionalesoscar santosAinda não há avaliações

- Entregable2 Plantilla 2022Documento9 páginasEntregable2 Plantilla 2022Eduardo GonzalezAinda não há avaliações

- Lab5 2016 2 Digitales Melchor MatosDocumento10 páginasLab5 2016 2 Digitales Melchor MatosCheCarlitosAinda não há avaliações

- Display - Circuitos DigitalesDocumento17 páginasDisplay - Circuitos DigitalesFranklin Jancovick Varòn HuertasAinda não há avaliações

- Cuaderno Ejercicios DigitalesDocumento42 páginasCuaderno Ejercicios Digitalesgmoivan100% (16)

- Instrumentación Didactica de Diseño Digital Con VHDL 2016Documento16 páginasInstrumentación Didactica de Diseño Digital Con VHDL 2016Juan Jose Cruz JimenezAinda não há avaliações

- Proyecto Fundamentos de Diseño DigitalDocumento4 páginasProyecto Fundamentos de Diseño DigitalLenaAinda não há avaliações

- Deber Segundo Parcial Digitales IIDocumento16 páginasDeber Segundo Parcial Digitales IIAlex Fernando Coro LuzuriagaAinda não há avaliações

- Quartus Tutorial001Documento25 páginasQuartus Tutorial001Alfredo Martin Machacuay SiuceAinda não há avaliações

- Práctica No. 9 Código HammingDocumento11 páginasPráctica No. 9 Código HammingOscar MonroyAinda não há avaliações

- Investigación FPGADocumento4 páginasInvestigación FPGAJose Mariano EscuderoAinda não há avaliações

- ME Lab03 - Circuitos Lógicos SecuencialesDocumento19 páginasME Lab03 - Circuitos Lógicos SecuencialesAdrianSequeraAinda não há avaliações

- Prob DiversosDocumento14 páginasProb DiversosLeslie_g_mAinda não há avaliações

- Consulta #1Documento305 páginasConsulta #1Jazmin Rodriguez0% (1)

- Guia I - 2020Documento33 páginasGuia I - 2020Omar MarcaAinda não há avaliações

- Tarea 3 Grupo 243004 1 PDFDocumento85 páginasTarea 3 Grupo 243004 1 PDFjonathanAinda não há avaliações

- Problemas de Ruta de DatosDocumento31 páginasProblemas de Ruta de Datoswalter100% (1)

- Reporte Pract1 EmbebidosDocumento15 páginasReporte Pract1 Embebidosfedexin_40Ainda não há avaliações

- Tarea #1 DigitalDocumento6 páginasTarea #1 DigitalYaniel LeliebreAinda não há avaliações

- Sandoval DiseosUrbticaSostenibilidadDocumento14 páginasSandoval DiseosUrbticaSostenibilidadmariaAinda não há avaliações

- Lenguaje VHDL MICROELECTRONICADocumento28 páginasLenguaje VHDL MICROELECTRONICAWilliams Ortiz MartinezAinda não há avaliações

- Dispositivos Logicos Programables Unidad 1Documento30 páginasDispositivos Logicos Programables Unidad 1Uvaldo Torres MorenoAinda não há avaliações