Escolar Documentos

Profissional Documentos

Cultura Documentos

Curvas Características Del MOSFET de Vaciamiento

Enviado por

Noe Sanchez HernandezDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Curvas Características Del MOSFET de Vaciamiento

Enviado por

Noe Sanchez HernandezDireitos autorais:

Formatos disponíveis

Prctica No.

____________

Curvas caractersticas del MOSFET de vaciamiento canal n

Objetivos especficos: El alumno aprender a:

Obtener las curvas caractersticas de drenaje del MOSFET de vaciamiento

Obtener la grfica de la funcin de transferencia del MOSFET de vaciamiento.

INTRODUCCION TEORICA.

Anlisis de la operacin del transistor MOSFET de vaciamiento canal-n.

Los MOSFET son dispositivos de cuatro terminales llamados Source o fuente (S), Drain o denaje(D), Gate

o compuerta (G) y Sustrate o substrato (SS). Sin embargo, el substrato generalmente est conectado

internamente al terminal del fuente, y por este motivo se pueden disponer de dispositivos MOSFET de

tres terminales. La palabra MOSFET es acrnimo de Metal-Oxide-Semiconductor Field Effect Transistor

(significa en castellano transistor de efecto de campo).

Los MOSFETs se dividen en dos tipos: el de vaciamiento (o decrecimiento, agotamiento, etc.) y

crecimiento (o incremental). Los trminos vaciamiento o crecimiento se definen como consecuencia de

los modos de operacin, como ser explicado ms adelante.

La construccin bsica de un MOSFET del tipo vaciamiento canal n se esquematiza en las figuras 8.1 y 8.2.

Se forma a partir de una base de material de silicio monocristalino tipo p al se le denomina sustrato. El

sustrato es el cimiento sobre el que se construir el dispositivo resultando un dispositivo de cuatro

terminales, como el que aparece en la figura 8.1. Las terminales de fuente y drenaje estn unidas entre s

a travs de una regin de semiconductor tipo n mediante una zona denominada canal n como se muestra

en la misma figura. La compuerta se conecta a una superficie de contacto metlico, pero permanece

aislada del canal n por una capa muy delgada de

pero permanece aislada del canal n por una capa muy delgada de dixido de silicio. El SiO2 es un tipo

particular de aislante que no permite una conexin elctrica directa entre la terminal de compuerta y el

canal para el MOSFET; por esta razn, a estos dispositivos se les conoce tambin como IGFETs (insulatedgate field-effect-transistor, transistor de efecto de campo con compuerta aislada).

No existe conexin elctrica directa entre la terminal de la compuerta y el canal de un MOSFET

La resistencia de entrada de un MOSFET es mucho mayor que la del JFET tpico, an cuando la impedancia

de entrada de la mayora de los JFET sea lo suficientemente alta comparada a la impedancia de entrada

de los BJTs. De hecho, debido a esta muy alta impedancia de entrada, la corriente de compuerta IG es

esencialmente de cero amperes para las diferentes configuraciones de polarizacin en cd.

Proceso1 tecnolgico para la fabricacin del MOSFET.

Continuacin vamos a describir de forma esquemtica los pasos del proceso para fabricar un transistor

MOSFET de canal n con compuerta metlica.

Este proceso se lleva a cabo usando la tecnologa planar que se puede realizar mediante procesos de

crecimiento epitaxial2 de pelculas semiconductoras, crecimiento trmico de xidos, difusin de

impurezas, implantacin de iones, fotolitografia y deposicin3 de polisilicio de capas dielctricas y

metlicas.

Consiste en una serie de pasos ordenados rigurosamente para la trasferencia del diseo grfico de un

chip a una oblea de silicio monoltico.

2

Es un proceso por medio del cual se hace crecer una capa de material que mantiene una relacin definida con

respecto al substrato cristalino inferior. Por ejemplo, partir de una cara de un cristal de material semiconductor, o

sustrato, se hace crecer una capa uniforme y de poco espesor con la misma estructura cristalina que este.

3

Depositar.

2

ETAPAS DE FABRICACION DE UN MOSFET DE VACIAMIENTO

Etapa

Vista frontal de la oblea

Descripcin de la etapa

La oblea de partida, silicio monocristalino, tipo p.

Se crece la capa de dixido de silicio (SiO2) trmico.

Primer proceso fotolitogrfico para la abertura de una

ventana en lo que sern las reas activas (regiones de

drenaje, compuerta y fuente) por medio de fotolitografia.

Se aplican varias gotas de photorresist4 (PR) sobre la

oblea y se hace girar a altas rpm para distribuir la

sustancia uniformemente.

Despus del paso de girado, se lleva a la oblea a

horneado para eliminar solventes y mejorar la adhesin

de la pelcula del PR.

Se enmascara5 la oblea para proteger de luz UV las zonas

que sern removidas.

Luego se expone a la oblea a luz UV y la capa de PR no

cubierta por el enmascaramiento experimenta un cambio en

sus propiedades qumicas (indosubilidad) que se fijan por

medio de un proceso similarmente al revelado en fotografa

Luego se remueve la zona que no recibi la luz por

medio de una solucin.

Finalmente, la oblea es limpiada, secada y horneada

nuevamente tal que la PR pueda resistir el acido fuerte

para atacar la capa de dixido expuesta

Para atacar el SiO2 se usa acido HF debido a que no ataca al

silicio

6

Resina fotosensible es una material sensible a la luz utilizado en varios procesos industriales, tales como la

fotolitografa y fotograbado, para formar un recubrimiento modelado sobre una superficie.

5

Mscara. Placa con aberturas que se disea para producir un patrn de grabacin en la capa fotosensible.

3

Despus de atacar al SiO2 se quita el PR por medio de un

solvente (Acetona) o por oxidacin por plasma , dejando el

patrn de aislamiento que es el mismo que la imagen sobre

la mascara.

Proceso de difusin de impurezas donadoras se usan para

formar el drenaje, compuerta y fuente

Se crece una capa adicional de oxido trmico

10

Segundo proceso de fotolitografia para quitar el oxido que

definir la regin de compuerta.

Enmascaramiento

Exposicion a la luz UV

Revelado

11

Remocin del PR no expuesto

12

Remocin de la capa de dixido de silicio por medio de

ataque quimico.

13

Despus de atacar al SiO2

se quita el PR por medio de un solvente (Acetona)

14

Se crece una delgada capa de dixido de silicio

15

Se inicia el tercer proceso de fotolitografia para remover el

oxido, definir ranuras de contactos para la fuente y drenaje.

16

definicin de los contactos de fuente

y drenaje.

17

Remover la capa PR

18

Se deposita aluminio evaporado sobre toda la superficie

bajo condiciones de alto vacio.

19

Se hace el proceso final de fotolitografia para remove la

capa de aluminio para definir el patrn de contactos.

20

Definicin exacta de contactos en puerta,

fuente y drenador

21

Definicin exacta de contactos en puerta,

fuente y drenador

22

Fabricacin del dispositivo MOSFET completada.

OPERACIN BSICA Y CARACTERSTICAS.

Respuesta de la corriente de drenaje ID con respecto a la variacin del voltaje

VDS, considerando la compuerta a tierra (VGS = 0 ).

I)

La diferencia de potencial entre compuerta y fuente de la figura 8.3 es cero volts (VGS = 0 ) al estar

conectadas en comn con la terminal del sustrato y la conexin de tierra. Por el lado del circuito de

drenaje se le est aplicando al transistor un voltaje VDD a travs de las terminales drenaje-fuente (VDS). El

resultado es que los electrones libres del canal n son arrastrados por esta diferencia de potencial VDS y

formaran la corriente ID similar a la establecida a travs del canal del JFET. En la figura 8.4 se muestra en la

curva caracterstica del funcionamiento del MOSFET de vaciamiento, es decir, la variacin de la corriente

resultante ID con respecto a la variacin de VDS. Se puede apreciar que la corriente ID aumenta conforme

el voltaje VDS aumenta (aumentando VDD). Ver Figura 8.3 (b).

Este comportamiento proporcional se mantendr a cierto valor donde VDS = VP (este valor de voltaje

provoca el estrangulamiento del canal). A partir de este valor, los incrementos del voltaje VDS no producen

mayor incremento de la corriente ID . El comportamiento constante del valor de ID se le llama corriente

de saturacin IDSS .

Figura 8.3 (b)

PROCEDIMIENTO EXPERIMENTAL SIMULADO I).

a) Armar el siguiente circuito.

b) Medir el voltaje VDS y la corriente ID, mientras se incrementa el valor de la fuente VDD desde 0 hasta 20

volts, manteniendo el voltaje VGS = 0 V. Anotar sus resultados en la siguiente tabla

c) Con los valores de la tabla anterior, realice la grfica de ID vs VDS.

d) Analice y comente con los integrantes del equipo, los resultados. Escriba sus conclusiones.

II) Respuesta de la corriente de drenaje ID con respecto a la variacin del voltaje

VGS, considerando VDS = a un valor constante.

Independientemente del efecto que provoca el voltaje VDS sobre la resistividad del canal (y su repercusin

en la corriente ID), por medio del aumento de la zona de vaciamiento, ahora se estudiar el efecto del

voltaje sobre la misma corriente. En la figura 8.5, VGS tiene un potencial negativo, tal como 1 V. El

potencial negativo en la compuerta producir un campo elctrico en direccin substrato-compuerta, tal

que arrastrar a los electrones libres (portadores mayoritarios en el canal n) hacia el sustrato tipo p y

atraer a los huecos del sustrato tipo p. Dependiendo del valor de la polarizacin negativa establecida por

VGS, ocurrir la recombinacin entre electrones y huecos que reducir el nmero de electrones libres

disponibles para la conduccin en el canal n. Mientras ms negativa sea la polarizacin, mayor ser la

velocidad de la recombinacin. Por consiguiente el valor de la corriente de drenaje ID se reduce con el

incremento en la polarizacin negativa para VGS como se muestra en la figura 8.5 para VGS = -1 V, -2 V, y as

sucesivamente, hasta el nivel de estrechamiento de -4 V. Los niveles resultantes de la corriente de

drenaje y la grfica de la curva de transferencia se comportan exactamente de la misma forma que para

el JFET.

La figura 6.31 muestra la curva obtendra al hacer el experimento de un MOSFET de vaciamiento.

Al igual que en el caso del JFET, bajo las condiciones experimentales W. Shockley dedujo la ecuacin que

define la relacin entre ID y VGS en un MOSFET de vaciamiento, la cual en honor a l se llama Ec. De

Shockley:

V

ID IDSS 1 GS

VP

10

PROCEDIMIENTO EXPERIMENTAL SIMULADO II).

a) Armar el siguiente circuito.

b) Medir el voltaje VDS y la corriente ID, mientras se incrementa el valor de la fuente VDD

desde 0 hasta 20 volts, manteniendo el voltaje VGS = - 3 V. Anotar sus resultados en la siguiente

tabla:

11

c) Con los valores de la tabla anterior, realice la grfica de ID vs VDS

d) Analice y comente con los integrantes del equipo, los resultados. Escriba sus conclusiones.

12

Você também pode gostar

- CAPITULO 4 El MOSFETDocumento7 páginasCAPITULO 4 El MOSFETIan García0% (1)

- Trabajo de Investigacion - MOSFETDocumento15 páginasTrabajo de Investigacion - MOSFETErick ArmasAinda não há avaliações

- Fabricación de FETs en tecnología microelectrónicaDocumento8 páginasFabricación de FETs en tecnología microelectrónicaAlex EdUu NúñezAinda não há avaliações

- Inversor CMOSDocumento10 páginasInversor CMOSCarlosMauricioMuñozRodasAinda não há avaliações

- Caracterización MOSFET y JFETDocumento20 páginasCaracterización MOSFET y JFETAntonio Cárdenas GuzmánAinda não há avaliações

- 5to LaboratorioDocumento11 páginas5to LaboratoriokarenAinda não há avaliações

- Tema4 El MosfetDocumento25 páginasTema4 El MosfetRaul EsparzaAinda não há avaliações

- MOSFET de EmpobrecimientoDocumento8 páginasMOSFET de EmpobrecimientoDaNiilel Polanco PerezAinda não há avaliações

- 8 Transistores de Efecto CampoDocumento44 páginas8 Transistores de Efecto CampoMarcelo OlivaresAinda não há avaliações

- FET y MOSFET: tipos, regiones de trabajo y curvas característicasDocumento33 páginasFET y MOSFET: tipos, regiones de trabajo y curvas característicasJohana Lagla100% (2)

- JFETDocumento12 páginasJFETOscar A. Santamaría VallejoAinda não há avaliações

- Circuitos ElectricosDocumento5 páginasCircuitos ElectricosNahum olaf Soto GodinezAinda não há avaliações

- Introducción Al MosfetDocumento8 páginasIntroducción Al MosfetAndres Zapata HAinda não há avaliações

- Proceso de Fabricación Del BJT y MOSDocumento7 páginasProceso de Fabricación Del BJT y MOSAlber Lim GboAinda não há avaliações

- Trabajo Sobre FETDocumento9 páginasTrabajo Sobre FETever5iba5ezAinda não há avaliações

- Seguidor de Corriente Con MosfetDocumento9 páginasSeguidor de Corriente Con MosfetgreomerAinda não há avaliações

- Mosfet Canal Tipo NDocumento10 páginasMosfet Canal Tipo NklauxixAinda não há avaliações

- Consolidado Laboratorios Electronica de Potencia 1 - 2 - 3 - Alexis Pedroza - G16Documento30 páginasConsolidado Laboratorios Electronica de Potencia 1 - 2 - 3 - Alexis Pedroza - G16alexis pedrozaAinda não há avaliações

- Transistor Mos o MosfetDocumento19 páginasTransistor Mos o MosfetLuis Cabrera PalaciosAinda não há avaliações

- El Transistor MOSFET - Electrónica Práctica Aplicada - PDF ImprimirDocumento17 páginasEl Transistor MOSFET - Electrónica Práctica Aplicada - PDF ImprimirUnkwAinda não há avaliações

- Lab Analogicaii 1Documento12 páginasLab Analogicaii 1Tania TorresAinda não há avaliações

- Informe MosfetDocumento9 páginasInforme MosfetCarlos Luis VargasAinda não há avaliações

- Circuito Unipolar PDFDocumento21 páginasCircuito Unipolar PDFHector CaryAinda não há avaliações

- Tema 6 - Transistores UnipolaresDocumento21 páginasTema 6 - Transistores UnipolaresDavid Ariza BetancurAinda não há avaliações

- El Transistor MOSFETDocumento27 páginasEl Transistor MOSFETPaul Ivan Napa OreAinda não há avaliações

- Transistor de Efecto de CampoDocumento51 páginasTransistor de Efecto de CampoMaria Alejandra Cardozo GuzmanAinda não há avaliações

- Prac7 El Transistor de Efecto de CampoDocumento7 páginasPrac7 El Transistor de Efecto de CampoKlinsman AráozAinda não há avaliações

- MosfetDocumento22 páginasMosfetMichael MartinezAinda não há avaliações

- El Transistor MosfetDocumento19 páginasEl Transistor MosfetLuis Cabrera PalaciosAinda não há avaliações

- Circuitos Electronicos 2 MosfetDocumento12 páginasCircuitos Electronicos 2 MosfetAlex OreAinda não há avaliações

- FET InacapDocumento16 páginasFET InacaplizandroAinda não há avaliações

- Transistores FET PDFDocumento12 páginasTransistores FET PDFCarlos Tamay Crespo50% (2)

- Corto Canal DispositivosDocumento13 páginasCorto Canal DispositivoszaddlerAinda não há avaliações

- Generalidades de Los Transistores MosfetDocumento4 páginasGeneralidades de Los Transistores MosfetVICTOR MANUEL RODRIGUEZ USECHEAinda não há avaliações

- El Transistor Mosfet de EmpobrecimientoDocumento2 páginasEl Transistor Mosfet de EmpobrecimientoCarlos E MachucaAinda não há avaliações

- Parcial - Julian Felipe Barrera BustosDocumento5 páginasParcial - Julian Felipe Barrera BustosJULIAN FELIPE BARRERA BUSTOSAinda não há avaliações

- Trans Compuerta Aislada.Documento106 páginasTrans Compuerta Aislada.Julio C. Canchano ParodyAinda não há avaliações

- Investigacion MosfetDocumento9 páginasInvestigacion MosfetArturo DíazAinda não há avaliações

- MOSFET BásicoDocumento21 páginasMOSFET BásicoJosé Isai Campos JuarezAinda não há avaliações

- TE1314 Apuntes Tema4 PDFDocumento24 páginasTE1314 Apuntes Tema4 PDFCourtney MontoyaAinda não há avaliações

- Canal N y PDocumento24 páginasCanal N y PJovaany GaarciiaaAinda não há avaliações

- MOSFET-transistor-efecto-campoDocumento21 páginasMOSFET-transistor-efecto-campoleonardo100% (1)

- Estructura y operación MOSFETDocumento14 páginasEstructura y operación MOSFETAntonio MontoyaAinda não há avaliações

- Amplificadores MOSFET laboratorio electrónicaDocumento8 páginasAmplificadores MOSFET laboratorio electrónicaverominajvAinda não há avaliações

- Electronica MosfetDocumento14 páginasElectronica MosfetFanny ChamorroAinda não há avaliações

- Tecnica e Fabricacion CMOSDocumento6 páginasTecnica e Fabricacion CMOSJuan CandanedoAinda não há avaliações

- Capitulo 7 - Transistores MOSDocumento28 páginasCapitulo 7 - Transistores MOSgeorgeAinda não há avaliações

- MJR - PM 16430388 Electronica de Potencia 1.2.2-1.4Documento23 páginasMJR - PM 16430388 Electronica de Potencia 1.2.2-1.4MarcosAinda não há avaliações

- Lab 12 Transistor MOSFET PDFDocumento59 páginasLab 12 Transistor MOSFET PDFEnder Thiago Montoya MendozaAinda não há avaliações

- Practica 6 - El Transistior de Efecto de CampoDocumento9 páginasPractica 6 - El Transistior de Efecto de CampoLilith DarkAinda não há avaliações

- Construcción y Características de Los JFETDocumento13 páginasConstrucción y Características de Los JFETBryan OcampoAinda não há avaliações

- INVESTIGACIÓN SOBRE TRANSISTORES DE CONMUTACIÓNDocumento37 páginasINVESTIGACIÓN SOBRE TRANSISTORES DE CONMUTACIÓNSebastian SartaAinda não há avaliações

- S13 S1-MaterialDocumento35 páginasS13 S1-MaterialChristian GuillmarAinda não há avaliações

- El Transistor MOSFETDocumento19 páginasEl Transistor MOSFETRonald DarisAinda não há avaliações

- Transistor unipolar FETDocumento36 páginasTransistor unipolar FETTomas CaicedoAinda não há avaliações

- Informe 6Documento8 páginasInforme 6Camilo SarmientoAinda não há avaliações

- Cap7 MosfetDocumento51 páginasCap7 MosfetAldo SalazarAinda não há avaliações

- Arrancadores para motores trifásicosDocumento10 páginasArrancadores para motores trifásicosNoe Sanchez HernandezAinda não há avaliações

- 2 Taller de Etica-CrisDocumento83 páginas2 Taller de Etica-CrisNoe Sanchez HernandezAinda não há avaliações

- Perfil ProfesionalDocumento8 páginasPerfil ProfesionalNoe Sanchez HernandezAinda não há avaliações

- Practicas Con Arduino Nivel IDocumento73 páginasPracticas Con Arduino Nivel Ialvaronevi100% (6)

- Suma Resta Multiplicacion de 2 MatricesDocumento6 páginasSuma Resta Multiplicacion de 2 MatricesNoe Sanchez HernandezAinda não há avaliações

- Jaula DE ORO: MeieffDocumento15 páginasJaula DE ORO: MeieffisqvuuAinda não há avaliações

- Texto Biotipos y Razas Bovinas - 2011Documento28 páginasTexto Biotipos y Razas Bovinas - 2011M Cecilia AmatoAinda não há avaliações

- Coeducación y perspectiva de géneroDocumento2 páginasCoeducación y perspectiva de génerodianaAinda não há avaliações

- Problemas sistemas cerrados: presión, calor y energía disponible en mezcla de gasesDocumento6 páginasProblemas sistemas cerrados: presión, calor y energía disponible en mezcla de gasesJuanAinda não há avaliações

- Vortices EnergeticosDocumento11 páginasVortices EnergeticosClaudio Rondan ChaconAinda não há avaliações

- Presentacion Dragado CRP V2 - DEFINITIVO-1Documento9 páginasPresentacion Dragado CRP V2 - DEFINITIVO-1Simon FuenmayorAinda não há avaliações

- El InconsienteDocumento8 páginasEl InconsienteABIGAIL HAZEL BAUTISTA TREJOAinda não há avaliações

- Introducción a la higiene y seguridad industrialDocumento127 páginasIntroducción a la higiene y seguridad industrialJulio Ortega RevillaAinda não há avaliações

- Humanidad IntraterrenaDocumento78 páginasHumanidad Intraterrenajavier8860Ainda não há avaliações

- Plan de CapacitacionDocumento10 páginasPlan de CapacitacionStanh IchAinda não há avaliações

- IndustrialDocumento9 páginasIndustrialEnzo ArrascoAinda não há avaliações

- Aplicación de Ciencia, Tecnología e Innovación para Mejorar El Proceso Productivo de La Mora en El Departamento de SantanderDocumento120 páginasAplicación de Ciencia, Tecnología e Innovación para Mejorar El Proceso Productivo de La Mora en El Departamento de SantanderJulian Andres Tovar MedinaAinda não há avaliações

- PreguntasDocumento5 páginasPreguntasRuben CastilloAinda não há avaliações

- Ejemplos de Rendimiento de Materiales (C)Documento8 páginasEjemplos de Rendimiento de Materiales (C)Estrella RufoAinda não há avaliações

- CG-Sem13-Ejercicios Estequiometría 2Documento3 páginasCG-Sem13-Ejercicios Estequiometría 2BetoCoronelVallejos50% (2)

- Larv Roadway 20 - 70wDocumento3 páginasLarv Roadway 20 - 70wAlicia AltamiranoAinda não há avaliações

- Binipatia y TrofologiaDocumento4 páginasBinipatia y TrofologiaJulio Antonio Muñoz LopezAinda não há avaliações

- Ejercicios - García GarciaDocumento9 páginasEjercicios - García GarciaRonald LlerenaAinda não há avaliações

- Williams y Mckenzie HerniaDocumento7 páginasWilliams y Mckenzie HerniaJohanna Beltran GaonaAinda não há avaliações

- Restauración Plantas MedicinalesDocumento260 páginasRestauración Plantas MedicinalesONG CETSUR100% (8)

- 1.2 Aplicaciones de Las EcuacionesDocumento17 páginas1.2 Aplicaciones de Las EcuacionesManuel Estuardo MoralesAinda não há avaliações

- Aplicando Lo Aprendido3 2° Básico CienciasDocumento6 páginasAplicando Lo Aprendido3 2° Básico CienciasEsc Chapod MaquehueAinda não há avaliações

- ProyectoDocumento78 páginasProyectoguamuchilsinAinda não há avaliações

- Sofista y AtomistaDocumento4 páginasSofista y Atomistaxstr100% (1)

- Ensayo Historia de La PsicopatologiaDocumento4 páginasEnsayo Historia de La PsicopatologiaErin ThompsonAinda não há avaliações

- Informe Julio Santos FloresDocumento70 páginasInforme Julio Santos FloresLeonel Rea NavarroAinda não há avaliações

- Los-Que-Nos-Salvaron-Jenna-Blum PDFDocumento303 páginasLos-Que-Nos-Salvaron-Jenna-Blum PDFalgarrobina19660% (1)

- Ejemplo de Negocio en MarchaDocumento10 páginasEjemplo de Negocio en MarchaJami Santiiago0% (1)

- Taller de Probabilidades AlumnosDocumento9 páginasTaller de Probabilidades AlumnosMISOL GALLEGUILLOS CALLEJASAinda não há avaliações

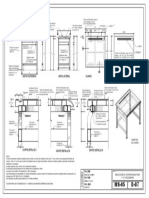

- Me - MS-05 Mesa Metal Polipropileno de 1-2 SecundariaDocumento1 páginaMe - MS-05 Mesa Metal Polipropileno de 1-2 SecundariaLuis Angel Solis AyoraAinda não há avaliações