Escolar Documentos

Profissional Documentos

Cultura Documentos

Fts 2007

Enviado por

andhracollegesDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Fts 2007

Enviado por

andhracollegesDireitos autorais:

Formatos disponíveis

www.andhracolleges.

com The Complete Information About Colleges in Andhra Pradesh

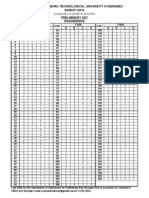

Code No: RR410506 Set No. 1

IV B.Tech I Semester Supplementary Examinations, February 2007

FAULT TOLERANT SYSTEMS

( Common to Computer Science & Engineering and Electronics &

Computer Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) How does a feedback briding fault leads the circuit into oscillation. What are

the conditions? [4+4]

(b) What are temporary faults? Differentiate between Transient faults and inter-

mittent faults. Which one is preferrable? [3+2+2+1]

2. (a) A circuit realizes the function.

Z=X1 X4 +X2 X3 +X1 X4

Using Boolean Difference method find the test vectors for SA0, SA1 faults on

all input lines of the circuit.

(b) What are the different properties of Boolean differences? Explain [5+5+6]

3. (a) Construct a seven-bit error correcting code to represent the decimal digit by

augmenting the Excess-3 code and by using add-1 parity check.

(b) Design a redundant circuit for f = a ⊕ b [9+7]

4. (a) What is the mechanism adopted in COPRA a fault Tolerant system. Explain

in detail.

(b) What is meant by Time redundancy? Explain. [4+4+4+4]

www.andhracolleges.com

5. (a) What is the need for self checking circuits

(b) Design a totally self checking checker by using reddy’s partition method for

2out of 5 code. [6+10]

6. Explain in detail about fail-safe sequential circuits design with an example. [16]

7. Write a short notes an [4x4=16]

(a) Controllability

(b) Observability

(c) Positive unate function

(d) Syndrom relations of all types of terminating gates.

8. (a) Discuss the sequential circuit design using nonscan techniques.

(b) i. What is meant by Enhanced controllability?

ii. How is a sequential circuit modified for the above sequential circuit and

enhanced controllability? [6+4+6]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

1 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

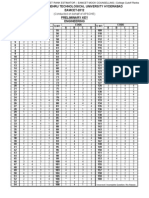

Code No: RR410506 Set No. 2

IV B.Tech I Semester Supplementary Examinations, February 2007

FAULT TOLERANT SYSTEMS

( Common to Computer Science & Engineering and Electronics &

Computer Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Distinguish between failures, and faults Explain [2+2]

(b) Explain the different modeling schemes of faults that generally come across in

digital circuits. [3x2=6]

(c) Explain the following terms with respect to digital circuits with suitable ex-

amples.

i. Fault diagnosis.

ii. Fault detection test set.

iii. Test vector generation. [3x2=6]

2. (a) Distinguish between fault detection and fault location [2+2]

(b) Illustrate the principles involved in fault table method of test generation using

the figure1 given below.Verify the above test vector, generated, with the help

of D-algorithm for C SAO fault. [12]

www.andhracolleges.com

so that it becomes hazard free?

Figure 1:

3. (a) Analyze the circuit shown in fig2 below for static hazards. Redesign the circuit

(b) Explain the concept of sift out modular redundancy scheme.

[4+4]

[8]

4. With an example explain :

(a) software redundancy.

(b) time redundancy. [8+8]

5. (a) What is the need for self checking circuits

(b) Design a totally self checking checker by using reddy’s partition method for

2out of 5 code. [6+10]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR410506 Set No. 2

www.andhracolleges.com Figure 2:

6. Explain in detail about fail-safe sequential circuits design with an example.

7. Explain the technique for designing minimally testable network which produces a

circuit which can be tested by three tests only.Modify the function f = A BC +A

B C into a circuit which has only three tests. [10+6]

8. (a) Draw the logic diagram of Hazard-free polarity hold latch, and explain with

[16]

the help of flow table & excitation table. [2+2+2]

(b) Draw the logic diagram of shift register latch and explain its principle. Using

above latch. [3+7]

⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR410506 Set No. 3

IV B.Tech I Semester Supplementary Examinations, February 2007

FAULT TOLERANT SYSTEMS

( Common to Computer Science & Engineering and Electronics &

Computer Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. Define and derive the following terms in a system.

(a) MTTR [2+6]

(b) Hazard rate functions. [2+6]

2. (a) What is a tree like circuit. Give properties of tree like circuits.

(b) For the given tree like circuit find the complete test set using path sensitizing

method as show in figure1. [3+5+8]

www.andhracolleges.com

3. (a) Explain fail soft-operation.

Figure 1:

(b) Explain the 5 MR reconfiguration mechanism and also explain how it care

tolerate single, double and Trible faults in a given system.

4. With an example explain :

(a) software redundancy.

[3x4=12]

[4]

(b) time redundancy. [8+8]

5. (a) What is the need for self checking circuits

(b) Design a totally self checking checker by using reddy’s partition method for

2out of 5 code. [6+10]

6. Explain in detail about fail-safe sequential circuits design with an example. [16]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR410506 Set No. 3

7. (a) Prove that five tests are sufficient to detect all faults in a combinational logic

circuit by inserting addition control logic to the following function, obtain the

test pattern.

f=(A,B,C,D)=AB+BC+BD

(b) Obtain the ten sequences denoted as P = {xo x1 ......xa } from the basic module

of the above circuit and get the compatable pair from the set P. [8+8]

www.andhracolleges.com

8. (a) Draw the logic diagram of Built-in Logic Block Observer.

(b) Discuss BILBO based BIST architecture. [8+8]

⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR410506 Set No. 4

IV B.Tech I Semester Supplementary Examinations, February 2007

FAULT TOLERANT SYSTEMS

( Common to Computer Science & Engineering and Electronics &

Computer Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Distinguish between failures, and faults Explain [2+2]

(b) Explain the different modeling schemes of faults that generally come across in

digital circuits. [3x2=6]

(c) Explain the following terms with respect to digital circuits with suitable ex-

amples.

i. Fault diagnosis.

ii. Fault detection test set.

iii. Test vector generation. [3x2=6]

2. (a) What are the goals of Design for testability?

(b) Distinguish between ditermenistic test pattern generation and probabilitstic

test pattern generation methods. [6+5+5]

3. (a) With an example explain sift out modular redundancy technique.

(b) With an example explain self-purging redundancy. [8+8]

www.andhracolleges.com

4. (a) What is the goal of “pluibus” system used in ARPA network. Explain its

working.

(b) What is ment by fail soft operation? What should a system have to achieve

the capability of fail soft operation. [4+4+4+4]

5. Design a totally

(a) self-checking circuit for m out of n codes by translating the code to 1 out of 2.

(b) Verify it for 3 out of 5 code. [8+8]

6. (a) Explain the design consideration of self checking PLA considering stray faults

with suitable example.

(b) How do you implement strong fault service for the functional PLA. [8+8]

7. (a) Prove that five tests are sufficient to detect all faults in a combinational logic

circuit by inserting addition control logic to the following function, obtain the

test pattern.

f=(A,B,C,D)=AB+BC+BD

(b) Obtain the ten sequences denoted as P = {xo x1 ......xa } from the basic module

of the above circuit and get the compatable pair from the set P. [8+8]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR410506 Set No. 4

8. Explain observability enhancement with neat diagram with suitable examples. [4+2+10]

⋆⋆⋆⋆⋆

www.andhracolleges.com

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

Você também pode gostar

- Moving Average and Exponential Smoothing ModelsDocumento13 páginasMoving Average and Exponential Smoothing ModelsP Singh KarkiAinda não há avaliações

- Manual CI KNX - KNX CrestronDocumento34 páginasManual CI KNX - KNX Crestronsdiazruiz100% (1)

- Visual Basic 6.0Documento164 páginasVisual Basic 6.0victoriajude100% (1)

- Drones in VDC FV5Documento15 páginasDrones in VDC FV5Imam Buchairi100% (1)

- Landmark - Drilling and Completions Portfolio PDFDocumento1 páginaLandmark - Drilling and Completions Portfolio PDFAnonymous VNu3ODGavAinda não há avaliações

- Mobile Edge Artificial Intelligence: Opportunities and ChallengesNo EverandMobile Edge Artificial Intelligence: Opportunities and ChallengesAinda não há avaliações

- 06rr410506 Fault Tolerant SystemsDocumento7 páginas06rr410506 Fault Tolerant SystemsandhracollegesAinda não há avaliações

- Set No. 1: Min Max Wmin Max Vmax Vmax Vmin VmaxDocumento5 páginasSet No. 1: Min Max Wmin Max Vmax Vmax Vmin VmaxandhracollegesAinda não há avaliações

- JNTU Old Question Papers 2007Documento8 páginasJNTU Old Question Papers 2007Srinivasa Rao GAinda não há avaliações

- Set No. 1Documento5 páginasSet No. 1andhracollegesAinda não há avaliações

- r07220205 Control SystemsDocumento9 páginasr07220205 Control SystemsandhracollegesAinda não há avaliações

- Co 2007Documento4 páginasCo 2007andhracollegesAinda não há avaliações

- NSC 2007Documento5 páginasNSC 2007andhracollegesAinda não há avaliações

- DicaDocumento8 páginasDicaandhracollegesAinda não há avaliações

- 08 r05310502 Object Oriented Analysis and DesignDocumento7 páginas08 r05310502 Object Oriented Analysis and DesignandhracollegesAinda não há avaliações

- Rr410506 Fault Tolerant SystemsDocumento8 páginasRr410506 Fault Tolerant Systemsdayas1979Ainda não há avaliações

- 08rr410404 Optical CommunicationDocumento8 páginas08rr410404 Optical CommunicationandhracollegesAinda não há avaliações

- Nov07 Pulse Digital CircuitsDocumento9 páginasNov07 Pulse Digital CircuitsandhracollegesAinda não há avaliações

- r05220205 Control SystemsDocumento9 páginasr05220205 Control SystemsandhracollegesAinda não há avaliações

- Sr05220205 Control SystemsDocumento8 páginasSr05220205 Control SystemsandhracollegesAinda não há avaliações

- Java 2006Documento5 páginasJava 2006andhracollegesAinda não há avaliações

- Set No. 1Documento6 páginasSet No. 1andhracollegesAinda não há avaliações

- Aca 2005Documento5 páginasAca 2005andhracollegesAinda não há avaliações

- Uml 2006Documento8 páginasUml 2006andhracollegesAinda não há avaliações

- 06N - RR410302 Cad CamDocumento4 páginas06N - RR410302 Cad CamandhracollegesAinda não há avaliações

- r05410408 Digital Image ProcessingDocumento5 páginasr05410408 Digital Image ProcessingandhracollegesAinda não há avaliações

- 07N - RR410302 Cad CamDocumento6 páginas07N - RR410302 Cad CamandhracollegesAinda não há avaliações

- Ads 2007Documento4 páginasAds 2007andhracollegesAinda não há avaliações

- Rr410203 Computer Methods in Power SystemsDocumento9 páginasRr410203 Computer Methods in Power SystemsandhracollegesAinda não há avaliações

- Rr720507 Neural NetworksDocumento5 páginasRr720507 Neural NetworksandhracollegesAinda não há avaliações

- Rr720303 MicroprocessorsDocumento8 páginasRr720303 MicroprocessorsandhracollegesAinda não há avaliações

- MechatronicsDocumento4 páginasMechatronicsandhracollegesAinda não há avaliações

- r05220503 Principles of CommunicationsDocumento7 páginasr05220503 Principles of CommunicationsandhracollegesAinda não há avaliações

- MM 2006Documento8 páginasMM 2006andhracollegesAinda não há avaliações

- C&dsDocumento4 páginasC&dsandhracollegesAinda não há avaliações

- 08 r05310404 Digital CommunicationDocumento8 páginas08 r05310404 Digital CommunicationandhracollegesAinda não há avaliações

- 08RR410302 Cad CamDocumento5 páginas08RR410302 Cad CamandhracollegesAinda não há avaliações

- Uml M 2006Documento8 páginasUml M 2006andhracollegesAinda não há avaliações

- Examination Paper: May/June 2020 COMP2211-WE01Documento6 páginasExamination Paper: May/June 2020 COMP2211-WE01africa threeAinda não há avaliações

- Neural Networks and Fuzzy Logic PDFDocumento9 páginasNeural Networks and Fuzzy Logic PDFbadamsmithAinda não há avaliações

- TC 2006Documento10 páginasTC 2006andhracollegesAinda não há avaliações

- Dmadwh 2007Documento5 páginasDmadwh 2007andhracollegesAinda não há avaliações

- Summer 2021 AMIIW Question PapersDocumento32 páginasSummer 2021 AMIIW Question PapersRiyaz AhmedAinda não há avaliações

- Dmadwh 2006Documento7 páginasDmadwh 2006andhracollegesAinda não há avaliações

- r05410409 Satellite CommunicationsDocumento5 páginasr05410409 Satellite CommunicationsandhracollegesAinda não há avaliações

- NcseDocumento5 páginasNcseandhracollegesAinda não há avaliações

- Set No. 1Documento7 páginasSet No. 1andhracollegesAinda não há avaliações

- VLSIDesignDocumento5 páginasVLSIDesignVenkatesh KolatiAinda não há avaliações

- LP 2005Documento8 páginasLP 2005andhracollegesAinda não há avaliações

- Ds 2006Documento4 páginasDs 2006andhracollegesAinda não há avaliações

- Srr320404 Microwave EngineeringDocumento7 páginasSrr320404 Microwave EngineeringandhracollegesAinda não há avaliações

- Rr420402 Radar EngineeringDocumento4 páginasRr420402 Radar EngineeringandhracollegesAinda não há avaliações

- Examination Paper: May/June 201 9 COMP2211-WE01Documento6 páginasExamination Paper: May/June 201 9 COMP2211-WE01africa threeAinda não há avaliações

- Sjr05010201 Applied PhysicsDocumento8 páginasSjr05010201 Applied PhysicsandhracollegesAinda não há avaliações

- Ece361 - Ee 2010 S1Documento5 páginasEce361 - Ee 2010 S1Mu'izz KaharAinda não há avaliações

- r07320204 InstrumentationDocumento6 páginasr07320204 InstrumentationandhracollegesAinda não há avaliações

- March2006 Network Security and CryptographyDocumento5 páginasMarch2006 Network Security and CryptographyKeerthi ReddyAinda não há avaliações

- r05310201 Computer IonDocumento5 páginasr05310201 Computer IonskssushAinda não há avaliações

- R05320506-SOFTWARE-TESTING-METHODOLOGIES May 2008Documento5 páginasR05320506-SOFTWARE-TESTING-METHODOLOGIES May 2008api-19718334Ainda não há avaliações

- Btech Cse 4 Sem Advance Computer Architecture 2012Documento7 páginasBtech Cse 4 Sem Advance Computer Architecture 2012souravnaskar12578954Ainda não há avaliações

- Rr720505 RoboticsDocumento7 páginasRr720505 RoboticsandhracollegesAinda não há avaliações

- Vidyasagar University: B.Sc. Honours Examinations 2021 Semester - III Subject: Computer Science Question PaperDocumento4 páginasVidyasagar University: B.Sc. Honours Examinations 2021 Semester - III Subject: Computer Science Question Paperenabarunmondal2004Ainda não há avaliações

- Switching Theory and Logic Design - June-2015Documento55 páginasSwitching Theory and Logic Design - June-2015Rama HarithaAinda não há avaliações

- JEE Main Advanced 2014 Paper I Maths Paper Answer SolutionsDocumento4 páginasJEE Main Advanced 2014 Paper I Maths Paper Answer Solutionsandhracolleges100% (1)

- Eamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 CutoffsDocumento3 páginasEamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 Cutoffsandhracolleges33% (3)

- Polycet 2014 SC BC Oc Certificatates Verification DatesDocumento1 páginaPolycet 2014 SC BC Oc Certificatates Verification DatesandhracollegesAinda não há avaliações

- Polycet 2014 ST Certificatates Verification DatesDocumento1 páginaPolycet 2014 ST Certificatates Verification DatesandhracollegesAinda não há avaliações

- ICET 2014 Preliminary Key Primary Key AndhracollegesDocumento2 páginasICET 2014 Preliminary Key Primary Key AndhracollegesandhracollegesAinda não há avaliações

- Polycet2014 Web Counselling NotificationDocumento2 páginasPolycet2014 Web Counselling NotificationandhracollegesAinda não há avaliações

- Eamcet 2014 Engineering Key Solutions AndhracollegesDocumento42 páginasEamcet 2014 Engineering Key Solutions Andhracollegesandhracolleges75% (8)

- JEE Advanced 2014 Paper I Chemistry Paper Answer SolutionsDocumento4 páginasJEE Advanced 2014 Paper I Chemistry Paper Answer SolutionsandhracollegesAinda não há avaliações

- JEE Main Advanced Paper I Answer Key 25 May 2014Documento1 páginaJEE Main Advanced Paper I Answer Key 25 May 2014andhracollegesAinda não há avaliações

- Eamcet 2014 Engineering Jntu Preliminary Key AndhracollegesDocumento1 páginaEamcet 2014 Engineering Jntu Preliminary Key AndhracollegesandhracollegesAinda não há avaliações

- EAMCET 2014 Agriculture & Medical Preliminary Answer KeysDocumento1 páginaEAMCET 2014 Agriculture & Medical Preliminary Answer KeysLohith_EnggAinda não há avaliações

- Eamcet 2010 Medical PaperDocumento63 páginasEamcet 2010 Medical PaperandhracollegesAinda não há avaliações

- JEE Advanced 2014 Paper I PHYSICS Paper Answer SolutionsDocumento6 páginasJEE Advanced 2014 Paper I PHYSICS Paper Answer SolutionsandhracollegesAinda não há avaliações

- Eamcet 2014 Medical Question Paper With Key Solutions AndhracollegesDocumento62 páginasEamcet 2014 Medical Question Paper With Key Solutions Andhracollegesandhracolleges100% (1)

- Eamcet 2012 Medical PaperDocumento60 páginasEamcet 2012 Medical Paperandhracolleges100% (1)

- Eamcet 2014 Engineering Key SolutionsDocumento42 páginasEamcet 2014 Engineering Key Solutionsandhracolleges100% (1)

- Eamcet 2014 Medical Question Paper AndhracollegesDocumento62 páginasEamcet 2014 Medical Question Paper Andhracollegesandhracolleges100% (1)

- Eamcet 2013 Engineering PaperDocumento62 páginasEamcet 2013 Engineering Paperandhracolleges0% (1)

- Eamcet 2012 Engineering Paper KeyDocumento1 páginaEamcet 2012 Engineering Paper KeyandhracollegesAinda não há avaliações

- Polycet 2014 Question PaperDocumento24 páginasPolycet 2014 Question PaperandhracollegesAinda não há avaliações

- Eamcet 2012 Engineering Paper KeyDocumento1 páginaEamcet 2012 Engineering Paper KeyandhracollegesAinda não há avaliações

- Eamcet 2012 Engineering PaperDocumento62 páginasEamcet 2012 Engineering Paperandhracolleges100% (1)

- Eamcet 2011 Engineering PaperDocumento61 páginasEamcet 2011 Engineering PaperandhracollegesAinda não há avaliações

- Andhracollege Eamcet 2014 Engineering Question Paper With Key SolutionsDocumento62 páginasAndhracollege Eamcet 2014 Engineering Question Paper With Key Solutionsandhracolleges50% (4)

- Eamcet 2012 Medical Paper KeyDocumento1 páginaEamcet 2012 Medical Paper KeyandhracollegesAinda não há avaliações

- Eamcet 2009 Engineering Chemistry PaperDocumento16 páginasEamcet 2009 Engineering Chemistry PaperandhracollegesAinda não há avaliações

- Eamcet 2013 Medical PaperDocumento62 páginasEamcet 2013 Medical PaperandhracollegesAinda não há avaliações

- Eamcet 2006 Engineering PaperDocumento14 páginasEamcet 2006 Engineering PaperandhracollegesAinda não há avaliações

- Eamcet 2008 Engineering PaperDocumento62 páginasEamcet 2008 Engineering PaperandhracollegesAinda não há avaliações

- Eamcet 2007 Engineering PaperDocumento13 páginasEamcet 2007 Engineering Paperandhracolleges100% (1)

- Cloud Based End-to-End AMI Solution PDFDocumento258 páginasCloud Based End-to-End AMI Solution PDFNaresh PattanaikAinda não há avaliações

- E ChequeDocumento5 páginasE ChequedeivaramAinda não há avaliações

- It Is Very Simple To Edit Your Office 2010 Pro PlusDocumento9 páginasIt Is Very Simple To Edit Your Office 2010 Pro PlusCarmen L. MonellAinda não há avaliações

- Anyconnect Secure Mobility Connection Error: "The VPN Client Was Unable To Setup Ip Filtering"Documento5 páginasAnyconnect Secure Mobility Connection Error: "The VPN Client Was Unable To Setup Ip Filtering"Dhiraj SinghAinda não há avaliações

- Skype For Business BW Calc Version 2.70 User GuideDocumento62 páginasSkype For Business BW Calc Version 2.70 User GuidevipermyAinda não há avaliações

- InformaticaDocumento14 páginasInformaticaMbaStudent56Ainda não há avaliações

- Petrel VolumetricsDocumento3 páginasPetrel VolumetricsSalah MahmoudAinda não há avaliações

- Ariyathalangalilekku SCDocumento85 páginasAriyathalangalilekku SCKareem PulipraAinda não há avaliações

- Eurachem Leaflet 17025 EN PDFDocumento2 páginasEurachem Leaflet 17025 EN PDFfaheemqcAinda não há avaliações

- Moumita Saha: Personal DetailsDocumento6 páginasMoumita Saha: Personal DetailsNehaKarunyaAinda não há avaliações

- Maskolis TemplateDocumento51 páginasMaskolis TemplateNannyk WidyaningrumAinda não há avaliações

- Ex Rtos CCSCDocumento9 páginasEx Rtos CCSCWelat YakubAinda não há avaliações

- Wiegand Magstripe How To OrderDocumento13 páginasWiegand Magstripe How To OrderVictor BitarAinda não há avaliações

- Software Requirements Specification: Super SudokuDocumento15 páginasSoftware Requirements Specification: Super SudokuFaisal Abbas BastamiAinda não há avaliações

- Unit 1 PDFDocumento29 páginasUnit 1 PDFsalma sulthana. kAinda não há avaliações

- Mcafee DLP 11.0.400Documento215 páginasMcafee DLP 11.0.400hoangcongchucAinda não há avaliações

- Annex 2: Nasgro 5.X User's Manual Introduction To Version Distributed With EsacrackDocumento6 páginasAnnex 2: Nasgro 5.X User's Manual Introduction To Version Distributed With EsacrackCarlos PlazaolaAinda não há avaliações

- SH CX 9.2.3Documento48 páginasSH CX 9.2.3Dent TewinAinda não há avaliações

- Loops PDFDocumento15 páginasLoops PDFRacer GovardhanAinda não há avaliações

- 1.3.2.5 Packet Tracer - Investigating Directly Connected Routes InstructionsDocumento3 páginas1.3.2.5 Packet Tracer - Investigating Directly Connected Routes InstructionsTadeo Alberto Arias Keb100% (1)

- Academic Analytics Model - Weka FlowDocumento3 páginasAcademic Analytics Model - Weka FlowMadalina BeretAinda não há avaliações

- Resume Paul PresentDocumento3 páginasResume Paul PresentPaul MosqueraAinda não há avaliações

- 2's Complement Division C++ ProgramDocumento11 páginas2's Complement Division C++ ProgramAjitabh Gupta100% (2)

- CSC-103L Object Oriented Programming Section CDocumento3 páginasCSC-103L Object Oriented Programming Section Cabdullahnasarullah10937Ainda não há avaliações

- FAST Ahmad - Bin.laiq IOS DeveloperDocumento1 páginaFAST Ahmad - Bin.laiq IOS DeveloperAhmad LaiqAinda não há avaliações