Escolar Documentos

Profissional Documentos

Cultura Documentos

Ucn5821a PDF

Enviado por

Kayse AhmadDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Ucn5821a PDF

Enviado por

Kayse AhmadDireitos autorais:

Formatos disponíveis

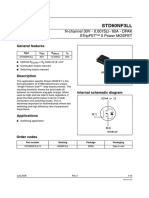

Data Sheet

26185.12E

5821 AND

5822

BiMOS II 8-BIT SERIAL-INPUT,

LATCHED DRIVERS

16

OUT 1

15

OUT 2

LOGIC

GROUND

14

OUT 3

LOGIC

SUPPLY

13

OUT 4

SERIAL

DATA OUT

12

OUT 5

STROBE

ST

11

OUT 6

OUTPUT

ENABLE

OE

10

OUT 7

POWER

GROUND

OUT 8

SERIAL

DATA IN

CLK

VDD

LATCHES

SHIFT REGISTER

CLOCK

SUB

Dwg. PP-026A

Note the DIP package and the SOIC package are

electrically identical and share common terminal

number assignments.

ABSOLUTE MAXIMUM RATINGS

at 25C Free-Air Temperature

Output Voltage, VOUT

UCN5821A & UCN5821LW ..... 50 V

UCN5822A & UCN5822LW ..... 80 V

Logic Supply Voltage, VDD ............. 15 V

Input Voltage Range,

VIN .................. -0.3 V to VDD + 0.3 V

Continuous Output Current,

IOUT ..................................... 500 mA

Package Power Dissipation, PD

Package Code A .................. 2.1 W

Package Code LW ............... 1.5 W

Operating Temperature Range,

TA ............................ -20C to +85C

Storage Temperature Range,

TS .......................... -55C to +150C

A merged combination of bipolar and MOS technology gives

these devices an interface flexibility beyond the reach of standard

logic buffers and power driver arrays. The UCN5821A,

UCN5821LW, UCN5822A, and UCN5822LW each have an

eight-bit CMOS shift register and CMOS control circuitry, eight

CMOS data latches, and eight bipolar current-sinking Darlington

output drivers. The UCN5821A/LW and UCN5822A/LW are

identical except for rated output voltage.

BiMOS II devices have much higher data-input rates than the

original BiMOS circuits. With a 5 V logic supply, they will

typically operate at better than 5 MHz. With a 12 V supply,

significantly higher speeds are obtained. The CMOS inputs are

compatible with standard CMOS and NMOS logic levels. TTL

circuits may require the use of appropriate pull-up resistors. By

using the serial data output, the drivers can be cascaded for

interface applications requiring additional drive lines.

The UCN5821/22A are furnished in a standard 16-pin plastic

DIP; the UCN5821/22LW are in a 16-lead wide-body SOIC for

surface-mount applications. The UCN5821A is also available for

operation from -40C to +85C. To order, change the prefix from

UCN to UCQ.

FEATURES

To 3.3 MHz Data Input Rate

CMOS, NMOS, TTL Compatible

Internal Pull-Down Resistors

Low-Power CMOS Logic & Latches

High-Voltage Current-Sink Outputs

Automotive Capable

Caution: CMOS devices have input static protection

but are susceptible to damage when exposed to

extremely high static electrical charges.

Always order by complete part number, e.g., UCN5821A .

www.allegromicro.com

5821 AND 5822

8-BIT SERIAL-INPUT,

LATCHED DRIVERS

TYPICAL INPUT CIRCUITS

V

FUNCTIONAL BLOCK DIAGRAM

DD

CLOCK

SERIAL

DATA IN

LOGIC

GROUND

LOGIC

SUPPLY

SERIAL-PARALLEL SHIFT REGISTER

SERIAL

DATA OUT

LATCHES

STROBE

OUTPUT ENABLE

(ACTIVE LOW)

POWER

GROUND

VDD

IN

MOS

STROBE &

OUTPUT

ENABLE

BIPOLAR

16

15

14

13

12

11

10

SUB

OUT 1 OUT 2 OUT 3 OUT 4 OUT 5 OUT 6 OUT 7 OUT 8

Dwg. EP-010-3

Dwg. FP-013A

NOTE There is an indeterminate resistance between logic ground and power

ground. For proper operation, these terminals must be externally connected

together.

VDD

CLOCK &

SERIAL

DATA IN

Number of Outputs ON

(IOUT = 200 mA

VDD = 12 V)

IN

Dwg. EP-010-4A

TYPICAL OUTPUT DRIVER

OUT

7.2K

3K

SUB

Dwg. No. A-14,314

8

7

6

5

4

3

2

1

Number of Outputs ON

(IOUT = 200 mA

VDD = 12 V)

8

7

6

5

4

3

2

1

UCN5821A Max. Allowable Duty Cycle

at Ambient Temperature of

25C

40C

50C

60C

70C

90%

100%

100%

100%

100%

100%

100%

100%

79%

90%

100%

100%

100%

100%

100%

100%

72%

82%

96%

100%

100%

100%

100%

100%

65%

74%

86%

100%

100%

100%

100%

100%

57%

65%

76%

91%

100%

100%

100%

100%

UCN5821LW Max. Allowable Duty Cycle

at Ambient Temperature of

25C

40C

50C

60C

70C

67%

77%

90%

100%

100%

100%

100%

100%

59%

68%

79%

95%

100%

100%

100%

100%

54%

62%

72%

86%

100%

100%

100%

100%

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

Copyright 1985, 2000, Allegro MicroSystems, Inc.

49%

56%

65%

78%

98%

100%

100%

100%

43%

49%

57%

68%

86%

100%

100%

100%

5821 AND 5822

8-BIT SERIAL-INPUT,

LATCHED DRIVERS

ELECTRICAL CHARACTERISTICS at TA = +25C, VDD = 5 V, (unless otherwise specified).

Limits

Characteristic

Symbol

Output Leakage

ICEX

Current

Collector-Emitter

VCE(SAT)

Saturation Voltage

Input Voltage

Supply Current

rIN

IDD(ON)

IDD(OFF)

www.allegromicro.com

Min.

Max.

Units

UCN5821A/LW, VOUT = 50 V

50

UCN5822A/LW, VOUT = 80 V

50

UCN5821A/LW, VOUT = 50 V, TA = +70C

100

UCN5822A/LW, VOUT = 80 V, TA = +70C

100

IOUT = 100 mA

1.1

IOUT = 200 mA

1.3

IOUT = 350 mA, VDD = 7.0 V

1.6

0.8

VDD = 12 V

10.5

VDD = 5.0 V

3.5

VDD = 12 V

50

VDD = 5.0 V

50

One Driver ON, VDD = 12 V

4.5

mA

One Driver ON, VDD = 10 V

3.9

mA

One Driver ON, VDD = 5.0 V

2.4

mA

VDD = 5.0 V, All Drivers OFF, All Inputs = 0 V

1.6

mA

VDD = 12 V, All Drivers OFF, All Inputs = 0 V

2.9

mA

VIN(0)

VIN(1)

Input Resistance

Test Conditions

5821 AND 5822

8-BIT SERIAL-INPUT,

LATCHED DRIVERS

Serial Data present at the input is

transferred to the shift register on the

logic 0 to logic 1 transition of the

CLOCK input pulse. On succeeding

CLOCK pulses, the registers shift data

information towards the SERIAL DATA

OUTPUT. The SERIAL DATA must

appear at the input prior to the rising edge

of the CLOCK input waveform.

CLOCK

D

A

B

DATA IN

C

STROBE

OUTPUT

ENABLE

Information present at any register is

transferred to its respective latch when the

STROBE is high (serial-to-parallel conversion). The latches will continue to

accept new data as long as the STROBE

is held high. Applications where the

latches are bypassed (STROBE tied high)

will require that the ENABLE input be

high during serial data entry.

OUT N

Dwg. No. A-12,627

TIMING CONDITIONS

(VDD = 5.0 V, TA = +25C, Logic Levels are VDD and Ground)

A. Minimum Data Active Time Before Clock Pulse

(Data Set-Up Time) ....................................................................... 75 ns

B. Minimum Data Active Time After Clock Pulse

(Data Hold Time) ........................................................................... 75 ns

When the ENABLE input is high, all

of the output buffers are disabled (OFF)

without affecting the information stored

in the latches or shift register. With the

ENABLE input low, the outputs are

controlled by the state of the latches.

C. Minimum Data Pulse Width .............................................................. 150 ns

D. Minimum Clock Pulse Width ............................................................ 150 ns

E.

Minimum Time Between Clock Activation and Strobe ....................... 30 ns

F.

Minimum Strobe Pulse Width ........................................................... 100 ns

G. Typical Time Between Strobe Activation and

Output Transition .......................................................................... 1.0 s

TRUTH TABLE

Serial

Shift Register Contents

Data Clock

Input Input I1 I2 I3 .............. I8

Serial

Data Strobe

Output Input

Latch Contents

I1

I2

I3

.............. I8

Output Contents

Output

Enable

I1 I2 I3 ..............

I8

R1 R2 .............. R7

R7

R1 R2 .............. R7

R7

R1 R2 R3 .............. R8

R8

R1 R2 R3 .............. R8

P8

P1 P2 P3 .............. P8

P1 P2 P3 ..............

P8

H H H ..............

.............. X

P1 P2 P3 .............. P8

L = Low Logic Level

H = High Logic Level

X = Irrelevant

.............. X

P = Present State

R = Previous State

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

5821 AND 5822

8-BIT SERIAL-INPUT,

LATCHED DRIVERS

UCN5821A and UCN5822A

Dimensions in Inches

(controlling dimensions)

0.014

0.008

16

0.430

MAX

0.280

0.240

0.300

BSC

1

0.070

0.045

0.100

0.775

0.735

8

0.005

BSC

MIN

0.210

MAX

0.015

0.150

0.115

MIN

0.022

0.014

Dwg. MA-001-16A in

Dimensions in Millimeters

(for reference only)

0.355

0.204

16

10.92

MAX

7.11

6.10

7.62

BSC

1

1.77

1.15

2.54

19.68

18.67

BSC

0.13

MIN

5.33

MAX

0.39

3.81

2.93

MIN

0.558

0.356

NOTES: 1. Lead thickness is measured at seating plane or below.

2. Lead spacing tolerance is non-cumulative.

3. Exact body and lead configuration at vendors option within limits shown.

www.allegromicro.com

Dwg. MA-001-16A mm

5821 AND 5822

8-BIT SERIAL-INPUT,

LATCHED DRIVERS

UCN5821LW and UCN5822LW

Dimensions in Inches

(for reference only)

16

0.0125

0.0091

0.419

0.394

0.2992

0.2914

0.050

0.016

0.020

0.013

0.050

0 TO 8

BSC

0.4133

0.3977

0.0926

0.1043

0.0040 MIN.

Dwg. MA-008-16A in

Dimensions in Millimeters

(controlling dimensions)

16

0.32

0.23

10.65

10.00

7.60

7.40

1.27

0.40

0.51

0.33

1.27

3

10.50

10.10

BSC

0 TO 8

2.65

2.35

0.10 MIN.

Dwg. MA-008-16A mm

NOTES: 1. Lead spacing tolerance is non-cumulative.

2. Exact body and lead configuration at vendors option within limits shown.

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

5821 AND 5822

8-BIT SERIAL-INPUT,

LATCHED DRIVERS

The products described here are manufactured under one or more

U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to

time, such departures from the detail specifications as may be

required to permit improvements in the performance, reliability, or

manufacturability of its products. Before placing an order, the user is

cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components

in life-support devices or systems without express written approval.

The information included herein is believed to be accurate and

reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of

third parties which may result from its use.

www.allegromicro.com

5821 AND 5822

8-BIT SERIAL-INPUT,

LATCHED DRIVERS

POWER

INTERFACE DRIVERS

Function

Output Ratings*

Part Number

SERIAL-INPUT LATCHED DRIVERS

8-Bit (saturated drivers)

8-Bit

8-Bit

8-Bit

8-Bit

8-Bit (constant-current LED driver)

8-Bit (DMOS drivers)

8-Bit (DMOS drivers)

8-Bit (DMOS drivers)

-120 mA

350 mA

350 mA

350 mA

350 mA

75 mA

250 mA

350 mA

100 mA

50 V

50 V

80 V

50 V

80 V

17 V

50 V

50 V

50 V

5895

5821

5822

5841

5842

6275

6595

6A595

6B595

10-Bit (active pull-downs)

-25 mA

60 V

5810-F and 6809/10

12-Bit (active pull-downs)

-25 mA

60 V

5811 and 6811

75 mA

17 V

6276

20-Bit (active pull-downs)

-25 mA

60 V

5812-F and 6812

32-Bit (active pull-downs)

32-Bit

32-Bit (saturated drivers)

-25 mA

100 mA

100 mA

60 V

30 V

40 V

5818-F and 6818

5833

5832

16-Bit (constant-current LED driver)

PARALLEL-INPUT LATCHED DRIVERS

4-Bit

350 mA

50 V

5800

8-Bit

8-Bit

8-Bit (DMOS drivers)

8-Bit (DMOS drivers)

-25 mA

350 mA

100 mA

250 mA

60 V

50 V

50 V

50 V

5815

5801

6B273

6273

SPECIAL-PURPOSE DEVICES

Unipolar Stepper Motor Translator/Driver

Addressable 8-Bit Decoder/DMOS Driver

Addressable 8-Bit Decoder/DMOS Driver

Addressable 8-Bit Decoder/DMOS Driver

Addressable 28-Line Decoder/Driver

1.25 A

250 mA

350 mA

100 mA

450 mA

50 V

50 V

50 V

50 V

30 V

5804

6259

6A259

6B259

6817

Current is maximum specified test condition, voltage is maximum rating. See specification for sustaining voltage limits.

Negative current is defined as coming out of (sourcing) the output.

Complete part number includes additional characters to indicate operating temperature range and package style.

Internal transient-suppression diodes included for inductive-load protection.

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

Você também pode gostar

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (890)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (399)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (265)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (119)

- Tanner IntroductionDocumento15 páginasTanner IntroductionMohan Raj VediyappanAinda não há avaliações

- 5555syllabi Physics 2014 PDFDocumento52 páginas5555syllabi Physics 2014 PDFAlan gomezAinda não há avaliações

- Batangas State University: The National Engineering UniversityDocumento14 páginasBatangas State University: The National Engineering UniversityDave SmithAinda não há avaliações

- Buk9575 100a PDFDocumento13 páginasBuk9575 100a PDFDanielAinda não há avaliações

- Experimental Estimation of The Band Gap in Silicon and GermaniumDocumento4 páginasExperimental Estimation of The Band Gap in Silicon and GermaniumDickyMaulanaAinda não há avaliações

- EPD-Concept To Product-1Documento34 páginasEPD-Concept To Product-1amunniAinda não há avaliações

- Solar Smart Irrigation SystemDocumento22 páginasSolar Smart Irrigation SystemSubhranshu Mohapatra100% (1)

- 2009-10 T.Y.B.SC. ElectronicsDocumento26 páginas2009-10 T.Y.B.SC. Electronicshys0671Ainda não há avaliações

- Std60Nf3Ll: N-Channel 30V - 0.0075 - 60A - Dpak Stripfet™ Ii Power MosfetDocumento13 páginasStd60Nf3Ll: N-Channel 30V - 0.0075 - 60A - Dpak Stripfet™ Ii Power MosfetFransiskus Galih SumartonoAinda não há avaliações

- Primary I Injection KitDocumento3 páginasPrimary I Injection Kitshashank715100% (1)

- Esr70 Userguide en PDFDocumento16 páginasEsr70 Userguide en PDFLy Fotoestudio DigitalcaAinda não há avaliações

- SMART MATERIALS MERITSDocumento6 páginasSMART MATERIALS MERITSRahul Darshan Srt100% (2)

- A SYSTEMATIC STUDY OF LAYOUT PROXIMITY EFFECTS FOR 28NM POLY/SIONDocumento4 páginasA SYSTEMATIC STUDY OF LAYOUT PROXIMITY EFFECTS FOR 28NM POLY/SIONSindhu100% (1)

- Controlling Stepper Motors With A PIC MicrocontrollerDocumento16 páginasControlling Stepper Motors With A PIC Microcontrollervasudeva yasasAinda não há avaliações

- Dual 1.5A-Peak Low-Side MOSFET Drivers: Features General DescriptionDocumento20 páginasDual 1.5A-Peak Low-Side MOSFET Drivers: Features General DescriptionNitish kumarAinda não há avaliações

- UNIT-I NewDocumento163 páginasUNIT-I NewSanjay Rajan VAinda não há avaliações

- DC Motor Control Through Power DevicesDocumento42 páginasDC Motor Control Through Power DevicesOnyango Okelo100% (1)

- uBer SWITCH V1.1 Microcontroller Relay True-Bypass CircuitDocumento3 páginasuBer SWITCH V1.1 Microcontroller Relay True-Bypass CircuitUjang PriyantoAinda não há avaliações

- DC Choppers ExplainedDocumento56 páginasDC Choppers Explainedsaikarthick023Ainda não há avaliações

- Lecture17 PDFDocumento19 páginasLecture17 PDFSuriya SkariahAinda não há avaliações

- Gen 042 V 1Documento28 páginasGen 042 V 1Yung Jia ChoongAinda não há avaliações

- Grimes C. A., Varghese O., Ranjan S. - Solar Production of Hydrogen by Water Photoelectrolysis (2007)Documento561 páginasGrimes C. A., Varghese O., Ranjan S. - Solar Production of Hydrogen by Water Photoelectrolysis (2007)Benjamin F ZavalaAinda não há avaliações

- LC Ladder Matching NetworksDocumento33 páginasLC Ladder Matching NetworksCarriceiros TourAinda não há avaliações

- Development of TSMC 0.25 M Standard Cell LibraryDocumento3 páginasDevelopment of TSMC 0.25 M Standard Cell Libraryhex0x1Ainda não há avaliações

- Cascadable Silicon Bipolar MMIC Amplifiers: Technical DataDocumento4 páginasCascadable Silicon Bipolar MMIC Amplifiers: Technical DataGabriel RacovskyAinda não há avaliações

- Aoyue Int2703ADocumento16 páginasAoyue Int2703AluisAinda não há avaliações

- Generator ProtectionDocumento10 páginasGenerator ProtectionVirendra SinghAinda não há avaliações

- TDA3683J: 1. General DescriptionDocumento31 páginasTDA3683J: 1. General DescriptionAlexis FloresAinda não há avaliações

- Transformers 5: Overcurrent ProtectionDocumento4 páginasTransformers 5: Overcurrent ProtectionKristian MevželjAinda não há avaliações

- 4.5 Optek BrochureDocumento28 páginas4.5 Optek BrochureRizal AfyudinAinda não há avaliações