Escolar Documentos

Profissional Documentos

Cultura Documentos

NTE4075B & NTE4075BT CMOS Triple 3-Input OR Gate Datasheet

Enviado por

Xxvic2rxXTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

NTE4075B & NTE4075BT CMOS Triple 3-Input OR Gate Datasheet

Enviado por

Xxvic2rxXDireitos autorais:

Formatos disponíveis

NTE4075B & NTE4075BT

Integrated Circuit

CMOS, Triple 3Input OR Gate

Description:

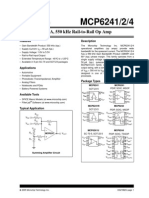

The NTE4075B (14Lead DIP) and NTE4075BT (SOIC14) are triple 3input OR gate devices

constructed with PChannel and NChannel enhancement mode devices in a single monolithic

structure. These complementary MOS logic gates find primary use where low power dissipation

and/or high noise immunity is desired.

Features:

D Supply Voltage Range: 3Vdc to 18Vdc

D All Outputs Buffered

D Capable of Driving Two LowPower TTL Loads or One LowPower Schottky TTL Load Over

the Rated Temperature Range

D Double Diode Protection on All Inputs

Absolute Maximum Ratings: (Voltages referenced to VSS, Note 1)

DC Supply Voltage, VDD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 to +18.0V

Input Voltage (DC or Transient), Vin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 to VDD to +0.5V

Output Voltage (DC or Transient), Vout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 to VDD to +0.5V

Input Current (DC or Transient, Per Pin), Iin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10mA

Output Current (DC or Transient, Per Pin), Iout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10mA

Power Dissipation (Per Package), PD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500mW

Temperature Derating (from +65 to +125C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7.0mW/C

Storage Temperature, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65 to +150C

Lead Temperature (During Soldering, 8sec max), TL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +260C

Note 1. Maximum Ratings are those values beyond which damage to the device may occur.

Electrical Characteristics: (Voltages referenced to VSS, Note 2)

555C

+255C

+1255C

VDD

Vdc

5.0

Min

Max

Min

Typ

Max

Min

Max

0.05

0.05

0.05

Unit

Vdc

10

0.05

0.05

0.05

Vdc

15

0.05

0.05

0.05

Vdc

5.0

4.95

4.95

5.0

4.95

Vdc

10

9.95

9.95

10

9.95

Vdc

15

14.95

14.95

15

14.95

Vdc

5.0

1.5

2.25

1.5

1.5

Vdc

(VO = 9.0 or 1.0Vdc)

10

3.0

4.50

3.0

3.0

Vdc

(VO = 13.5 or 1.5Vdc)

15

4.0

6.75

4.0

4.0

Vdc

5.0

3.5

3.5

2.75

3.5

Vdc

(VO = 1.0 or 9.0Vdc)

10

7.0

7.0

5.50

7.0

Vdc

(VO = 1.5 or 13.5Vdc)

15

11.0

11.0

8.25

11.0

Vdc

5.0

3.0

2.4

4.2

1.7

mAdc

(VOH = 4.6Vdc)

5.0

0.64

0.51

0.88

0.36

mAdc

(VOH = 9.5Vdc)

10

1.6

1.3

2.25

0.9

mAdc

(VOH = 13.5Vdc)

15

4.2

3.4

8.8

2.4

mAdc

5.0

0.64

0.51

0.88

0.36

mAdc

(VOL = 0.5Vdc)

10

1.6

1.3

2.25

0.9

mAdc

(VOL = 1.5Vdc)

15

4.2

3.4

8.8

2.4

mAdc

Parameter

Output Voltage

Vin = VDD or 0

Symbol

0 Level

VOL

1 Level

VOH

Vin = 0 or VDD

Input Voltage

0 Level

(VO = 4.5 or 0.5Vdc)

(VO = 0.5 or 4.5Vdc)

Output Drive Current

(VOH = 2.5Vdc)

1 Level

Source

(VOL = 0.4Vdc)

Sink

VIL

VIH

IOH

IOL

Input Current

Iin

15

0.1

0.00001

0.1

0.1

Adc

Input Capacitance (VIN = 0)

Cin

5.0

7.5

pF

Quiescent Current

(Per Package)

IDD

5.0

0.25

0.0005

0.25

7.5

Adc

10

0.5

0.0010

0.5

15

Adc

15

1.0

0.0015

1.0

30

Adc

Total Supply Current

(Dynamic plus Quiescent,

Per Gate, CL = 50pF,

Note 3, Note 4)

IT

5.0

IT = (0.3A/kHz) f + IDD/N

Adc

10

IT = (0.6A/kHz) f + IDD/N

Adc

15

IT = (0.8A/kHz) f + IDD/N

Adc

Note 2. Data labeled Typ is not to be used for design purposes but is intended as an indication of

the devices potential performance.

Note 3. The formulas given are for the typical characteristics only at +25C.

Note 4. To calculate total supply current at loads other than 50pF:

IT(CL) = IT(50pF) + (CL 50) Vfk

where: IT is in H (per package), CL in pF, V = (VDD VSS) in volts, f in kHz is input frequency,

and k = 0.001 x the number of exercised gates per package.

Switching Characteristics: (CL = 50pF, TA = +25C, Note 2)

VDD

Vdc

Min

Typ

Max

Unit

5.0

100

200

ns

tTLH = (0.60ns/pf) CL + 20ns

10

50

100

ns

tTLH = (0.40ns/pf) CL + 20ns

15

40

80

ns

5.0

100

200

ns

tTHL = (0.60ns/pf) CL + 20ns

10

50

100

ns

tTHL = (0.40ns/pf) CL + 20ns

15

40

80

ns

5.0

160

300

ns

tPLH, tPHL = (0.36ns/pf) CL + 47ns

10

65

130

ns

tPLH, tPHL = (0.26ns/pf) CL + 37ns

15

50

100

ns

Parameter

Symbol

Output Rise Time

tTLH = (1.35ns/pf) CL + 33ns

tTLH

Output Fall Time

tTHL = (1.35ns/pf) CL + 33ns

tTHL

Propagation Delay Time

tPLH, tPHL = (0.90ns/pf) CL + 115ns

tPLH.

tPHL

Note 2. Data labeled Typ is not to be used for design purposes but is intended as an indication of

the devices potential performance.

Note 3. The formulas given are for the typical characteristics only at +25C.

Logic Diagram

1

2

8

3

4

5

11

12

13

10

VDD = Pin14

VSS = Pin7

Pin Connection Diagram

A 1

14 VDD

B 2

D 3

13 G

12 H

E 4

11 I

F 5

10 L = G + H + I

K=D+E+F 6

VSS 7

9 J=A+B+C

8 C

NTE4075B

14

.300

(7.62)

.600 (15.24)

.200 (5.08)

Max

.100 (2.45)

.099 (2.5) Min

.785 (19.95)

Max

NTE4075BT

.340 (8.64)

.050 (1.27)

14

.198

(5.03)

.154

(3.91)

.236

(5.99)

016 (.406)

061

(1.53)

.006 (.152)

NOTE: Pin1 on Beveled Edge

Você também pode gostar

- Nte 4013Documento4 páginasNte 4013Codinasound CaAinda não há avaliações

- Nte 4053Documento4 páginasNte 4053Codinasound CaAinda não há avaliações

- D D D D D D D D D D D D: For Description of "B" Series CMOS DevicesDocumento25 páginasD D D D D D D D D D D D: For Description of "B" Series CMOS Devicestotal4321Ainda não há avaliações

- D D D D D D D D D D D D: CD4066B Cmos Quad Bilateral SwitchDocumento20 páginasD D D D D D D D D D D D: CD4066B Cmos Quad Bilateral SwitchAnna Kaye Sapanhila AninAinda não há avaliações

- NTE15044 CMOS IC detects supply voltage for reset signalsDocumento3 páginasNTE15044 CMOS IC detects supply voltage for reset signalsWesley Silva FreitasAinda não há avaliações

- NTE2372 Mosfet P CH, Enhancement Mode High Speed Switch TO220 Type PackageDocumento3 páginasNTE2372 Mosfet P CH, Enhancement Mode High Speed Switch TO220 Type Packagebat2188Ainda não há avaliações

- CD 4528Documento9 páginasCD 4528L30N1Ainda não há avaliações

- NTE7223 adjustable output voltage regulator ICDocumento3 páginasNTE7223 adjustable output voltage regulator IChernan021178Ainda não há avaliações

- Ad 7524Documento8 páginasAd 7524Giovanny ContrerasAinda não há avaliações

- Nte 962Documento2 páginasNte 962Amine IchigoAinda não há avaliações

- Ic-Cmos-4008 UNTUK DECODER PDFDocumento9 páginasIc-Cmos-4008 UNTUK DECODER PDFBenny PadlyAinda não há avaliações

- Datasheet NTE85Documento2 páginasDatasheet NTE85ikaro181083Ainda não há avaliações

- NTE1497 Integrated Circuit Audio Preamp /alc: W DescriptionDocumento2 páginasNTE1497 Integrated Circuit Audio Preamp /alc: W DescriptionPratomoEdhiAinda não há avaliações

- HC14Documento10 páginasHC14Bruno NascimentoAinda não há avaliações

- NTE4093B Integrated Circuit Cmos,: Quad 2 Input NAND Schmitt TriggerDocumento3 páginasNTE4093B Integrated Circuit Cmos,: Quad 2 Input NAND Schmitt TriggerJoséYairsiñoCuberoDíazAinda não há avaliações

- ISL3293E, ISL3294E, ISL3295E, ISL3296E, ISL3297E, ISL3298E: 16.5kV ESD Protected, +125°C, 3.0V ToDocumento17 páginasISL3293E, ISL3294E, ISL3295E, ISL3296E, ISL3297E, ISL3298E: 16.5kV ESD Protected, +125°C, 3.0V Tobndfruit1Ainda não há avaliações

- cd4007 Intersil DatasheetDocumento9 páginascd4007 Intersil DatasheetMarie HayesAinda não há avaliações

- D D D D D D D D D: Description/ordering InformationDocumento16 páginasD D D D D D D D D: Description/ordering InformationCarlos de SouzaAinda não há avaliações

- LC MOS Precision Quad SPST Switches ADG411/ADG412/ADG413: 615 V Analog Signal Range V) MW)Documento8 páginasLC MOS Precision Quad SPST Switches ADG411/ADG412/ADG413: 615 V Analog Signal Range V) MW)Fer TgAinda não há avaliações

- Nte 956Documento2 páginasNte 956belami93Ainda não há avaliações

- Low Power, +3.3 V, RS-232 Line Drivers/Receivers: F Charge Pump CapacitorsDocumento8 páginasLow Power, +3.3 V, RS-232 Line Drivers/Receivers: F Charge Pump Capacitorsmeroka2000Ainda não há avaliações

- TLC 7628Documento12 páginasTLC 7628velizarkoAinda não há avaliações

- Cto de Corrimiento Elevador ThyssenDocumento20 páginasCto de Corrimiento Elevador ThyssenFrancisco Javier BurgosAinda não há avaliações

- Driver Mosfet TC4425Documento18 páginasDriver Mosfet TC4425jaimeAinda não há avaliações

- NTE1927 Integrated Circuit 4-Terminal Negative Adjustable Voltage RegulatorDocumento3 páginasNTE1927 Integrated Circuit 4-Terminal Negative Adjustable Voltage RegulatorLeandro AguiarAinda não há avaliações

- TL3472 High-Slew-Rate, Single-Supply Operational Amplifier: D D D D D D D DDocumento6 páginasTL3472 High-Slew-Rate, Single-Supply Operational Amplifier: D D D D D D D DLaura MrnAinda não há avaliações

- NTE950/NTE951/NTE977 Integrated Circuit Positive 3 Terminal Voltage Regulator, 100maDocumento3 páginasNTE950/NTE951/NTE977 Integrated Circuit Positive 3 Terminal Voltage Regulator, 100maRolando CoelloAinda não há avaliações

- NE5532 - Nte778aDocumento3 páginasNE5532 - Nte778adaneloAinda não há avaliações

- NTE7142 Integrated Circuit +5V - Powered, Multichannel RS - 232 Driver/ReceiverDocumento3 páginasNTE7142 Integrated Circuit +5V - Powered, Multichannel RS - 232 Driver/ReceiverJefferson Arley Alvarino GranadosAinda não há avaliações

- OpAmp - MCP6241Documento28 páginasOpAmp - MCP6241Ludwig SchmidtAinda não há avaliações

- CD22100 - DataSheetDocumento10 páginasCD22100 - DataSheetHao ChungAinda não há avaliações

- Nte 3041Documento3 páginasNte 3041Albert VásquezAinda não há avaliações

- l7812cv Nte966Documento3 páginasl7812cv Nte966ch3o108362660% (1)

- N-Channel Silicon Junction Field Effect Transistor: DescriptionDocumento4 páginasN-Channel Silicon Junction Field Effect Transistor: DescriptionKoky HSAinda não há avaliações

- NTE3078 & NTE3079 0.56" Single Digit Numeric Display Seven Segment, RHDPDocumento2 páginasNTE3078 & NTE3079 0.56" Single Digit Numeric Display Seven Segment, RHDPFadli Fatur RahmatAinda não há avaliações

- NE5532P DatasheetDocumento11 páginasNE5532P DatasheetdiralarkAinda não há avaliações

- CD4094BMS: Pinout FeaturesDocumento11 páginasCD4094BMS: Pinout FeaturesakbarparlindunganAinda não há avaliações

- RFG60P06E: 60A, 60V, 0.030 Ohm, ESD Rated, P-Channel Power MOSFET FeaturesDocumento7 páginasRFG60P06E: 60A, 60V, 0.030 Ohm, ESD Rated, P-Channel Power MOSFET FeaturesNguyen Danh HuyAinda não há avaliações

- CA3161EDocumento4 páginasCA3161EAlejandro Borrego DominguezAinda não há avaliações

- TLC 272Documento53 páginasTLC 272Giapy Phuc TranAinda não há avaliações

- NTE2396 MOSFET N-Ch, Enhancement Mode High Speed Switch TO220Documento4 páginasNTE2396 MOSFET N-Ch, Enhancement Mode High Speed Switch TO220OSBALDO1205Ainda não há avaliações

- NTE7061 Integrated Circuit Dual 5.3W Audio Power Amplifier CircuitDocumento2 páginasNTE7061 Integrated Circuit Dual 5.3W Audio Power Amplifier CircuitDJORJEAinda não há avaliações

- IRF9520Documento8 páginasIRF9520David AllendesAinda não há avaliações

- TL084 - Nte859Documento3 páginasTL084 - Nte859nollcaton7685Ainda não há avaliações

- Driver tc4421Documento18 páginasDriver tc4421Jonatan Saavedra AguirreAinda não há avaliações

- CD4093 PDFDocumento8 páginasCD4093 PDFIván IvanovAinda não há avaliações

- HCTS245MS: Radiation Hardened Octal Bus Transceiver, Three-State, Non-InvertingDocumento9 páginasHCTS245MS: Radiation Hardened Octal Bus Transceiver, Three-State, Non-InvertingDeepa DevarajAinda não há avaliações

- Max 31865 DatasheetDocumento25 páginasMax 31865 Datasheetalexender2kAinda não há avaliações

- N-Channel JFET General Purpose Amplifier/Switch: Absolute Maximum Ratings Pin ConfigurationDocumento2 páginasN-Channel JFET General Purpose Amplifier/Switch: Absolute Maximum Ratings Pin ConfigurationdungeonlegendAinda não há avaliações

- CMOS timing circuit NTE955MCDocumento7 páginasCMOS timing circuit NTE955MCManuel ReynosoAinda não há avaliações

- NTE398 Silicon PNP Transistor TV Vertical Output (Compl To NTE375)Documento2 páginasNTE398 Silicon PNP Transistor TV Vertical Output (Compl To NTE375)Sergio Daniel BarretoAinda não há avaliações

- Low Power, 3.3 V, RS-232 Line Drivers/Receivers: F Charge Pump CapacitorsDocumento9 páginasLow Power, 3.3 V, RS-232 Line Drivers/Receivers: F Charge Pump Capacitorsdarkinvader2099Ainda não há avaliações

- CD 4060Documento10 páginasCD 4060ahocine2011Ainda não há avaliações

- CD4008BMS - Full AdderDocumento8 páginasCD4008BMS - Full AdderTony TohAinda não há avaliações

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsAinda não há avaliações

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1No EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Nota: 2.5 de 5 estrelas2.5/5 (3)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsNo EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsNota: 3.5 de 5 estrelas3.5/5 (6)

- 184 6154699899Documento64 páginas184 6154699899Xxvic2rxXAinda não há avaliações

- DER EE DE-5000 English User ManualDocumento19 páginasDER EE DE-5000 English User ManualRenatoBašić100% (2)

- Hardware Reference Guide: HP Compaq Business Desktops dx6100 Microtower ModelDocumento52 páginasHardware Reference Guide: HP Compaq Business Desktops dx6100 Microtower ModelXxvic2rxXAinda não há avaliações

- Compal Electronics, inc. M/B LA-1011 schematicDocumento46 páginasCompal Electronics, inc. M/B LA-1011 schematicXxvic2rxXAinda não há avaliações

- Success Creathjs KKHDSDDocumento4 páginasSuccess Creathjs KKHDSDXxvic2rxXAinda não há avaliações

- Schematis HP V3000 DV2000 IntelDocumento47 páginasSchematis HP V3000 DV2000 Intelmadoo0% (2)

- Viper22A-E Viper22Adip-E, Viper22As-E: Low Power Off-Line Smps Primary SwitcherDocumento21 páginasViper22A-E Viper22Adip-E, Viper22As-E: Low Power Off-Line Smps Primary SwitcherAkash KumarAinda não há avaliações

- Platinum Remote PCB DiagramDocumento2 páginasPlatinum Remote PCB DiagramXxvic2rxX86% (22)

- Writing PBP Commands/macros: Forum PICBASIC - Co.uk Mel Pic Basic ProDocumento2 páginasWriting PBP Commands/macros: Forum PICBASIC - Co.uk Mel Pic Basic ProXxvic2rxXAinda não há avaliações

- 5-Types of DiodesDocumento24 páginas5-Types of DiodesHidayah HadiAinda não há avaliações

- 88acd 888Z3 LA-1044Documento44 páginas88acd 888Z3 LA-1044JtzabalaAinda não há avaliações

- TCP vs. COFDocumento2 páginasTCP vs. COFXxvic2rxXAinda não há avaliações

- 200 Ways To Revive Hard DiskDocumento74 páginas200 Ways To Revive Hard Diskdanielle leighAinda não há avaliações

- Troubleshooting SCADA Data Acquisition SystemsDocumento24 páginasTroubleshooting SCADA Data Acquisition SystemsXxvic2rxXAinda não há avaliações

- AVR Fuses TutorialDocumento6 páginasAVR Fuses TutorialXxvic2rxXAinda não há avaliações

- 5 Command Line Tools To Detect Windows HacksDocumento6 páginas5 Command Line Tools To Detect Windows HacksameyAinda não há avaliações

- TL866 Schematic DiagramDocumento4 páginasTL866 Schematic Diagramradioman_35100% (5)

- Getting Started with Arduino GuideDocumento34 páginasGetting Started with Arduino Guidesairam_9100% (11)

- GP-12-2500A Power Inverter PDFDocumento2 páginasGP-12-2500A Power Inverter PDFamurugan006Ainda não há avaliações

- Optocoupler Vs OptoisolatorDocumento2 páginasOptocoupler Vs OptoisolatorXxvic2rxXAinda não há avaliações

- Novice's Guide To AVR DevelopmentDocumento5 páginasNovice's Guide To AVR Developmentdeivs001100% (1)

- CRT Rejuvenator MonochromeDocumento1 páginaCRT Rejuvenator MonochromeXxvic2rxXAinda não há avaliações

- Arduino Tips Tricks and TechniquesDocumento39 páginasArduino Tips Tricks and TechniquesVinay Nagnath JokareAinda não há avaliações

- 2000 Watt Audio AmpDocumento2 páginas2000 Watt Audio AmpXxvic2rxX50% (2)

- Lipirea Panourilor LCDDocumento11 páginasLipirea Panourilor LCDfox7878Ainda não há avaliações

- Assembly Manual: In-Circuit LOPT/FBT Tester K 7205Documento6 páginasAssembly Manual: In-Circuit LOPT/FBT Tester K 7205majanaam100% (1)

- SONY T CON Training ManualDocumento12 páginasSONY T CON Training ManualКрасимир Костадинов96% (26)

- R A 9292 PDFDocumento18 páginasR A 9292 PDFDaryl Langamon Uy CruzAinda não há avaliações

- EEE726 Assignments PDFDocumento4 páginasEEE726 Assignments PDFIkenna OnyegbadueAinda não há avaliações

- M&a SecB Group7 GE AlstomDocumento7 páginasM&a SecB Group7 GE AlstomPOOJA GUPTAAinda não há avaliações

- Variable DC SupplyDocumento3 páginasVariable DC SupplyVamsi PatwariAinda não há avaliações

- Panacea 351PDocumento2 páginasPanacea 351POscar MorenoAinda não há avaliações

- Electrical Design GuideDocumento25 páginasElectrical Design GuideSayed Nagy100% (3)

- Design of LCL Filters For The Back-To-Back Converter in A Doubly Fed Induction Generator PDFDocumento7 páginasDesign of LCL Filters For The Back-To-Back Converter in A Doubly Fed Induction Generator PDFStefania OliveiraAinda não há avaliações

- 103 QStart Flatpack2 PSSyst PDFDocumento32 páginas103 QStart Flatpack2 PSSyst PDFGregory CoerielAinda não há avaliações

- Field Inspection and Testing of MediumVoltage Motor Control Centres MCCDocumento4 páginasField Inspection and Testing of MediumVoltage Motor Control Centres MCCMahmoud FawzyAinda não há avaliações

- Pre Commissioning Tests ChecklistDocumento9 páginasPre Commissioning Tests ChecklistFeroz Hakkim80% (5)

- Water Injection: Atox 30.0 Vendor Instruction Other Information Plant Name: Ha LongDocumento127 páginasWater Injection: Atox 30.0 Vendor Instruction Other Information Plant Name: Ha LongDuc Nguyen VanAinda não há avaliações

- Rele Temporizador ScheinederDocumento4 páginasRele Temporizador ScheinederJasson da GiedreAinda não há avaliações

- Proper Storing of Hand Tools and Instruments: SjkhsDocumento43 páginasProper Storing of Hand Tools and Instruments: SjkhsFrancess Mae BunaganAinda não há avaliações

- Source Cat 6 Cable 305m Box Network Cable 23AWG 0.57mm Cat 6 Utp Onfame Ethernet Cat6 Cable OnDocumento1 páginaSource Cat 6 Cable 305m Box Network Cable 23AWG 0.57mm Cat 6 Utp Onfame Ethernet Cat6 Cable OnMubeezi ConseptarAinda não há avaliações

- Asco S300G - Manual de UsuarioDocumento40 páginasAsco S300G - Manual de UsuarioImplementación OLCAinda não há avaliações

- Temporizador SiemensDocumento7 páginasTemporizador SiemensHarly HenaoAinda não há avaliações

- Applications of Electromagnetic InductionDocumento6 páginasApplications of Electromagnetic InductionAdeniji OlusegunAinda não há avaliações

- CT & PT CalculationsDocumento10 páginasCT & PT CalculationsAbhishek RajputAinda não há avaliações

- Capacitor Banks Improve DG Set ProductivityDocumento4 páginasCapacitor Banks Improve DG Set ProductivityTigrillo100% (1)

- 1SBC101140C0201-Contactors For Capacitors 2Documento34 páginas1SBC101140C0201-Contactors For Capacitors 2thiago_gomes7953Ainda não há avaliações

- User Manual: YX2000/3000/3300 Sensorless Vector TypeDocumento172 páginasUser Manual: YX2000/3000/3300 Sensorless Vector TypeAlex VargasAinda não há avaliações

- Bussmann DFJ Fuse DatasheetDocumento4 páginasBussmann DFJ Fuse DatasheetlarryAinda não há avaliações

- Coordinated Voltage and Reactive Power Control Strategy With Distributed Generator For Improving The Operational EfficiencyDocumento8 páginasCoordinated Voltage and Reactive Power Control Strategy With Distributed Generator For Improving The Operational EfficiencyRaphael NgenyiAinda não há avaliações

- X05B-X06Relay Datasheet REVA 29MAR17Documento2 páginasX05B-X06Relay Datasheet REVA 29MAR17Abdelaaziz ALLALIAinda não há avaliações

- CDI Tester Circuit Electronic Circuit ProjectsDocumento37 páginasCDI Tester Circuit Electronic Circuit Projectssahilsahni200% (1)

- KP D50PDocumento5 páginasKP D50PDerek ChenAinda não há avaliações

- NECA 402: Standard For Installing and Maintaining Motor Control CentersDocumento42 páginasNECA 402: Standard For Installing and Maintaining Motor Control CentersGILBERTO ALTUNARAinda não há avaliações

- LORENTZ - PSk2-7 - c-sj8-30 - Pi - en - Ver310183Documento2 páginasLORENTZ - PSk2-7 - c-sj8-30 - Pi - en - Ver310183Muhammad JawadAinda não há avaliações

- Single-Phase Converter Systems Containing Ideal RectifiersDocumento51 páginasSingle-Phase Converter Systems Containing Ideal Rectifiersselaroth168Ainda não há avaliações

- APC EASY UPS BV 650VA, AVR, Universal Outlet, 230V: Technical SpecificationsDocumento3 páginasAPC EASY UPS BV 650VA, AVR, Universal Outlet, 230V: Technical SpecificationsUsman QureshiAinda não há avaliações

- 03 User ManualAMF Controller and Monitoring With EStone-IIUpto 32kVA DG RatingDocumento37 páginas03 User ManualAMF Controller and Monitoring With EStone-IIUpto 32kVA DG RatingSangram NayakAinda não há avaliações