Escolar Documentos

Profissional Documentos

Cultura Documentos

M XQSZV

Enviado por

Roozbeh BahmanyarTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

M XQSZV

Enviado por

Roozbeh BahmanyarDireitos autorais:

Formatos disponíveis

MITSUBISHI

MITSUBISHI

SEMICONDUCTOR

SEMICONDUCTOR

<Intelligent

<Intelligent

Power

Power

Module>

Module>

PS21553-G

PS21553-G

TRANSFER-MOLD

TRANSFER-MOLD

TYPE

TYPE

INSULATED

INSULATED

TYPE

TYPE

PS21553-G

INTEGRATED POWER FUNCTIONS

4th generation (planar) IGBT inverter bridge for three phase

DC-to-AC power conversion.

INTEGRATED DRIVE, PROTECTION AND SYSTEM CONTROL FUNCTIONS

For upper-leg IGBTS : Drive circuit, High voltage isolated high-speed level shifting, Control circuit under-voltage (UV) protection.

Note : Bootstrap supply scheme can be applied.

For lower-leg IGBTS : Drive circuit, Control circuit under-voltage protection (UV), Short-circuit protection (SC).

Fault signaling : Corresponding to a SC fault (Low-side IGBT) or a UV fault (Low-side IGBT).

Input interface : 5V line CMOS/TTL compatible, Schmitt Trigger receiver circuit.

APPLICATION

AC100V~200V three-phase inverter drive for small power motor control.

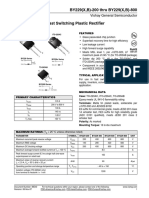

Fig. 1 PACKAGE OUTLINES

(3.556)

TERMINAL CODE

(1.656)

(3.556)

HEAT SINK SIDE

1

TERMINAL

(1)

2

(0.5)

3

4

5

PCB

6

(1)

PATTERN 7

8

(1.9) SLIT

(1)

(0.5)

9

(1.8MIN)

10

(PCB LAYOUT)

11

DUMMY PIN

Detail A

(1.778 26)

*Note2

12

13

(1.778)

(5)

14

(6.25) (6.25) (6.25) (8)

(8)

A

15

16

)

2

17

TH

28 27 26 25 24 23 22 21 20 19 18 16

15 13

12 10

987

654

321

EP

18

17

14

11

D

2

19

(

29

)

20

3

Type

name

,

Lot

No.

.

30

(3

21

22

23

HEAT SINK SIDE

24

(35

)

25

26

27

28

35

34

33

32

31

29

30

31

(7.62)

(4MIN)

32

33

(7.62 4)

(1.25)

34

(2.5)

(41)

35

(42)

(1.5)

(10.5)

(1.2)

(17.4)

(0.5)

(17.4)

(0.75)

(30.5)

(0.5)

(6.5)

(0.5)

(49)

Dimensions in mm

VUFS

(UPG)

VUFB

VP1

(COM)

UP

VVFS

(VPG)

VVFB

VP1

(COM)

VP

VWFS

(WPG)

VWFB

VP1

(COM)

WP

(UNG)

VNO(NC)

UN

VN

WN

FO

CFO

CIN

VNC

VN1

(WNG)

(VNG)

P

U

V

W

N

*Note1:(***) = Dummy Pin.

*Note 2: In order to increase the surface distance between terminals, cut a slit, etc. on the PCB surface

when mounting a module.

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21553-G

TRANSFER-MOLD TYPE

INSULATED TYPE

Fig. 2 INTERNAL FUNCTIONS BLOCK DIAGRAM (TYPICAL APPLICATION EXAMPLE)

CBW

CBW+

CBU+

CBV+

CBV

CBU

High-side input (PWM)

(5V line) (Note 1,2)

C3 : Tight tolerance, temp-compensated electrolytic type

(Note : The capacitance value depends on the PWM control

scheme used in the applied system).

C4 : 0.22~2F R-category ceramic capacitor for noise filtering.

C4

C3

Input signal Input signal Input signal

coditioning coditioning coditioning

Level shifter Level shifter Level shifter

Protection

circuit (UV)

Protection

circuit (UV)

(Note 6)

Protection

circuit (UV)

DIP-IPM

Drive circuit Drive circuit Drive circuit

Inrush current

limiter circuit

AC input

H-side IGBTS

(Note 4)

Fig. 3

U

V

W

M

AC line output

N1

VNC

Z : ZNR (Surge absorber)

C : AC filter (Ceramic capacitor 2.2~6.5nF)

(Note : Additionally, an appropriate line to line

surge absorber circuit may become necessary

depending on the application environment.)

N

L-side IGBTS

CIN

Drive circuit

SC

protection

Fo logic

Input signal conditioning

Control supply

Under-Voltage

protection

FO CFO

Low-side input (PWM)

(5V line)

(Note 1, 2) FO output (5V line)

(Note 3, 5)

Note1:

2:

3:

4:

5:

6:

VNC

VD

(15V line)

To prevent the input signals oscillation, an RC coupling at each input is recommended. (see also Fig. 6)

By virtue of integrating an application specific type HVIC inside the module, direct coupling to CPU terminals without any opto-coupler or transformer

isolation is possible. (see also Fig. 6)

This output is open collector type. The signal line should be pulled up to the positive side of the 5V power supply with approximately 5.1k resistance.

(see also Fig. 6)

The wiring between the power DC link capacitor and the P/N1 terminals should be as short as possible to protect the DIP-IPM against catastrophic high

surge voltages. For extra precaution, a small film type snubber capacitor (0.1~0.22F, high voltage type) is recommended to be mounted close to

these P and N1 DC power input terminals.

Fo output pulse width should be decided by connecting external capacitor between CFO and VNC terminals. (Example : CFO=22nF tFO=1.8ms (Typ.))

High voltage (600V or more) and fast recovery type (less than 100ns) diodes should be used in the bootstrap circuit.

Fig. 3 EXTERNAL PART OF THE DIP-IPM PROTECTION CIRCUIT

DIP-IPM

Short Circuit Protective Function (SC) :

SC protection is achieved by sensing the L-side DC-Bus current (through the external

shunt resistor) after allowing a suitable filtering time (defined by the RC circuit).

When the sensed shunt voltage exceeds the SC trip-level, all the L-side IGBTs are turned

OFF and a fault signal (Fo) is output. Since the SC fault may be repetitive, it is

recommended to stop the system when the Fo signal is received and check the fault.

Drive circuit

IC (A)

H-side IGBTS

SC Protection

Trip Level

U

V

W

L-side IGBTS

External protection circuit

N1

Shunt Resistor

(Note 1)

VNC

C R

Drive circuit

CIN

B

C

Collector current

waveform

Protection circuit

(Note 2)

Note1: In the recommended external protection circuit, please select the RC time constant in the range 1.5~2.0s.

2: To prevent erroneous protection operation, the wiring of A, B, C should be as short as possible.

0

2

tw (s)

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21553-G

TRANSFER-MOLD TYPE

INSULATED TYPE

MAXIMUM RATINGS (Tj = 25C, unless otherwise noted)

INVERTER PART

Symbol

VCC

VCC(surge)

VCES

IC

ICP

PC

Tj

Parameter

Condition

Applied between P-N

Supply voltage

Supply voltage (surge)

Collector-emitter voltage

Each IGBT collector current

Each IGBT collector current (peak)

Collector dissipation

Junction temperature

Ratings

Applied between P-N

Tf = 25C

Tf = 25C, instantaneous value (pulse)

Tf = 25C, per 1 chip

(Note 1)

450

500

600

10

20

25

20~+150

Unit

V

V

V

A

A

W

C

Note 1 : The maximum junction temperature rating of the power chips integrated within the DIP-IPM is 150C (@ Tf 100C). However, to

ensure safe operation of the DIP-IPM, the average junction temperature should be limited to Tj(ave) 125C (@ T f 100C).

CONTROL (PROTECTION) PART

Symbol

VD

Parameter

Control supply voltage

VDB

Control supply voltage

VCIN

Input voltage

VFO

Fault output supply voltage

Fault output current

Current sensing input voltage

IFO

VSC

Condition

Applied between VP1-VNC , VN1 -VNC

Applied between VUFB -VUFS, VVFB-V VFS,

VWFB-VWFS

Applied between UP, VP, WP-VNC,

UN, VN, WN-VNC

Applied between FO-VNC

Sink current at F O terminal

Applied between CIN-V NC

Ratings

20

Unit

V

20

0.5~+5.5

0.5~VD+0.5

15

0.5~VD+0.5

V

mA

V

Ratings

Unit

400

20~+100

40~+125

C

C

2500

Vrms

TOTAL SYSTEM

Symbol

Parameter

VCC(PROT) Self protection supply voltage limit

(short-circuit protection capability)

Heat-fin operation temperature

Tf

Tstg

Storage temperature

Viso

Isolation voltage

Condition

VD = 13.5~16.5V, Inverter part

Tj = 125C, non-repetitive, less than 2 s

(Note 2)

60Hz, Sinusoidal, AC 1 minute, connection

pins to heat-sink plate

Note 2 : Tf MEASUREMENT POINT

Al Board Specifications:

Dimensions 100 100 10mm, finishing: 12s, warp: 50~100m

Control Terminals

FWD Chip

18mm

IGBT/FWD Chip

16mm

Al Board

Groove

IGBT Chip

Temp. measurement

point

(inside the Al board)

Temp. measurement point

(inside the Al board)

Power Terminals

100~200m of evenly applied Silicon-Grease

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21553-G

TRANSFER-MOLD TYPE

INSULATED TYPE

THERMAL RESISTANCE

Symbol

Rth(j-f)Q

Rth(j-f)F

Parameter

Junction-to-heat sink thermal

resistance

Limits

Condition

Inverter IGBT part (per 1/6 module)

Inverter FWD part (per 1/6 module)

Min.

Typ.

Max.

5.0

6.5

Unit

C/W

Note 3 : Grease with good thermal conductivity should be applied evenly about +100m ~ +200m on the contact surface of a DIP-IPM and a

Heat sink.

ELECTRICAL CHARACTERISTICS (Tj = 25C, unless otherwise noted)

INVERTER PART

Symbol

Condition

Parameter

VCE(sat)

Collector-emitter saturation

voltage

VEC

ton

trr

tc(on)

toff

tc(off)

FWD forward voltage

ICES

Collector-emitter cut-off

current

IC = 10A, Tj = 25C

VD = VDB = 15V

VCIN = 0V

IC = 10A, Tj = 125C

Tj = 25C, IC = 10A, VCIN = 5V

VCC = 300V, VD = VDB =15V

IC = 10A, Tj = 125C

Switching times

Inductive load (upper-lower arm)

VCIN = 5 0V

VCE = VCES

Tj = 25C

Tj = 125C

Limits

Typ.

Max.

1.80

1.90

2.10

0.60

0.10

0.20

1.10

0.35

2.45

2.60

2.85

1.10

0.60

2.20

1.25

1

10

Min.

Limits

Typ.

Max.

13.5

13.5

4.9

0.8

15.0

15.0

0.8

1.2

16.5

16.5

8.50

1.00

1.2

1.8

0.45

10.0

10.5

10.3

10.8

1.0

0.8

2.5

0.5

1.8

1.4

3.0

0.55

12.0

12.5

12.5

13.0

2.0

4.0

V

V

V

V

V

ms

V

V

Min.

0.10

Unit

V

V

s

s

s

s

s

mA

CONTROL (PROTECTION) PART

Symbol

Parameter

Condition

VD

VDB

Control supply voltage

Control supply voltage

ID

Circuit current

VFOH

VFOL

VFOsat

Fault output voltage

VSC = 0V, FO = 10k 5V pull-up

VSC = 1V, FO = 10k 5V pull-up

VSC = 1V, IFO = 15mA

tdead

Arm shoot-through blocking time

Relates to corresponding input signal for blocking arm

shoot-through.

20C Tf 100C

VSC(ref)

UVDBt

UVDBr

UVDt

UVDr

tFO

Vth(on)

Vth(off)

Short-circuit trip level

Supply circuit under-voltage

protection

Fault output pulse width

ON threshold voltage

OFF threshold voltage

Applied between VP1-VNC, VN1-VNC

Applied between VUFB-VUFS, VVFB-VVFS , VWFB-VWFS

Total of VP1-VNC , VN1-VNC

VD = VDB =15V

VUFB-VUFS, VVFB -VVFS, VWFB-VWFS

VCIN = 5V

Tj = 25C, VD = 15V

Trip level

Reset level

Tj 125C

Trip level

Reset level

(Note 4)

CFO = 22nF

Applied between:

UP, VP, WP-VNC, U N, VN, WN-VNC

(Note 5)

Unit

V

V

mA

V

V

V

Note 4 : Short-circuit protection operates only at the low-arms. Please select the value of the external shunt resistor such that the SC trip level

is less than 17A

5 : Fault signal is outputted when the low-arm short-circuit or control supply under-voltage protective functions operate. The fault output

pulse-width tFO depends on the capacitance value of CFO according to the following approximate equation. : CFO = (12.2 10-6) tFO [F]

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21553-G

TRANSFER-MOLD TYPE

INSULATED TYPE

MECHANICAL CHARACTERISTICS AND RATINGS

Parameter

Condition

Mounting torque

Terminal pulling strength

Bending strength

Weight

Heat-sink flatness

Mounting screw : M3

Weight 9.8N

Weight 4.9N. 90deg bend

EIAJ-ED-4701

EIAJ-ED-4701

(Note 6)

Min.

0.59

10

2

50

Limits

Typ.

0.78

20

Max.

0.98

100

Min.

Limits

Typ.

Max.

Unit

Nm

s

times

g

m

Note 6: Measurement point of heat-sink flatness

DIP-IPM

+

Measurement Range

3mm

Heat-sink

+

Heat-sink

RECOMMENDED OPERATION CONDITIONS

Symbol

Parameter

VCC

VD

VDB

VD, VDB

tdead

fPWM

VCIN(ON)

VCIN(OFF)

Supply voltage

Control supply voltage

Control supply voltage

Control supply variation

Arm shoot-through blocking time

PWM input frequency

Input ON voltage

Input OFF voltage

Condition

Applied between P-N

Applied between VP1-VNC, V N1-VNC

Applied between VUFB-VUFS, V VFB-VVFS, V WFB-VWFS

Relates to corresponding input signal for blocking arm shoot-through

Tj 125C, Tf 100C

Applied between UP, VP, W P-VNC, UN, VN, WN-VNC

0

13.5

13.5

1

3

300

15.0

15.0

15

0~0.65

4.0~5.5

400

16.5

16.5

1

Unit

V

V

V

V/s

s

kHz

V

V

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21553-G

TRANSFER-MOLD TYPE

INSULATED TYPE

Fig. 4 THE DIP-IPM INTERNAL CIRCUIT

DIP-IPM

VUFB

VUFS

VP1

UP

HVIC 1

VCC

Di1

IGBT1

VB

HO

IN

VS

COM

VVFB

VVFS

VP1

VP

HVIC 2

Di2

IGBT2

VB

VCC

HO

IN

VS

COM

VWFB

VWFS

HVIC 3

VP1

VCC

WP

IN

Di3

IGBT3

VB

HO

COM

VS

LVIC

IGBT4

Di4

IGBT5

Di5

IGBT6

Di6

UOUT

VN1

VCC

VOUT

UN

UN

VN

VN

WN

WN

Fo

Fo

WOUT

VNO

CIN

VNC

GND

VNO(NC)

N

CFO

CFO

CIN

Note: The IGBTs gates and the HVICs COM terminals are connected to the dummy pins.

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21553-G

TRANSFER-MOLD TYPE

INSULATED TYPE

Fig. 5 TIMING CHARTS OF THE DIP-IPM PROTECTIVE FUNCTIONS

[A] Short-Circuit Protection (N-side only)

(For the external shunt resistor and CR connection, please refer to Fig. 3.)

a1. Normal operation : IGBT ON and carrying current.

a2. Short-circuit current detection (SC trigger).

a3. IGBT gate interrupt.

a4. IGBT turns OFF.

a5. FO timer operation starts : The pulse width of the F O signal is set by the external capacitor CFO.

a6. Input H : IGBT OFF state.

a7. Input L : IGBT ON state.

a8. IGBT OFF state.

N-side control input

a6

Protection circuit state

a7

SET

Internal IGBT gate

RESET

a3

a2

SC

a4

a1

Output current Ic(A)

a8

SC reference voltage

Sense voltage of the

shunt resistor

CR circuit time constant DELAY

Fault output Fo

a5

[B] Under-Voltage Protection (N-side, UVD)

a1. Normal operation : IGBT ON and carrying current.

a2. Under-voltage trip (UVDt).

a3. IGBT OFF in spite of control input condition.

a4. FO timer operation starts.

a5. Under-voltage reset (UVDr).

a6. Normal operation : IGBT ON and carrying current.

Control input

Protection circuit state

Control supply voltage VD

RESET

SET

UVDr

UVDt

a5

a2

a1

a3

a6

Output current Ic(A)

Fault output Fo

a4

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21553-G

TRANSFER-MOLD TYPE

INSULATED TYPE

[C] Under-Voltage Protection (P-side, VDB)

a1. Control supply voltage rises : After the voltage level reachs UVDBr, the circuits start to operate when the next input is applied.

a2. Normal operation : IGBT ON and carrying current.

a3. Under-voltage trip (UVDBt).

a4. IGBT OFF in spite of control input condition (there is no FO signal output).

a5. Under-voltage reset (UVDBr).

a6. Normal operation : IGBT ON and carrying current.

Control input

Protection circuit state

RESET

SET

RESET

UVDBr

Control supply voltage VDB

a1

UVDBt

a2

a5

a3

a4

a6

Output current Ic(A)

High-level (no fault output)

Fault output Fo

Fig. 6 RECOMMENDED CPU I/O INTERFACE CIRCUIT

5V line

DIP-IPM

5.1k

4.7k

UP,VP,WP,UN,VN,WN

Fo

CPU

1nF

1nF

VNC (GND)

Note : RC coupling at each input (parts shown dotted) may change depending on the

PWM control scheme used in the application and on the wiring impedance of

the applications printed circuit board.

Sep. 2001

MITSUBISHI SEMICONDUCTOR <Intelligent Power Module>

PS21553-G

TRANSFER-MOLD TYPE

INSULATED TYPE

Fig. 7 TYPICAL DIP-IPM APPLICATION CIRCUIT EXAMPLE

C1: Tight tolerance temp - compensated electrolytic type; C2,C3: 0.22~2 F R - category ceramic capacitor for noise filtering

5V line

C2

VUFB

C1

VUFS

DIP-IPM

P

VP1

C3

UP

VCC

VB

IN

HO

COM

VS

VCC

VB

C2

VVFB

C1

VVFS

VP1

C3

VP

IN

HO

COM

VS

VCC

VB

IN

HO

C2

VWFB

C1

C

P

U

VWFS

VP1

C3

WP

U

N

I

T

COM

VS

UOUT

C3

VN1

VCC

5V line

VOUT

UN

VN

WN

Fo

UN

VN

WOUT

If this wiring is too long,

short circuit might

be caused.

WN

Fo

VNO

CIN

VNC

GND

CFO

C

15V line

CFO

CIN

C4(CFO )

A

The long wiring of GND might generate

noise on input signals and cause IGBT

to be malfunctioned.

B

C5

R1

Shunt

resistor

If this wiring is too long, the SC level

fluctuation might be large and cause

SC malfunction.

N1

Note 1 : To prevent the input signals oscillation, an RC coupling at each input is recommended, and the wiring of each input should be as short

as possible (less than 2cm).

2 : By virtue of integrating an application specific type HVIC inside the module, direct coupling to CPU terminals without any opto-coupler

or transformer isolation is possible.

3 : FO output is open collector type. This signal line should be pulled up to the positive side of the 5V power supply with approximately

5.1k resistance.

4 : FO output pulse width should be decided by connecting an external capacitor between CFO and VNC terminals (C FO). (Example : CFO

= 22 nF tFO = 1.8 ms (typ.))

5 : Each input signal line should be pulled up to the positive side of the 5V power supply with approximately 4.7k resistance (other RC

coupling circuits at each input may be needed depending on the PWM control scheme used and on the wiring impedances of the

systems printed circuit board). Approximately a 0.22~2F by-pass capacitor should be used across each power supply connection

terminals.

6 : To prevent errors of the protection function, the wiring of A, B, C should be as short as possible.

7 : In the recommended protection circuit, please select the R1C5 time constant in the range of 1.5~2s.

8 : Each capacitor should be put as nearby the terminals of the DIP-IPM as possible.

9 : To prevent surge destruction, the wiring between the smoothing capacitor and the P&N1 terminals should be as short as possible. Approximately a 0.1~0.22F snubber capacitor between the P&N1 terminals is recommended.

Sep. 2001

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

Você também pode gostar

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (120)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Datasheet MEC Floorscanner v03 2014Documento2 páginasDatasheet MEC Floorscanner v03 2014pitichai_pAinda não há avaliações

- DSE6110 MKIII DSE6120 MKIII Installation Instructions PDFDocumento2 páginasDSE6110 MKIII DSE6120 MKIII Installation Instructions PDFjorge100% (3)

- Eaton Exrt 5-11 KvaDocumento76 páginasEaton Exrt 5-11 KvaAxel CastaAinda não há avaliações

- ID DCU IndustrialDocumento4 páginasID DCU IndustrialRoozbeh BahmanyarAinda não há avaliações

- Real Time Audio Signal Processing SystemtDocumento24 páginasReal Time Audio Signal Processing SystemtradhikasontakayAinda não há avaliações

- Subaru Eh Engines Eh36 Eh41 PartsDocumento28 páginasSubaru Eh Engines Eh36 Eh41 PartsMutu DanielAinda não há avaliações

- Green Cloud ComputingDocumento9 páginasGreen Cloud ComputingJohn SinghAinda não há avaliações

- Flyback Transformers 10 To 16 W El 19Documento1 páginaFlyback Transformers 10 To 16 W El 19ikaro181083Ainda não há avaliações

- Downloaded From Manuals Search EngineDocumento128 páginasDownloaded From Manuals Search EngineRoozbeh BahmanyarAinda não há avaliações

- Sample Program: XGB-INV IG5A (RS-485 Modbus RTU)Documento4 páginasSample Program: XGB-INV IG5A (RS-485 Modbus RTU)Roozbeh BahmanyarAinda não há avaliações

- Delta Programmable Logic Controller DVP Series: Automation For A Changing WorldDocumento52 páginasDelta Programmable Logic Controller DVP Series: Automation For A Changing Worlddetroja tusharAinda não há avaliações

- FL 912 Genset EN-1Documento2 páginasFL 912 Genset EN-1Farhad GhaffarAinda não há avaliações

- TL7705ACPDocumento17 páginasTL7705ACProozbehxoxAinda não há avaliações

- BY229 (X, B) - 200 Thru BY229 (X, B) - 800: Vishay General SemiconductorDocumento5 páginasBY229 (X, B) - 200 Thru BY229 (X, B) - 800: Vishay General SemiconductorroozbehxoxAinda não há avaliações

- Vish k847pDocumento9 páginasVish k847pRoozbeh BahmanyarAinda não há avaliações

- 2 Tle4276Documento20 páginas2 Tle4276Roozbeh BahmanyarAinda não há avaliações

- Im662 Sae400Documento34 páginasIm662 Sae400Roozbeh BahmanyarAinda não há avaliações

- Irf7341Qpbf: Typical ApplicationsDocumento9 páginasIrf7341Qpbf: Typical ApplicationsRoozbeh BahmanyarAinda não há avaliações

- 0 J 4804 Uh 2 FJ 973 Ol 0 PQCZGSX 987 yDocumento5 páginas0 J 4804 Uh 2 FJ 973 Ol 0 PQCZGSX 987 yRoozbeh BahmanyarAinda não há avaliações

- DS2431 PDFDocumento27 páginasDS2431 PDFscribd2827Ainda não há avaliações

- Uc 3717 ADocumento12 páginasUc 3717 ARoozbeh BahmanyarAinda não há avaliações

- Voltage Regulator: Semiconductor Technical DataDocumento9 páginasVoltage Regulator: Semiconductor Technical DataEnriqueAinda não há avaliações

- CMD PriceDocumento2 páginasCMD PriceRoozbeh BahmanyarAinda não há avaliações

- CMD PriceDocumento2 páginasCMD PriceRoozbeh BahmanyarAinda não há avaliações

- CMD Pricelist MasterDocumento2 páginasCMD Pricelist MasterRoozbeh BahmanyarAinda não há avaliações

- 00967ADocumento18 páginas00967ASendhilKumarAinda não há avaliações

- Certificat ISO 14001 enDocumento3 páginasCertificat ISO 14001 enRoozbeh BahmanyarAinda não há avaliações

- BDocumento4 páginasBRoozbeh Bahmanyar100% (1)

- 2 Pole: 1 Phase IP21 or IP23Documento2 páginas2 Pole: 1 Phase IP21 or IP23Roozbeh BahmanyarAinda não há avaliações

- 2012061315052731Documento4 páginas2012061315052731Roozbeh BahmanyarAinda não há avaliações

- Powerpack 200 CumminsDocumento1 páginaPowerpack 200 CumminsRoozbeh BahmanyarAinda não há avaliações

- SS8 CPGKDocumento4 páginasSS8 CPGKRoozbeh BahmanyarAinda não há avaliações

- C200D6 enDocumento2 páginasC200D6 enRoozbeh BahmanyarAinda não há avaliações

- Sae400 Severe Duty Im727Documento33 páginasSae400 Severe Duty Im727Roozbeh BahmanyarAinda não há avaliações

- 6ctaa83 G3 PDFDocumento2 páginas6ctaa83 G3 PDFShahzad AliAinda não há avaliações

- NATM InstrumentDocumento23 páginasNATM Instrumentthuy giangAinda não há avaliações

- Issues in DB Mirroring Log Shipping ClusteringDocumento1 páginaIssues in DB Mirroring Log Shipping ClusteringPrageet SurheleyAinda não há avaliações

- Lab 1 Development Environment and Basic Constructs in JavaDocumento11 páginasLab 1 Development Environment and Basic Constructs in Javadavid jhonAinda não há avaliações

- Add Two 8 Bit Numbers and Show The Result in DecimalDocumento3 páginasAdd Two 8 Bit Numbers and Show The Result in DecimalAmeenSonuAinda não há avaliações

- Product Data Filtering: User's GuideDocumento34 páginasProduct Data Filtering: User's GuideashkansoheylAinda não há avaliações

- PC Max86150 Breakout Qwiic2part Part1Documento1 páginaPC Max86150 Breakout Qwiic2part Part1AwadhAinda não há avaliações

- Constant Current BiasDocumento72 páginasConstant Current BiasMithilesh N KumarAinda não há avaliações

- Schimbare Semering UleiDocumento19 páginasSchimbare Semering Uleiradu2000vAinda não há avaliações

- JVM Internals & Runtime Data AreasDocumento13 páginasJVM Internals & Runtime Data AreaskannangceAinda não há avaliações

- SD2Vita - The Ultimate Guide Is HereDocumento14 páginasSD2Vita - The Ultimate Guide Is HerePatrick JeanAinda não há avaliações

- Difference Between Char and VarcharDocumento3 páginasDifference Between Char and VarcharPavan KumarAinda não há avaliações

- Apollo User Manual PDFDocumento43 páginasApollo User Manual PDFAngel Nahun RiveraAinda não há avaliações

- MCMC Sheldon RossDocumento68 páginasMCMC Sheldon RossMuhamadSukinAinda não há avaliações

- FC101 Product OverviewDocumento8 páginasFC101 Product OverviewMuhammad Irfan HameedAinda não há avaliações

- Zenith c32v23 Service ManualDocumento81 páginasZenith c32v23 Service Manualshaft12100% (1)

- Motoman Mh5f ManualDocumento66 páginasMotoman Mh5f ManualschrienerAinda não há avaliações

- FANUC System PMC Introduction: Origin: Input Time: 07-06-05 02:32:28Documento8 páginasFANUC System PMC Introduction: Origin: Input Time: 07-06-05 02:32:28occhityaAinda não há avaliações

- Visual Basic 6+ - ExcelDocumento5 páginasVisual Basic 6+ - ExcelHimanshu VermaAinda não há avaliações

- FUS100 LIS EnglishDocumento13 páginasFUS100 LIS EnglishFelipe MancillaAinda não há avaliações

- AC Stag 300 ISA2 - ManualDocumento45 páginasAC Stag 300 ISA2 - ManualnixonbnAinda não há avaliações

- Layer 2 Tunnel Protocol Version 3 - CiscoDocumento117 páginasLayer 2 Tunnel Protocol Version 3 - CiscoВладан ДакићAinda não há avaliações

- Spesifikasi Hardware Workstation Include SIMSCADA + Maintenance ServiceDocumento2 páginasSpesifikasi Hardware Workstation Include SIMSCADA + Maintenance Servicefajar riansyahAinda não há avaliações

- 4.1 Xbox Case StudyDocumento3 páginas4.1 Xbox Case StudySuhel Md RezaAinda não há avaliações

- Сигейт F3 Serial Port DiagnosticsDocumento60 páginasСигейт F3 Serial Port Diagnosticssvm9050% (2)

- ARP PoisoningDocumento22 páginasARP Poisoningrazorblademk2Ainda não há avaliações