Escolar Documentos

Profissional Documentos

Cultura Documentos

S/H Time Basics

Enviado por

rahul shiv shankarTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

S/H Time Basics

Enviado por

rahul shiv shankarDireitos autorais:

Formatos disponíveis

Understanding the basics of setup and hold time ...

http://www.edn.com/design/analog/4371393/Unde...

EDN MOMENT

Steve Jobs

leaves Apple

Computer,

September 16,

About Us

DESIGN CENTERS

Subscribe to Newsletters

TOOLS & LEARNING

COMMUNITY

EDN VAULT

Search

Login | Register

Home > Analog Design Center > How To Article

Understanding the basics of setup and hold time

Deepak Behera, Karthik Rao C.G. and Deepak Mahajan, Freescale Semiconductor -April 19,

2012

15 Comments

To understand why setup and hold time arises in a flip-flop one needs to begin by looking at its

basic function. These flip-flop building blocks include inverters and transmission gates. Inverters

are used to invert the input. It is important here to note its characteristic voltage transfer curve

(See Figure 1).

Figure 1. A basic building block of a flip-flop, an inverter features a characteristic voltage

transfer curve.

A transmission gate, denoted by Tx throughout the article, is a parallel connection of nMOS and

pMOS with complementary inputs to both MOSFETs (see Figure 2). Bidirectional, it carries current

in either direction. Depending on the voltage on the gate, the connection between the input and

output is either low-resistance or high-resistance, so that Ron = 100 or less and Roff > 5 M.

This effectively isolates the output from the input.

Figure 2. A transmission gate, shown here with a truth table, is a parallel connection of

nMOS and pMOS with complementary inputs to both MOSFETs.

Whenever both nMOS and pMOS are turned on, any signal '1' or '0' passes equally well without

1 of 10

09/17/2016 06:56 PM

Understanding the basics of setup and hold time ...

http://www.edn.com/design/analog/4371393/Unde...

degradation. The use of transmission gates eliminates undesirable threshold voltage effects which

give rise to loss of logic levels.

The transistor level structure of a D flip-flop contains two 'back-to-back' inverters known as a

'latching circuit,' since it retains a logic value. Immediately after the D input, an inverter may or

may not be present (See Figure 3).

Figure 3. The transistor level structure of D flip-flop contains two back-to-back inverters

known as a'latching circuit.

Normal operation of a flip-flop

In order to visualize normal operations of a flip-flop (See Figure 4), in 4a, initially D = 0 and CLK

is LOW. Input follows the path D-W-X-Y-Z and finally Z = 0. We are neglecting the 'latching circuit'

on RHS for the time being.

Figure 4. The workings of a D flip-flop whereby the darkened line shows the conducting

path.

When the CLK is HIGH (See 4b), latching circuit on LHS is enabled. It latches 1, which results in

Q = 0 (which is what it should be for D = 0). Note that the output arrives at the positive edge of

CLK. Hence it is a positive edge triggered flip-flop.

2 of 10

09/17/2016 06:56 PM

Understanding the basics of setup and hold time ...

http://www.edn.com/design/analog/4371393/Unde...

When the CLK is LOW, the RHS latching circuit is enabled (See 4c) and there is no change in

output. Any change in input is reflected at node Z which is reflected in the output at the next

positive edge of CLK.

In summary, if D changes, the change would reflect only at node Z when CLK is LOW and it

would appear at the output only when the CLK is HIGH.

It is here that we introduce SETUP and HOLD time. Setup time is defined as the minimum

amount of time before the clock's active edge that the data must be stable for it to be latched

correctly. Any violation may cause incorrect data to be captured, which is known as setup

violation.

Hold time is defined as the minimum amount of time after the clock's active edge during which

data must be stable. Violation in this case may cause incorrect data to be latched, which is known

as a hold violation. Note that setup and hold time is measured with respect to the active clock

edge only.

Reason for SETUP Time:

Figure: 5. The time it takes data D to reach node Z is called the setup time.

In Figure 5, when D = 0 and CLK is LOW, input D is reflected at node Z so that W = 1, Y = 0,

and Z = 1 and it will take some time to traverse the path D-W-X-Y-Z. The time that it takes data D

to reach node Z is called the SETUP time. When the CLK is HIGH, T1 is switched OFF and T2 is

switched ON. Therefore, the LHS 'latching circuit' kicks into action latching the value present at

node Z, and producing it in the output (Q = 0 and Q' = 1).

It is indispensable for node Z to have a stable value by then. Any data sent before the setup time,

as defined above, will produce a stable value at node Z. This defines the reason for the setup

time within a flop.

Reason for HOLD Time:

Figure 6. The darkened line shows the conducting path for hold time.

As previously indicated, HOLD time is measured with respect to the active CLK edge only. In

Figure 6, input data D is given to the inverter, or any other logic sitting before transmission gate

T1, and is a part of the flip-flop. The CLK and CLK BAR in Figure 6 that controls the switching of

the transmission gates, come after the ramping up of the CLK signal, i.e. after passing through

buffers and inverters.

There is a finite delay between the CLK and CLK BAR so that the transmission gate takes some

time to switch on or off. In the meantime it is necessary to maintain a stable value at the input to

ensure a stable value at node W, which in turn translates to the output, defining the reason for

3 of 10

09/17/2016 06:56 PM

Understanding the basics of setup and hold time ...

http://www.edn.com/design/analog/4371393/Unde...

hold time within a flop.

A finite positive setup time always occurs, however hold time can be positive, zero, or even

negative. Let's look at why and how this can be true. As discussed earlier, there may be

combinational logic sitting before the first transmission gate to make the flop set-reset-enable or

scan-enable, possibly for yet another reason. This introduces a certain delay in the path of input

data D to reach the transmission gate. This delay establishes whether the hold time is positive,

negative, or zero.

In Figure 7, Tinitial is the time delay introduced by the combinational logic sitting before the first

transmission gate and TTX is the time taken for the transmission gate to switch ON or OFF after

the CLK and CLK BAR is given. The relationship between Tinitial and TTX gives rise to the

various types of hold time that exist.

Figure 7. The relationship between Tinitial and TTX establishes various types of hold time

The relationship between Tinitial and TTX in Figure 8 further clarifies positive, zero, and negative

hold time.

Figure: 8. Relationships that establish positive, zero, and negative hold time. Adjusting the

TTX changes the hold margin.

In Figure 8, CLK represents the clock with an active rising edge, D1, D2 and D3 represent various

data signals, S represents the setup margin, and H1, H2, and H3 denotes the respective hold

margins. TTX indicates the time taken for the transmission gate to switch ON or OFF after the

CLK and CLK BAR arrive, and Tinitial is the time delay introduced by the combinational logic

sitting before the first transmission gate. Since HOLD margin is always decided with respect to

the active clock edge, playing with the TTX will change the hold margin.

About the authors:

Deepak Behera is a design engineer with experience in signal integrity and package designing

and analysis. Karthik Rao C.G. is a design engineer with experience in digital IP design. Deepak

Mahajan is a design Engineer with experience in SoC verification.

15 Comments

Write a Comment

4 of 10

09/17/2016 06:56 PM

Understanding the basics of setup and hold time ...

http://www.edn.com/design/analog/4371393/Unde...

To comment

please Log In

CauN060

Great!!!

Base on the above circuit, how to calculate the

minimum pulse width of CLK pin. Tks a lot!

Aug 14, 2016 11:41 PM EDT

0|

Reply

Jon Fuge

An excellent and very well written article; thank you for

submitting this, I will be referring colleagues to this for

many years.

Apr 7, 2016 8:41 AM EDT

0|

Reply

Prathameshs19

Thanks a lot for a detailed explaination! :D

Feb 27, 2016 11:50 PM EST

0|

Reply

KarthikR856

Hi DurgeshK461,

Hold time is not just a formality. If there is no setup

violation, stable data has indeed reached point Z (not

just point X). But after the clock edge, there is a

certain time before the transmission gate itself closes

completely. If any new data change now passes

through this gate before its completely closes, the

original data is now corrupted and hence correct data

cannot come out of the RHS latch.

- Karthik Rao C. G.

Sept 25, 2015 3:31 PM EDT

1|

Reply

DurgeshK461

I think the hold requirement is just a formality. because

It is measured from the edge. That means if we think

that there is no set up violation, the stable data has

already reached the point X. So after the edge, even if

we change the input It will not get latched in the first

5 of 10

09/17/2016 06:56 PM

Understanding the basics of setup and hold time ...

http://www.edn.com/design/analog/4371393/Unde...

latch. That means the correct data will come out even

if we have a hold violation. One more thing worth

mentioning that a combi logic sitting before the D input

will also affect teh set up time as it will take more time

for the input to reach the output of latch 1.

Apr 29, 2014 2:54 AM EDT

0|

Reply

jasonkee111

hi

if the clock is not 50% duty cycle, e.g. 80% high 20%

low, does it mean that it is more easier prone to setup

failure? Thanks

Mar 10, 2014 10:44 PM EST

0|

Reply

pekon_

Thank you for such informative article with in-depth

explanation.

[pekon]

Feb 27, 2014 12:16 PM EST

0|

Reply

deependsailor

Superb article..I got it clear now that what exactly

setup and hold time is.

Regards

Deepen

Sept 11, 2013 7:36 AM EDT

0|

Reply

kiran5509

Hello Deepak,

I think i understand the hold time now. The minimum

amount of time the data required to be stable on active

clock edge while T1 and T2 turn off and on

respectively. This article is really top notch a much

needed on.

Thank you,

Manju

Apr 2, 2013 4:08 PM EDT

0|

6 of 10

09/17/2016 06:56 PM

Understanding the basics of setup and hold time ...

http://www.edn.com/design/analog/4371393/Unde...

Reply

kiran5509

The conducting path during rise edge is from Z to Q

right. But during explanation of hold the conduction

path is show from D to W. should the hold time be Z

holding study while the T2 gets turned on?. Kindly

please clarify.

Thank you,

Manju

Apr 2, 2013 4:47 PM EDT

0|

Reply

Sai Govinda Rao

Awesome Article . The whole of my engineering and

even my 1 year job did not help me in giving such a

good reasoned understanding.

Thank You very Much

Aug 2, 2012 2:42 AM EDT

0|

Reply

ddr71m

Hi Saurabh, Very well written article...

Jun 26, 2012 5:30 AM EDT

0|

Reply

Karthik Rao

Hi Saurabh,

That figure essentially consists of two latches

connected in series, with the transmission gates

present to provide the right clock edges to the latches

resulting in a Flip-Flop operation. As mentioned in the

article, the initial inverter stage may or may not be

present in the actual circuit. This inverter, if present is

usually used for adding scan chaining capabilities to

the flip-flop to help check Design For Testability.

Apr 27, 2012 5:42 AM EDT

7 of 10

0|

0|

Reply

09/17/2016 06:56 PM

Understanding the basics of setup and hold time ...

http://www.edn.com/design/analog/4371393/Unde...

anonymous user

I think its more important to understand what happens

when you cannot control setup and hold times. Is their

a good article, without Marketing Fluff, giving concrete

ways to minimize metastability using MSI logic for

those of us who dont use programmable logic

devices?

Apr 26, 2012 1:22 AM EDT

Reply

anonymous user

But sir why do we need such a complex circuit for D

flip flop? This can be made simply by feeding the

output of first d-latch to the second d-latch (i.e. only 2

d-latches in series) with first one driven by clk and

second one by clk'.In my circuit, can you tell me the

cause for setup and hold time?

Apr 22, 2012 2:07 AM EDT

0|

8 of 10

Reply

09/17/2016 06:56 PM

Understanding the basics of setup and hold time ...

Most Popular

http://www.edn.com/design/analog/4371393/Unde...

Most Commented

System level design and

integration challenges with

multiple ADCs on single chip

Understanding the basics of

setup and hold time

Product How-to: Digital

isolators offer easy-to-use

isolated USB option

Managing noise in the signal

chain, Part 2: Noise and

distortion in data converters

War of currents: Tesla vs

Edison

Simple reverse-polarityprotection circuit has no

voltage drop

Control an LM317T with a

PWM signal

Start with the right op amp

when driving SAR ADCs

Helping board designers work

with high-performance timing

Design calculations for robust

I2C communications

FEATURED RESOURCES

Subscribe to RSS:

DESIGN CENTERS

9 of 10

or

MORE EDN

09/17/2016 06:56 PM

Understanding the basics of setup and hold time ...

http://www.edn.com/design/analog/4371393/Unde...

Analog

Medical

Blogs

EDN TV

Automotive

PCB

Design Ideas

Events

Components & Packaging

Power Management Tech Papers

Consumer

Sensors

Courses

DIY

Systems Design

Webinars

IC Design

Test & Measurement

LEDs

Wireless/Networking

GLOBAL NETWORK

EE Times Asia

EE Times China

Taiwan

EDN Asia

EE Times Europe

EDN China

About Us

SUBSCRIBE TO

NEWSLETTERS TODAY!

DON'T MISS ANOTHER

ISSUE OF EDN IN YOUR

INBOX!

EE Times India

EDN Japan

EE Times Japan

EE Times Korea

EE Times

ESC Brazil

UBM Communities

EE Times | EDN | EBN | DataSheets.com | Embedded | TechOnline | Design News | DesignCon | ESC

Working With Us: About | Contact Us | Media Kits

Terms of Service | Privacy Statement | Copyright 2016 UBM All Rights Reserved

10 of 10

09/17/2016 06:56 PM

Você também pode gostar

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (400)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- IEC 60060-2 - High-Voltage Test Techniques - Part 2: Measuring Systems - Edition 3.0Documento19 páginasIEC 60060-2 - High-Voltage Test Techniques - Part 2: Measuring Systems - Edition 3.0ONUR YILMAZAinda não há avaliações

- MCQ EeeDocumento9 páginasMCQ EeeVishal ThakurAinda não há avaliações

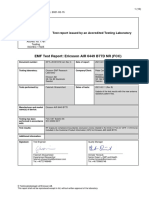

- EMF Test Report: Ericsson AIR 6449 B77D NR (FCC) : Test Report Issued by An Accredited Testing LaboratoryDocumento10 páginasEMF Test Report: Ericsson AIR 6449 B77D NR (FCC) : Test Report Issued by An Accredited Testing LaboratorySilvia OrtegoAinda não há avaliações

- Airport Electrical StandardsDocumento580 páginasAirport Electrical StandardsJayadevDamodaran50% (2)

- Vi Editor Cheat Sheet: Movement CommandsDocumento2 páginasVi Editor Cheat Sheet: Movement Commandsrahul shiv shankarAinda não há avaliações

- VCS CommandsDocumento6 páginasVCS Commandsrahul shiv shankarAinda não há avaliações

- 2017 12 Month Calendar Template One PageDocumento1 página2017 12 Month Calendar Template One Pagerahul shiv shankarAinda não há avaliações

- Soichiro Honda - Wikipedia, The Free EncyclopediaDocumento5 páginasSoichiro Honda - Wikipedia, The Free Encyclopediarahul shiv shankarAinda não há avaliações

- Pa Dalign PDFDocumento12 páginasPa Dalign PDFrahul shiv shankarAinda não há avaliações

- Design of An Efficient FSM For An Implementation of AMBA AHB MasterDocumento5 páginasDesign of An Efficient FSM For An Implementation of AMBA AHB Masterrahul shiv shankarAinda não há avaliações

- Format For Letter of RecommendationDocumento1 páginaFormat For Letter of Recommendationrahul shiv shankarAinda não há avaliações

- Floating ResistorDocumento6 páginasFloating Resistorrahul shiv shankarAinda não há avaliações

- VLSI Logic Test, Validation and Verification Lecture 1, Aug 25, 2004Documento6 páginasVLSI Logic Test, Validation and Verification Lecture 1, Aug 25, 2004rahul shiv shankarAinda não há avaliações

- Dyna 1750Documento2 páginasDyna 1750rahul shiv shankarAinda não há avaliações

- Phase Shift Provided by One Phase Shift Network in RC Phase Shift Oscillator in 3 Stage IsDocumento5 páginasPhase Shift Provided by One Phase Shift Network in RC Phase Shift Oscillator in 3 Stage IsJoyce GeorgeAinda não há avaliações

- Philco DVH 429Documento9 páginasPhilco DVH 429ffabiannAinda não há avaliações

- OMMIC GaN ProcessDocumento22 páginasOMMIC GaN ProcessMario San Miguel MontesdeocaAinda não há avaliações

- Unit 2 - Introduction To Iots - Improving Quality of Life: Week1 AssessmentDocumento30 páginasUnit 2 - Introduction To Iots - Improving Quality of Life: Week1 AssessmentPraghashrajaAinda não há avaliações

- Service-Manual Ivx StandartDocumento480 páginasService-Manual Ivx StandartMarco Antonio ParraAinda não há avaliações

- Thermo Trex Thermocouple Extension WireDocumento2 páginasThermo Trex Thermocouple Extension WireKhin Aung ShweAinda não há avaliações

- Flow Control Parameter ListDocumento21 páginasFlow Control Parameter ListJuan Manuel MuñozAinda não há avaliações

- 787A - Ficha Técnica - Acelerómetro Propósito General Con Salida LateralDocumento1 página787A - Ficha Técnica - Acelerómetro Propósito General Con Salida LateralJhon BaldeonAinda não há avaliações

- Gravity Analog TDS Sensor Meter For Arduino SKU SEN0244-DFRobotDocumento9 páginasGravity Analog TDS Sensor Meter For Arduino SKU SEN0244-DFRobotTOP ZJRAinda não há avaliações

- SA350.5 Directional AntennasDocumento1 páginaSA350.5 Directional Antennasmstin22Ainda não há avaliações

- Minimization of Power Losses Through Optimal Battery Placement in A Distributed Network With High Penetration of PhotovoltaicsDocumento16 páginasMinimization of Power Losses Through Optimal Battery Placement in A Distributed Network With High Penetration of Photovoltaicspoulomi gangulyAinda não há avaliações

- MP2x8i NMEA Buffer: Installation and User ManualDocumento2 páginasMP2x8i NMEA Buffer: Installation and User ManualAbdul Wajid MAinda não há avaliações

- Semiconductor MemoriesDocumento81 páginasSemiconductor MemoriesYash DodiaAinda não há avaliações

- Installer Pack v3 2Documento50 páginasInstaller Pack v3 2Chris JefferyAinda não há avaliações

- 624 DS-NLC-wiring Diagram PDFDocumento337 páginas624 DS-NLC-wiring Diagram PDFPopa Mihai100% (1)

- SPN 4334 - Fmi 4 - GHG17Documento5 páginasSPN 4334 - Fmi 4 - GHG17Francisco Javier TorresAinda não há avaliações

- Unit 5 - Electronic Measurement & Instrumentation - WWW - Rgpvnotes.inDocumento12 páginasUnit 5 - Electronic Measurement & Instrumentation - WWW - Rgpvnotes.inRahul kumar singhAinda não há avaliações

- NPT14 MaintenanceDocumento26 páginasNPT14 MaintenanceElver MesaAinda não há avaliações

- Experion Series 8 IO C300 Controller SpecsheetDocumento41 páginasExperion Series 8 IO C300 Controller SpecsheetTÀi VÕAinda não há avaliações

- Midos: Type MVTP Busbar Supervision RelayDocumento4 páginasMidos: Type MVTP Busbar Supervision RelayCandy BobbyAinda não há avaliações

- TFT-LCD - Claa215fa01 - Chunghwa Picture TubesDocumento30 páginasTFT-LCD - Claa215fa01 - Chunghwa Picture TubesLucian TrifinaAinda não há avaliações

- UTC LM324 Linear Integrated Circuit: Quad Operational AmplifiersDocumento5 páginasUTC LM324 Linear Integrated Circuit: Quad Operational Amplifierseduardoguerra155_604Ainda não há avaliações

- Lec.02 - Medium Voltage SwitchgearDocumento22 páginasLec.02 - Medium Voltage SwitchgearAchafi Moussa MahamatAinda não há avaliações

- Lab No. 2 Title: Simulating Opamp Circuit Transient Response in Pspice To Verify The Gain of The CircuitDocumento10 páginasLab No. 2 Title: Simulating Opamp Circuit Transient Response in Pspice To Verify The Gain of The Circuitlearner guyAinda não há avaliações

- Session 1: Conceptualization of Smart Urban Energy SystemsDocumento12 páginasSession 1: Conceptualization of Smart Urban Energy SystemsRamakrishna SagarAinda não há avaliações

- Valhalla Schematic PDFDocumento1 páginaValhalla Schematic PDFelekoss100% (1)