Escolar Documentos

Profissional Documentos

Cultura Documentos

A Fibonacci Coding Technique To Avoid Crosstalk On On-Chip Data Bus

Enviado por

Rahul YadavTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

A Fibonacci Coding Technique To Avoid Crosstalk On On-Chip Data Bus

Enviado por

Rahul YadavDireitos autorais:

Formatos disponíveis

International Journal of Science and Research (IJSR)

ISSN (Online): 2319-7064

A Fibonacci Coding Technique to Avoid Crosstalk

on On-Chip Data Bus

V. N. V. Sathya Prakash1, P. R. Niharika2

1

Associate Professor, School of Electronics & Communication Engineering, RGMCET, Nandyal-518 501, Kurnool (dist), Andhra Pradesh,

India

2

M. Tech (ES), Student, RGMCET, Nandyal-518501, Kurnool (dist), Andhra Pradesh, India

Abstract: As VLSI technology has scale down to the deep sub-micrometer (DSM) technology the global interconnect delay is becoming

a large fraction of the overall delay of a circuit. Additionally, the increasing cross-coupling capacitances between wires on the same

metal layer create a situation where the delay of a wire is strongly dependent on the electrical state of its neighboring wires. So the

crosstalk delay on a data bus is highly dependent on the data patterns transmitted on the data bus. Different crosstalk avoidance coding

schemes have been proposed to increase the bus speed by decreasing the interconnect delay. By exploiting Fibonacci number a family of

Fibonacci coding Techniques is proposed for crosstalk avoidance. The properties of the Fibonacci coding techniques which are used for

crosstalk avoidance are analyzed and show that mathematically, a mapping scheme exists based on the presentation of numbers in the

Fibonacci numeral system. . Compared to the existing techniques these coding techniques require only 23 wires for 16 bit data. The

proposed techniques evaluate the performance details of the Fibonacci coding techniques which avoids the crosstalk Class 4 and Class 3

completely. Hence crosstalk delay reduces which intern improves the overall performance of the system.

Keywords: Deep sub-micrometer technology, Crosstalk, Fibonacci number system

1. Introduction

As VLSI technology has grown into the deep submicrometer (DSM) regime, new challenges are presented to

circuit designers. As one of the key challenges, the

performance of bus based interconnects has become a

bottleneck to the overall system performance. In large

designs [e.g., systems-on chip (SoCs)] where long and wide

global busses are used, interconnect delays often dominate

logic delays.

Once negligible, crosstalk has become a major determinant

of the total power consumption and delay of on-chip buses.

Fig. 1.1 illustrates a simplified on-chip bus model with

crosstalk. The impact of crosstalk in on-chip busses has been

studied as part of the effort to improve the power and speed

characteristics of the on-chip bus interconnects. CL denotes

the load capacitance seen by the driver, which includes the

receiver gate capacitance and also the parasitic wire-tosubstrate parasitic capacitance. CI is the inter-wire coupling

capacitance between adjacent signal lines of the bus. For

DSM processes, CI is much greater than CL [4]. The delay,

which determines the maximum speed of the bus, is limited

by the maximum crosstalk that any wire in the bus incurs. It

has been shown that reducing the crosstalk can boost the bus

performance significantly [1] [2].

Figure.1.1: On-chip bus model with crosstalk

Depend upon the transmission patterns on the wire of interest

and as well as its immediate neighbours on either side the

crosstalk patterns can be classified into 0C, 1C, 2C, 3C, and

4C patterns, respectively.

Class

0c

1c

2c

3c

4c

Table 1: Crosstalk classification

ceff

Transition patterns

cL

cL (1+ )

cL (1+2 )

cL (1+3 )

cL (1+4 )

000 111

011 000

010 000

010 100

010 101

1.1. Crosstalk Classification

As stated in Section 1, the degree of crosstalk in an on-chip

bus is dependent on data transition patterns on the bus. This

model shown in Figure.1.1, the delay Tj of the

given in equation (1) as in [1].

j th wire is

. . . . , . . , 1

Paper ID: 02013307

Several techniques have been proposed in literature to

eliminate crosstalk transitions. A simple technique to

eliminate crosstalk transitions is to insert a shield wire

between every pair of adjacent wires [3].As there is no

activity on shield wires, the shielding (SHD) technique

completely eliminates crosstalk transitions. This technique

can reduce the bus delay by nearly 50%. However, it requires

doubling the number of wires and hence incurs a 100% area

overhead.

Volume 2 Issue 10, October 2013

www.ijsr.net

124

International Journal of Science and Research (IJSR)

ISSN (Online): 2319-7064

*Forbidden pattern coding (FPC) technique [5] prohibits 010

and 101 patterns from code words, which in turn eliminates

crosstalk transitions. It requires 52 wires for a 32-bit bus.

Table 2: NFF Encoding algorithm

Input: d;

rm = d;

for k = m 1 to 1 do

if rk +1 < f k then

* By exploiting Fibonacci number system, a family of

Fibonacci coding techniques for crosstalk avoidance [6] are

proposed, give a generalized framework to generate crosstalk

avoidance codes. For 32-bit data, these coding techniques

require 40 and 46 wires, respectively, as compared to 63

wires required by the SHD technique. For 16-bit data, these

coding techniques require 23 wires, respectively, as

compared to 31 wires required by the SHD technique.

ck = 0;

else

ck =1;

end if

=

rk rk +1 f k .ck ;

end for

2. Fibonacci Number System

This works reports a systematic Crosstalk-free CODEC

design approach which is based on the Fibonacci Numeral

System (FNS). Fibonacci number system of order s, s2,is

defined as S=(Fs,{0,1}), where=(fn) n0 such that

fi = 2i for 0 i s-1

fi =

f i 1 + .......... + fi s for i s.

An integer may have multiple representations in Fibonacci

number system of order s, s2. To overcome the ambiguity

in representing integers in Fibonacci number system of order

s, s2 , a normal-form [8] is defined, wherein each integer

has a unique representation which does not contain s

consecutive bits equal to 1.

3. Exploiting Fibonacci Representation For

Crosstalk Avoidance

Throughout the paper, we use notation dataword and

codeword for data to be encoded and encoded data,

respectively. For every data word, we give a codeword using

Fibonacci number system of order 2 such that the decimal

equivalent of the data word is same as that of the codeword.

3.1 Normal-Form Fibonacci (NFF) Coding Technique

The NFF technique is described in two parts, namely, data

encoding and data transmission. For data encoding, we use

normal-form Fibonacci number system of order 2. For a n-bit

data word,, using the NFF technique, the unique m-bit

codeword, can be generated using NFF encoding algorithm

as shown in Table 2 . Let NFFm be the set of m-bit code

words and it can be generated as follows.

NFF0 =

NFF1 = {0, 1}

NFF

{0 x,10 y | x NFFm +1 , y NFFm }.

=

m+ 2

For example, transmission of NFF code words 0001 and

0010 results in crosstalk transitions in the least significant

two bits. In order to avoid crosstalk transitions, NFF code

words are transmitted using transition signaling (TS)

technique, wherein data to be transmitted is XOR ed with the

data present on the bus.

Paper ID: 02013307

c0 = r1 ;

Output: cm 1cm 2 ..........c0 ;

3.2 Redundant Fibonacci (RF) Coding Technique

We now present a coding technique which does not require

the TS technique to eliminate crosstalk transitions. In the

case of NFF technique, Fibonacci numbers are considered as

the basis elements to generate m-bit codewords. Similar to

the NFF technique, in redundant Fibonacci (RF) coding

technique we consider Fibonacci numbers as the basis

elements with the exception that f0 is used twice. That is, in

order to generate m-bit RF codewords, we consider fm-1, ----,

f0, f0 as the basis elements. As f0 is considered twice in the

RF technique, we get two sets of RF codewords; each is a

complement of the other. We consider these two sets as

redundant Fibonacci (RF) and complement redundant

Fibonacci (CRF) codeword sets. Let RFm be the set of m-bit

RF code words. Then

RF0 =

RF1 = {0,1}

=

{0 x,11y | x RF2 m +1 , y RF2 m }

RF

2 m+ 2

=

RF

{1x, 00 y | x RF2 m + 2 , y RF2 m +1}.

2 m+3

The encoding logic given in [7] can be used for

implementing the RF technique.

3.2 Complement Redundant Fibonacci (CRF) Coding

Technique

CRF codewords are generated by taking bit-wise

complement of each codeword from the set of RF

codewords. Let CRFm be the set of m-bit CRF codewords.

Then

CRFm = { x | x RFm }.

The CRF Encoding algorithm shown in Table3. The code

words for different coding technique are shown in Table 4.

Volume 2 Issue 10, October 2013

www.ijsr.net

125

International Journal of Science and Research (IJSR)

ISSN (Online): 2319-7064

Table 3: CRF Encoding algorithm

Input: d;

rm = d;

for k = m 1 to 1 do

if rk +1 < f k 1 then

2

ck = 0;

else

ck =1;

end if

=

rk rk +1 f k 1.ck ;

end for

c0 = r1 ;

Output:

cm 1cm 2 ..........c0 ;

Figure 4.1: crosstalk classes count for 1000 inputs using

NFF TS coding Technique.

Table 4: Different coding technique code words

Dataword

NFF4

010

101

011

110

111

000

001

010

0010

1000

0100

1001

1010

0000

0001

0010

Fibonacci codeword

NFF4TS

RF4

CRF4

0010

1010

1110

0111

1101

1101

1100

1110

0100

1100

0101

1101

1111

0000

0001

0100

0011

1011

1000

1110

1111

0000

0010

0011

4. Results

The proposed techniques performance is evaluated by

applying 1000 random input patterns for different bus width

(i.e. 3-, 8-, and 16-bit).

Figure 4.2: crosstalk classes count for 1000 inputs using RF

coding Technique.

Figure4.1 describes the performance of NFF coding

technique by applying 1000 random input patterns for

different bus width (i.e. 3-, 8-, and 16-bit).

Figure4.2 describes the performance of RF coding

techniques by applying 1000 random input patterns for

different bus width (i.e. 3-, 8-, and 16-bit).

Figure4.3 describes the performance of CRF coding

technique by applying 1000 random input patterns for

different bus width (i.e. 3-, 8-, and 16-bit).

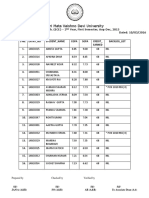

Table 4: The 4c and 3c Cross talk classes comparison

between uncoded and coded bus for 1000 random inputs.

Bus width

Un-coded

4C

3C

coded

RF

4C 3C

0

0

451

NFF

4C 3C

138 0

0

CRF

4C 3C

0

0

442

597

16

1176

671

Figure4.3: crosstalk classes count for 1000 inputs using

CRF coding Technique.

5. Conclusion

By exploiting Fibonacci number system, we proposed a

family of Fibonacci coding techniques for crosstalk

avoidance. Crosstalk avoidance codes have been developed

to reduce the inter-wire crosstalk and therefore boost the

Paper ID: 02013307

Volume 2 Issue 10, October 2013

www.ijsr.net

126

International Journal of Science and Research (IJSR)

ISSN (Online): 2319-7064

maximum speed on the data bus. These coding techniques

require 23 wires for 16-bit data. So the number of wires

requirement is less comparing to shielding technique and

FPF-CAC. Hence the proposed techniques have the

advantage of consuming less area overhead than shielding

technique and FPF-CAC. The proposed techniques avoid the

3c and 4c crosstalk classes completely. The efficiency to

avoid the 3c and 4c crosstalk classes for the proposed

techniques is 100%.

6. Future Scope

The proposed techniques eliminate the 3c and 4c crosstalk

classes completely. We plan to come up with a suitable

mechanism to minimize the Energy dissipation using these

Fibonacci codes.

References

[1] P. Sotiriadis and A. Chandrakasan, Low power bus

coing techniques considering inter-wire capacitance, in

Proc. IEEE-CICC, 2000, pp. 507510.

[2] C. Duan, A. Tirumala, and S. P. Khatri, Analysis and

avoidance of cross - talk in on-chip bus, in Proc. 9th

Symp. High Perform. Interconnects (HOTI), 2001, pp.

133138.

[3] R. Arunachalam, E.Acar, and S. Nassif, Optimal

shielding/spacing metrics for low power design, in proc.

IEEE Comput. Soc. Annu. Symp. VLSI, 2003, pp. 167

172.

[4] S. P. Khatri, Cross-talk noise immune VLSI design,

using regular layout fabrics, Ph.D. dissertation, Dept.

Elect. Eng. Computer science, unv California, Berkeley,

1999.

[5] C. Duan, V. C. Calle, and S. Khatri, Efficient on-chip

crosstalk avoidance codec design, IEEE Trans. Very

Large Scale Integr. (VLSI)Syst., vol. 17, no. 4, pp. 551

560, Apr 2009.

[6] Madhu Mutyam, Fibonacci codes for Crosstalk

avoidance, IEEE Trans on Very Large Scale Integration. (VLSI) syst. vol. 20, no.10, October 2012.

[7] C. Duan, C. Zhu, and S. Khatri, Forbidden transitions

free crosstalk avoidance codec design, in Proc. Design

Autom. Conf., 2008, pp.986991.

[8] W. Kautz, Fibonacci codes for synchronization

Control,IEEE Trans. Inf. Theory, vol.11, no.2, pp. 284

292, Apr. 1965.

Author Profile

Mr. V. N. V. Sathya Prakash received the B-tech degree from the

JNTU, Electronics and communication and M-tech Degree from

SVU, Tirupati in Andhra Pradesh. Currently he is as an Associate

professor in Rajeev Gandhi Memorial College of Engineering And

Technology. His research interests on Digital signal Processing and

high speed, low power VLSI designs.

P. R. Niharika received the B-tech degree from Vaagdevi Institute

of Technology and Sciences (JNTUA), in Electronics and

communication. And pursuing M. Tech Degree in Rajeev Gandhi

Memorial College of Engineering And Technology in the

specialization Embedded System. My research interest on high

speed, low power VLSI designs.

Paper ID: 02013307

Volume 2 Issue 10, October 2013

www.ijsr.net

127

Você também pode gostar

- Error-Correction on Non-Standard Communication ChannelsNo EverandError-Correction on Non-Standard Communication ChannelsAinda não há avaliações

- 1 s2.0 S2212017314004368 MainDocumento7 páginas1 s2.0 S2212017314004368 Mainbenesseddik.abdessalemeAinda não há avaliações

- Performance Improvement of Mc-Cdma System Through DSTBC Site DiversityDocumento8 páginasPerformance Improvement of Mc-Cdma System Through DSTBC Site Diversityمحمد الطراونهAinda não há avaliações

- Orthogonal Code Generator For 3G Wireless Transceivers: Boris D. Andreev, Edward L. Titlebaum, and Eby G. FriedmanDocumento4 páginasOrthogonal Code Generator For 3G Wireless Transceivers: Boris D. Andreev, Edward L. Titlebaum, and Eby G. FriedmanSrikanth ChintaAinda não há avaliações

- Development of Wimax Physical Layer Building BlocksDocumento5 páginasDevelopment of Wimax Physical Layer Building BlocksSandeep Kaur BhullarAinda não há avaliações

- Ubicc 200 200Documento7 páginasUbicc 200 200Ubiquitous Computing and Communication JournalAinda não há avaliações

- Fibonacci Codes For Crosstalk Avoidance: Sireesha Kondapalli, Dr. Giri Babu KandeDocumento7 páginasFibonacci Codes For Crosstalk Avoidance: Sireesha Kondapalli, Dr. Giri Babu KandePronadeep BoraAinda não há avaliações

- An Experimental Study To Reduce The Effect of ICI in OFDM Based WLAN SystemDocumento4 páginasAn Experimental Study To Reduce The Effect of ICI in OFDM Based WLAN SystemSandeep Kaur BhullarAinda não há avaliações

- A Preamble Sequence Design Techniqe For Efficient Beam ID Detection in Millimeter-Wave Cellular SystemsDocumento6 páginasA Preamble Sequence Design Techniqe For Efficient Beam ID Detection in Millimeter-Wave Cellular Systemsshapour2Ainda não há avaliações

- 2 DS-CDMA With MRC: U U I I IDocumento5 páginas2 DS-CDMA With MRC: U U I I INasir KhanAinda não há avaliações

- Crosstalk Avoidance using Fibonacci Code Word for Sub Micrometer on Soc ApplicationDocumento4 páginasCrosstalk Avoidance using Fibonacci Code Word for Sub Micrometer on Soc ApplicationPronadeep BoraAinda não há avaliações

- Exams INWK 6113Documento102 páginasExams INWK 6113shiva_201185Ainda não há avaliações

- Performance Analysis of Spreading and Modulation in WCDMA UplinkDocumento5 páginasPerformance Analysis of Spreading and Modulation in WCDMA UplinkseventhsensegroupAinda não há avaliações

- Comparison of OFDM, SC-FDMA and MC-CDMA As AccessDocumento7 páginasComparison of OFDM, SC-FDMA and MC-CDMA As AccessFarman Ullah100% (1)

- BER of OFDM System Using Concatenated Forward Error Correcting Codes (FEC) Over Nakagami-M Fading ChannelDocumento5 páginasBER of OFDM System Using Concatenated Forward Error Correcting Codes (FEC) Over Nakagami-M Fading Channelseventhsensegroup100% (1)

- VLSI Implementation of Sphere Decoding for Wide-Band MIMO Systems Minimizes Area-DelayDocumento27 páginasVLSI Implementation of Sphere Decoding for Wide-Band MIMO Systems Minimizes Area-DelayVimalAinda não há avaliações

- Exam #2 For Computer Networks (CIS 6930) SOLUTIONS : Problem #1Documento4 páginasExam #2 For Computer Networks (CIS 6930) SOLUTIONS : Problem #1svahidsAinda não há avaliações

- Parallel CRC GeneratorDocumento20 páginasParallel CRC GeneratorEvgeni StavinovAinda não há avaliações

- tr413 PDFDocumento17 páginastr413 PDFWANKHAMAAinda não há avaliações

- Rijhun 1Documento9 páginasRijhun 1amit kumarAinda não há avaliações

- WC & LTE 4G - Module 2Documento57 páginasWC & LTE 4G - Module 2kirankumar humseAinda não há avaliações

- Coupling-Driven Signal Encoding Scheme For Low-Power Interface DesignDocumento4 páginasCoupling-Driven Signal Encoding Scheme For Low-Power Interface DesignshastryAinda não há avaliações

- #Parallel CRC RealizationDocumento8 páginas#Parallel CRC RealizationBainan ChenAinda não há avaliações

- Department of Computer Science and Engineering Introduction To Internet (IT30037)Documento7 páginasDepartment of Computer Science and Engineering Introduction To Internet (IT30037)Bhavya NagAinda não há avaliações

- Data Communication NotesDocumento5 páginasData Communication NotesitsmelittyAinda não há avaliações

- ECX5234 Data Communications Assignment 1 - 2011/2012: The Open University of Sri LankaDocumento2 páginasECX5234 Data Communications Assignment 1 - 2011/2012: The Open University of Sri LankaSasith WickramasingheAinda não há avaliações

- CCN LABORATORY CERTIFICATEDocumento109 páginasCCN LABORATORY CERTIFICATEVishal GuptaAinda não há avaliações

- The Basic Principles of OFDMDocumento30 páginasThe Basic Principles of OFDMsureshya22Ainda não há avaliações

- Modeling and Analyzing The Ber Performance of Ofdm-Mimo System With 16-Qam Using Ostbc For Wireless Communication Based On MatlabDocumento10 páginasModeling and Analyzing The Ber Performance of Ofdm-Mimo System With 16-Qam Using Ostbc For Wireless Communication Based On MatlabTJPRC PublicationsAinda não há avaliações

- Modeling ADSL Data Transmission with SDFDocumento9 páginasModeling ADSL Data Transmission with SDFIrving Peña BalderasAinda não há avaliações

- Combinepdf WclteDocumento169 páginasCombinepdf Wclteatul bhardwajAinda não há avaliações

- Implementation of OFDM Transmitter and Receiver Using FPGA: Nasreen Mev, Brig. R.M. KhaireDocumento4 páginasImplementation of OFDM Transmitter and Receiver Using FPGA: Nasreen Mev, Brig. R.M. Khaireankita6298Ainda não há avaliações

- Ijcet: International Journal of Computer Engineering & Technology (Ijcet)Documento10 páginasIjcet: International Journal of Computer Engineering & Technology (Ijcet)IAEME PublicationAinda não há avaliações

- Channel Coding Techniques in TetraDocumento12 páginasChannel Coding Techniques in TetraAdnan Shehzad100% (1)

- Exam in Computer Networks A (Datornätverk A) : Magnus - Eriksson@miun - SeDocumento6 páginasExam in Computer Networks A (Datornätverk A) : Magnus - Eriksson@miun - SeHjernquistAinda não há avaliações

- Low Power Design of The Physical Layer of NarrowBand IoT LTE TransmitterDocumento7 páginasLow Power Design of The Physical Layer of NarrowBand IoT LTE Transmitteromnia taysirAinda não há avaliações

- Under Water Acoustic Communication Based On Pattern Time Delay Shift Coding SchemeDocumento0 páginaUnder Water Acoustic Communication Based On Pattern Time Delay Shift Coding SchemenvanthaoAinda não há avaliações

- Kiran Gunnam, Weihuang Wang, Euncheol Kim, Gwan Choi, Mark YearyDocumento6 páginasKiran Gunnam, Weihuang Wang, Euncheol Kim, Gwan Choi, Mark YearypathmakerpkAinda não há avaliações

- Ubicc 68Documento11 páginasUbicc 68Ubiquitous Computing and Communication JournalAinda não há avaliações

- A Low Power VITERBI Decoder Design With Minimum Transition Hybrid Register Exchange Processing For Wireless ApplicationsDocumento9 páginasA Low Power VITERBI Decoder Design With Minimum Transition Hybrid Register Exchange Processing For Wireless ApplicationsAnonymous e4UpOQEPAinda não há avaliações

- Design of Spreading Permutations for MIMO-CDMA Based on Space-Time Block CodesDocumento3 páginasDesign of Spreading Permutations for MIMO-CDMA Based on Space-Time Block CodesBalaram KvAinda não há avaliações

- Numerically Controlled Oscillator With Spur Reduction: Hans-Jörg Pfleiderer Stefan LachowiczDocumento4 páginasNumerically Controlled Oscillator With Spur Reduction: Hans-Jörg Pfleiderer Stefan LachowiczRaffi SkAinda não há avaliações

- FPGA Implementation of The Ternary Pulse Compression SequencesDocumento5 páginasFPGA Implementation of The Ternary Pulse Compression SequencesvijaykannamallaAinda não há avaliações

- Network Planning , midterm 2023 Exam SolutionDocumento3 páginasNetwork Planning , midterm 2023 Exam SolutionBasel wesamAinda não há avaliações

- Ieee 802.11N: On Performance of Channel Estimation Schemes Over Ofdm Mimo Spatially-Correlated Frequency Selective Fading TGN ChannelsDocumento5 páginasIeee 802.11N: On Performance of Channel Estimation Schemes Over Ofdm Mimo Spatially-Correlated Frequency Selective Fading TGN Channelszizo1921Ainda não há avaliações

- Data Communication Sample Tutorial& AnswerDocumento14 páginasData Communication Sample Tutorial& AnswerCik Ayeen MuhammadAinda não há avaliações

- Comparative Evaluation of Bit Error Rate For Different Ofdm Subcarriers in Rayleigh ChannelDocumento8 páginasComparative Evaluation of Bit Error Rate For Different Ofdm Subcarriers in Rayleigh ChannelLawrence AveryAinda não há avaliações

- I N - C D W C S - T T: Terative Etwork Hannel Ecoding ITH Ooperative Pace IME RansmissionDocumento11 páginasI N - C D W C S - T T: Terative Etwork Hannel Ecoding ITH Ooperative Pace IME RansmissionijasucAinda não há avaliações

- Turbo Codes: Farah Ilyas Vohra (TC-28), Shafaq Mustafa (TC-13), Sabieka Rizvi (TC-61) and Zainab Qazi (TC-11)Documento5 páginasTurbo Codes: Farah Ilyas Vohra (TC-28), Shafaq Mustafa (TC-13), Sabieka Rizvi (TC-61) and Zainab Qazi (TC-11)Zainab QaziAinda não há avaliações

- Noncoherent Physical-Layer Network Coding With FSK Modulation: Relay Receiver Design IssuesDocumento10 páginasNoncoherent Physical-Layer Network Coding With FSK Modulation: Relay Receiver Design IssuesramrcvAinda não há avaliações

- Implementing Cognitive Radio for Efficient RF CommunicationDocumento8 páginasImplementing Cognitive Radio for Efficient RF CommunicationinfydiptiAinda não há avaliações

- Network On Chip: A New Approach of QoS Metric Modeling Based On Calculus TheoryDocumento8 páginasNetwork On Chip: A New Approach of QoS Metric Modeling Based On Calculus TheoryAIRCC - IJCNCAinda não há avaliações

- Design of Convolutional Encoder and Viterbi Decoder Using MATLABDocumento6 páginasDesign of Convolutional Encoder and Viterbi Decoder Using MATLABThu NguyễnAinda não há avaliações

- Real Time Implementation of OFDM System On DSP ProcessorDocumento8 páginasReal Time Implementation of OFDM System On DSP ProcessorFaroukSatAinda não há avaliações

- Wireless Com. Report 20111115 - EnglishDocumento23 páginasWireless Com. Report 20111115 - EnglishHoang MaiAinda não há avaliações

- Power Line Communication Performance Channel CharacteristicsDocumento10 páginasPower Line Communication Performance Channel CharacteristicsGiAinda não há avaliações

- OFDM Write UpDocumento6 páginasOFDM Write Up20112075Ainda não há avaliações

- 3d Turbo CodesDocumento5 páginas3d Turbo CodesVasu DevAinda não há avaliações

- Signal Integrity: From High-Speed to Radiofrequency ApplicationsNo EverandSignal Integrity: From High-Speed to Radiofrequency ApplicationsAinda não há avaliações

- Samsung Interview Experience - Free Online Questions and Answers PDFDocumento8 páginasSamsung Interview Experience - Free Online Questions and Answers PDFRahul YadavAinda não há avaliações

- GSAT Sample Questions Paper With Solutions and PDF For FresherDocumento9 páginasGSAT Sample Questions Paper With Solutions and PDF For FresherRahul YadavAinda não há avaliações

- TCS Placement Paper (Conducted at JNTUK On 13.9Documento3 páginasTCS Placement Paper (Conducted at JNTUK On 13.9Rahul YadavAinda não há avaliações

- UPSC Result 2015Documento43 páginasUPSC Result 2015Vishal KumarAinda não há avaliações

- 2016 Set-2 - 2Documento16 páginas2016 Set-2 - 2Rahul YadavAinda não há avaliações

- Antenna Wave Propagation NotesDocumento130 páginasAntenna Wave Propagation Notesnivas_tptAinda não há avaliações

- Gate 90 Day Strategy Civil Beings FinalDocumento3 páginasGate 90 Day Strategy Civil Beings FinalRahul YadavAinda não há avaliações

- ECE Graduate Rahul Yadav ResumeDocumento3 páginasECE Graduate Rahul Yadav ResumeRahul YadavAinda não há avaliações

- KingdomNomics Book 131205 PDFDocumento94 páginasKingdomNomics Book 131205 PDFsaikishore6100% (2)

- Introduction To Adaptive Filtering: Block Diagram That Defines The Inputs and Output of A Generic RLS Adaptive FilterDocumento2 páginasIntroduction To Adaptive Filtering: Block Diagram That Defines The Inputs and Output of A Generic RLS Adaptive FilterRahul YadavAinda não há avaliações

- Osmosis, Diffusion PresentationDocumento19 páginasOsmosis, Diffusion PresentationRahul YadavAinda não há avaliações

- Title Remote Control Based Home Appliances Introduction:-: ApplicationDocumento3 páginasTitle Remote Control Based Home Appliances Introduction:-: ApplicationRahul YadavAinda não há avaliações

- Lecture11.0 EtchingDocumento30 páginasLecture11.0 EtchingRahul YadavAinda não há avaliações

- Curriculum Development of An Audio Processing Laboratory CourseDocumento13 páginasCurriculum Development of An Audio Processing Laboratory CourseJude SudarioAinda não há avaliações

- Date Sheet For Minor-I-19-22Feb 2016Documento1 páginaDate Sheet For Minor-I-19-22Feb 2016Rahul YadavAinda não há avaliações

- DSP Filter DesignDocumento10 páginasDSP Filter DesignPrasad NagavaraAinda não há avaliações

- Ece2year2014Documento8 páginasEce2year2014Rahul YadavAinda não há avaliações

- Computrac MAX 5000XL Moisture Analyzer Seminar Hong Kong 2009Documento67 páginasComputrac MAX 5000XL Moisture Analyzer Seminar Hong Kong 2009udiptya_papai2007Ainda não há avaliações

- Install CadenceDocumento4 páginasInstall Cadencenguyenbinh12xAinda não há avaliações

- Microsoft Interview QuestionsDocumento17 páginasMicrosoft Interview Questionspavankumar112Ainda não há avaliações

- SICAM 8 CP8050 My First Project 2023-06-30 JDDocumento279 páginasSICAM 8 CP8050 My First Project 2023-06-30 JDquoc dat NguyenAinda não há avaliações

- Case Study: Starbucks Progressive Web App: BackgroundDocumento2 páginasCase Study: Starbucks Progressive Web App: BackgroundAhmad MusaffaAinda não há avaliações

- Collection Hashmap PDFDocumento3 páginasCollection Hashmap PDFANIL KUMARAinda não há avaliações

- Adobe Acrobat DC SDK Release Notes: Edition 1.0Documento4 páginasAdobe Acrobat DC SDK Release Notes: Edition 1.0InquisitiveAinda não há avaliações

- Installation and Usage Guide of The New Generic USB DAC Driver For FiiO PlayersDocumento16 páginasInstallation and Usage Guide of The New Generic USB DAC Driver For FiiO PlayersArmando SgabeiAinda não há avaliações

- Density Based Traffic Control Using ArduinoDocumento16 páginasDensity Based Traffic Control Using Arduinofaisul faryAinda não há avaliações

- University of Central Punjab: Program (S) To Be Evaluated A. Course Description BsseDocumento5 páginasUniversity of Central Punjab: Program (S) To Be Evaluated A. Course Description Bssenabeel nawazAinda não há avaliações

- Multiple Monitor Replacement GuideDocumento2 páginasMultiple Monitor Replacement GuideVikas KumarAinda não há avaliações

- Virtualization and Cloud Computing-U3Documento8 páginasVirtualization and Cloud Computing-U3Prabhash JenaAinda não há avaliações

- COMP1829: Week 3Documento22 páginasCOMP1829: Week 3SujiKrishnanAinda não há avaliações

- 990002-2508 M1000 ManualDocumento116 páginas990002-2508 M1000 ManualYassine EL MAROUDIAinda não há avaliações

- Memory QVL For AMD Ryzen 2000 Series Processors PDFDocumento21 páginasMemory QVL For AMD Ryzen 2000 Series Processors PDFChris OrtizAinda não há avaliações

- Claims Processing SystemDocumento100 páginasClaims Processing Systemrazamohammadqaisar9330Ainda não há avaliações

- BaanERP TutorialDocumento55 páginasBaanERP TutorialKuldip Joshi100% (3)

- Problems Unit3Documento5 páginasProblems Unit3Akash G SAinda não há avaliações

- Spool AdministrationDocumento5 páginasSpool AdministrationKola K SivaramAinda não há avaliações

- ST 232Documento11 páginasST 232Negru P. PlantatieAinda não há avaliações

- SPN9971 Mosfet Radio SurDocumento10 páginasSPN9971 Mosfet Radio Surroberto caiadoAinda não há avaliações

- Lesson 1 Introduction To NetworkingDocumento14 páginasLesson 1 Introduction To NetworkingKevin SambuAinda não há avaliações

- Instructional Module Tle - Css 9 Afro-Asian Literture: Guanzon ST., Kabankalan City, Negros OccidentalDocumento35 páginasInstructional Module Tle - Css 9 Afro-Asian Literture: Guanzon ST., Kabankalan City, Negros OccidentalRussel SuperficialAinda não há avaliações

- Virtualization - Dark Web Forensics Using Csi Linux: Deborah K. Wells, Lecturer, CWUDocumento48 páginasVirtualization - Dark Web Forensics Using Csi Linux: Deborah K. Wells, Lecturer, CWUpicturesbyprathameshAinda não há avaliações

- MongoDB Shell Cheat SheetDocumento3 páginasMongoDB Shell Cheat SheetShivam AgrawalAinda não há avaliações

- 2) Routing Protocol BasisDocumento23 páginas2) Routing Protocol BasisRandy DookheranAinda não há avaliações

- CONTROL-M Job Parameter and Variable Reference Guide 20091008Documento542 páginasCONTROL-M Job Parameter and Variable Reference Guide 20091008Rajni ChaudharyAinda não há avaliações

- Ac Voltage Controller Circuits: Unit-8Documento49 páginasAc Voltage Controller Circuits: Unit-8Naeemo IraqiAinda não há avaliações

- Software Engineering Chapter 2Documento49 páginasSoftware Engineering Chapter 2nitin guptaAinda não há avaliações

- Delta Brochure Infrasuite enDocumento27 páginasDelta Brochure Infrasuite enSadanand GowdaAinda não há avaliações