Escolar Documentos

Profissional Documentos

Cultura Documentos

Contagem 0-99 com CI contadores

Enviado por

Ericles Henrique Oliveira CostaTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Contagem 0-99 com CI contadores

Enviado por

Ericles Henrique Oliveira CostaDireitos autorais:

Formatos disponíveis

1

Laboratrio 04 Contadores

CONTADOR COM DECODIFICADOR E DISPLAYS DE 7 SEGMENTOS

A capacidade de contar uma operao fundamental em eletrnica digital.

Um contador fornece

uma sada binria igual ao nmero de impulsos binrios ocorridos na sua entrada. Os contadores podem ser

construdos com flip flop's sendo o seu limite de contagem de 2 n-1 em que n o nmero de flip flop's

colocados em cascata.

Nesta aula prtica de laboratrio, utilizaremos alguns CI que j realizam a funo de contagem. Na

primeira parte da aula utilizaremos um contador BCD para realizar a contagem de 0 a 9, um decodificador

BCD para 7 segmentos e um display de 7 segmentos para observar a contagem.

J na segunda parte do

trabalho usaremos outro contador em cascata com o primeiro para podermos efetuar contagens de 0 at 99 e

um segundo conjunto descodificador/display para observarmos a contagem. Usaremos ainda alguma lgica

adicional para limitarmos a contagem de 0 a 59.

Logo, so objetivos dessa aula prtica a familiarizao com os CI contadores, descodificadores e

displays, bem como a sua interligao e funcionamento.

Em exerccios propostos, estaremos utilizando

circuitos adicionais, tais como foto-transistors para detectar objetos e realizar uma implementao prtica de

contagem.

1 EQUIPAMENTOS

Contadores, Decodificadores e Displays de 7 Segmentos.

Datapool

Centro de Engenharias e Cincias Exatas Bloco B11 Espao 2 Sala 03

Parque Tecnolgico Itaipu - Av. Tancredo Neves, 6731 - CEP 85856-970 Foz do Iguau PR

e-mail eng_pantaleao@yahoo.com.br

PARTE I CONTADOR DECIMAL

2 TEORIA E MONTAGEM

Nesta montagem vai usar os circuitos integrados 74LS90 (contador assncrono), o CI 9368

(decodificador BCD) e Display de 7 segmentos (Catodo comum).

Para conhecer o seu funcionamento

aconselha-se uma consulta ao datasheet destes CI's. O CI 74LS90 (Figura 4.1a) um contador assncrono,

BCD que efetua, portanto, contagem crescente em binrio e pode ser utilizado tambm como divisores de

frequncia por 2 e por 5 (conforme diagrama da Figura 4.1b). Os pinos A e B so as entradas de clock para

os dois divisores.

alternativa.

Em situaes de fabricantes diferentes, teramos um diagrama funcional com notao

Neste caso, as sadas denominadas Q0, Q1, Q2 e Q3, corresponderiam, respectivamente, QA,

QB, QC e QD e as entradas CP0 e CP1 corresponderiam, respectivamente, s entradas A e B.

(a)

(b)

Figura 5.1 (a) Diagrama de pinos contador 74LS90 e (b) Diagrama de pinos divisor por 2 e 5.

A sada do flip-flop da esquerda da Figura 4.2 (QA) executa a diviso por 2, ou seja, um sinal de

frequncia f1 na entrada A (pino 14) d origem a um sinal f1 / 2 no pino 12 (Q A). J os trs flip-flops da

mesma figura, executam a diviso por 5, ou seja, um sinal de frequncia f2 na entrada B (pino 1) d origem a

um sinal f2 / 5 no pino 11 (QD).

A porta lgica 1 controla as entradas set dos flip-flops extremos.

entradas reset dos quatro flip-flops.

A porta lgica 2 controla as

A Tabela 4.1 ilustra o procedimento para ressetar o contador: o

contador resseta se ambas as entradas R0(1) e R0(2) assumem nvel 1 e pelo menos uma das entradas R9s

estiver em 0. Qualquer uma das combinaes nas linhas 4, 5, 6 e 7 habilita o contador para contagem.

Centro de Engenharias e Cincias Exatas Bloco B11 Espao 2 Sala 03

Parque Tecnolgico Itaipu - Av. Tancredo Neves, 6731 - CEP 85856-970 Foz do Iguau PR

e-mail eng_pantaleao@yahoo.com.br

Figura 4.2 Circuito contador 74LS90.

Tabela 4.1 Combinaes para ressetar o contador.

Se dos divisores da Figura 4.1b forem interligados, ou seja, a sada QA (pino 12) for ligada

externamente entrada B (pino 1), obtemos um circuito divisor por dez. A frequncia na sada QD (pino 11)

ser igual frequncia na linha clock do pino 14 dividida por 10.

Neste caso, como a sequncia de

contagem vai de 0 a 9, o contador chamado de contador BCD ou contador de dcada.

transies negativas na entrada do clock (pino 14), o estado inicial se repete.

A cada 10

Por exemplo, se o estado

inicial 0000 (0 em decimal), aps 10 transies negativas na linha de clock o estado ser novamente 0000.

Tabela 4.2 Tabela de combinaes no modo BCD.

Centro de Engenharias e Cincias Exatas Bloco B11 Espao 2 Sala 03

Parque Tecnolgico Itaipu - Av. Tancredo Neves, 6731 - CEP 85856-970 Foz do Iguau PR

e-mail eng_pantaleao@yahoo.com.br

A Figura 4.3a a seguir apresenta uma ligao tpica envolvendo as entradas reset. Quando S vai

para 1, o contador resseta, caso contrrio, fica liberado para contagem. J a Figura 4.3b ilustra o diagrama

de pinos do decodificador 9368 e a Figura 4.3c o diagrama de pinos do display para 7 segmentos (ctodo

comum).

(a)

(b)

(c)

Figura 5.3 (a) Diagrama de pinos do contador 74LS90, (b) Diagrama de pinos do decodificador 9368 e

(c) Diagrama de pinos do display de 7 segmentos ctodo comum.

O CI 9368 fornece corrente correspondente 20mA nos seus pinos de sada, suficiente para uma boa

luminosidade.

O valor de corrente nunca poder ser superior 40mA para no danificar o display.

As

entradas do decodificador 9368 A, B, C e D devero ser ligadas s sadas QA, QB, QC e QD do contador

74LS90. As Figuras 4.4a e b ilustram as disposies de acionamento dos displays nodo comum e ctodo

comum.

Figura 4.4 (a) Diagrama de acionamento do display nodo

comum e (b) Diagrama de acionamento do display ctodo comum.

Centro de Engenharias e Cincias Exatas Bloco B11 Espao 2 Sala 03

Parque Tecnolgico Itaipu - Av. Tancredo Neves, 6731 - CEP 85856-970 Foz do Iguau PR

e-mail eng_pantaleao@yahoo.com.br

Tambm importante informar que, no decodificador 9368, o pino EL utilizado como controle para

isolar a informao do display de 7 segmentos: Se EL estiver em 0, a informao em DCBA passa para o

display, caso contrrio, se estiver em 1, a informao isolada.

J a entrada RB0 utilizada para apagamento (blank) de zeros nos cantos de uma configurao, por

exemplo, quando polarizado convenientemente (Figura 4.5), os zeros esquerda e direita em um instrumento

digital so apagados (ex. o nmero 060,040 ficaria 60,04).

Figura 4.5 Diagrama de ligao dos pinos RB0 e RBI para o apagamento dos zeros direita e esquerda.

Entretanto, para montar um contador BCD simples (um digito), basta fazer a ligao conforme Figura

4.6 abaixo. O pino EL (pino 3) dever ser 0 para permitir a passagem da informao de DCBA (se for 1 o

display fica parado) e o clock dever ser ligado a uma frequncia de 1Hz (um pulso por segundo).

Figura 4.6 Diagrama de ligao de um contador BCD de um digito.

Centro de Engenharias e Cincias Exatas Bloco B11 Espao 2 Sala 03

Parque Tecnolgico Itaipu - Av. Tancredo Neves, 6731 - CEP 85856-970 Foz do Iguau PR

e-mail eng_pantaleao@yahoo.com.br

Caso no tenha os componentes acima citados, pode-se utilizar de outros modelos de contadores e

decodificadores, como o caso do decodificador 4511 e do contador 4518.

O contador 4518 um CI que possui

internamente dois contadores assncronos, independentes, ou seja, podem ser utilizados separadamente.

Uma outra

vantagem desse CI so os pinos enable e reset, conforme figura abaixo:

Pinos de alimentao 16 (VDD 3 a 18V) e 08 (VSS - GND). Pinos de clock 01 (contador A) e 09 (contador

B).

Pinos de reset 07 (contador A) e 15 (contador B), sendo que se colocados em 0 permitem a contagem e se

colocados em 1 zeram a contagem. Pinos de enable 02 (contador A) e 10 (contador B), sendo que se colocados em 0

param a contagem e se colocados em 1 habilitam a contagem. A seguir apresentado a pinagem dos decodificadores

4511 e 74LS48 (catodo comum) e do 74LS47 (anodo comum).

Centro de Engenharias e Cincias Exatas Bloco B11 Espao 2 Sala 03

Parque Tecnolgico Itaipu - Av. Tancredo Neves, 6731 - CEP 85856-970 Foz do Iguau PR

e-mail eng_pantaleao@yahoo.com.br

Centro de Engenharias e Cincias Exatas Bloco B11 Espao 2 Sala 03

Parque Tecnolgico Itaipu - Av. Tancredo Neves, 6731 - CEP 85856-970 Foz do Iguau PR

e-mail eng_pantaleao@yahoo.com.br

A seguir apresentado uma soluo para contagem de 00 a 99 com o contador 4518 e decodificadores 4511.

Centro de Engenharias e Cincias Exatas Bloco B11 Espao 2 Sala 03

Parque Tecnolgico Itaipu - Av. Tancredo Neves, 6731 - CEP 85856-970 Foz do Iguau PR

e-mail eng_pantaleao@yahoo.com.br

PARTE II CONTAGEM DE 0 AT 99

3 MONTAGEM

Na Figura 5.7 temos um circuito obtido do cascateamento de duas dcadas contadoras 74LS90, com

sadas para o decodificador 9368. De acordo com o cascateamento, vemos que aps 10 pulsos de entrada

clock, ocorre uma transio negativa em QD (no caso da Figura 5.7 seria o QD1). Essa transio negativa

poder, ento, ser utilizada como gatilho para a segunda dcada levando o conjunto a variar de 00 a 99,

passando por 100 estgios diferentes.

O estgio inicial poder ser garantido atravs da entrada Reset.

Cabe lembrar que a cada dcada cascateada aumenta a contagem em 10 vezes.

Figura 5.7 Contador BCD com dois dgitos.

Figura 5.8 Contador BCD com dois dgitos com parada de contagem (chave SW).

Centro de Engenharias e Cincias Exatas Bloco B11 Espao 2 Sala 03

Parque Tecnolgico Itaipu - Av. Tancredo Neves, 6731 - CEP 85856-970 Foz do Iguau PR

e-mail eng_pantaleao@yahoo.com.br

Você também pode gostar

- APLV Uma Abordagem Pratica 14.04.21 - V CorrigidaDocumento45 páginasAPLV Uma Abordagem Pratica 14.04.21 - V CorrigidaEnzoAinda não há avaliações

- Slides AutismoDocumento14 páginasSlides AutismoGLAUCIA RIBEIRO DOS SANTOSAinda não há avaliações

- Ana Mae Barbosa PDFDocumento6 páginasAna Mae Barbosa PDFlacan5Ainda não há avaliações

- Teoria Da Firma PDFDocumento8 páginasTeoria Da Firma PDFDiego Palmiere0% (1)

- Mia CoutoDocumento4 páginasMia CoutoMateus RaulAinda não há avaliações

- 4 Mil 4ha 6bis LT 2408Documento7 páginas4 Mil 4ha 6bis LT 2408nelcimarAinda não há avaliações

- ETEC Dr. Celso Giglio: Curso Técnico em Meio AmbienteDocumento5 páginasETEC Dr. Celso Giglio: Curso Técnico em Meio AmbienteGabriela Ribeiro DeodatoAinda não há avaliações

- DOCENTE Inscritos 66 RodadaDocumento3 páginasDOCENTE Inscritos 66 RodadaCarolina Mendonca Fernandes de BarrosAinda não há avaliações

- Conceitos e usos de marketingDocumento17 páginasConceitos e usos de marketingrenan lescano romãoAinda não há avaliações

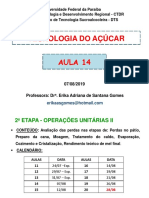

- Aula 14 - Tecnologia Do Açúcar - 2019.1Documento26 páginasAula 14 - Tecnologia Do Açúcar - 2019.1Erika Adriana SantanaAinda não há avaliações

- Tabela de Resistencia QuímicaDocumento4 páginasTabela de Resistencia QuímicaFelipe FariaAinda não há avaliações

- TrabalhoUFCD 725Documento14 páginasTrabalhoUFCD 725Joana TrindadeAinda não há avaliações

- Lendas de Arton 5 Taskan Skylander Interpor e ArremessoDocumento9 páginasLendas de Arton 5 Taskan Skylander Interpor e ArremessoLucas Cardoso FerreiraAinda não há avaliações

- Frequencia Alfa Na Meditacao GurdjieffDocumento6 páginasFrequencia Alfa Na Meditacao Gurdjieffricardo ferreira mirapalhetaAinda não há avaliações

- Plano de Negócios - BICICLETARIADocumento32 páginasPlano de Negócios - BICICLETARIAGuilherme RodriguesAinda não há avaliações

- Metodologia para Monitoramento de Estruturas Na Construção CivilDocumento10 páginasMetodologia para Monitoramento de Estruturas Na Construção Civilwelisson2Ainda não há avaliações

- Requerimento de Pensão por MorteDocumento2 páginasRequerimento de Pensão por MorteSidneyAinda não há avaliações

- Serviço em Computação em NuvemDocumento75 páginasServiço em Computação em NuvemfibralinkirAinda não há avaliações

- Pagar boleto de R$299,00Documento1 páginaPagar boleto de R$299,00Gabriel SouzaAinda não há avaliações

- Tabela de preços de cabos e acessórios elétricosDocumento2 páginasTabela de preços de cabos e acessórios elétricosEverton Roberto Dos SantosAinda não há avaliações

- Como Maximizar A Eficiência e Organizar Times de Customer SuccessDocumento40 páginasComo Maximizar A Eficiência e Organizar Times de Customer SuccessJoiceAinda não há avaliações

- Normatiza procedimentos matrículas rede pública educação Paraná 2023Documento53 páginasNormatiza procedimentos matrículas rede pública educação Paraná 2023Rafael SilvaAinda não há avaliações

- Pe - Conversão e MaquinasDocumento6 páginasPe - Conversão e MaquinasLayse Ribeiro MascarenhasAinda não há avaliações

- Emoções Embaralhadas (1) - 1Documento26 páginasEmoções Embaralhadas (1) - 1Karla LeuthierAinda não há avaliações

- Programa Computacional para o Dimensionamento de Vigas Retangulares de Concreto Armado Conforme A NBR 6118:2014Documento24 páginasPrograma Computacional para o Dimensionamento de Vigas Retangulares de Concreto Armado Conforme A NBR 6118:2014VitorAinda não há avaliações

- Projecto AgrotecniaDocumento15 páginasProjecto AgrotecniaDelizio Marcanizzy DBAinda não há avaliações

- Curso de Projeto de Sistemas Web 3Documento2 páginasCurso de Projeto de Sistemas Web 3Joaopcdroid GamerAinda não há avaliações

- Rare Eugene Scwartz Interview - En.ptDocumento21 páginasRare Eugene Scwartz Interview - En.ptCarlos Eduardo AmorimAinda não há avaliações

- Mat 3ºtrim 6ºanoDocumento2 páginasMat 3ºtrim 6ºanoNayane Oliveira100% (1)

- Desenvolvimento de Um Controle Odométrico para Um Veículo Terrestre Não Tripulado Com Modelo de Direção AckermannDocumento102 páginasDesenvolvimento de Um Controle Odométrico para Um Veículo Terrestre Não Tripulado Com Modelo de Direção AckermannDAN_73Ainda não há avaliações