Escolar Documentos

Profissional Documentos

Cultura Documentos

Lab Sist Digitales Exp01-15

Enviado por

GiraldoCarpioRamosTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Lab Sist Digitales Exp01-15

Enviado por

GiraldoCarpioRamosDireitos autorais:

Formatos disponíveis

UNIVERSIDAD NACIONAL DE SAN AGUSTN

DEPARTAMENTO ACADMICO DE INGENIERIA ELECTRICA

ESCUELA PROFESIONAL DE INGENIERA ELCTRICA

LABORATORIO DE SISTEMAS DIGITALES

________________________________________________________________________________________

EXPERIENCIA N 01

INSTRUMENTACIN Y PRINCIPIOS BSICOS

I.- OBJETIVO:

El objetivo de esta primera prctica consiste en que el alumno tome contacto con la

instrumentacin y otros elementos del laboratorio que utilizara a lo largo del curso.

II.- INTRODUCCION TEORICA:

En el laboratorio de sistemas digitales, el alumno aprender a utilizar circuitos analgicos y

digitales integrados reales con el fin de entender su funcionamiento e interconexin. Los

circuitos integrados que se utilizaran sern tanto analgicos (741 y 356) como digitales de

lgica Transistor-Transistor (TTL) y metal-oxido-semiconductor complementario CMOS.

2.1. Normas de conexin para circuitos integrados.

En los manuales de datos existe un a disposicin del alumno hojas de caractersticas de los

componentes a utilizar, entre ellos las del A741, LM351 y 555 que son los amplificadores

operacionales y temporizador, respectivamente, que utilizaremos en las prcticas. Slo hacer

notar que para los amplificadores operacionales las tensiones de alimentacin son de + 15 y 15 V.

La familia de integrados que se utilizara mas frecuentemente durante las prcticas digitales

corresponden a la familia TTL. La numeracin de cualquier circuito integrado (CI) de esta

familia comienza con los nmeros 74 (serie comercial) 54 (serie militar, con

especificaciones ms exigentes). Como normas generales de funcionamiento se puede decir

que para la familia TTL:

No se puede conectar directamente dos salidas (slo en open collector).

La tensin de alimentacin debe ser constante de 5 V (+/- 0.5V), excepto para los casos de

familias de baja potencia por los cuales la tensin de alimentacin puede ser por debajo de

los 3.3 V.

________________________________________________________________________________

Ing. Giraldo Carpio R.

Abril 2015

1 de 6

UNIVERSIDAD NACIONAL DE SAN AGUSTN

DEPARTAMENTO ACADMICO DE INGENIERIA ELECTRICA

ESCUELA PROFESIONAL DE INGENIERA ELCTRICA

LABORATORIO DE SISTEMAS DIGITALES

________________________________________________________________________________________

No se debe dejar sin conectar ninguna entrada. Una entrada al aire no tiene referencia de

tensin, por lo tanto, la conmutacin depender de los niveles de tensin internos de la

puerta. La mayor parte de los problemas de funcionamiento son debidos a estos fallos de

conexin.

Para una mayor inmunidad frente al ruido, velocidad de conmutacin y menor consumo, el

fabricante recomienda conectar las entradas que no se utilizan a nivel lgico 1.

Deben evitarse conexiones largas entre circuitos. Los cables podran actuar de antenas y

generar un funcionamiento incorrecto.

Los niveles tpicos de tensin asociados a los niveles lgicos de las entradas y salidas son los

que se muestran en la Tabla 1. Cualquier tensin entre 0 y 0.8V a la entrada de una puerta

LS-TTL ser interpretada como un 0 lgico, y cualquier tensin entre 2 y 5 V ser

interpretada como un 1 lgico.

Tabla 1: Rango de tensiones para niveles lgicos en LS-TTL

Estos datos son proporcionados por el fabricante en unas tablas como la de la figura

siguiente:

Como se puede observar en la Tabla 2, los niveles de salida se encuentran dentro de los

mrgenes admitidos por los de las entradas de la misma familia, de forma que siempre se

pueden interconectar en cascada varias puertas. Para la familia LS-TTL, la tensin de salida

mxima garantizada para el 0 lgico es de 0.5 V (inferior en 0.3 V al mximo permitido

para el 0 de entrada), mientras que la tensin de salida mnima para el 1 lgico es de 2.7

V (superior en 0.7 V al mnimo permitido para la entrada).

________________________________________________________________________________

Ing. Giraldo Carpio R.

Abril 2015

2 de 6

UNIVERSIDAD NACIONAL DE SAN AGUSTN

DEPARTAMENTO ACADMICO DE INGENIERIA ELECTRICA

ESCUELA PROFESIONAL DE INGENIERA ELCTRICA

LABORATORIO DE SISTEMAS DIGITALES

________________________________________________________________________________________

Tabla 2: Niveles lgicos en la familia TTL

Utilizar al menos un condensador de desacoplo (valores entre 10 nF y 100 nF) para cada

grupo de 5 a 10 puertas, uno por cada 2 a 5 subsistema combinacional o secuencial (registro

y contadores), y uno por cada monoestable. Los condensadores de desacoplo neutralizan los

impulsos elctricos que tienen lugar cuando una salida TTL cambia de estado y protegen

frente a variaciones de tensin de alimentacin.

Los terminales han de ser cortos y conectarse desde +V CC (+5 V) a masa lo ms cerca

posible de los CI.

Las consideraciones generales de conexin mencionadas anteriormente para circuitos de la

familia TTL son tambin aplicables a los circuitos de la familia CMOS. Estos tipos de

circuitos se caracterizan por:

Bajo consumo en reposo y reducido tamao, lo que permite una alta integracin de

funciones.

La alimentacin puede oscilar entre 3 V y 15 V. Valores entre 9 V y 12 V proporcionan

rendimientos ptimos para la familia 4000.

La tensin de entrada a las puertas no debe nunca exceder la tensin de alimentacin

(excepto en buffers).

________________________________________________________________________________

Ing. Giraldo Carpio R.

Abril 2015

3 de 6

UNIVERSIDAD NACIONAL DE SAN AGUSTN

DEPARTAMENTO ACADMICO DE INGENIERIA ELECTRICA

ESCUELA PROFESIONAL DE INGENIERA ELCTRICA

LABORATORIO DE SISTEMAS DIGITALES

________________________________________________________________________________________

Deben evitarse, en lo posible, flancos de subida y/o de bajada excesivamente lentos de la

seal de entrada ya que ello repercute en un excesivo consumo. Se consideran tiempos

ptimos aquellos menores de 15 s.

Todas las entradas no utilizadas deben conectarse a alimentacin o masa. En caso contrario

se producira un funcionamiento incorrecto o un alto consumo.

Nunca se debe conectar una seal de entrada a un circuito CMOS si no est conectada la

alimentacin.

Las razones que explican el porqu se debe tener tan especial cuidado en el manejo de

circuitos CMOS hay que buscarlas en la propia estructura interna de estos circuitos.

El transistor bsico CMOS est basado en una capa delgada de SiO2 que separa y asla el

metal de la puerta del substrato de silicio (Si). Al ser esta capa una pelcula muy delgada, el

CI CMOS queda virtualmente sin carga ante una seal de entrada, siendo muy susceptible de

perforarse por electricidad esttica.

2.2. Conexiones de los Circuitos Integrados.

Los CI pueden contener ms de una puerta lgica. El fabricante proporciona esquemas de las

conexiones. Por ejemplo, la Figura 1 corresponde al esquema de conexiones del CI 74XX00

(XX= LS, ALS, etc.). Se observan las entradas y salidas de cada una de las cuatro puertas

NAND que contiene. La alimentacin es comn a todas las puertas.

Todos los CIs numeran las conexiones (pines) tomando como referencia la muesca o marca

de fbrica situado en uno de los extremos del circuito integrado y se comienza en sentido

contrario al de las agujas del reloj.

Atencin a la hora de conectar las conexiones de alimentacin (VCC) y masa (GND),

puesto que una incorrecta conexin significa en la mayora de los casos la destruccin del

CI.

________________________________________________________________________________

Ing. Giraldo Carpio R.

Abril 2015

4 de 6

UNIVERSIDAD NACIONAL DE SAN AGUSTN

DEPARTAMENTO ACADMICO DE INGENIERIA ELECTRICA

ESCUELA PROFESIONAL DE INGENIERA ELCTRICA

LABORATORIO DE SISTEMAS DIGITALES

________________________________________________________________________________________

Figura 1: Esquema de conexiones del CI 74LS00

III.- ELEMENTOS A UTILIZAR:

- 01 Osciloscopio Digital con puntas de 100 MHz con puntas lgicas.

- 01 Generador de funciones con su cable de salida.

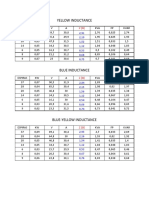

- Resistencias: Normalizadas

IV.- PROCECIMIENTO

4.1. Medidas bsicas, generacin y visualizacin de seales.

El osciloscopio, generador de funciones, las fuentes de alimentacin y el multmetro se

utilizarn en las prcticas posteriores para visualizar/medir/generar una seal de entrada y/o

medir caractersticas dinmicas de las seales de salida de los circuitos implementados.

El generador de funciones proporcionar seales digitales, conectando ste en la funcin de

onda senoidal, cuadrada o triangular y actuando sobre los controles de amplitud, ganancia y

OFFSET. De ese modo, se obtiene seales de entrada a nuestros circuitos.

1. Visualizar mediante el osciloscopio una seal TTL por el canal 1 de 10 Khz.

2. Visualizar la misma seal por el canal 2.

________________________________________________________________________________

Ing. Giraldo Carpio R.

Abril 2015

5 de 6

UNIVERSIDAD NACIONAL DE SAN AGUSTN

DEPARTAMENTO ACADMICO DE INGENIERIA ELECTRICA

ESCUELA PROFESIONAL DE INGENIERA ELCTRICA

LABORATORIO DE SISTEMAS DIGITALES

________________________________________________________________________________________

3. Visualizar utilizando el Offset una seal TTL de 50 Khz. Localice los valores unos y

ceros.

4. Visualizar una seal de -2 a 5 V a 1000 Hz. Aumentar la frecuencia y comentar posibles

malformaciones de la onda.

5. Visualizar una onda triangular de 0 a 9 V. a 20 kHz. Comprobar lo que ocurre con el

acople de continua y de alterna. Usar la tecla GD del osciloscopio para comprobar la

correcta lectura de la seal.

6. Visualizar una onda senoidal de 0 +200 mV a 10 kHz.

7. Visualizar una onda cuadrada de -200 mV a -600 mV a 5 kHz.

8. Visualice la onda senoidal ms pequea posible en amplitud.

9. Mediante el multmetro compruebe la continuidad de pistas en la protoboard y la ausencia

de cortocircuitos.

10. Disee un divisor de tensin segn resistencias normalizadas para obtener en la misma

rama 4.5 V y 3 V.

IV.- OBSERVACIONES Y CONCLUSIONES

Dar sus observaciones y conclusiones de forma personal, en forma clara y empleando el

menor numero de palabras.

Ing. G. Carpio R

Docente DAIEL

________________________________________________________________________________

Ing. Giraldo Carpio R.

Abril 2015

6 de 6

Você também pode gostar

- Letras Canciones 2019Documento3 páginasLetras Canciones 2019GiraldoCarpioRamosAinda não há avaliações

- Manual PspiceDocumento572 páginasManual PspiceHugo Jimenez100% (1)

- Simbologia Neumatica e Hidraulica PDFDocumento10 páginasSimbologia Neumatica e Hidraulica PDFElvis Justo Choquegonza GomezAinda não há avaliações

- Fluke Manual de Usuario (Serie 87 III)Documento58 páginasFluke Manual de Usuario (Serie 87 III)jauregui1100% (4)

- Hoja Tecnica Barras Cuadradas PDFDocumento2 páginasHoja Tecnica Barras Cuadradas PDFGiraldoCarpioRamosAinda não há avaliações

- 10-Materiales MagneticosDocumento16 páginas10-Materiales MagneticosSantos GarzaAinda não há avaliações

- File - 1915 - Manual de Soldadura Indura 2007Documento88 páginasFile - 1915 - Manual de Soldadura Indura 2007Pedro Junior Sotelo LedezmaAinda não há avaliações

- Manual de Motores ElectricosDocumento70 páginasManual de Motores ElectricosAndres Videla Flores98% (306)

- Inductancias Nucleo HierroDocumento3 páginasInductancias Nucleo HierroGiraldoCarpioRamosAinda não há avaliações

- Supervisor de MantenimientoDocumento5 páginasSupervisor de MantenimientoErick MoraAinda não há avaliações

- Máquinas de Corriente ContinuaDocumento30 páginasMáquinas de Corriente ContinuaJosep Lluís Morey FemeniaAinda não há avaliações

- Supervisor de MantenimientoDocumento2 páginasSupervisor de MantenimientoELoo Cruuz GonzaLeezAinda não há avaliações

- Gestion de MantenimientoDocumento250 páginasGestion de MantenimientoJassonMendozaAinda não há avaliações

- Cap3 Tiristores PDFDocumento51 páginasCap3 Tiristores PDFCesar J Cadena BAinda não há avaliações

- Grundig RC 113 Service ManualDocumento4 páginasGrundig RC 113 Service ManualGiraldoCarpioRamosAinda não há avaliações

- Equipo Electromecanico 5-7-2018Documento23 páginasEquipo Electromecanico 5-7-2018GiraldoCarpioRamosAinda não há avaliações

- Manual de Prácticas de Electrónica de Potencia PDFDocumento40 páginasManual de Prácticas de Electrónica de Potencia PDFGiraldoCarpioRamosAinda não há avaliações

- Sifon UcvDocumento19 páginasSifon UcvKevin Jams Piers Inga Coronado0% (1)

- Maquinas Electricas Cap02Documento16 páginasMaquinas Electricas Cap02Luis Alejandro GonzálezAinda não há avaliações

- Regulacion de Velocidad de Motores Serie de CCDocumento12 páginasRegulacion de Velocidad de Motores Serie de CCGiraldoCarpioRamosAinda não há avaliações

- Calculo de Inductores Con Nucleo de HierroDocumento6 páginasCalculo de Inductores Con Nucleo de HierroJ Adan Solis SchroederAinda não há avaliações

- Abaco Calc Tiempo de Aceleracion HankeDocumento1 páginaAbaco Calc Tiempo de Aceleracion HankeGiraldoCarpioRamosAinda não há avaliações

- Selección de MotoresDocumento37 páginasSelección de MotoresGiraldoCarpioRamosAinda não há avaliações

- Coeficientes de Momento CM y Potencia CP de Savonius HelicoidalDocumento2 páginasCoeficientes de Momento CM y Potencia CP de Savonius HelicoidalGiraldoCarpioRamosAinda não há avaliações

- Regulacion de Velocidad de Motores Serie de CCDocumento13 páginasRegulacion de Velocidad de Motores Serie de CCGiraldoCarpioRamosAinda não há avaliações

- Inversor PWMDocumento10 páginasInversor PWMGiraldoCarpioRamosAinda não há avaliações

- Motor Trifásico de Alto Rendimiento HankeDocumento8 páginasMotor Trifásico de Alto Rendimiento HankeGiraldoCarpioRamosAinda não há avaliações

- Practica 1Documento3 páginasPractica 1scorpionjcAinda não há avaliações

- Sistemas HidrulicosDocumento51 páginasSistemas HidrulicosHarold Urueña100% (1)

- Ardware YSoftware - Perifericos de Entrada y SalidaDocumento2 páginasArdware YSoftware - Perifericos de Entrada y Salidaeliecer moralesAinda não há avaliações

- Manual CentralitaDocumento50 páginasManual CentralitaAnonymous gnGgs630nAinda não há avaliações

- Manual de Fabricante PLCDocumento152 páginasManual de Fabricante PLCAle ZuritaAinda não há avaliações

- SsssDocumento53 páginasSsssAndrés Llanos SánchezAinda não há avaliações

- Informe Labo 5 de Microprocesadores UnivalleDocumento6 páginasInforme Labo 5 de Microprocesadores UnivalleAldrinTorrezChallapaAinda não há avaliações

- Imforme Del Laboratorio de Modulacion AmDocumento6 páginasImforme Del Laboratorio de Modulacion Amjunior jean sernaque ´pasacheAinda não há avaliações

- Examen Circuitos de Corriente Continua: Gabriel Fernández de La Paz 17.143.919-1 Técnico Nivel Superior en ElectricidadDocumento19 páginasExamen Circuitos de Corriente Continua: Gabriel Fernández de La Paz 17.143.919-1 Técnico Nivel Superior en Electricidadgabriel fernandezAinda não há avaliações

- Ejercicios PotenciaDocumento2 páginasEjercicios PotenciaKaren RubioAinda não há avaliações

- Examen3a Electronica Iiip Iip2020 LMDocumento2 páginasExamen3a Electronica Iiip Iip2020 LMkelvioAinda não há avaliações

- Trabajo de Investigacion Instalaciones ElectricasDocumento15 páginasTrabajo de Investigacion Instalaciones ElectricasKevin Contreras MoranAinda não há avaliações

- Taller de Electronica 5Documento46 páginasTaller de Electronica 5Pablo Diego Cecere CasadoAinda não há avaliações

- 19.Tv AnalogicaDocumento37 páginas19.Tv AnalogicaGina Paola Guerra ReinosoAinda não há avaliações

- Práctica de Introducción A LabVIEWDocumento20 páginasPráctica de Introducción A LabVIEWgallaghermacAinda não há avaliações

- BalumDocumento4 páginasBalumChristian PizanánAinda não há avaliações

- EIIIDocumento73 páginasEIIIErwin Geovanni Villalobos GutiérrezAinda não há avaliações

- Jairo Zambrano Individual SOLUCIONDocumento9 páginasJairo Zambrano Individual SOLUCIONjairo100% (1)

- Módulos Saitel DP-SP-Rev3.2 PDFDocumento150 páginasMódulos Saitel DP-SP-Rev3.2 PDFLuis André Otero SaavedraAinda não há avaliações

- Uso Del MicrocomputadorDocumento5 páginasUso Del MicrocomputadorDANELISAinda não há avaliações

- Fichas LivinglightDocumento336 páginasFichas LivinglightFabian Yusef Mowgli Espinosa SanchezAinda não há avaliações

- DAC y ADCDocumento55 páginasDAC y ADCleonelAinda não há avaliações

- Lab104 PC25Documento10 páginasLab104 PC25Victor SaavedraAinda não há avaliações

- Introduccion Al PLC PDFDocumento26 páginasIntroduccion Al PLC PDFGustavo Hernández'Ainda não há avaliações

- Minicomp Kairos M-X ESU - Service Manual 2 (Es)Documento74 páginasMinicomp Kairos M-X ESU - Service Manual 2 (Es)joseAinda não há avaliações

- Antologia de Arquitectura de ComputadorasDocumento95 páginasAntologia de Arquitectura de ComputadorasCésar Vicente Morales Morales100% (1)

- Informe 4 EAN1+Documento5 páginasInforme 4 EAN1+Santiago Cifuentes RamírezAinda não há avaliações

- Manual MIX 100 PDFDocumento31 páginasManual MIX 100 PDFpiptendoAinda não há avaliações

- Alarma Con Flip FlopsDocumento6 páginasAlarma Con Flip FlopsEdwin Camilo Delgado MartinezAinda não há avaliações

- Trabajo TCMDocumento34 páginasTrabajo TCMMarx CortesAinda não há avaliações

- 1er Informe VHDLDocumento8 páginas1er Informe VHDLCristian SanchezAinda não há avaliações

- Diodos - Sesion 3Documento7 páginasDiodos - Sesion 3Mily MundacaAinda não há avaliações