Escolar Documentos

Profissional Documentos

Cultura Documentos

Analog & Digital Student Lab Manual

Enviado por

Maheshwaran MahiDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Analog & Digital Student Lab Manual

Enviado por

Maheshwaran MahiDireitos autorais:

Formatos disponíveis

EC6311 Analog and Digital Lab

RAJALAKSHMI INSTITUTE OF TECHNOLOGY

Kuthambakkam - Chennai

ANNA UNIVERSITY

Regulation - 2013

DEPARTMENT OF ELECTRONICS & COMMUNICATION

ENGINEERING

EC6311-Analog and Digital Communication Laboratory

(II Year B.E - ECE, III Semester)

Prepared by,

Mr.K.Sivakumar, AP(SS)/ECE

Ms.V.Subashini, AP/ECE

STAFF-IN CHARGE

Semester 03

of Technology

HOD/ECE

Department of ECE

PRINCIPAL

Rajalakshmi Institute

Page 1

EC6311 Analog and Digital Lab

SYLLABUS

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 2

EC6311 Analog and Digital Lab

EC6311 ANALOG AND DIGITAL CIRCUITS LABORATORY

LIST OF EXPERIMENTS

LIST OF ANALOG EXPERIMENTS:

1. Frequency Response of CE / CB / CC amplifier

2. Frequency response of CS Amplifiers

3. Darlington Amplifier

4. Differential Amplifiers- Transfer characteristic.

5. CMRR Measurement

6. Cascode / Cascade amplifier

7. Class A Amplifier

8. Class B amplifier

9. Fullwave rectifier and Halfwave rectifier

10. Determination of bandwidth of single stage and multistage amplifiers

11. Spice Simulation of Common Emitter and Common Source amplifiers

LIST OF DIGITAL EXPERIMENTS

Introduction

Study Experiment-Verification of Logic Gates & Boolean Theorems and Laws

12. Design and implementation of code converters using logic gates

(i) BCD to excess-3 code and vice versa (ii) Binary to gray and vice-versa

13. Design and implementation of 4 bit binary Adder/ Subtractor and BCD adder using IC 7483

14. Design and implementation of Multiplexer and De-multiplexer using logic gates

15. Design and implementation of encoder and decoder using logic gates

16. Construction and verification of 4 bit ripple counter and Mod-10 / Mod-12 Ripple counters

17. Design and implementation of 3-bit synchronous up/down counter

18. Implementation of SISO, SIPO, PISO and PIPO shift registers using Flip- flops

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 3

EC6311 Analog and Digital Lab

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 4

EC6311 Analog and Digital Lab

LAB SCHEDULE

SL NO

LIST OF EXPERIMENTS

LIST OF ANALOG EXPERIMENTS

1.

2.

3.

4.

5.

6.

7.

Introduction

- Study of electronic components [Active and Passive].

- Study of Regulated Power supply, Signal Generator, Function Generator

and CRO.

- Study of transistor parameters using Transistor Data Sheets.

Design and Analysis of Common Emitter Amplifier

- To Determine a. DC characters tics, b. AC characteristics, c. Gain,

d. Bandwidth, e. Gain- Bandwidth Product, f. SPICE Simulation of

Amplifier(Additional)

Design and Analysis of Common Collector Amplifier

- To Determine a. DC characteristics, b. AC characteristics, c. Gain,

d. Bandwidth, e. Gain- Bandwidth Product, f. SPICE Simulation of

Amplifier(Additional)

Design and Analysis of Common Base Amplifier

- To Determine a. DC characteristics, b. AC characteristics, c. Gain,

d. Bandwidth, e. Gain- Bandwidth Product, f. SPICE Simulation of

Amplifier(Additional)

Design and Analysis of Darlington Amplifier

- To Determine a. DC characteristics, b. AC characteristics, c. Gain

d. Bandwidth, e. Gain- Bandwidth Product, f. SPICE Simulation of

Amplifier(Additional)

Design and Analysis of Common Source Amplifier

- To Determine a. DC characteristics, b. AC characteristics, c. Gain

d. Bandwidth, e. Gain- Bandwidth Product, f. SPICE Simulation of

Amplifier (Additional)

Design and Analysis of Cascade Amplifier

- To Determine a. DC characteristics, b. AC characteristics, c. Gain

d. Bandwidth, e. Gain- Bandwidth Product, f. SPICE Simulation of

Amplifier (Additional)

Design and Analysis of Cascode Amplifier

- To Determine a. DC characteristics, b. AC characteristics, c. Gain

d. Bandwidth, e. Gain- Bandwidth Product, f. SPICE Simulation of

Amplifier (Additional)

8.

Design and Analysis of Class A amplifier

9.

Design and Analysis of Class B amplifier

10.

Design and Analysis of Half-wave rectifier

11.

Design and Analysis of Full-wave rectifier

12.

Design and Analysis of Differential Amplifier

- To Determine a. Transfer characteristics, b. CMRR

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 5

EC6311 Analog and Digital Lab

13.

Pspice Simulation of Common Emitter Amplifier

a. Gain, b. Bandwidth

14.

Pspice Simulation of Common source Amplifier

a. Gain, b. Bandwidth

LIST OF DIGITAL EXPERIMENTS

15.

Introduction

- Study of Digital IC's using IC data sheets

- Study of IC trainer Kit

Study Experiment-Verification of Logic Gates & Boolean Theorems and

Laws

16.

Design and implementation of code converters using logic gates

(i) BCD to excess-3 code and vice versa (ii) Binary to gray and vice-versa

17.

Design and implementation of 4 bit binary Adder/ Subtractor and

BCD adder using IC 7483

18.

Design and implementation of Multiplexer and De-multiplexer using logic

gates

19.

Design and implementation of encoder and decoder using logic gates

20.

Construction and verification of 4 bit ripple counter and Mod-10 / Mod-12

Ripple counters

21.

Design and implementation of 3-bit synchronous up/down counter

Implementation of SISO, SIPO, PISO and PIPO shift registers using Flipflops

CONTENT BEYOND SYLLABUS

23.

Bridge Rectifier

24.

Seven Segment Display

22.

INDEX

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 6

EC6311 Analog and Digital Lab

S. No

Date

Name of the Experiment

Page No.

Sign

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15.

16.

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 7

EC6311 Analog and Digital Lab

17.

18.

19.

20.

21.

22.

23.

Common Emitter Amplifier circuit diagram

CE Amplifier without Feedback :

CE Amplifier with Feedback:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 8

EC6311 Analog and Digital Lab

COMMON EMITTER AMPLIFIER

EXPERIMENT:

01

DATE:

1. OBJECTIVE:

To Design and Construct a Common Emitter Amplifier using voltage divider

bias and to determine its:

a.

b.

c.

d.

e.

DC Characteristics

Maximum Signal Handling Capacity

Gain of the amplifier

Bandwidth of the amplifier

Gain -Bandwidth Product

2. REQUIREMENTS:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 9

EC6311 Analog and Digital Lab

S.n

Requireme

nt

Name

Transistor [Active]

Range

Quantity

BC 107

(0-3)MHz

30MHz

(0-30)V

Resistor [Passive]

2

Component

Watt , + 1%

Tolerence

Capacitor [Passive]

Signal

4

5

Generator[SG]

Equipment

Regulated power

supply

7

8

CRO

Bread Board

Accessories

Connecting Wires

Single strand

as

required

DESIGN PROCEDURE:

Given specifications:

VCC= 10V, IC=1.2mA, AV= 30, hFE= 100

(i) To calculate RC:

(ii) To calculate R1&R2:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 10

EC6311 Analog and Digital Lab

(iii) Input coupling capacitor :

(iv) Output coupling capacitor:

3. THEORY:

A common emitter amplifier is type of BJT amplifier which increases the

voltage level of the applied input signal Vin at output of collector.

The CE amplifier typically has a relatively high input resistance (1 - 10 K)

and a fairly high output resistance. Therefore it is generally used to drive

medium to high resistance loads. It is typically used in applications where a

small voltage signal needs to be amplified to a large voltage signal like radio

receivers.

The input signal Vin is applied to base emitter junction of the transistor and

amplifier output Vo is taken across collector terminal. Transistor is

maintained at the active region by using the resistors R1,R2 and Rc. A very

small change in base current produces a much larger change in collector

current. The output Vo of the common emitter amplifier is 180 degrees out

of phase with the applied the input signal V in.

4. PROCEDURE:

1. Connect the circuit as per the circuit diagram

2. Determine the Q-point of the CE amplifier using DC analysis.

3. Determine Maximum input voltage that can be applied to CE amplifier

using AC analysis.

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 11

EC6311 Analog and Digital Lab

3. Set the input voltage Vin=V

from 0Hz to 1MHz in

MSH

/2 and vary the input signal frequency

incremental steps and note down the corresponding

output voltage Vo for at least 20 different values for the considered range.

5. The voltage gain is calculated as Av = 20log (V0/Vi) dB

6. Find the Bandwidth and Gain-Bandwidth Product from Semi-log graph

taking

frequency on x-axis and gain in dB on y-axis.,

Bandwidth, BW = f2-f1

where f1 lower cut-off frequency

f2 upper cut-off frequency

a.

DC ANALYSIS:

It is the procedure to find the operating region of transistor

Steps:

i)

ii)

iii)

Set Vin = 0 by reducing the amplitude of the input signal from

signal generator

Open circuit the capacitors since it blocks DC voltage

Set VCC= +10v and measure the voltage drop across the

Resistor VRC, voltage across Collector- Emitter Junction VCE

iv)

and Voltage drop across base emitter junction. V BE

Find the Q-point of the transistor and draw the DC load line.

To verify dc condition

1. VBE :

(forward bias)

2. VRC

= ____________

3. VCE

= _______ (REVERSE BIAS)

4. Ic( Ic = (Vcc VCE ) / Rc) =________

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 12

EC6311 Analog and Digital Lab

Q point analysis:

It is the procedure to choose the opearating point of transistor

Q-point: ( ICQ =_____ ; VCEQ =______ )

b. Maximum signal handling capacity :

It is the process to find the maximum input voltage that can be

handled by the amplifier, so that it amplifies the input signal without any

distortion.

Procedure:

i.

Apply input signal Vin = 20 mV of 1Khz frequency to the

amplifier using the signal generator between base emitter

junction of the transistor. Find the sinusoidal output using

ii.

CRO across RL.

By increasing

the

amplitude

maximum input voltage V

MSH

of

the

input

signal

find

across VBE at which the

sinusoidal signal gets distorted during the process which can

be seen in the CRO. The amplitude obtained at this point is

maximum voltage that can be applied to the transistor for

efficient operating of transistor.

V

MSH

= _________ volts

MODEL GRAPH:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 13

EC6311 Analog and Digital Lab

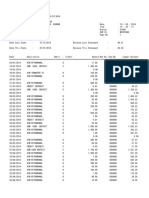

4. TABULATION [Without Feedback ] :

Input voltage (Vin=V

S. NO

/2) =____________V

MSH

FREQUENCY

OUTPUT VOLTAGE

[Hz]

[ VO] in Volts

GAIN= 20 log Vo/Vin

dB

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 14

EC6311 Analog and Digital Lab

11.

12.

13.

14.

15.

16.

With Feedback :

Input voltage (Vin=V

S. NO

/2) =____________ V

MSH

FREQUENCY

OUTPUT

[Hz]

VOLTAGE [ VO] in

Volts

GAIN= 20 log ( vo/vin )

dB

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 15

EC6311 Analog and Digital Lab

15.

16.

WORKSHEET

5. RESULT:

INFERENCE:

The Common Emitter Amplifier was constructed and the following results

were determined:

a) Gain of the amplifier :

b) Bandwidth of the amplifier :

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 16

EC6311 Analog and Digital Lab

c) Gain-Bandwidth product :

CONCLUSION:

Common Collector Amplifier Circuit Diagram:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 17

EC6311 Analog and Digital Lab

MODEL GRAPH:

COMMON COLLECTOR AMPLIFIER

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 18

EC6311 Analog and Digital Lab

EXPERIMENT: 02

DATE:

1. OBJECTIVE:

To Design and Construct a Common collector Amplifier and to determine

its:

a.

b.

c.

d.

e.

2.

DC Characteristics

Maximum Signal Handling Capacity

Gain of the amplifier

Bandwidth of the amplifier

Gain -Bandwidth Product using frequency response curve

REQUIREMENTS:

Requiremen

S.No

Name

Components

Transistor [Active]

Resistor [Passive]

Capacitor [Passive]

Signal Generator

Equipment

[SG]

CRO

Range

Quantity

BC 107

0-3MHz

0-30MHz

0-30 V

Single strand

as required

Regulated power

supply

Accessories

Bread Board

Connecting Wires

Design of Common collector amplifier:

Given specifications:

VCC= 15V, IC=1.2mA, hie = 2.1k hFE= 75 hib= 27.6

(i)

To calculate Zb ( Device input impedance )

Zb = hie + hfe ( RE || RL)

Assume RE = 4.7 K and RL= 3.3 K

Zb = 2.1k + 75 (4.7 K || 3.3 K) = __________

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 19

EC6311 Analog and Digital Lab

(ii)

To calculate Zi ( Input Impedance )

Zi = R1 || R2 || Zb

Assume R1= R2= 10k

Zi = _______

(iii) To Calculate Voltage gain Av :

Av = [ ( RE || RL ) / ( hib + ( RE || RL) ) ]

Av = _____

3.

THEORY:

A common collector amplifier is a unity gain BJT amplifier used for

impedance matching and as a buffer amplifier.

Circuit Operation :

When a positive half-cycle of the input signal is applied

to Base emitter junction of transistor the forward bias voltage V be is increased,

which in turn increases the base current I b of transistor. Since emitter current Ie

is directly proportional to Ib the voltage drop across the Emitter Ve= IeRe is

increased, hence, output voltage Vo is increased, thus, we get positive half-cycle

of the output. It means that a positive-going input signal results in a positive

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 20

EC6311 Analog and Digital Lab

going output signal and, consequently, the input and output signals are in phase

with each other. Similarly the negative half cycle of input signal produces

negative going output signal.

Characteristics of a CC Amplifier

1. high input impedance (20-500 K )

2. low output impedance (50-1000 )

3. high current gain of (1 + ) i.e. 50 500

4. voltage gain of less than 1 (unity)

5. power gain of 10 to 20 dB

6. no phase reversal of the input signal

4. PROCEDURE:

1.

Connect the circuit as per the circuit diagram

2.

Determine the Q-point of the CE amplifier using DC analysis.

3.

Determine Maximum input voltage that can be applied to CE amplifier

using AC analysis.

3. Set the input voltage Vin=V MSH /2 and vary the input signal frequency

from 0Hz to 1MHz in incremental steps and note down the corresponding

output voltage Vo for at least 15 different values for the considered range.

5. The voltage gain is calculated as Av = 20log (V0/Vin)

6. Find the Bandwidth and Gain-Bandwidth Product from Semi-log graph

taking

frequency on x-axis and gain in dB on y-axis.,

Bandwidth, BW = f2-f1

Where f1 - lower cut-off frequency

f2 - upper cut-off frequency

a. DC ANALYSIS:

It is the procedure to find the operating region of transistor

Steps:

i)

Set Vin = 0 by reducing the amplitude of the input signal

from signal generator

ii)

Open circuit the capacitors since it blocks DC voltage

iii)

Set VCC= +10v and measure the voltage drop across the

Resistor VRC, voltage across Collector- Emitter Junction VCE

and Voltage drop across base emitter junction. V BE

iv)

Find the Q-point of the transistor and draw the DC load line.

To verify dc condition

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 21

EC6311 Analog and Digital Lab

1. VBE :

(forward bias)

2. VRC

= ____________

3. VCE

= _______ (REVERSE BIAS)

4. Ic( Ic = (Vcc VCE ) / Rc) =________

Q point analysis:

It is the procedure to choose the opearating point of transistor

Q-point: ( ICQ =_____ ; VCEQ =______ )

b. Maximum signal handling capacity :

It is the process to find the maximum input voltage that can be

handled by the amplifier, so that it amplifies the input signal without any

distortion.

Procedure:

i.

Apply input signal Vin = 1 V of 1Khz frequency to the CC

amplifier using the signal generator between base emitter

junction of the transistor. Find the sinusoidal output using

CRO across RL.

ii.

By increasing the amplitude of the input signal find

maximum input voltage V MSH across VBE at which the

sinusoidal signal gets distorted during the process which can

be seen in the CRO. The amplitude obtained at this point is

maximum voltage that can be applied to the transistor for

efficient operating of transistor.

V

MSH

= _________ volts

5. TABULATION

Input voltage (Vin=V

S. NO

Semester 03

of Technology

MSH

FREQUENCY

[Hz]

/2) =____________ volts

OUTPUT

VOLTAGE

GAIN= 20 log vo/vin dB

[ VO] in Volts

Department of ECE

Rajalakshmi Institute

Page 22

EC6311 Analog and Digital Lab

1.

0

2.

100

3.

500

4.

600

5.

800

6.

900

7.

1 KHz

8.

100 KHz

9.

500 KHz

10.

11.

600 KHz

700 KHz

12.

800 KHz

13.

900 KHz

14.

1 MHz

15.

1.1 MHz

16.

1.5 MHz

WORKSHEET

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 23

EC6311 Analog and Digital Lab

6. RESULT:

INFERENCE:

The common collector amplifier was constructed and input resistance and gain

were determined. The results are found to be as given below

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 24

EC6311 Analog and Digital Lab

a) Gain of the amplifier (in dB) :

b) Bandwidth of the amplifier (in Hz) :

c) Gain-Bandwidth product (GBWP) :

CONCLUSION:

Common Base Amplifier Circuit Diagram:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 25

EC6311 Analog and Digital Lab

MODEL GRAPH:

COMMON BASE AMPLIFIER

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 26

EC6311 Analog and Digital Lab

EXPERIMENT:03

DATE:

1. OBJECTIVE:

To Design and Construct a Common Base Amplifier and to determine its:

a.

b.

c.

d.

e.

DC Characteristics

Maximum Signal Handling Capacity

Gain of the amplifier

Bandwidth of the amplifier

Gain -Bandwidth Product using frequency response curve

2. REQUIREMENTS:

S.N

o.

Requirement

Name

Range

Transistor [Active]

Quantity

BC 107

signal Generator

(0-3)MHz

CRO

30MHz

Regulated

supply

Bread Board

Components

2

Resistor [Passive]

Capacitor [Passive]

4

Equipment

power (0-30)V

1

1

Accessories

8

Connecting Wires

Single strand

as required

DESIGN PROCEDURE:

Given Transistor specifications:

hie = 2.1k ; hfe = 75 ; hfb =0.987

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 27

EC6311 Analog and Digital Lab

i) To find Device input impedance :

hib = ( hie / (1+ hfe))

hib = ____

ii) To find Circuit input impedance (Zi) :

iii) To find Circuit output impedance (Zo) :

iv) To find Voltage Gain (Av) :

3. THEORY:

A common base amplifier is type of BJT amplifier which increases the

voltage level of the applied input signal Vin at output of collector.

The Common base amplifier typically has good voltage gain and relatively

high output impedance. But the Common base amplifier unlike CE amplifier has

very low input impedance which makes it unsuitable for most voltage amplifier. It

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 28

EC6311 Analog and Digital Lab

is typically used used as an active load for a cascode amplifier and also as a

current follower circuit.

Circuit Opeartion:

A positive-going signal voltage at the input of a CB pushes the transistor

emitter in a positive direction while the base voltage remains fixed, hence Vbe

reduces. The reduction in V BE results in reduction in V RC, consequently VCE

increases. The rise in collector voltage effectively rises the output voltage. The

positive going pulse at the input produces a positive-going output, hence the

there is no phase shift from input to output in CB circuit. In the same way the

negative-going input produces a negative-going output.

4. PROCEDURE:

1. Connect the circuit as per the circuit diagram

2. Determine the Q-point of the CB amplifier using DC analysis.

3. Determine Maximum input voltage that can be applied to CE amplifier

using

AC analysis.

4. Set the input voltage Vin=V MSH /2 and vary the input signal frequency

from 0Hz to 1MHz in incremental steps and note down the corresponding

output voltage Vo for atleast 20 different values for the considered range.

5. The voltage gain is calculated as Av = 20log (V0/Vi)

5. Find the Bandwidth and Gain-Bandwidth Product from Semi-log graph

taking

frequency on x-axis and gain in dB on y-axis.,

Bandwidth, BW = f2-f1

where f1 lower cut-off frequency

f2 upper cut-off frequency

a. DC ANALYSIS:

It is the procedure to find the operating region of transistor

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 29

EC6311 Analog and Digital Lab

Steps:

i)

ii)

iii)

iv)

Set Vin = 0 by reducing the amplitude of the input signal

from signal generator

Open circuit the capacitors since it blocks DC voltage

Set VCC= +10v and measure the voltage drop across the

Resistor VRC, voltage across Collector- Emitter Junction VCE

and Voltage drop across base emitter junction. V BE

Find the Q-point of the transistor and draw the DC load line.

To verify dc condition

1. VBE :

(forward bias)

2. VRC

= ____________

3. VCE

= _______ (REVERSE BIAS)

4. Ic( Ic = (Vcc VCE ) / Rc) =________

Q point analysis:

It is the procedure to choose the opearating point of transistor

Q-point: ( ICQ =_____ ; VCEQ =______ )

b. Maximum signal handling capacity :

It is the process to find the maximum input voltage that can be

handled by the amplifier, so that it amplifies the input signal without any

distortion.

Procedure:

i.

Apply input signal Vin = 20 mV of 1Khz frequency to the

amplifier using the signal generator between base emitter

junction of the transistor. Find the sinusoidal output using

CRO across RL.

ii.

By increasing the amplitude of the input signal find

maximum input voltage V MSH across VBE at which the

sinusoidal signal gets distorted during the process which can

be seen in the CRO. The amplitude obtained at this point is

maximum voltage that can be applied to the transistor for

efficient operating of transistor.

V

MSH

= _________ volts

5. TABULATION

Input voltage (Vin=V

Semester 03

of Technology

MSH

/ 2) =____________V

Department of ECE

Rajalakshmi Institute

Page 30

EC6311 Analog and Digital Lab

S. NO

FREQUENCY

[Hz]

17.

18.

100

19.

500

20.

600

21.

800

22.

GAIN= 20 log Vo/ vin

dB

900

23.

1 KHz

24.

100 KHz

25.

500 KHz

26.

600 KHz

27.

OUTPUT

VOLTAGE

[ VO] in Volts

700 KHz

28.

800 KHz

29.

900 KHz

30.

1 MHz

31.

1.1 MHz

32.

1.5 MHz

WORKSHEET

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 31

EC6311 Analog and Digital Lab

6. RESULT:

INFERENCE:

The Common base amplifier was constructed and input resistance and gain were

determined. The results are found to be as given below

a) Gain of the amplifier :

b) Bandwidth of the amplifier :

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 32

EC6311 Analog and Digital Lab

c) Gain-Bandwidth product :

CONCLUSION:

Darlington Amplifier Circuit Diagram

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 33

EC6311 Analog and Digital Lab

MODEL GRAPH:

DARLINGTON AMPLIFIER

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 34

EC6311 Analog and Digital Lab

EXPERIMENT:04

DATE:

1. OBJECTIVE:

To Design and Construct a BJT amplifier using Darlington pair and to

determine its:

a.

b.

c.

d.

e.

DC Characteristics

Maximum Signal Handling Capacity

Gain of the amplifier

Bandwidth of the amplifier

Gain -Bandwidth Product using frequency response curve

2. REQUIREMENTS:

S.N

o.

Requirement

Name

Range

Transistor [Active]

Quantity

BC 107

signal Generator

(0-3)MHz

CRO

30MHz

Regulated

supply

Components

2

Resistor [Passive]

Capacitor [Passive]

4

Equipment

power (0-30)V

Bread Board

1

1

Accessories

8

Connecting Wires

Single strand

as required

DESIGN PROCEDURE:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 35

EC6311 Analog and Digital Lab

Given specifications:

VCC= 12V, IC=1.2mA, AV= 30, f 1 = 300 HZ, f2 = 500KHZ, hFE= 150

(i) To calculate RC:

(ii) To calculate R1&R2:

(iii) To Find Cin :

(iv) To Find CO :

3. THEORY:

The Darlington transistor (often called a Darlington pair) is compound

structure consisting of two bipolar transistors connected in such a way that the

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 36

EC6311 Analog and Digital Lab

First transistor does current amplification of input signal and then it will be fed

to the second transistor which performs voltage amplification.

This configuration gives a much higher gain than each transistor taken

separately and, in the case of integrated devices, can take less space than two

individual transistors because they can use a shared collector. The Darlington

amplifier typically has a relatively high input resistance (1 - 10 K) and a fairly

high output resistance. Therefore it is generally used to drive medium to high

resistance loads. It is typically used in applications where a small voltage signal

needs to be amplified to a large voltage signal like radio receivers.

4. PROCEDURE:

1. Connect the circuit as per the circuit diagram

2. Determine the Q-point of the Darlington amplifier using DC analysis.

3. Determine Maximum input voltage that can be applied to Darlington

amplifier using AC

analysis.

4. Set the input voltage Vin=V MSH /2 and vary the input signal frequency

from 0Hz to 1MHz in incremental steps and note down the corresponding

output voltage Vo for at least 20 different values for the considered range.

5. The voltage gain is calculated as Av = 20log (V0/Vi)

6. Find the Bandwidth and Gain-Bandwidth Product from Semi-log graph

taking

frequency on x-axis and gain in dB on y-axis.,

Bandwidth, BW = f2-f1

where f1 - lower cut-off frequency

f2 - upper cut-off frequency

a. DC ANALYSIS:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 37

EC6311 Analog and Digital Lab

It is the procedure to find the operating region of transistor

Steps:

i)

ii)

iii)

iv)

Set Vin = 0 by reducing the amplitude of the input signal

from signal generator

Open circuit the capacitors since it blocks DC voltage

Set VCC= +10v and measure the voltage drop across the

Resistor VRC, voltage across Collector- Emitter Junction VCE

and Voltage drop across base emitter junction. V BE

Find the Q-point of the transistor and draw the DC load line.

To verify dc condition

1. VBE :

(forward bias)

2. VRC

= ____________

3. VCE

= _______ (REVERSE BIAS)

4. Ic( Ic = (Vcc VCE ) / Rc) =________

Q point analysis:

It is the procedure to choose the opearating point of transistor

Q-point: ( ICQ =_____ ; VCEQ =______ )

b. Maximum signal handling capacity :

It is the process to find the maximum input voltage that can be

handled by the amplifier, so that it amplifies the input signal without any

distortion.

Procedure:

i.

Apply input signal Vin = 20 mV of 1Khz frequency to the

amplifier using the signal generator between base emitter

junction of the transistor.Find the sinusoidal output using CRO

across RL.

ii.

By increasing the amplitude of the input signal find

maximum input voltage V MSH across VBE at which the

sinusoidal signal gets distorted during the processwhich can

be seen in the CRO. The amplitude obtained at this point is

maximum voltage that can be applied to the transistor for

efficient operating of transistor.

V

Semester 03

of Technology

MSH

= _________ volts

Department of ECE

Rajalakshmi Institute

Page 38

EC6311 Analog and Digital Lab

5. TABULATION

Input voltage (Vin=V

S. NO

FREQUENCY

[Hz]

/2) =____________ V

MSH

OUTPUT

VOLTAGE

GAIN= 20 log Vo/Vin

dB

[ VO] in Volts

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

0

100

500

600

800

900

1 KHz

100 KHz

500 KHz

600 KHz

700 KHz

12.

800 KHz

13.

900 KHz

14.

1 MHz

15.

1.1 MHz

16.

1.5 MHz

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 39

EC6311 Analog and Digital Lab

WORKSHEET

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 40

EC6311 Analog and Digital Lab

6. RESULT:

INFERENCE:

The Darlington amplifier was constructed and the results are found to be

a. Gain of the amplifier :

b. Bandwidth of the amplifier :

c. Gain-Bandwidth product :

CONCLUSION:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 41

EC6311 Analog and Digital Lab

Common Source Amplifier Circuit Diagram

MODEL GRAPH:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 42

EC6311 Analog and Digital Lab

COMMON SOURCE AMPLIFIER

EXPERIMENT:05

DATE:

1. OBJECTIVE:

To Design and Construct a Common source

bootstrapped gate resistance and to determine its:

a.

b.

c.

d.

e.

2.

amplifier

using

the

DC Characteristics

Maximum Signal Handling Capacity

Gain of the amplifier

Bandwidth of the amplifier

Gain -Bandwidth Product

REQUIREMENTS:

S.N

o.

Requirement

Name

Range

Transistor [Active]

Quantity

BFW10

signal Generator

(0-3)MHz

CRO

30MHz

Regulated

supply

Bread Board

Components

2

Resistor [Passive]

Capacitor [Passive]

4

Equipment

power (0-30)V

1

1

Accessories

8

Semester 03

of Technology

Connecting Wires

Department of ECE

Single strand

as required

Rajalakshmi Institute

Page 43

EC6311 Analog and Digital Lab

DESIGN ANALYSIS :

Given :

VDD = 20 V, IDSS = 5mA, ID = 1.5 mA,

i) To Find the voltage across the Gate-source region (V GS)

VGS = ID RS

ii) To find Voltage Across Drain to Source (VDS)

iii) To Find input impedance :

iv) To Find output impedance :

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 44

EC6311 Analog and Digital Lab

3. THEORY

There are three basic types of FET amplifier or FET transistor namely

common source amplifier, common gate amplifier and source follower amplifier.

The common-source (CS) amplifier may be viewed as a transconductance

amplifier or as a voltage amplifier.

i) As a transconductance amplifier, the input voltage is seen as modulating

the current going to the load.

ii) As a voltage amplifier, input voltage modulates the amount of current

flowing through the FET, changing the voltage across the output resistance

according to Ohm's law.

However, the FET device's output resistance typically is not high enough

for a reasonable transconductance amplifier (ideally infinite), nor low enough for

a decent voltage amplifier (ideally zero). Another major drawback is the

amplifier's limited high-frequency response. Therefore, in practice the output

often is routed through either a voltage follower (common-drain or CD stage), or

a current follower (common-gate or CG stage), to obtain more favorable output

and frequency characteristics

4. PROCEDURE:

1. Connect the circuit as per the circuit diagram

2. Determine the Q-point of the CS amplifier using DC analysis.

3.

Determine Maximum input voltage that can be applied to CE amplifier

using

AC analysis.

4. Set the input voltage Vin=V MSH /2 and vary the input signal frequency

from 0Hz to 1MHz in incremental steps and note down the corresponding

output voltage Vo for atleast 20 different values for the considered range.

5. The voltage gain is calculated as Av = 20log (V0/Vi)

6. Find the Bandwidth and Gain-Bandwidth Product from Semi-log graph

taking

frequency on x-axis and gain in dB on y-axis.,

Bandwidth, BW = f2-f1

where f1 - lower cut-off frequency

f2 - upper cut-off frequency

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 45

EC6311 Analog and Digital Lab

a. DC ANALYSIS:

It is the procedure to find the operating region of transistor

Steps:

i)

ii)

iii)

iv)

Set Vin = 0 by reducing the amplitude of the input signal

from signal generator

Open circuit the capacitors since it blocks DC voltage

Set VCC= +10v and measure the voltage drop across the

Resistor VRC, voltage across Collector- Emitter Junction VCE

and Voltage drop across base emitter junction. V BE

Find the Q-point of the transistor and draw the DC load line.

To verify dc condition

1. VGS

= ____________

2. VDS

= ____________

3 ID

= _______

b. Maximum signal handling capacity :

It is the process to find the maximum input voltage that can be

handled by the amplifier, so that it amplifies the input signal without any

distortion.

Procedure:

i.

ii.

Apply input signal Vin = 1 V of 1Khz frequency to the CS

amplifier using the signal generator between base emitter

junction of the transistor. Find the sinusoidal output using

CRO across RL.

By increasing the amplitude of the input signal find

maximum input voltage V MSH across VBE at which the

sinusoidal signal gets distorted during the process which can

be seen in the CRO. The amplitude obtained at this point is

maximum voltage that can be applied to the transistor for

efficient operating of transistor.

V

Semester 03

of Technology

MSH

= _________ volts

Department of ECE

Rajalakshmi Institute

Page 46

EC6311 Analog and Digital Lab

5. TABULATION

Input voltage (Vin=V

S. NO

/2) =____________V

MSH

FREQUENCY

[Hz]

OUTPUT

VOLTAGE

GAIN= 20 log Vo/Vin

dB

[ VO] in Volts

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

0

100

500

600

800

900

1 KHz

100 KHz

500 KHz

600 KHz

700 KHz

12.

800 KHz

13.

900 KHz

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 47

EC6311 Analog and Digital Lab

14.

1 MHz

15.

1.1 MHz

16.

1.5 MHz

WORKSHEET

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 48

EC6311 Analog and Digital Lab

6. RESULT:

INFERENCE:

The common Source amplifier was constructed and input resistance and gain

were determined. The results are found to be as given below

a) Gain of the amplifier (in db) :

b) Bandwidth of the amplifier (in HZ) :

c) Gain-Bandwidth product (GBWP) :

CONCLUSION:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 49

EC6311 Analog and Digital Lab

Cascade amplifier Circuit Diagram

MODEL GRAPH:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 50

EC6311 Analog and Digital Lab

CASCADE AMPLIFIER

EXPERIMENT:06

DATE:

1. OBJECTIVE:

To Design and Construct a Cascade Amplifier and to determine its:

a.

b.

c.

d.

e.

2.

DC Characteristics

Maximum Signal Handling Capacity

Gain of the amplifier

Bandwidth of the amplifier

Gain -Bandwidth Product

REQUIREMENTS:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 51

EC6311 Analog and Digital Lab

S.N

o.

Requirement

Name

Range

Transistor [Active]

Quantity

BC 107

Components

2

Resistor [Passive]

Capacitor [Passive]

signal Generator

(0-3)MHz

CRO

30MHz

Regulated

supply

Equipment

power (0-30)V

Bread Board

1

1

Accessories

8

Connecting Wires

Single strand

as required

DESIGN PROCEDURE:

Given specifications:

VCC= 14 V, IC1=1.2mA, RL = 40K hFE= 100

(i) To calculate R5 :

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 52

EC6311 Analog and Digital Lab

(ii) To calculate R6 :

(iii) To calculate R1, R2 , R3 & R4:

3. THEORY:

A cascade is type of multistage amplifier where two or more single stage

amplifiers are connected serially. Many times the primary requirement of the

amplifier cannot be achieved with single stage amplifier, because Of the

limitation of the transistor parameters. In such situations more than one

amplifier stages are cascaded such that input and output stages provide

impedance matching requirements with some amplification and remaining

middle stages provide most of the amplification. These types of amplifier circuits

are employed in designing microphone and loudspeaker.

4. PROCEDURE:

1. Connect the circuit as per the circuit diagram

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 53

EC6311 Analog and Digital Lab

2. Determine the Q-point of the amplifier using DC analysis.

3. Determine Maximum input voltage that can be applied to amplifier using

AC analysis.

4. Set the input voltage Vin=V MSH /2 and vary the input signal frequency

from 0Hz to 1MHz in incremental steps and note down the corresponding

output voltage Vo for atleast 20 different values for the considered range.

5. The voltage gain is calculated as Av = 20log (V0/Vi)

6. Find the Bandwidth and Gain-Bandwidth Product from Semi-log graph

taking

frequency on x-axis and gain in dB on y-axis.,

Bandwidth, BW = f2-f1

where f1 - lower cut-off frequency

f2 - upper cut-off frequency

a. DC ANALYSIS:

It is the procedure to find the operating region of transistor

Steps:

v)

vi)

vii)

viii)

Set Vin = 0 by reducing the amplitude of the input signal

from signal generator

Open circuit the capacitors since it blocks DC voltage

Set VCC= +10v and measure the voltage drop across the

Resistor VRC, voltage across Collector- Emitter Junction VCE

and Voltage drop across base emitter junction. V BE

Find the Q-point of the transistor and draw the DC load line.

To verify dc condition

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 54

EC6311 Analog and Digital Lab

1. VBE :

(forward bias)

2. VRC

= ____________

3. VCE

= _______ (REVERSE BIAS)

4. Ic( Ic = (Vcc VCE ) / Rc) =________

Q point analysis:

It is the procedure to choose the opearating point of transistor

Q-point: ( ICQ =_____ ; VCEQ =______ )

b. Maximum signal handling capacity :

It is the process to find the maximum input voltage that can be

handled by the amplifier, so that it amplifies the input signal without any

distortion.

Procedure:

iii.

Apply input signal Vin = 20 mV of 1Khz frequency to the

amplifier using the signal generator between base emitter

junction of the transistor.Find the sinusoidal output using CRO

across RL.

iv.

By increasing the amplitude of the input signal find

maximum input voltage V MSH across VBE at which the

sinusoidal signal gets distorted during the processwhich can

be seen in the CRO. The amplitude obtained at this point is

maximum voltage that can be applied to the transistor for

efficient operating of transistor.

V

MSH

= _________ volts

5. TABULATION

Input voltage (Vin=V

S. NO

1.

2.

Semester 03

of Technology

/2) =____________ volts

MSH

FREQUENCY

[Hz]

OUTPUT

VOLTAGE

[ VO] in Volts

GAIN= 20 log Vo/Vin

dB

0

100

Department of ECE

Rajalakshmi Institute

Page 55

EC6311 Analog and Digital Lab

3.

4.

5.

6.

7.

8.

9.

10.

11.

500

600

800

900

1 KHz

100 KHz

500 KHz

600 KHz

700 KHz

12.

800 KHz

13.

900 KHz

14.

1 MHz

15.

1.1 MHz

16.

1.5 MHz

WORKSHEET

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 56

EC6311 Analog and Digital Lab

6. RESULT:

INFERENCE:

The Cascade amplifier was constructed and input resistance and gain were

determined. The results are found to be as given below

a) Gain of the amplifier :

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 57

EC6311 Analog and Digital Lab

b) Bandwidth of the amplifier :

c) Gain-Bandwidth product :

CONCLUSION:

Cascode amplifier Circuit Diagram

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 58

EC6311 Analog and Digital Lab

MODEL GRAPH:

CASCODE AMPLIFIER

EXPERIMENT: 07

Semester 03

of Technology

DATE:

Department of ECE

Rajalakshmi Institute

Page 59

EC6311 Analog and Digital Lab

1. OBJECTIVE:

To Design and Construct a Cascode Amplifier and to determine its:

a.

b.

c.

d.

e.

DC Characteristics

Maximum Signal Handling Capacity

Gain of the amplifier

Bandwidth of the amplifier

Gain -Bandwidth Product

2. REQUIREMENTS:

S.N

o.

Requirement

Name

Range

Quantity

Transistor [Active]

BC 107

Resistor [Passive]

61k, 10k, 1k,

4.7k

Capacitor [Passive]

10f, 100f

signal Generator

(0-3)MHz

CRO

30MHz

Regulated

supply

Components

1,1,1,2

2,1

Equipment

power (0-30)V

Bread Board

1

1

Accessories

8

Connecting Wires

Single strand

as required

DESIGN PROCEDURE:

Given specifications:

VCC= 20V, IC =1.2mA, AV= 30, , RL = 90K ;

Transistor Parameters: hFE= 50 , hie = 1.2K and hib= 24

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 60

EC6311 Analog and Digital Lab

(i) To calculate RC:

(ii) To calculate RE:

(iii) To Calculate Bias Resistors R1, R2, R3 :

Determination of Capacitor Values:

To Find C1 :

To Find C2 :

To Find C3 :

To Find C4 :

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 61

EC6311 Analog and Digital Lab

THEORY:

The cascode configuration has one of two configurations of multistage

amplifier. In each case the collector of the leading transistor is connected to the

emitter of the following transistor. The arrangement of the two transistors is

shown in the circuit diagram. The cascode amplifier consists of CE stage

connected in series with CB stage. The arrangement provides a relatively high

input impedance with low voltage gain for the first stage to ensure the input

miller capacitance is at a minimum, whereas the following CB stage provides an

excellent high frequency response.

Features:

1. It provides high voltage gain and has high input impedance.

2. It provides high stability and has high output impedance

PROCEDURE:

1. Connect the circuit as per the circuit diagram

2. Determine the Q-point of the CE amplifier using DC analysis.

3. Determine Maximum input voltage that can be applied to CE amplifier

using AC analysis.

4. Set the input voltage Vin=V MSH /2 and vary the input signal frequency

from 0Hz to 1MHz in

incremental steps and note down the corresponding output voltage V o for

atleast 20 different

values for the considered range.

5. The voltage gain is calculated as Av = 20log (V0/Vi)

6. Find the Bandwidth and Gain-Bandwidth Product from Semi-log graph

taking frequency on xaxis and gain in dB on y-axis.,

Bandwidth, BW = f2-f1

where

f1 - lower cut-off frequency

f2 - upper cut-off frequency

a. DC ANALYSIS:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 62

EC6311 Analog and Digital Lab

It is the procedure to find the operating region of transistor

Steps:

ix)

x)

xi)

xii)

Set Vin = 0 by reducing the amplitude of the input signal

from signal generator

Open circuit the capacitors since it blocks DC voltage

Set VCC= +10v and measure the voltage drop across the

Resistor VRC, voltage across Collector- Emitter Junction VCE

and Voltage drop across base emitter junction. V BE

Find the Q-point of the transistor and draw the DC load line.

To verify dc condition

1. VBE :

(forward bias)

2. VRC

= ____________

3. VCE

= _______ (REVERSE BIAS)

4. Ic( Ic = (Vcc VCE ) / Rc) =________

Q point analysis:

It is the procedure to choose the opearating point of transistor

Q-point: ( ICQ =_____ ; VCEQ =______ )

b. Maximum signal handling capacity :

It is the process to find the maximum input voltage that can be

handled by the amplifier, so that it amplifies the input signal without any

distortion.

Procedure:

v.

Apply input signal Vin = 20 mV of 1Khz frequency to the

amplifier using the signal generator between base emitter

junction of the transistor.Find the sinusoidal output using CRO

across RL.

vi.

By increasing the amplitude of the input signal find

maximum input voltage V MSH across VBE at which the

sinusoidal signal gets distorted during the processwhich can

be seen in the CRO. The amplitude obtained at this point is

maximum voltage that can be applied to the transistor for

efficient operating of transistor.

V

Semester 03

of Technology

MSH

= _________ volts

Department of ECE

Rajalakshmi Institute

Page 63

EC6311 Analog and Digital Lab

5. TABULATION

Input voltage (Vin=V

S. NO

/2) =____________ V

MSH

FREQUENCY

[Hz]

OUTPUT

VOLTAGE

GAIN= 20 log Vo/Vin

dB

[ VO] in Volts

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

0

100

500

600

800

900

1 KHz

100 KHz

500 KHz

600 KHz

700 KHz

12.

800 KHz

13.

900 KHz

14.

1 MHz

15.

1.1 MHz

16.

1.5 MHz

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 64

EC6311 Analog and Digital Lab

WORKSHEET

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 65

EC6311 Analog and Digital Lab

6. RESULT:

INFERENCE:

The Cascode amplifier was constructed and input resistance and gain were

determined. The results are found to be as given below

a) Gain of the amplifier :

b) Bandwidth of the amplifier :

c) Gain-Bandwidth product :

CONCLUSION:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 66

EC6311 Analog and Digital Lab

Circuit Diagram

WITHOUT FILTER:

WITH FILTER:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 67

EC6311 Analog and Digital Lab

HALF WAVE RECTIFIER

Exp.No:

Date

AIM:

To construct half wave rectifier with and without filter and to draw their input and output

waveforms and find out ripple factor.

S.No.

1.

2.

3.

4.

5

6

7

8

9

Requirement List

Components

Equipments

Other Accessories

Name

Transformer

Diode

Resistor

Capacitor

Regulated power supply

Signal Generator

CRO

Bread Board

Connecting Wires

Range

230 V / 6-0-(-6)

IN4007

1 k

100F

(0-30)V

(0-3)MHz

30 MHz

Single strand

Quantity

1

1

1

1

1

1

1

1

as reqd.

Requirements:

THEORY:

Half wave rectifier:

A rectifier is a circuit, which uses one or more diodes to convert A.C voltage into D.C voltage. In this

rectifier during the positive half cycle of the A.C input voltage, the diode is forward biased and

conducts for all voltages greater than the offset voltage of the semiconductor material used. The

voltage produced across the load resistor has same shape as that of the positive input half cycle of A.C

input voltage.

During the negative half cycle, the diode is reverse biased and it does not conduct. So there is no

current flow or voltage drop across load resistor. The net result is that only the positive half cycle of

the input voltage appears at the output.

FORMULA USED:

Ripple Factor =

Where Im is the peak current

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 68

EC6311 Analog and Digital Lab

MODEL GRAPH:

TABULATION

HALF WAVE RECTIFIER:

INPUT VOLTAGE = 12V (peak peak)

Without filter

Output signal

Amplitude(V)

With filter

Time period

Output signal

Amplitude(V)

Time period

CALCULATION OF RIPPLE FACTOR AND EFFICIENCY

Ripple Factor

Ripple factor is defined as the ratio of rms value of ac component to the dc

component in the output.

Ripple factor

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 69

EC6311 Analog and Digital Lab

Vav the average or the dc content of the voltage across the load is given by

RMS voltage at the load resistance can be calculated as

Ripple Factor

Efficiency

Efficiency, is the ratio of the dc output power to ac input power

Thus

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 70

EC6311 Analog and Digital Lab

PROCEDURE:

1.

2.

3.

4.

Connect the circuit as per the circuit diagram.

Apply a.c input using transformer.

Measure the amplitude and time period for the input and output waveforms.

Calculate ripple factor and effiency

RESULT:

Thus the half wave rectifier was constructed and its input and output waveforms are

drawn. The ripple factor of capacitive filter is calculated as

Ripple factor=

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 71

EC6311 Analog and Digital Lab

Circuit Diagram

FULLWAVE RECTIFIER WITHOUT FILTER

FULLWAVE RECTIFIER WITH FILTER

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 72

EC6311 Analog and Digital Lab

Requirement List

S.No.

1.

2.

3.

4.

5

6

7

8

Components

Equipments

Other Accessories

Exp. No

Name

Transformer

Diode

Resistor

Capacitor

Regulated power supply

Signal Generator

CRO

Bread Board

Range

230 V / 6-0-(-6)

IN4007

1 k

100f

(0-30)V

(0-3)MHz

30 MHz

-

Connecting Wires

Single strand

FULL WAVE RECTIFIER

Quantity

1

2

1

2

1

1

1

1

as reqd.

Date:

AIM:

To construct a full wave rectifier and to calculate the ripple factor.

REQUIREMENTS

THEORY:

The full wave rectifier conducts for both the positive and negative half cycles of the input ac

supply. In order to rectify both the half cycles of the ac input, two diodes are used in this circuit. The

diodes feed a common load RL with the help of a centre tapped transformer. The ac voltage is applied

through a suitable power transformer with proper turns ratio. The rectifiers dc output is obtained

across the load. The dc load current for the full wave rectifier is twice that of the half wave rectifier.

The lowest ripple factor is twice that of the full wave rectifier. The efficiency of full wave rectification

is twice that of half wave rectification. The ripple factor also for the full wave rectifier is less

compared to the half wave rectifier.

FORMULA USED:

Ripple Factor =

[(Im/2) / (2*Im /)] 2-1

Where Im is the peak current

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 73

EC6311 Analog and Digital Lab

MODEL GRAPH

TABULATOIN:

INPUT VOLTAGE = 12V (peak peak)

Without filter

Output signal

Amplitude(V)

With filter

Time period

Output signal

Amplitude(V)

Time period

CALCULATION OF RIPPLE FACTOR AND EFFICIENCY

Ripple Factor

The ripple factor for a Full Wave Rectifier is given by

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 74

EC6311 Analog and Digital Lab

The average voltage or the dc voltage available across the load resistance is

RMS value of the voltage at the load resistance is

Efficiency

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 75

EC6311 Analog and Digital Lab

Efficiency, is the ratio of dc output power to ac input power

The maximum efficiency of a Full Wave Rectifier is 81.2%.

PROCEDURE:

1. Connections are given as per the circuit diagram wiyhout filter.

2. Note the amplitude and time period of the input signal at the secondary winding of the

transformer and rectified output.

3. Repeat the same steps with the filter and measure Vdc.

4. Calculate the ripple factor.

5. Draw the graph for voltage versus time.

CONCLUSION

Thus, the full wave rectifier was constructed and the ripple factor was calculated as Ripple

factor =

CLASS A CIRCUIT DIAGRAM

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 76

EC6311 Analog and Digital Lab

MODEL WAVEFORM

V in = 50mV

V out = 10V (p-p)

Vin = Vmsh/2 = 100mV/2 = 50mV

Vout = 10V

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 77

EC6311 Analog and Digital Lab

CLASS - A POWER AMPLIFIER

Exp. No.:

Date:

AIM:

To construct a Class A power amplifier and observe the waveform and to compute maximum

power dissipation and efficiency.

REQUIREMENTS:

S.No.

1.

2.

3.

4.

5.

6.

7.

Name

Transistor

Resistor

Capacitor

Signal Generator

CRO

Regulated power supply

Bread Board

Range

SL100

61k,10K,1K, 2.2K

10F, 10F, 100F

(0-3)MHz

30MHz

(0-30)V

Quantity

1

1,1,2,1

1,1,1

1

1

1

1

THEORY:

The power amplifier is said to be Class A amplifier if the Q point and the input signal

are selected such that the output signal is obtained for a full input signal cycle.

For all values of input signal, the transistor remains in the active region and never enters into

cut-off or saturation region. When an a.c signal is applied, the collector voltage varies sinusoidally

hence the collector current also varies sinusoidally. The collector current flows for 360 0 (full cycle) of

the input signal. i e the angle of the collector current flow is 360 0 .

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 78

EC6311 Analog and Digital Lab

Observation:

Keep the input voltage constant, Vin = Vmsh/2 = 100mV/2 = 50mV

Vout = 10V

DC analysis

Vbe = 0.6

hfe = 165

Ic = (Vcc Vce)/ Rc =

Vce =

To find Max Efficiency

% max = (Pout(AC)) / (Pin (DC)) x 100 %

= [(Vcc2 /8RC) / (Vcc2 /2RC)] x 100%

% max = 25 % (theoretical)

% max = 23 % (practical)

To find Max power dissipation

Power dissipation = Pin (DC) Pout(AC)

=

=

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 79

EC6311 Analog and Digital Lab

PROCEDURE:

1. Connect the circuit as per the circuit diagram.

2. Set Vi =50 mv, using the signal generator.

3. Keeping the input voltage constant, vary the frequency from 10 Hz to 1M Hz in regular steps and

note down the corresponding output voltage.

4. Plot the graph; Gain (dB) vs Frequency(Hz).

CONCLUSION:

Thus the Class A power amplifier was constructed. The following parameters were calculated:

`

Semester 03

of Technology

a) Maximum power dissipation =

b) Efficiency=

Department of ECE

Rajalakshmi Institute

Page 80

EC6311 Analog and Digital Lab

CIRCUIT DIAGRAM

With Distortion

Without Distortion

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 81

EC6311 Analog and Digital Lab

CLASS B COMPLEMENTARY SYMMETRY POWER AMPLIFIER

S.No.

1.

2.

3.

4.

4.

5.

6.

7.

Requirement List

Components

Equipments

Name

Transistor

Resistors

capacitor

DIODE

Regulated power supply

Signal Generator

CRO

Bread Board

Other Accessories

8.

Connecting Wires

Exp. No.

Range

SL100,SK100

4.7k, 15 k

100F

IN4007

(0-30)V

(0-3)MHz

30 MHz

-

Quantity

1,1

2,1

2

2

1

1

1

1

Single strand

as reqd.

Date:

AIM:

To construct a Class B complementary symmetry power amplifier and observe the waveforms

with and without cross-over distortion and to compute maximum power delivered and efficiency.

REQUIREMENTS:

THEORY:

A power amplifier is said to be Class B amplifier if the Q-point and the input signal are

selected such that the output signal is obtained only for one half cycle for a full input cycle. The Qpoint is selected on the X-axis. Hence, the transistor remains in the active region only for the positive

half of the input signal.

There are two types of Class B power amplifiers: Push Pull amplifier and complementary symmetry

amplifier. In the complementary symmetry amplifier, one n-p-n and another p-n-p transistor is used.

The matched pair of transistor are used in the common collector configuration. In the positive half

cycle of the input signal, the n-p-n transistor is driven into active region and starts conducting and in

negative half cycle, the p-n-p transistor is driven into conduction. However there is a period between

the crossing of the half cycles of the input signals, for which none of the transistor is active and

output, is zero

FORMULA:

Input power, Pin=2VccIm/

Output power, Pout=VmIm/2

Power Gain or efficiency, =/4*(Vm/Vcc)* 100

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 82

EC6311 Analog and Digital Lab

Theoretical Calculation

= AC (output) / DC (Input) = Pac / Pdc

Pac = Vrms x Irms = Vm/2 x Im/2

Pac = VmIm / 2

Pdc = Vcc x Idc

Idc = Im /

Pdc = (Vcc x Im/)

Since two transistors involved

Pdc = (2Vcc x Im/)

= AC (output) / DC (Input) = Pac / Pdc

= [(VmIm/2) / (2VccIm/)]

for max output Vm = Vcc

= /4 = 0.7854

% = 78.54%

Practical Efficiency

= AC (output) / DC (Input) = Pac / Pdc

= [(VmIm/2) / (2VccIm/)]

= /4 x (Vm/Vcc) x 100

=

%=

To find max power dissipation

Pd = 0.4 x Pac (max)

= 0.4 x (Vcc2/2RL)

=

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 83

EC6311 Analog and Digital Lab

Pd =

OBSERVATION

Input Voltage = 12V (p-P)

Amplitude (volts)

Time Period (ms)

With Distortion

Without Distortion

MODEL GRAPH

PROCEDURE:

1. Connections are given as per the circuit diagram without diodes.

2. Observe the waveforms and note the amplitude and time period of the input signal and

distorted waveforms.

3. Connections are made with diodes.

4. Observe the waveforms and note the amplitude and time period of the input signal and

output signal.

5. Draw the waveforms for the readings.

6. Calculate the maximum output power and efficiency.

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 84

EC6311 Analog and Digital Lab

Hence the nature of the output signal gets distorted and no longer remains the same as the

input. This distortion is called cross-over distortion. Due to this distortion, each transistor conducts for

less than half cycle rather than the complete half cycle. To overcome this distortion, we add 2 diodes

to provide a fixed bias and eliminate cross-over distortion.

CONCLUSION:

Thus the Class B complementary symmetry power amplifier was constructed to observe

cross-over distortion and the circuit was modified to avoid the distortion. The following parameters

were calculated:

a)Maximum power dissipation =

b)Efficiency=

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 85

EC6311 Analog and Digital Lab

Differential amplifier Circuit Diagram

Common Mode :

Differential Mode :

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 86

EC6311 Analog and Digital Lab

DIFFERENTIAL AMPLIFIER

Exp. No.:

Date:

1. OBJECTIVE:

To Design and Construct a Differential Amplifier using BJT

determine its:

a.

b.

c.

d.

2.

and to

Transfer Characteristics

Gain of the amplifier in common mode

Gain of the amplifier in differential mode

CMRR (Common Mode Rejection Ratio)

REQUIREMENTS:

S.N

o.

Requirement

Name

Range

Transistor [Active]

Quantity

BC 107

signal Generator

(0-3)MHz

CRO

30MHz

Regulated

supply

Bread Board

Components

2

Resistor [Passive]

Capacitor [Passive]

4

Equipment

power (0-30)V

1

1

Accessories

8

Connecting Wires

Single strand

as required

3. THEORY:

A differential amplifier is a type of electronic amplifier that amplifies

the difference between two voltages but does not amplify the particular

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 87

EC6311 Analog and Digital Lab

voltages. The

need

for

differential

amplifier

arises

in

many

physical

measurements where response from D.C to many MHZ is required. It is also

used in input stage of integrated amplifier.

DESIGN PROCEDURE:

Given specifications:

VCC= 12V, IC=1.2mA, V CE = 5V

MODEL GRAPH:

Differential amplifier Transfer Characteristics:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 88

EC6311 Analog and Digital Lab

The output signal in differential amplifier is proportional to the difference

between the two input signals.

Vo = Ad (V1 V2 ).

Where V1,V2 are the input voltages and Ad is the differential gain.

If V1 = V2, then output voltage is zero. A non zero output voltage is

obtained if V1 and V2 are not equal.

i)

ii)

iii)

The difference mode input voltage is defined as V d = (V1-V2)

The common mode input voltage is defined as the V cm= (V1+V2)/2

The CMRR is defined as the ratio of the differential gain Ad to

common mode gain Ac and is generally expressed in dB.

CMRR= 20 log10 ( Ad / Ac)

4. PROCEDURE:

1. Connect the circuit as per the circuit diagram

2. Determine the Q-point of the Differential amplifier using DC analysis.

3. Determine Maximum input voltage that can be applied to amplifier using

AC analysis.

4. Determine the Transfer characteristics of Differential amplifier by plotting

the graph for normalized differential input voltage [ (Vb1 V b2) / VT ] vs.

Normalized collector current [ Ic / Io].

5. Calculate the voltage gain of differential amplifier for differential mode

as Ad = 20log (V0/Vi) , Where Vi = V1 V2

6. Calculate the voltage gain of differential amplifier for Common mode

as AC = 20log (V0/Vi) , Where Vi = (V1+ V2 / 2 )

7. Find the Common mode rejection ratio of differential amplifier using the

formula given below.

CMRR= 20 log10 ( Ad/Ac)

Where Ad- Differential mode gain in dB

Ac Common Mode gain in dB

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 89

EC6311 Analog and Digital Lab

a. DC ANALYSIS:

It is the procedure to find the operating region of transistor

Steps:

i)

ii)

iii)

iv)

Set Vin = 0 by reducing the amplitude of the input signal

from signal generator

Open circuit the capacitors since it blocks DC voltage

Set VCC= +10v and measure the voltage drop across the

Resistor VRC, voltage across Collector- Emitter Junction VCE

and Voltage drop across base emitter junction. V BE

Find the Q-point of the transistor and draw the DC load line.

To verify dc condition

1. VBE :

(forward bias)

2. VRC

= ____________

3. VCE

= _______ (REVERSE BIAS)

4. Ic( Ic = (Vcc VCE ) / Rc) =________

Q point analysis:

It is the procedure to choose the operating point of transistor

Q-point: ( ICQ =_____ ; VCEQ =______ )

b. Maximum signal handling capacity :

It is the process to find the maximum input voltage that can be

handled by the amplifier, so that it amplifies the input signal without any

distortion.

Procedure:

vii.

Apply input signal Vin = 20 mV of 1Khz frequency to the

amplifier using the signal generator between base emitter

junction of the transistor. Find the sinusoidal output using

CRO across RL.

viii.

By increasing the amplitude of the input signal find

maximum input voltage V MSH across VBE at which the

sinusoidal signal gets distorted during the process which can

be seen in the CRO. The amplitude obtained at this point is

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 90

EC6311 Analog and Digital Lab

maximum voltage that can be applied to the transistor for

efficient operating of transistor.

V

MSH

= _________ volts

5. TABULATION

a. Transfer Characteristics Calculation:

S.no

Input Voltage

Vi = (Vb1 Vb2) in Volts

Output Current

Ic2 in Ampere

1.

2.

3.

4.

5.

6.

b. CMRR Calculation:

To Find Differential Gain (Ad ) :

S. NO

INPUT

VOLTAGE

in volts

OUTPUT VOLTAGE [

VO] in Volts

Differntial gain in dB

Ad = 20log (V0/Vi)

Where Vi = Vi1 Vi2

33.

Vi1

34.

Vi2

To Find Common Mode Gain (AC ) :

S. NO

INPUT

VOLTAGE

in volts

OUTPUT VOLTAGE

[ VO] in Volts

Common mode gain in

dB

AC = 20log (V0/Vi)

where Vi = (V1+ V2 /

2)

1.

Vi1

2.

Vi2

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 91

EC6311 Analog and Digital Lab

6. RESULT:

INFERENCE:

The Differential amplifier was constructed and input resistance and gain were

determined. The results are found to be as given below

d) Trans-Conductance of Differential amplifier ( in millisiemens) :

e) Differential mode gain in dB

f) Common Mode Gain in dB

g) CMRR in dB

CONCLUSION:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 92

EC6311 Analog and Digital Lab

WORKSHEET

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 93

EC6311 Analog and Digital Lab

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 94

EC6311 Analog and Digital Lab

SPICE SIMULATION USING PSPICE Common

Emitter Amplifier circuit diagram

CE Amplifier without Feedback :

CE Amplifier with Feedback:

Semester 03

of Technology

Department of ECE

Rajalakshmi Institute

Page 95

EC6311 Analog and Digital Lab

COMMON EMITTER AMPLIFIER

EXPERIMENT:

DATE:

1. OBJECTIVE:

To Design and Construct a Common Emitter Amplifier using Pspice

simulation tool and to determine its:

a. Gain of the amplifier

b. Bandwidth of the amplifier

c. Gain -Bandwidth Product

2. REQUIREMENTS:

S.n

o

Requirements

Quantity

PC

Pspice Software

THEORY:

A common emitter amplifer is type of BJT amplifier which increases the

voltage level of the applied input signal Vin at output of collector.

The CE amplifier typically has a relatively high input resistance (1 - 10 K)

and a fairly high output resistance. Therefore it is generally used to drive

medium to high resistance loads. It is typically used in applications where a