Escolar Documentos

Profissional Documentos

Cultura Documentos

Harmonic Analysis of Three Level Diode Clamped Inverter

Enviado por

Journal 4 ResearchTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Harmonic Analysis of Three Level Diode Clamped Inverter

Enviado por

Journal 4 ResearchDireitos autorais:

Formatos disponíveis

Journal for Research | Volume 02 | Issue 07 | September 2016

ISSN: 2395-7549

Harmonic Analysis of Three Level Diode

Clamped Inverter

Pooja Sahastrabuddhe Dr. Hari Kumar Naidu

Student Dean

Department of Electrical Engineering Department of Electrical Engineering

Tulasiramji Gaikwad-Patil College of Engineering & Tulasiramji Gaikwad-Patil College of Engineering &

Technology, Nagpur, India Technology, Nagpur, India

Abstract

The power electronics device which converts DC power to AC power at required output voltage and frequency level is known as

inverter. Multilevel inverter is to synthesize a near sinusoidal voltage from several levels of dc voltages. In order to maintain the

different voltage levels at appropriate intervals, the conduction time intervals of MOSFETS have been maintained by controlling

the pulse width of gating pulses. In this paper single phase to three phase power conversion using PWM technique. The simulation

is carried out in MATLAB/Simulink environment which demonstrate the feasibility of proposed scheme.

Keywords: Inverter, Microcontroller, MOSFET, Pulse Width Modulation

_______________________________________________________________________________________________________

I. INTRODUCTION

Over the years, three-phase motors, more than single phase motors have been the main consideration in industries due to certain

parameters such as; efficiency, torque ripples and power factor. In rural areas, in order to operate machine tools and rolling mills

as well as in low power industrial application for robotics, where a three phase utility may not be available, high-performance

converters are typically used to run the three-phase motor drives. Low losses and cost effectiveness are the very important

properties for these converters various single-phase to three-phase converters have been proposed with at least 6 switches. An

alternative for the reduction of losses in these converters is that the number of power switches is reduced. Many components-

minimized structures are proposed in literatures[1]

Three different topologies have been proposed for multilevel inverters: diode-clamped (neutral-clamped) capacitor- clamped

(flying capacitors) and cascaded multi cell with separate dc sources. In addition, several modulation and control strategies have

been developed or adopted for multilevel inverters including the following: multilevel sinusoidal pulse width modulation (PWM),

multilevel selective harmonic elimination, and space-vector modulation (SVM).[7 8]

The most attractive features of multilevel inverters are as follows.

1) They can generate output voltages with extremely low distortion and lower dv/dt.

2) They draw input current with very low distortion.

3) They generate smaller common-mode (CM) voltage, thus reducing the stress in the motor bearings. In addition, using

sophisticated modulation methods, CM voltages can be eliminated.

4) They can operate with a lower switching frequency. The diode-clamp method can be applied to higher level converters

As the number of levels increases, the synthesized output waveform adds more steps, producing a staircase wave which approaches

the sinusoidal wave with minimum harmonic distortion. Ultimately, a zero harmonic distortion of the output wave can be obtained by an

infinite number of levels. More levels also mean higher voltages can be spanned by series devices without device voltage sharing

problems. [9 10] Unfortunately, the number of the achievable voltage levels is quite limited not only due to voltage unbalance problems

but also due to voltage clamping requirement, circuit layout, and packaging constraints.

The simulation is carried out in Matlab/Simulink environment which demonstrate the feasibility of proposed scheme.

II. DIODE CLAMPED MULTILEVEL CONVERTER

Three-level diode-clamped inverter is shown in Fig. 1. In this circuit, the dc-bus voltage is split into three levels by two series-

connected bulk capacitors, C1 & C2. The middle point of the two capacitors can be defined as the neutral point. The output voltage

van has three states: Vdc /2 and Vdc /2. For voltage level Vdc/2, switchesS1 and S2 need to be turned on; forVdc /2, switchesS1 and

S2 need to be turned on; and for the 0 level, S2 and S1need to be turned on. The key components that distinguish this circuit from

a conventional two-level inverter are D1 and D1. These two diodes clamp the switch voltage to half the level of the dc-bus voltage.

When both S1and S2 turn on, the voltage across a and 0 is, i.e., vao=Vdc. In this case, D1 balances out the voltage sharing between

S1 and S2 with S1blocking the voltage across C1and S2 blocking the voltage acrossC2.

Output voltage van is ac, and vao is dc. The difference between van and vao is the voltage across C2, which is Vdc /2. If the output

is removed out between a and 0, then the circuit becomes a dc/dc converter, which has three output voltage levels: Vdc, Vdc /2 and

0.

All rights reserved by www.journalforresearch.org 18

Harmonic Analysis of Three Level Diode Clamped Inverter

(J4R/ Volume 02 / Issue 07 / 005)

Fig. 1: Three level diode clamped inverter

III. CONTROL TECHNIQUE OF DIODE CLAMPED MULTILEVEL INVERTER

The sinusoidal PWM technique is very popular for industrial converters. In this technique, an isosceles triangle carrier wave of

frequency fc is compared with the fundamental frequency f sinusoidal modulating wave and the points of intersection determines

the switching points of power devices.

Two important parameters of the design process are amplitude modulation index ma= Vr/Vc, where Vr is the peak amplitude of

reference control signals, Vc is the peak amplitude of the carrier wave, and the frequency modulation index mf= fc/fr, where fc is

the frequency of the carrier wave and fr is the reference sinusoidal signal frequency. Ma and fr determines the magnitude and

frequency of output voltage, fc determines switching frequency of power semiconductor devices.

Multilevel converters are mainly controlled with sinusoidal PWM extended to multiple carrier arrangements of two types: Level

Shifted (LS-PWM), which includes Phase Disposition (PD-PWM), Phase Opposition Disposition (POD-PWM) and Alternative

Phase Opposition Disposition (APOD-PWM) or they can be Phase Shifted (PS-PWM). In present topology PD is used.

IV. PROPOSE SCHEME

Fig. 2: Block Diagram of Single Phase to Three Phase Conversion

The proposed scheme describes the theory of 1 phase to 3 phase conversion and the hardware implementation shall be made using

a programmed microcontroller of 8051 family duly interfaced to 3 phase inverter with 6 number MOSFET or IGBTs from DC

derived from a single phase, 50 Hz supply. The load can be a star connected three phase 50 Hz, 440 volt, 0.5 to 1 HP motor.

Alternatively, a star lamp load can be used to view the waveform only. The power supply consists of a step down transformer

230/12V, which steps down the volt a to 12V AC. This is converted to DC using a Bridge rectifier. The ripples are removed using

a capacitive filter and it is then regulated to +5V using a voltage regulator 7805 which is required for the operation of the

microcontroller and other components.

V. HARDWARE IMPLEMENTATION

The figure shows the hardware implementation of project single phase to three phase power conversion by PWM technique. There

are twelve MOSFETs are used for three level inverter.

All rights reserved by www.journalforresearch.org 19

Harmonic Analysis of Three Level Diode Clamped Inverter

(J4R/ Volume 02 / Issue 07 / 005)

Fig. 3: Hardware Implementation

VI. MULTILEVEL PWM INVERTER

The multilevel PWM inverters include an array of power semiconductors and capacitor voltage sources, the output of which

generate voltages in stepped waveform. The commutation of the switches allows the addition of the capacitor voltages which

reaches the high voltage level at the output, while the power semiconductors withstand only with reduced voltage. A five-level

PWM inverter generates an output voltage with five values (levels) with respect to the negative terminal of the capacitor. By

considering that n is the number of steps of the phase voltage with respect to the negative terminal of the inverter, then the number

of steps in the voltage between two phases of the load K is defined by:

K = 2m + 1 (1)

The number of steps p in the phase voltage of a single-phase load in wyes connection is given by:

p = 2k+1 (2)

The term multilevel starts with the three-level inverter. By increasing the number of levels in the inverter, the output voltages

have more steps generating a staircase waveform, it results to reduction in harmonic distortion. However, a high number of levels

results in increasing the complexity and also introduce voltage imbalance problems.

Three different topologies have been proposed for multilevel inverters as diode-clamped (neutral-clamped), capacitor Clamped

(flying capacitors) and cascaded multicell with separate dc sources. In addition, several modulation and control strategies have

been developed or adopted for multilevel inverters including the following: multilevel sinusoidal pulse width modulation (PWM),

multilevel selective harmonic elimination and space-vector modulation (SVM).

The most attractive features of multilevel inverters are

as follows:

1) It can generate output voltage with extremely low distortion.

2) It draws input current with very low distortion.

3) It generates smaller common-mode (CM) voltage, thus reducing the stress in the motor bearings. In addition, by using

sophisticated modulation methods, CM voltages can be eliminated.

4) They can operate with a lower switching frequency.

VII. MOSFET DRIVER

It is beneficial to use N-channel MOSFETs as the high side switches as well as the low side switches because they have a lower

ON resistance and therefore less power loss. However, to do so, the drain of the high side device is connected to the 170V DC

power which is to be inverted into the 120 AC power. This is a problem because the 170V is the highest voltage in the system and

in order for the switch to be turned on the voltage at the gate terminal must be 10V higher than the drain terminal voltage. In order

to achieve the extra voltage necessary to switch on the device, a MOSFET driver is used with a bootstrap capacitor.

The MOSFET driver operates from a signal input given from the microcontroller and takes its power from the battery voltage

supply that the system uses. The driver is capable of operating both the high side and low side devices, but in order to get the extra

10V for the high side device, an external bootstrap capacitor is charged through a diode from the 12V power supply when the

device is off. Because the power for the driver is supplied from the low voltage source, the power consumed to drive the gate is

small. When the driver is given the signal to turn on the high side device, the gate of the MOSFET has an extra boost in charge

from the bootstrap capacitor, surpassing the needed 10V to activate the device and turning the

VIII. MICROCONTROLLER

In order to use the H-bridge properly, there are four MOSFETs that need to be controlled. This can be done either with analog

circuits or a microcontroller. In this case, we chose the microcontroller over the analog system for several reasons. First, it would

All rights reserved by www.journalforresearch.org 20

Harmonic Analysis of Three Level Diode Clamped Inverter

(J4R/ Volume 02 / Issue 07 / 005)

be simpler to adapt. With an analog system, it would be difficult to make changes for the desired output. In many cases, this is a

desired trait, as it would be designed for a single purpose and therefore a single output. However, as this is something that is

designed to be available all over the world, it needs to be adjustable to different standards of frequency and voltage. With an analog

circuit, this would require a different circuit that it would have to switch over to, while with a micro-controller, it merely requires

a change in the programs code. The second advantage of using a microcontroller is that it can allow for easy feedback to control

the power flowing through the load. One of the problems that can occur with systems like this is that the variances in load can

cause variances in the supplied current and voltage. With a microcontroller, it is possible to have it look at the power output and

change the duty cycle based on whether or not the load requires additional power or is being oversupplied.

Necessary waveforms generated by the microcontroller vao, vbo, vco and the ouput vab, vbc, vca.

A0

V

B0

V

C0

V

AB

V

BC

V

CA

V

Fig. 4: Microcontroller

IX. SIMULATION RESULTS

1 300

0.5

200

0

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

Filter Voltage(v)

1 100

Voltage (v)

0.5 0

0

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1 -100

1

-200

0.5

0 -300

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1 0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

Time(sec) Time(sec)

Fig. 5: Input DC Voltage Fig. 6: Three Phase Sinosoidal Voltage

All rights reserved by www.journalforresearch.org 21

Harmonic Analysis of Three Level Diode Clamped Inverter

(J4R/ Volume 02 / Issue 07 / 005)

500

-500

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

Line Voltage(v)

500

-500

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

500

-500

0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.08 0.09 0.1

Time(sec)

Fig. 7: Three Level Output Voltage

The input dc voltage and three phase sinusoidal voltage is shown in fig.3and fig.4. The output result of three level diode clamped

inverter is shown in fig.5 It is observed that there is phase of 120 degree in three phase voltage.

X. TOTAL HARMONIC DISTORTION

From Three Level Inverter output waveform three levels i.e. -200V, 0V and +200V of output voltage is obtained. The CMV varies

from -200V to +200V can be observed from waveform of CMV of Three Level Inverter. From FFT analysis THD is obtained

34.88% in Line Voltage of Two Level Inverter. Here, CMV is decreases from CMV of Two Level Inverter and is also decrease as

compare to Two Level Inverter. As the comparison with 2-level inverter reduction in THD is shown in the graph below.

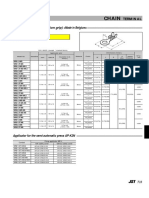

Modulation Index (ma) % THD 2-Level % THD 3-Level % Reduction in THD

1.1 31.94 15.93 50%

1 35.25 17.23 51%

0.9 39.20 17.45 54%

0.8 42.03 21.73 56%

0.7 44.30 24.18 57%

0.6 49.17 26.43 58%

0.5 68.54 34.38 60%

Fig. 6: Reduction in THD

All rights reserved by www.journalforresearch.org 22

Harmonic Analysis of Three Level Diode Clamped Inverter

(J4R/ Volume 02 / Issue 07 / 005)

XI. CONCLUSION

In this paper diode clamped Multilevel Inverter required only two-battery sources. A three level equal step switching control has

been applied to obtain a multilevel ac output. Multilevel Inverter with unequal voltage sources is simulated using MATLAB

Simulink. This paper presents a single-phase to three-phase conversion system that improves the local power quality for linear and

non-linear loads, and guarantees unity power factor at the single-phase feeder. The inverter controls the local power quality,

producing three-phase, symmetrical and sinusoidal voltages. It also controls the single-phase power flow, by adjusting the local

voltage amplitude and phase angle.

REFERENCES

[1] Anil K Adapa , Vinod John, Single Phase to Three Phase Power Conversion Using Reduced Rated Inverters, IEEE978-1-4799-1823-2/15/$31.00 2015.

[2] Cipriano, E., Jacobina, C.B., da Silva, E.R.C., Rocha, N., "Single-Phase to Three-Phase Power Converters: State of the Art," Power Electronics, IEEE

Transactions on, vol.27, no.5, pp.2437,2452, May 2012

[3] Shivanagouda.B.Patil, M. S. Aspalli Operating Three Phase Induction Motor Connected to Single Phase Supply, ISSN 2250-2459, Volume 2, Issue 11,

November 2012

[4] X. Wang, H. Zhong , Y. Yang and X. Mu "Study of a novel energy efficient single-phase induction motor with three series-connected windings and two

capacitors", IEEE Trans. Energy Convers., vol. 25, no. 2, pp.433 -440 2010

[5] M. Liserre "Dr. Bimal K. Bose: A reference for generations [editors column]", IEEE Ind. Electron. Mag., vol. 3, no. 2, pp.2 -5 2009

[6] B. Saint "Rural distribution system planning using smart grid technologies", Proc. IEEE Rural Electr. Power Conf., pp.B3 -B3-8 Apr. 2009

[7] H.-C. Chen "Single-loop current sensorless control for single-phase boost-type SMR", IEEE Trans. Power Electron., vol. 24, no. 1, pp.163 -171 2009

[8] B. Zahedi and S. Vaez-Zadeh "Efficiency optimization control of single-phase induction motor drives", IEEE Trans. Power Electron., vol. 24, no. 4, pp.1062

-1070 2009

[9] V. Kinnares and C. Charumit "Modulating functions of space vector PWM for three-leg VSI-fed unbalanced two-phase induction motors", IEEE Trans.

Power Electron., vol. 24, no. 4, pp.1135 -1139 2009

[10] A. R. C. de L. M. Duarte, U. H. Bezerra , M. E. de L. Tostes and G. N. da Rocha Filho "Alternative energy sources in the Amazon", IEEE Power Energy

Mag., vol. 5, no. 1, pp.51 -57 2007

[11] G. Pandia*, S. Rama Reddy, Implementation Of Single Phase To Three Phase Pwm Inverter Fed Induction Motor Drive, India. Dec. 20-22, 2007. pp.355-

360.

[12] R. Q. Machado, S. Buso and J. A. Pomilio "A line-interactive single-phase to three-phase converter system", IEEE Trans. Power Electron., vol. 21, no. 6,

pp.1628 -1636 2006

[13] F. Blaabjerg , A. Consoli , J. A. Ferreira and J. D. van Wyk "The future of electronic power processing and conversion", IEEE Trans. Ind. Appl., vol. 41,

no. 1, pp.3 -8 2005

[14] A. H. Maggs "Single-phase to three-phase conversion by the ferrarisarno system", Electr. Eng.Part I: Gen., J. Inst., vol. 93, no. 68, pp.133 -136 1946

All rights reserved by www.journalforresearch.org 23

Você também pode gostar

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (120)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- 2021 Individual 20546 (Lawrence, Stephen R. and Bette F.) ClientDocumento18 páginas2021 Individual 20546 (Lawrence, Stephen R. and Bette F.) ClientVANDA MOOREAinda não há avaliações

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- All About TarlacDocumento12 páginasAll About TarlacAnonymous uLb5vOjXAinda não há avaliações

- Design of Purlins: Try 75mm X 100mm: Case 1Documento12 páginasDesign of Purlins: Try 75mm X 100mm: Case 1Pamela Joanne Falo AndradeAinda não há avaliações

- A Detailed Lesson PlanDocumento5 páginasA Detailed Lesson PlanIsaac-elmar Agtarap74% (23)

- Line Follower Robot - J4rv4i1010Documento4 páginasLine Follower Robot - J4rv4i1010Journal 4 ResearchAinda não há avaliações

- (Ebook - Antroposofia - EnG) - Rudolf Steiner - Fundamentals of TheraphyDocumento58 páginas(Ebook - Antroposofia - EnG) - Rudolf Steiner - Fundamentals of Theraphyblueyes247Ainda não há avaliações

- A Review Study On Gas-Solid Cyclone Separator Using Lapple Model - J4rv4i1001Documento5 páginasA Review Study On Gas-Solid Cyclone Separator Using Lapple Model - J4rv4i1001Journal 4 ResearchAinda não há avaliações

- Introduction: Meaning of HypothesisDocumento8 páginasIntroduction: Meaning of HypothesisMANISH KUMARAinda não há avaliações

- 03 IGT-Influence of Codes Guidelines and Other Regulations On The Tunnel Design in AustriaDocumento48 páginas03 IGT-Influence of Codes Guidelines and Other Regulations On The Tunnel Design in AustriaSudarshan GadalkarAinda não há avaliações

- STW 44 3 2 Model Course Leadership and Teamwork SecretariatDocumento49 páginasSTW 44 3 2 Model Course Leadership and Teamwork Secretariatwaranchai83% (6)

- Design and Analysis of Hydraulic Actuator in A Typical Aerospace Vehicle - J4RV4I2003Documento10 páginasDesign and Analysis of Hydraulic Actuator in A Typical Aerospace Vehicle - J4RV4I2003Journal 4 ResearchAinda não há avaliações

- IoT Based Digital Agriculture Monitoring System and Their Impact On Optimal Utilization of Resources - J4RV4I1017Documento6 páginasIoT Based Digital Agriculture Monitoring System and Their Impact On Optimal Utilization of Resources - J4RV4I1017Journal 4 ResearchAinda não há avaliações

- Movie Recommendation System - J4RV4I1016Documento8 páginasMovie Recommendation System - J4RV4I1016Journal 4 ResearchAinda não há avaliações

- Experimental Verification and Validation of Stress Distribution of Composite Beam With Metal Beam With Different Support Conditions - J4RV4I2002Documento2 páginasExperimental Verification and Validation of Stress Distribution of Composite Beam With Metal Beam With Different Support Conditions - J4RV4I2002Journal 4 ResearchAinda não há avaliações

- Image Binarization For The Uses of Preprocessing To Detect Brain Abnormality Identification - J4RV4I2001Documento4 páginasImage Binarization For The Uses of Preprocessing To Detect Brain Abnormality Identification - J4RV4I2001Journal 4 ResearchAinda não há avaliações

- Movie Recommendation System - J4RV4I1016Documento8 páginasMovie Recommendation System - J4RV4I1016Journal 4 ResearchAinda não há avaliações

- A Review Paper On Bfo and Pso Based Movie Recommendation System - J4rv4i1015Documento6 páginasA Review Paper On Bfo and Pso Based Movie Recommendation System - J4rv4i1015Journal 4 ResearchAinda não há avaliações

- An Overview: Daknet Technology - Broadband Ad-Hoc Connectivity - J4rv4i1009Documento4 páginasAn Overview: Daknet Technology - Broadband Ad-Hoc Connectivity - J4rv4i1009Journal 4 ResearchAinda não há avaliações

- A Review On Design of Public Transportation System in Chandrapur City - J4rv4i1007Documento7 páginasA Review On Design of Public Transportation System in Chandrapur City - J4rv4i1007Journal 4 ResearchAinda não há avaliações

- Hci Based Application For Playing Computer Games - J4rv4i1014Documento5 páginasHci Based Application For Playing Computer Games - J4rv4i1014Journal 4 ResearchAinda não há avaliações

- Laboratory Study of Strong, Moderate and Weak Sandstones - J4rv4i1012Documento8 páginasLaboratory Study of Strong, Moderate and Weak Sandstones - J4rv4i1012Journal 4 ResearchAinda não há avaliações

- Design Analysis and Fabrication of Manual Rice Transplanting Machine - J4rv4i1011Documento5 páginasDesign Analysis and Fabrication of Manual Rice Transplanting Machine - J4rv4i1011Journal 4 ResearchAinda não há avaliações

- A Review On Lifting and Assembly of Rotary Kiln Tyre With Shell by Flexible Gripper - J4rv4i1013Documento3 páginasA Review On Lifting and Assembly of Rotary Kiln Tyre With Shell by Flexible Gripper - J4rv4i1013Journal 4 ResearchAinda não há avaliações

- Chatbot For College Related Queries - J4rv4i1008Documento5 páginasChatbot For College Related Queries - J4rv4i1008Journal 4 ResearchAinda não há avaliações

- An Implementation For Framework For Chemical Structure Using Graph Grammar - J4rv3i12022Documento9 páginasAn Implementation For Framework For Chemical Structure Using Graph Grammar - J4rv3i12022Journal 4 ResearchAinda não há avaliações

- Unmanned Aerial Vehicle For Remittance - J4rv3i12023Documento6 páginasUnmanned Aerial Vehicle For Remittance - J4rv3i12023Journal 4 ResearchAinda não há avaliações

- An Integrated Approach To Reduce Intra City Traffic at Coimbatore - J4rv4i1002Documento6 páginasAn Integrated Approach To Reduce Intra City Traffic at Coimbatore - J4rv4i1002Journal 4 ResearchAinda não há avaliações

- Use of Galvanized Steels For Automotive Body - Car Survey Results at Coastal Areas, Mumbai - J4rv3i12013Documento7 páginasUse of Galvanized Steels For Automotive Body - Car Survey Results at Coastal Areas, Mumbai - J4rv3i12013Journal 4 ResearchAinda não há avaliações

- Image Segmentation Using FCM Algoritm - J4rv3i12021Documento3 páginasImage Segmentation Using FCM Algoritm - J4rv3i12021Journal 4 ResearchAinda não há avaliações

- Survey On A Modern Medicare System Using Internet of Things - J4rv3i12024Documento3 páginasSurvey On A Modern Medicare System Using Internet of Things - J4rv3i12024Journal 4 ResearchAinda não há avaliações

- Model Based Analysis of Temperature Process Under Various Control Strategies - J4rv3i12010Documento4 páginasModel Based Analysis of Temperature Process Under Various Control Strategies - J4rv3i12010Journal 4 ResearchAinda não há avaliações

- Automated Headlight Control Using Labview - J4rv3i12018Documento5 páginasAutomated Headlight Control Using Labview - J4rv3i12018Journal 4 ResearchAinda não há avaliações

- 3-Axial Automated Bowling Arm - J4rv3i12012Documento5 páginas3-Axial Automated Bowling Arm - J4rv3i12012Journal 4 ResearchAinda não há avaliações

- Design A Two Stage Grid Connected PV Systems With Constant Power Generation and Input Output Linearizer Controller - J4rv3i12015Documento5 páginasDesign A Two Stage Grid Connected PV Systems With Constant Power Generation and Input Output Linearizer Controller - J4rv3i12015Journal 4 ResearchAinda não há avaliações

- Advanced Civil Engineering Optimization by Artificial Intelligent Systems: Review - J4rv3i12004Documento3 páginasAdvanced Civil Engineering Optimization by Artificial Intelligent Systems: Review - J4rv3i12004Journal 4 ResearchAinda não há avaliações

- Space Exploration Rover Using Labview - J4rv3i12011Documento8 páginasSpace Exploration Rover Using Labview - J4rv3i12011Journal 4 ResearchAinda não há avaliações

- Sensor Fault Identification in Complex Systems - J4rv3i12007Documento7 páginasSensor Fault Identification in Complex Systems - J4rv3i12007Journal 4 ResearchAinda não há avaliações

- Design and Modification of Green Building Aspect at Jilla Sevasadan, Vyara - J4rv3i12006Documento6 páginasDesign and Modification of Green Building Aspect at Jilla Sevasadan, Vyara - J4rv3i12006Journal 4 ResearchAinda não há avaliações

- Icc Esr-2302 Kb3 ConcreteDocumento11 páginasIcc Esr-2302 Kb3 ConcretexpertsteelAinda não há avaliações

- Full Download University Physics With Modern Physics 14th Edition Young Test Bank PDF Full ChapterDocumento13 páginasFull Download University Physics With Modern Physics 14th Edition Young Test Bank PDF Full Chapterpoetrycloudyzjm12q100% (19)

- The Teacher Research Movement: A Decade Later: Cite This PaperDocumento13 páginasThe Teacher Research Movement: A Decade Later: Cite This PaperAlexandre NecromanteionAinda não há avaliações

- Support Vector Machine Master ThesisDocumento7 páginasSupport Vector Machine Master Thesistammymajorsclarksville100% (2)

- Paper 1 Computer Science ASDocumento194 páginasPaper 1 Computer Science ASLailaEl-BeheiryAinda não há avaliações

- DC Generator - Construction, Working Principle, Types, and Applications PDFDocumento1 páginaDC Generator - Construction, Working Principle, Types, and Applications PDFGokul GokulAinda não há avaliações

- Swift As A MisanthropeDocumento4 páginasSwift As A MisanthropeindrajitAinda não há avaliações

- MCFKTP G3 S2 SC Number Pattern PuzzlesDocumento5 páginasMCFKTP G3 S2 SC Number Pattern PuzzlesEric GoAinda não há avaliações

- Pot-Roasted Beef BrisketDocumento4 páginasPot-Roasted Beef Brisketmarcelo nubileAinda não há avaliações

- Antenatal Care (ANC)Documento77 páginasAntenatal Care (ANC)tareAinda não há avaliações

- DatuinMA (Activity #5 - NSTP 10)Documento2 páginasDatuinMA (Activity #5 - NSTP 10)Marc Alen Porlaje DatuinAinda não há avaliações

- Chain: SRB Series (With Insulation Grip)Documento1 páginaChain: SRB Series (With Insulation Grip)shankarAinda não há avaliações

- Department of Education: Republic of The PhilippinesDocumento2 páginasDepartment of Education: Republic of The PhilippinesISMAEL KRIS DELA CRUZAinda não há avaliações

- 한국항만 (영문)Documento38 páginas한국항만 (영문)hiyeonAinda não há avaliações

- Sub-Wings of YuvanjaliDocumento2 páginasSub-Wings of Yuvanjalin_tapovan987100% (1)

- LT3845ADocumento26 páginasLT3845Asoft4gsmAinda não há avaliações

- Lecture BouffonDocumento1 páginaLecture BouffonCarlos Enrique GuerraAinda não há avaliações

- MSDS Leadframe (16 Items)Documento8 páginasMSDS Leadframe (16 Items)bennisg8Ainda não há avaliações

- Pipe Freezing StudyDocumento8 páginasPipe Freezing StudymirekwaznyAinda não há avaliações

- Module 5Documento14 páginasModule 5shin roseAinda não há avaliações

- Microsome S9 Prep ProtocolDocumento22 páginasMicrosome S9 Prep ProtocolSAN912Ainda não há avaliações