Escolar Documentos

Profissional Documentos

Cultura Documentos

Ejemplo de Diseño Del Proyecto #1 PDF

Enviado por

LuceroMilagrosCubaMirandaTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Ejemplo de Diseño Del Proyecto #1 PDF

Enviado por

LuceroMilagrosCubaMirandaDireitos autorais:

Formatos disponíveis

DEPARTAMENTO DE ELECTRONICA

Ejemplo de diseo del Proyecto N 1

La empresa de potabilizacin de agua dispone de un tanque de decantacin

y desea desde una sala de control monitorear algunas caractersticas de los

mismos.

Supongamos tener un tanque con agua, el cual puede variar entre 0 y 7 unidades;

adems se tiene la posibilidad de fijar un valor predeterminado como nivel de

referencia. Tanto el tanque con agua como el nivel de referencia lo simularemos

con la PC mediante una planta realizada en Visual Basic, y estos dos valores los

tendremos disponibles en binario en el puerto paralelo de la PC como se muestra a

continuacin:

Se quiere mostrar en un Display alguna de las siguientes opciones:

1. Si el valor del nivel de agua del tanque NT es menor al de referencia NR

fijado por el usuario deber mostrarse en el display el Nivel del Tanque.

2. Si el valor del nivel de agua del tanque es igual al de referencia fijado por el

usuario deber mostrarse en el display el Nivel del Tanque Titilando.

3. Si el valor del nivel de agua del tanque es mayor al de referencia fijado por

el usuario deber mostrarse en el display El nmero 8 mostrando de

esta manera que hay un problema.

Ejemplo de diseo del Proyecto N 1 Electrnica Digital I Hoja 1 de 6

DEPARTAMENTO DE ELECTRONICA

El esquema general del proyecto sera:

CIRCUITO A

DISEAR

El diagrama de Bloques correspondiente al diseo de este proyecto es el

siguiente:

M

U

NT DECO

L

DIFIC

T ADOR

I

P

L BCD

E

C 8 X

NT 7

O O SEG

M R

P

A

R

A NT > R

D

O

LGICA

NT = R

NR R DE CLOCK

NT < R CONTROL

Segn este diagrama de bloques podemos observar que para el diseo de este

proyecto, se necesitan los siguientes elementos:

a) Un comparador numrico quien tendr que comparar el valor del Nivel

del tanque NT con el de referencia NR y segn sea su comportamiento

actuar en consecuencia.

b) Un display quien mostrar los valores numricos requeridos, ya sean del

nivel del tanque NT o el nmero 8

c) Un decodificador BCD a 7 segmentos que actuar sobre el display.

d) Un selector (Multiplexor) quien deber seleccionar segn sea el caso, el

valor del nivel del tanque NT o el Nmero 8, dicho valor ser enviado al

decodificador para ser mostrado luego en el display.

e) Un clock que ser utilizado para que titile el display, cuando el valor del

nivel del tanque sea igual al de referencia NT = NR.

f) Una lgica de control que estar encargada de accionar el selector y el

control de apagado del display utilizando como informacin los datos

provenientes del comparador y la seal de clock.

Ejemplo de diseo del Proyecto N 1 Electrnica Digital I Hoja 2 de 6

DEPARTAMENTO DE ELECTRONICA

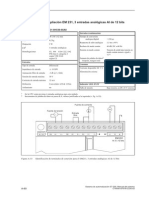

Los circuitos integrados que utilizaremos y las consideraciones a tener en cuenta

de los mismos son las siguientes:

a) Como Comparador de magnitud de 4 bits utilizaremos el circuito

integrado CD-4585 que tiene la posibilidad de comparar 2 nmeros binarios

de 4 bits, llamados A ( A3 A2 A1 A0 ) y B ( B3 B2 B1 B0 ) y entregar en una

de sus 3 salidas la informacin de esa comparacin. Las entradas de este

componente estarn conectadas al puerto paralelo de la PC por el cual la

misma entregar la informacin correspondiente al Nivel del Tanque NT

que estar conectada a las entradas correspondientes al nmero A y al

Nivel de Referencia NR conectadas a las entradas del nmero B. Como

la informacin proveniente de la PC corresponde a 2 nmeros entre 0 y 7 y

su representacin en binario estar dada por 3 bits cada uno, el cuarto bit o

sea el A3 y el B3 debern estar conectados a nivel bajo (0) o bien enviar

desde la PC la informacin como nmero binario de 4 bits cada uno.

La informacin de salida, ser a un (1) en la salida A < B , A = B , o A > B,

segn corresponda y un (0) en las otras dos. Cabe destacar que como este

componente suele ser utilizado para comparar nmeros de ms de un dgito

posee 3 entradas de informacin A < B , A = B , o A > B, que se utilizan en

cadena o sea que por ejemplo las salidas del circuito integrado

correspondiente a las decenas se conectan a las entradas correspondientes

de las unidades, En nuestro caso como slo compararemos nmeros de un

dgito entre 0 y 7 estas entradas debern conectarse de la siguiente

manera, A < B, y A > B a nivel bajo (0), y A = B a nivel alto (1) indicando

que los dgitos anteriores de ambos nmeros son iguales.

b) El Display que se utilizar ser del tipo Ctodo Comn, pues como se ver

en el tem siguiente, el decodificador entrega valores altos para los LEDs

correspondientes a los segmentos. Adems se deber conectar en serie

con cada segmento una resistencia limitadora de corriente cuyo valor

deber estar entre 180 y 680 ya que se utilizar como fuente de

alimentacin una tensin de 5 V.

c) Como Decodificador BCD a 7 Segmentos utilizaremos el circuito integrado

CD-4511 quien entrega los valores de los segmentos en lgica positiva, o

sea que cuando se quiere mostrar un nmero, este deber ingresarse por

los pines de entrada D-C-B-A como numero binario ( BCD) y a la salida se

pondrn en uno los pines correspondientes a-b-c-d-e-f-g que luego

activarn los segmentos del display. Adems este componente posee 3

entradas de control, una entrada /LT Lamp Test que se acciona con nivel

bajo y se utiliza para testear las salidas llevndolas todas a nivel alto, por

lo que en nuestro caso deber estar conectada a nivel alto (1) para poder

mostrar en el display los distintos nmeros; otra entrada LE Latch Enable

que se acciona con nivel alto y se utiliza para memorizar el nmero que se

est mostrando, o sea que aunque los datos de entrada al decodificador

este sigue mostrando el nmero memorizado; como en este proyecto esta

propiedad no la necesitamos deberemos conectarla a nivel bajo (0). Por

ltimo una entrada /BI Blanking Input que se activa con nivel bajo y se

utiliza para apagar el display.

Ejemplo de diseo del Proyecto N 1 Electrnica Digital I Hoja 3 de 6

DEPARTAMENTO DE ELECTRONICA

d) El Multiplexor Demultiplexor que se utilizar como selector es el circuito

integrado CD-4551 el cual es un selector cudruple de 2 posiciones o sea

que podremos utilizarlo para elegir uno de dos nmeros de 4 bits. En la

posicin (0) Z0 Y0 X0 W0 conectaremos el nmero correspondiente al Nivel

del Tanque T3 T2 T1 T0 y en la posicin (1) Z1 Y1 X1 W1 conectaremos el

valor binario correspondiente al Nmero 8 o sea el 1 0 0 0. La eleccin de

uno de estos dos valores estar comandada por el circuito correspondiente

a la lgica de control y el nmero seleccionado estar disponible en los

terminales de salida Z Y X W los que se conectarn a las entradas D C B A

del decodificador BCD a 7 Segmentos.

e) El Clock se armar de la manera tradicional, con 2 compuertas NAND

Schmitt Trigger del circuito integrado CD-4093 y el perodo del mismo

depender de los valores de R y C que se adopten. En este caso al utilizar

un valor de R =1 M y un valor de C = 1 F el perodo estar en el orden de

1 segundo que es un valor aceptable para ver titilar un nmero en el

display.

f) La Lgica de Control se disear a continuacin teniendo en cuenta las

especificaciones a cumplir. Para ello armaremos una tabla de verdad con la

informacin de entrada que disponemos o sea los valores correspondientes

a las salidas del comparador ( < ) , ( = ) y ( > ) y la seal de Clock ; y las dos

salidas que tendremos correspondern al terminal de control del

Multiplexor y al /BI del Conversor BCD 7 Segmentos. Luego de llenar la

tabla con las consideraciones correspondientes se volcarn los valores a

dos diagramas de Karnaugh para proceder a la simplificacin de las dos

funciones de salida.

Las consideraciones a tener en cuenta para el llenado de la tabla de verdad

son las siguientes:

Las salidas del comparador slo pueden tener un estado en alto a la

vez por lo que los estados en que haya mas de un 1 o las 3 salidas

en 0 sern consideradas X o sea al no ser un caso posible de ocurrir,

se lo puede tomar como un comodin.

El terminal de Control del Multiplexor al estar en estado bajo (0)

seleccionar el valor del Nivel del Tanque y al estar en estado alto

(1) seleccionar el Nmero ( 8 ) por lo que estar en estado bajo 0

para las condiciones NT < NR y NT = NR estar en estado alto 1

para la condicin NT > NR independientemente del valor del Clock.

El terminal /BI deber estar siempre en estado alto 1 para mostrar el

valor correspondiente al Nivel del Tanque NT o al Nmero 8, salvo

en la condicin NT = NR en el que deber alternar entre 0 y 1 para

lograr el efecto que el nmero Titile; esto se lograr colocando en la

condicin NT = NR un nivel alto 1 cuando el Clock est en bajo y un

nivel bajo 0 cuando el Clock est en alto, aunque esto podra

considerarse a la inversa pues producira el mismo efecto.

Ejemplo de diseo del Proyecto N 1 Electrnica Digital I Hoja 4 de 6

DEPARTAMENTO DE ELECTRONICA

Los valores de las variables de entrada y salida, para mayor

comodidad las designaremos de la siguiente manera:

m corresponde a NT < NR

I NT = NR

M NT > NR

CK corresponde a Clock

C Control

/BI Blank

La tabla de verdad y los diagramas de Karnaugh seran los siguientes:

CK m I M C /BI I I

0 0 0 0 X X IM

0 0 0 1 1 1 CKm 00 01 11 10

0 0 1 0 0 1 00 X 1 X 0 m

0 0 1 1 X X

0 1 0 0 0 1 CK

01 0 X X X

0 1 0 1 X X

0 1 1 0 X X m

0 1 1 1 X X 11 0 X X X

1 0 0 0 X X CK

1 0 0 1 1 1 10 X 1 X 0 m

1 0 1 0 0 0

1 0 1 1 X X

1 1 0 0 0 1 M M M

1 1 0 1 X X

1 1 1 0 X X

1 1 1 1 X X

De este diagrama de Karnaugh se puede determinar que la expresin

correspondiente a la salida C:

C =M

Deducimos as, que el terminal de Control del Multiplexor deber estar conectado

a la salida A > B del Comparador que corresponde a la condicin NT > NR.

Ejemplo de diseo del Proyecto N 1 Electrnica Digital I Hoja 5 de 6

DEPARTAMENTO DE ELECTRONICA

Del segundo diagrama de

I I Karnaugh se obtiene que la

IM expresin correspondiente a la

CKm 00 01 11 10 entrada /BI ser la siguiente:

00 X 1 X 1 m

CK

1 X X X

BI = I + CK

01

m Si aplicamos el postulado de De

11 1 X X X Morgan para convertir la expresin

CK a lgica NAND quedar:

10 X 1 X 0 m

BI = I + CK

M M M

BI = I * CK

Debido A lo demostrado, el terminal /BI del decodificador BCD a 7

Segmentos deber estar accionado por una compuerta NAND cuyas

entradas estarn conectadas una a la salida A > B del Comparador y la otra

conectada al circuito de Clock. Esta compuerta NAND como las del Clock

corresponden al mismo Circuito Integrado.

El Circuito Esquemtico de este proyecto quedara:

MULTIPLEXOR DECODIFICADOR

W0 W A a

X0 X B

b

Y0 Y C BCD c

Z0 Z D

7 d

0 W1 SEG e

1 LT

0 X1 f

0 Y1 0 LE g

1 Z1

BI 4511

4551

Cont

COMPARADOR

A0

A>B

A1

N A2

T

A3

O A=B

4585 U

N T

B0 Lgica de Control

R

B1

A<B

B2

Clock

B3

IN

0 1 0

A>B A=B A>B

Ejemplo de diseo del Proyecto N 1 Electrnica Digital I Hoja 6 de 6

Você também pode gostar

- Ejemplo de Diseño Del Proyecto #1 PDFDocumento6 páginasEjemplo de Diseño Del Proyecto #1 PDFBill GonzálezAinda não há avaliações

- DAC: Convertidor digital analógicoDocumento10 páginasDAC: Convertidor digital analógicoLuis VrgsAinda não há avaliações

- Sislab 1Documento14 páginasSislab 1Erick Alvarez CastañedaAinda não há avaliações

- Practica 6.comparador de 8 BitesDocumento7 páginasPractica 6.comparador de 8 BitesCarlos Andres CujiAinda não há avaliações

- Convertidor DADocumento34 páginasConvertidor DAEric Dueñas TrujilloAinda não há avaliações

- Lab# 4 - Conversor AD (Análogo/Digital), Ing. Docente de La Materia Microcontroladores, Desiderio Arancibia Rivera (Escuela Militar de Ingenieria)Documento8 páginasLab# 4 - Conversor AD (Análogo/Digital), Ing. Docente de La Materia Microcontroladores, Desiderio Arancibia Rivera (Escuela Militar de Ingenieria)The history fuck manAinda não há avaliações

- TareaDocumento7 páginasTareaHenrySolórzanoMartelAinda não há avaliações

- Logica Digital Examen de InternteDocumento3 páginasLogica Digital Examen de InternteUreña Personaje Jesus UreñaAinda não há avaliações

- Práctica No 5-ELE1Documento12 páginasPráctica No 5-ELE1Juan CarlosAinda não há avaliações

- P05 Programacion en MikroBasicDocumento9 páginasP05 Programacion en MikroBasicRicardo NarvaezAinda não há avaliações

- Parcial3 201516Documento8 páginasParcial3 201516Mario Zurrón MartinAinda não há avaliações

- Convertidor Analogico Digital R2RDocumento7 páginasConvertidor Analogico Digital R2RSergio Limck Plnckk100% (1)

- Conversor Análogico Digital Del PIC 16F870Documento40 páginasConversor Análogico Digital Del PIC 16F870Whendy GarciaAinda não há avaliações

- Contadores BinariosDocumento8 páginasContadores BinariosDonny QuinteroAinda não há avaliações

- Examen 12Documento7 páginasExamen 12Belkis HernándezAinda não há avaliações

- Lectura del ADC de 8 y 10 bits en PIC y CDocumento16 páginasLectura del ADC de 8 y 10 bits en PIC y CJuan Pablo Garcia LanderoAinda não há avaliações

- Display de 7 SegmentosDocumento10 páginasDisplay de 7 SegmentosCajamarca AlexAinda não há avaliações

- Informe-Practica de Digitales (Codificadores BDC)Documento7 páginasInforme-Practica de Digitales (Codificadores BDC)IvanGomezGAinda não há avaliações

- Proyecto de Circuitos DigitalesDocumento9 páginasProyecto de Circuitos Digitaleslinuzx15Ainda não há avaliações

- Contador de Dos (2) DigitosDocumento9 páginasContador de Dos (2) DigitosPAPOFULEAinda não há avaliações

- Convertidores Analogicos Digitales y Digitales AnalogicosDocumento7 páginasConvertidores Analogicos Digitales y Digitales AnalogicosCristian ChimboAinda não há avaliações

- Tarea 7 DiseñodelprogramadeuncontadorDocumento8 páginasTarea 7 DiseñodelprogramadeuncontadorEstefania Rodriguez SanchezAinda não há avaliações

- Guia - ADC0808Documento6 páginasGuia - ADC0808Eduardo Mayorga EspejoAinda não há avaliações

- Proyecto Termometro DigitalDocumento21 páginasProyecto Termometro Digitalxamtugil84070% (1)

- Simulación Conversioes A2D y D2ADocumento7 páginasSimulación Conversioes A2D y D2AEligio VásquezAinda não há avaliações

- Informe 1Documento9 páginasInforme 1Yih LibedAinda não há avaliações

- Uso Del Adc Con Pic16f877 - Display de 7 SegmentosDocumento5 páginasUso Del Adc Con Pic16f877 - Display de 7 SegmentosSolano NaolsAinda não há avaliações

- Proyecto Dado DigitalDocumento2 páginasProyecto Dado DigitalAnonymous vDTinHoU9Ainda não há avaliações

- PRACTICA9Documento20 páginasPRACTICA9Mauricio OrtegaAinda não há avaliações

- Practica 2.1 - Codificadores y DecodificadoresDocumento7 páginasPractica 2.1 - Codificadores y DecodificadoresFabián Calzada DelgadoAinda não há avaliações

- ADC Aproximaciones SucesivasDocumento29 páginasADC Aproximaciones SucesivasRamses GarateAinda não há avaliações

- Conversor de CodigoDocumento11 páginasConversor de Codigotefanizamora1317100% (1)

- Sep 03Documento9 páginasSep 03Sasuke BacusAinda não há avaliações

- Decodificador BCD A 7 Segmentos 2009Documento6 páginasDecodificador BCD A 7 Segmentos 2009Rosario Trejo CerinoAinda não há avaliações

- Conteo Con Display y Timer en C (PIC16F628A)Documento2 páginasConteo Con Display y Timer en C (PIC16F628A)Fátima QuijasAinda não há avaliações

- Conversores DAC y ADCDocumento13 páginasConversores DAC y ADChernanmp89Ainda não há avaliações

- Sistemas AnalogicosDocumento9 páginasSistemas AnalogicosDavid Leonardo Higuera CamargoAinda não há avaliações

- Contador Del 0 Al 9Documento3 páginasContador Del 0 Al 9Christian Villon PradoAinda não há avaliações

- Tipos de Displays de 7 SegmentosDocumento19 páginasTipos de Displays de 7 SegmentosAnonymous H3E7i3Yzyd100% (1)

- PLC IiDocumento88 páginasPLC IiCarlos Andre Yuri LaraAinda não há avaliações

- Convertidores Analogo-DigitalDocumento22 páginasConvertidores Analogo-DigitalBerenice FraireAinda não há avaliações

- Tipos de ADCDocumento6 páginasTipos de ADCJhony SiguenzaAinda não há avaliações

- Cronómetro Digital Con Parada Programable N 4-052Documento4 páginasCronómetro Digital Con Parada Programable N 4-052diegoAinda não há avaliações

- Actividad 4.1Documento6 páginasActividad 4.1Dimas Ramirez PortasAinda não há avaliações

- Diseño de decoder BCD y ALU de 4 bitsDocumento14 páginasDiseño de decoder BCD y ALU de 4 bitsJoaquin QuinterosAinda não há avaliações

- Catagña Alcoser Yupanqui Conversor Analogico Digital p3Documento9 páginasCatagña Alcoser Yupanqui Conversor Analogico Digital p3luisAinda não há avaliações

- TP Final - Sensor de Temperatura Con AlarmaDocumento24 páginasTP Final - Sensor de Temperatura Con AlarmaJuanCarrizoBondazAinda não há avaliações

- 04 - Subsistemas Digitales PDFDocumento9 páginas04 - Subsistemas Digitales PDFPaula CabreraAinda não há avaliações

- Sistemas digitales - Decodificadores y multiplexoresDocumento9 páginasSistemas digitales - Decodificadores y multiplexoresashe goodAinda não há avaliações

- 04 - Subsistemas DigitalesDocumento9 páginas04 - Subsistemas DigitalesEmiliano BraidaAinda não há avaliações

- 04 - Subsistemas DigitalesDocumento9 páginas04 - Subsistemas DigitalesgabrielAinda não há avaliações

- Guia 3Documento8 páginasGuia 3jonatanAinda não há avaliações

- Manejo de PerifericosDocumento135 páginasManejo de PerifericosGabby Michelle OrtizAinda não há avaliações

- Configuración ADC PIC18F8722 10 bitsDocumento5 páginasConfiguración ADC PIC18F8722 10 bitsDavid EspinosaAinda não há avaliações

- Laboratorio de circuitos ADC y DAC de 3 bitsDocumento12 páginasLaboratorio de circuitos ADC y DAC de 3 bitsosmarAinda não há avaliações

- Sumador AritmeticoDocumento9 páginasSumador AritmeticoBrian ZM100% (1)

- Proyecto MicroDocumento40 páginasProyecto Microjhompix50% (2)

- Conversor Analógico Digital - Adc: Usted Puede Ver Los 4 Niveles en La Siguiente IlustraciónDocumento6 páginasConversor Analógico Digital - Adc: Usted Puede Ver Los 4 Niveles en La Siguiente IlustraciónLeira Nahitsirc IhcamilAinda não há avaliações

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaNo EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAinda não há avaliações

- Problemas resueltos de Hidráulica de CanalesNo EverandProblemas resueltos de Hidráulica de CanalesNota: 4.5 de 5 estrelas4.5/5 (7)

- Get ConnectedDocumento1 páginaGet ConnectedLuceroMilagrosCubaMiranda100% (1)

- Temario Az FundamentalsDocumento2 páginasTemario Az FundamentalsLuceroMilagrosCubaMirandaAinda não há avaliações

- Modulo 1 v2Documento19 páginasModulo 1 v2LuceroMilagrosCubaMirandaAinda não há avaliações

- Novedades HTML 5 y MultimediaDocumento2 páginasNovedades HTML 5 y MultimediaLuceroMilagrosCubaMiranda100% (1)

- Casos prácticos HTML tablas 1-100Documento3 páginasCasos prácticos HTML tablas 1-100LuceroMilagrosCubaMirandaAinda não há avaliações

- Trabajar en EquipoDocumento6 páginasTrabajar en EquipoUriel Vera RockmanAinda não há avaliações

- RFB ProtocolDocumento1 páginaRFB ProtocolLuceroMilagrosCubaMirandaAinda não há avaliações

- Accesibilidad y Usabilidad en Paginas WebDocumento4 páginasAccesibilidad y Usabilidad en Paginas WebLuceroMilagrosCubaMirandaAinda não há avaliações

- ChatDocumento2 páginasChatLuceroMilagrosCubaMirandaAinda não há avaliações

- Diseño Web Con HTML5 + CSSDocumento3 páginasDiseño Web Con HTML5 + CSSLuceroMilagrosCubaMiranda100% (1)

- Posicionamiento SEO Y Trabajo en EquipoDocumento3 páginasPosicionamiento SEO Y Trabajo en EquipoLuceroMilagrosCubaMiranda60% (5)

- Accesibilidad y Usabilidad en Paginas WebDocumento4 páginasAccesibilidad y Usabilidad en Paginas WebLuceroMilagrosCubaMirandaAinda não há avaliações

- Herramientas para Trabajar Con HTML5Documento3 páginasHerramientas para Trabajar Con HTML5LuceroMilagrosCubaMirandaAinda não há avaliações

- Curso CiberseguridadDocumento10 páginasCurso CiberseguridadLuceroMilagrosCubaMirandaAinda não há avaliações

- Fast Call For HelpDocumento1 páginaFast Call For HelpLuceroMilagrosCubaMirandaAinda não há avaliações

- Modulo 2Documento7 páginasModulo 2LuceroMilagrosCubaMirandaAinda não há avaliações

- Introducción A Las Redes de Computadoras 2016Documento31 páginasIntroducción A Las Redes de Computadoras 2016CamilaAbiTorresAinda não há avaliações

- La Capa FísicaDocumento49 páginasLa Capa FísicaMishelzhitha CalderónAinda não há avaliações

- PatricioDocumento2 páginasPatricioLuceroMilagrosCubaMirandaAinda não há avaliações

- Biosensors MonografiaDocumento27 páginasBiosensors MonografiaLuceroMilagrosCubaMirandaAinda não há avaliações

- Control Digital Introducción SistemasDocumento12 páginasControl Digital Introducción SistemasAndrés Calagua OrtizAinda não há avaliações

- Laboratorio N4Documento1 páginaLaboratorio N4LuceroMilagrosCubaMirandaAinda não há avaliações

- TUTORÍADocumento14 páginasTUTORÍALuceroMilagrosCubaMirandaAinda não há avaliações

- Curva densidad líneas telefónicas Perú años 1-40Documento2 páginasCurva densidad líneas telefónicas Perú años 1-40LuceroMilagrosCubaMirandaAinda não há avaliações

- 366 844 2 PBDocumento21 páginas366 844 2 PBLuceroMilagrosCubaMirandaAinda não há avaliações

- Ex PosicionDocumento42 páginasEx PosicionsesechaAinda não há avaliações

- Final RedesDocumento9 páginasFinal RedesLuceroMilagrosCubaMirandaAinda não há avaliações

- Ingenieria de ControlDocumento7 páginasIngenieria de ControlLuceroMilagrosCubaMirandaAinda não há avaliações

- Fuentes verificación estándares calidadDocumento19 páginasFuentes verificación estándares calidadLuceroMilagrosCubaMiranda100% (1)

- La Capa FísicaDocumento49 páginasLa Capa FísicaMishelzhitha CalderónAinda não há avaliações

- Código Binario (Resumen)Documento9 páginasCódigo Binario (Resumen)luismf14Ainda não há avaliações

- Estructura y Tecnologia de ComputadoresDocumento392 páginasEstructura y Tecnologia de Computadoresemail4556Ainda não há avaliações

- Manual de Clases Arq. ComputacionalDocumento46 páginasManual de Clases Arq. ComputacionalZoilo juan nkogo bayemeAinda não há avaliações

- Diagnostico 1 Semestre Cultura DigitalDocumento9 páginasDiagnostico 1 Semestre Cultura DigitalProfa Patty Martínez AraizaAinda não há avaliações

- Topicos Avanzados Programacion Java NetbeansDocumento33 páginasTopicos Avanzados Programacion Java NetbeanscahecazAinda não há avaliações

- Glosario InformaticoDocumento88 páginasGlosario InformaticoFabio DuránAinda não há avaliações

- Protocolo RC-5 controles remotos infrarrojosDocumento6 páginasProtocolo RC-5 controles remotos infrarrojosHectorLopezAinda não há avaliações

- Autocad 2012 PDF Dxf-Reference EnuDocumento270 páginasAutocad 2012 PDF Dxf-Reference EnuCarlos Enrique PérezAinda não há avaliações

- Entrega 3Documento4 páginasEntrega 3Gabo FrancoAinda não há avaliações

- SistemasNumeraciónBásicaDocumento24 páginasSistemasNumeraciónBásicaLuis MoralesAinda não há avaliações

- Hadware y Sistemas OperativosDocumento11 páginasHadware y Sistemas OperativosBeatriz Noria SerranoAinda não há avaliações

- II 1920 Python PDFDocumento39 páginasII 1920 Python PDFAlberto Felipez GarciaAinda não há avaliações

- Cuestionario Introducción ArduinoDocumento5 páginasCuestionario Introducción ArduinoLuis Calupiña100% (1)

- A.33 Módulo de Ampliación EM 231, 3 Entradas Analógicas AI de 12 BitsDocumento9 páginasA.33 Módulo de Ampliación EM 231, 3 Entradas Analógicas AI de 12 BitsmcsecAinda não há avaliações

- Introduccion Control Logix 5000Documento20 páginasIntroduccion Control Logix 5000Ulises Pino VidalAinda não há avaliações

- Introducción al lenguaje PascalDocumento49 páginasIntroducción al lenguaje PascalKarl NchAinda não há avaliações

- 1756-Pm014 - Es-P Control Adores Logix5000 Fallos Mayores y MenoresDocumento32 páginas1756-Pm014 - Es-P Control Adores Logix5000 Fallos Mayores y Menoresnelsongil211Ainda não há avaliações

- Curso PLCDocumento102 páginasCurso PLCchesterbrenes100% (18)

- Cómo controlar un display LCD con el controlador HD44780Documento27 páginasCómo controlar un display LCD con el controlador HD44780ED Diego Ramirez CHAinda não há avaliações

- Indroduccion A La Electronica Digital PDFDocumento30 páginasIndroduccion A La Electronica Digital PDFalexAinda não há avaliações

- INFORME Sensor HallDocumento8 páginasINFORME Sensor HallWaniel Calvache100% (1)

- Apuntes PrograDocumento33 páginasApuntes PrograErick Perez ChavezAinda não há avaliações

- Control RemotoDocumento5 páginasControl RemotoJohn DuarteAinda não há avaliações

- Introduccion MicrosDocumento28 páginasIntroduccion MicrosperlepoliAinda não há avaliações

- MOUSEDocumento13 páginasMOUSEgabi g.100% (52)

- Transimison Sincrona y AsicronaDocumento2 páginasTransimison Sincrona y AsicronaAxl GuamanAinda não há avaliações

- Ejercicios de Numeracion y Funciones LogicasDocumento10 páginasEjercicios de Numeracion y Funciones LogicasGemerson Ahumada SernaquéAinda não há avaliações

- Tipos de Datos Primitivos en JavaDocumento7 páginasTipos de Datos Primitivos en JavaTorres Mendoza JuanAinda não há avaliações

- Modulación PWM con ATmega8Documento42 páginasModulación PWM con ATmega8Jose Ruben TorresHortaAinda não há avaliações

- M. en C. Erika VilchesDocumento23 páginasM. en C. Erika VilchesFelixcito BomAinda não há avaliações