Escolar Documentos

Profissional Documentos

Cultura Documentos

Uart Abstract

Enviado por

inagantimanoj0 notas0% acharam este documento útil (0 voto)

91 visualizações2 páginasabstract for UART

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

DOCX, PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoabstract for UART

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato DOCX, PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

91 visualizações2 páginasUart Abstract

Enviado por

inagantimanojabstract for UART

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato DOCX, PDF, TXT ou leia online no Scribd

Você está na página 1de 2

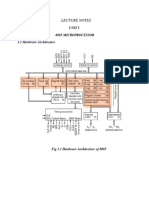

DESIGN AND IMPLEMENTATION OF UART

COMMUNICATION USING FPGA BOARD

A universal asynchronous receiver and transmitter (UART) is a circuit

that sends parallel data through a serial line. UARTs are frequently used in

conjunction with the EIA (Electronic Industries Alliance) RS-232 standard, which

specifies the electrical, mechanical, functional, and procedural characteristics of two

data communication equipment. This project focuses on the implementation of UART

using FPGA board and verilog language. UART is a serial communication protocol

which allows the full duplex communication in serial link, it is an essential to

computers and allows them to communicate with low speed peripheral devices, such

as the keyboard, the mouse, modems etc.

A field-programmable gate array (FPGA) is an integrated circuit designed

to be configured by a customer or a designer after manufacturing hence "field-

programmable". FPGAs contain an array of programmable logic blocks, and a

hierarchy of reconfigurable interconnects that allow the blocks to be "wired together",

like many logic gates that can be inter-wired in different configurations. Logic

blocks can be configured to perform complex combinational functions, or merely

simple logic gates like AND and XOR. In most FPGAs, logic blocks also include

memory elements, which may be simple flip-flops or more complete blocks of

memory.

A UART includes a transmitter and a receiver. The transmitter is

essentially a special shift register that loads data in parallel and then shifts it out bit by

bit at a specific rate. The receiver, on the other hand, shifts in data bit by bit and then

reassembles the data. The serial line is 1 when it is idle. The transmission starts with a

start bit, which is 0, followed by data bits and an optional parity bit, and ends with

stop bits, which are 1. The number of data bits can be 6, 7, or 8. The optional parity bit

is used for error detection. For odd parity, it is set to 0 when the data bits have an odd

number of 1s. For even parity, it is set to 0 when the data bits have an even number of

1s. The number of stop bits can be 1, 1.5 or 2.

UART is used mostly for the short distance, low speed and is of low cost.

The UART consists of three main components namely transmitter, receiver and baud

rate generator which is nothing but the frequency divider. The universal asynchronous

receiver/transmitter is shortened as UART. The designated "start" and "stop" bits

indicate the framing of each character.

Ch.Sumanth sai - 13071A04D4

I.N.S Manoj - 13071A04E4

D.Nithish - 13071A04G2

E.Shiva Prasad - 14075A0433

Basic UART Transmission Flow:

Circuit diagram for UART communication :

The hardware language used for designing is Verilog and software used

for simulation is modelsim.

Verilog Description : Verilog, is a hardware description language (HDL) used to

model electronic systems. It is most commonly used in the design and verification of

digital circuits at the register-transfer level of abstraction.

Modelsim : ModelSim is a multi-language HDL simulation environment by Mentor

Graphics, for simulation of hardware description languages such as VHDL, Verilog

and SystemC, and includes a built-in C debugger.

Você também pode gostar

- Project Report UartDocumento35 páginasProject Report UartSushant MongiaAinda não há avaliações

- Implementation of Uart and Ethernet Using FpgaDocumento15 páginasImplementation of Uart and Ethernet Using FpgaBANDARU SRI RAM SAI GANESH BANDARU SRI RAM SAI GANESHAinda não há avaliações

- Rfid Tag and ReaderDocumento8 páginasRfid Tag and ReaderKavin SengodanAinda não há avaliações

- UART ProtocolDocumento6 páginasUART Protocolvimal rajAinda não há avaliações

- UARTDocumento26 páginasUARTShantanu Tripathi100% (2)

- UartDocumento5 páginasUartGowdhaman Mohan100% (1)

- USART UART RS232 USB SPI I2C TTL Etc What Are All of These and How Do They Relate To Each OtherDocumento4 páginasUSART UART RS232 USB SPI I2C TTL Etc What Are All of These and How Do They Relate To Each OtherMohamed Ashraf100% (1)

- Management-Design and Implementation of UART-Mahesh GiriDocumento6 páginasManagement-Design and Implementation of UART-Mahesh GiriBESTJournalsAinda não há avaliações

- "Universal Asynchronous Receiver and Transmitter" (UART) : A Project Report OnDocumento24 páginas"Universal Asynchronous Receiver and Transmitter" (UART) : A Project Report Ondasari himajaAinda não há avaliações

- UartDocumento25 páginasUartWajeed Mohamad100% (2)

- Universal - Asynchronous - Receiver-Transmitter - ENDocumento12 páginasUniversal - Asynchronous - Receiver-Transmitter - ENArturo Yanez S.G.Ainda não há avaliações

- Serial Communication 2Documento31 páginasSerial Communication 2jaigodara100% (1)

- Task 6Documento13 páginasTask 6Vishnu SasidharanAinda não há avaliações

- Low Power Uart DeviceDocumento19 páginasLow Power Uart DeviceparnabmasterAinda não há avaliações

- Untitled PresentationDocumento22 páginasUntitled PresentationNITHYASREE K RAinda não há avaliações

- An Advanced Universal Asynchronous ReceiDocumento6 páginasAn Advanced Universal Asynchronous Receivpnhoang932002Ainda não há avaliações

- 2023EV167 Department of Ece: UART CommunicationDocumento7 páginas2023EV167 Department of Ece: UART CommunicationNITHYASREE K RAinda não há avaliações

- Computer Multitasking Real-Time ComputingDocumento3 páginasComputer Multitasking Real-Time ComputingAlazar DInberuAinda não há avaliações

- UART Communication: 2023EV167 Department of EceDocumento7 páginasUART Communication: 2023EV167 Department of EceNITHYASREE K RAinda não há avaliações

- 89 S 52Documento8 páginas89 S 52Ashok BalajiAinda não há avaliações

- Synchronizing Two FPGA's For A Reliable Communication: Mercy SubaramanDocumento4 páginasSynchronizing Two FPGA's For A Reliable Communication: Mercy SubaramanIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalAinda não há avaliações

- Es Notes Unit 5Documento33 páginasEs Notes Unit 51balamanianAinda não há avaliações

- 5.UART Serial Communication Module Design and SimulationDocumento4 páginas5.UART Serial Communication Module Design and Simulationvenkatahari babuAinda não há avaliações

- Microprocessor System: Session # 7Documento13 páginasMicroprocessor System: Session # 7Aamir BhuttoAinda não há avaliações

- Uart, Spi & I2cDocumento12 páginasUart, Spi & I2cdeepakacharya424Ainda não há avaliações

- How To Set Up UART Communication On The ArduinoDocumento22 páginasHow To Set Up UART Communication On The ArduinojackAinda não há avaliações

- Serial Communication Protocol:: Data Bit Communication Channel Computer Bus Parallel CommunicationDocumento24 páginasSerial Communication Protocol:: Data Bit Communication Channel Computer Bus Parallel CommunicationAshalatha MadasuAinda não há avaliações

- Universal Asynchronous Receiver and Transmitter (UART)Documento8 páginasUniversal Asynchronous Receiver and Transmitter (UART)Narendra gunnamAinda não há avaliações

- Synthesis and FPGA Implementation of UAR PDFDocumento3 páginasSynthesis and FPGA Implementation of UAR PDFquang nguyenAinda não há avaliações

- Communication InterfacesDocumento9 páginasCommunication InterfacesAzteca PicksAinda não há avaliações

- Unit Iv - The Microcontroller Connections 1.hardware Interface SequencingDocumento9 páginasUnit Iv - The Microcontroller Connections 1.hardware Interface SequencingAshwin Prabhu .M VISTASAinda não há avaliações

- XR16C854/854D: General DescriptionDocumento55 páginasXR16C854/854D: General DescriptionAnonymous QakmLc3kTIAinda não há avaliações

- Pic16f877a Phpapp02Documento35 páginasPic16f877a Phpapp02firdaus_n9Ainda não há avaliações

- Microprocessors and MicrocontrollersDocumento86 páginasMicroprocessors and MicrocontrollersbrightmoreAinda não há avaliações

- Uart DetailsDocumento12 páginasUart DetailsDlishaAinda não há avaliações

- UART/USART, SPI, I C Features and ApplicationsDocumento5 páginasUART/USART, SPI, I C Features and ApplicationsVishal Kottarathil100% (2)

- Design and Implementation of UartDocumento21 páginasDesign and Implementation of Uartbhanu455Ainda não há avaliações

- Design and Implementation of Uart On Soc PDFDocumento6 páginasDesign and Implementation of Uart On Soc PDFMaharaj MmayaAinda não há avaliações

- Design and Implementation of Uart Serial CommunicationDocumento19 páginasDesign and Implementation of Uart Serial CommunicationRam KrishnaAinda não há avaliações

- USART Vs UART Know The DifferenceDocumento2 páginasUSART Vs UART Know The DifferenceSandra Daniela RotaruAinda não há avaliações

- Serial Communication - Usart, Uart, Rs232, Usb, Spi, I2c, TTLDocumento1 páginaSerial Communication - Usart, Uart, Rs232, Usb, Spi, I2c, TTLvedhh100% (2)

- Chapter 3 Z80 Microprocessor ArchitectureDocumento30 páginasChapter 3 Z80 Microprocessor ArchitecturehowlerbrAinda não há avaliações

- AN2853Documento12 páginasAN2853rockymaxdeemann100% (1)

- UART in LPC2148 ARM7 MicrocontrollerDocumento8 páginasUART in LPC2148 ARM7 Microcontrollerrudra_1Ainda não há avaliações

- Z80 Microprocessor ArchitectureDocumento15 páginasZ80 Microprocessor ArchitectureVarsha DevAinda não há avaliações

- ARM MBED Board (LPC1768) - MBEDDocumento4 páginasARM MBED Board (LPC1768) - MBEDKrishanu Modak100% (1)

- Arm Ep9302 UartDocumento15 páginasArm Ep9302 UartBala ChandranAinda não há avaliações

- UART Vs I2C Vs SPIDocumento49 páginasUART Vs I2C Vs SPIKishore KishuAinda não há avaliações

- Design of A Micro-Uart For Soc ApplicationDocumento12 páginasDesign of A Micro-Uart For Soc ApplicationUtkarsh Jain100% (1)

- AttachmentDocumento7 páginasAttachmentnandini swamiAinda não há avaliações

- UAV Data Transmission and Communication ProtocolsDocumento92 páginasUAV Data Transmission and Communication ProtocolsReza NugrahaAinda não há avaliações

- Universal Asynchronous Receiver/Transmitter (UART) On The LM3S8962Documento12 páginasUniversal Asynchronous Receiver/Transmitter (UART) On The LM3S8962thanhvnptAinda não há avaliações

- RF Based Bus Stop Announcement SystemDocumento43 páginasRF Based Bus Stop Announcement SystemSaravanan Viswakarma100% (1)

- UART Using System VerilogDocumento4 páginasUART Using System VerilogJaiAinda não há avaliações

- Microcontroller Basics - PPSXDocumento44 páginasMicrocontroller Basics - PPSXholaAinda não há avaliações

- MPMC NotesDocumento301 páginasMPMC NotesVarinder KumarAinda não há avaliações

- RS232Documento26 páginasRS232Pratesh Kumar Reddy100% (3)

- Serial Communication ProtocolsDocumento32 páginasSerial Communication ProtocolsVissu Sweet100% (1)

- Unit 3 Notes PDFDocumento68 páginasUnit 3 Notes PDFPadmanaban MAinda não há avaliações

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Ainda não há avaliações

- PMT 928Documento2 páginasPMT 928inagantimanojAinda não há avaliações

- Output: Enter Carrier Frequency 50Documento6 páginasOutput: Enter Carrier Frequency 50inagantimanojAinda não há avaliações

- Automatic Gain Control (AGC) Is A Closed-LoopDocumento1 páginaAutomatic Gain Control (AGC) Is A Closed-LoopinagantimanojAinda não há avaliações

- Automatic: Gain ControlDocumento5 páginasAutomatic: Gain ControlinagantimanojAinda não há avaliações

- SensorsDocumento2 páginasSensorsinagantimanojAinda não há avaliações

- Aakriti 1Documento92 páginasAakriti 1raghav bansalAinda não há avaliações

- Pioneer vsx-1020-k 1025-k SM PDFDocumento132 páginasPioneer vsx-1020-k 1025-k SM PDFluisclaudio31Ainda não há avaliações

- General Chemistry 2 Q1 Lesson 5 Endothermic and Exotheric Reaction and Heating and Cooling CurveDocumento19 páginasGeneral Chemistry 2 Q1 Lesson 5 Endothermic and Exotheric Reaction and Heating and Cooling CurveJolo Allexice R. PinedaAinda não há avaliações

- 07 GDL Web-Site 04 (2021-2022) For 15284Documento2 páginas07 GDL Web-Site 04 (2021-2022) For 15284ABCDAinda não há avaliações

- CS-6777 Liu AbsDocumento103 páginasCS-6777 Liu AbsILLA PAVAN KUMAR (PA2013003013042)Ainda não há avaliações

- Numerical Modelling and Design of Electrical DevicesDocumento69 páginasNumerical Modelling and Design of Electrical Devicesfabrice mellantAinda não há avaliações

- Gaming Ports MikrotikDocumento6 páginasGaming Ports MikrotikRay OhmsAinda não há avaliações

- Chapter 4 - Basic ProbabilityDocumento37 páginasChapter 4 - Basic Probabilitynadya shafirahAinda não há avaliações

- The Mane Reason - UNDERSTANDING CONSUMER BEHAVIOUR TOWARDS NATURAL HAIR PRODUCTS IN GHANADocumento68 páginasThe Mane Reason - UNDERSTANDING CONSUMER BEHAVIOUR TOWARDS NATURAL HAIR PRODUCTS IN GHANAYehowadah OddoyeAinda não há avaliações

- UM-140-D00221-07 SeaTrac Developer Guide (Firmware v2.4)Documento154 páginasUM-140-D00221-07 SeaTrac Developer Guide (Firmware v2.4)Antony Jacob AshishAinda não há avaliações

- Financial Management 2E: Rajiv Srivastava - Dr. Anil Misra Solutions To Numerical ProblemsDocumento5 páginasFinancial Management 2E: Rajiv Srivastava - Dr. Anil Misra Solutions To Numerical ProblemsParesh ShahAinda não há avaliações

- I I Formularies Laundry Commercial Liquid Detergents 110-12-020 USDocumento6 páginasI I Formularies Laundry Commercial Liquid Detergents 110-12-020 USfaissalAinda não há avaliações

- A Hybrid Genetic-Neural Architecture For Stock Indexes ForecastingDocumento31 páginasA Hybrid Genetic-Neural Architecture For Stock Indexes ForecastingMaurizio IdiniAinda não há avaliações

- Bba VDocumento2 páginasBba VkunalbrabbitAinda não há avaliações

- Virtual Assets Act, 2022Documento18 páginasVirtual Assets Act, 2022Rapulu UdohAinda não há avaliações

- ThorpeDocumento267 páginasThorpezaeem73Ainda não há avaliações

- BJAS - Volume 5 - Issue Issue 1 Part (2) - Pages 275-281Documento7 páginasBJAS - Volume 5 - Issue Issue 1 Part (2) - Pages 275-281Vengky UtamiAinda não há avaliações

- Curriculum Guide Ay 2021-2022: Dr. Gloria Lacson Foundation Colleges, IncDocumento9 páginasCurriculum Guide Ay 2021-2022: Dr. Gloria Lacson Foundation Colleges, IncJean Marie Itang GarciaAinda não há avaliações

- Mathematics BQP 2022Documento43 páginasMathematics BQP 2022muhammadmansuri815Ainda não há avaliações

- Acc116 Dec 2022 - Q - Test 1Documento6 páginasAcc116 Dec 2022 - Q - Test 12022825274100% (1)

- Ritesh Agarwal: Presented By: Bhavik Patel (Iu1981810008) ABHISHEK SHARMA (IU1981810001) VISHAL RATHI (IU1981810064)Documento19 páginasRitesh Agarwal: Presented By: Bhavik Patel (Iu1981810008) ABHISHEK SHARMA (IU1981810001) VISHAL RATHI (IU1981810064)Abhi SharmaAinda não há avaliações

- BS 7974 2019Documento68 páginasBS 7974 2019bcyt00Ainda não há avaliações

- Introduction To Atomistic Simulation Through Density Functional TheoryDocumento21 páginasIntroduction To Atomistic Simulation Through Density Functional TheoryTarang AgrawalAinda não há avaliações

- Aditya Birla GroupDocumento21 páginasAditya Birla GroupNarendra ThummarAinda não há avaliações

- MSC-MEPC.2-Circ.17 - 2019 Guidelines For The Carriage of Blends OfBiofuels and Marpol Annex I Cargoes (Secretariat)Documento4 páginasMSC-MEPC.2-Circ.17 - 2019 Guidelines For The Carriage of Blends OfBiofuels and Marpol Annex I Cargoes (Secretariat)DeepakAinda não há avaliações

- Chemistry Investigatory Project (R)Documento23 páginasChemistry Investigatory Project (R)BhagyashreeAinda não há avaliações

- Transportasi Distribusi MigasDocumento25 páginasTransportasi Distribusi MigasDian Permatasari100% (1)

- Knee JointDocumento28 páginasKnee JointRaj Shekhar Singh100% (1)

- Research 093502Documento8 páginasResearch 093502Chrlszjhon Sales SuguitanAinda não há avaliações

- Haier in India Building Presence in A Mass Market Beyond ChinaDocumento14 páginasHaier in India Building Presence in A Mass Market Beyond ChinaGaurav Sharma100% (1)