Escolar Documentos

Profissional Documentos

Cultura Documentos

Veda Unit6&7

Enviado por

Leela KrishnaDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Veda Unit6&7

Enviado por

Leela KrishnaDireitos autorais:

Formatos disponíveis

SRI VEDA ECET INSTITUTIONS

FLIP-FLOPS AND COUNTERS

1. A combinational logic circuit

a) must contain flip-flop s b) may contain flip-flops

c) does not contain flip-flops d)contains latches

2. The output of a logic circuit depends upon the sequence in which the input is applied .the circuit

a) is a combinational logic circuit

b) is a sequential logic circuit

c) may be a combinational or sequential logic circuit

d) is none of the above

3. A sequential circuit does not use clock pulses. It is

a)an asynchronous sequential circuit b)a synchronous sequential circuit

c)a counter d)a shift register

4. The basic memory element in a digital circuit

a)consists of a NAND gate b)consists of NOR gate

c) is a flip-flop D)is a shift register

5. A flip-flop has two output which are

a) always 0 b)always 1

c)always complementary d)all of the above states

6. A flip-flop can be made using

a) basic gates such as AND,OR and NOT b)NAND gates

c) NOR gates d) any of the above

7. Which of the following flip-flop is used as a latch?

a) J-K flip-flop b) master-slave flip-flop

c) T flip-flop d) D flip-flop

8. Which of the following flip-flop is used as a latch?

a) J-K flip-flop b) master-slave flip-flop

c) S-R flip-flop d) T flip-flop

9. A flip-flop can store

a) one bit of data b)two bits of data

Prepared by S.L.V SRAVAN KUMAR M.Tech (ph.d) Page 1

SRI VEDA ECET INSTITUTIONS

c)three bits of data d)any number of bits of data

10. When an inverter is placed between the inputs of an S-R flip-flop, the resulting flip-flop is a

a) J-K flip-flop b) master-slave flip-flop

c) T flip-flop d) D flip-flop

11. Which of the following input combinations is not allowed in an S-R flip-flop?

a)S=0,R=0 b)S=0,R=1

c)S=1,R=0 d)S=1,R=1

12. The functional difference an S-R flip-flop and J-K flip-flop is that

a) J-K flip-flop is faster than S-R flip-flop b) J-K flip-flop has a feedback path

c)J-K flip-flop accepts both input 1 d)J-K flip-flop does not required external clock

13. When a flip-flop is set, its outputs will be

a) Q=0,=0 b)Q=1,=0 C)Q=0,=1 d)Q=1,=1

14. When a flip-flop is reset, its outputs will be

a)Q=0,=0 b)Q=1,=1 C)Q=0,=1 d)Q=1,=0

15. The race around condition occurs in a J-K flip-flop when

a. both inputs are 0 b)both inputs are 1

c) the inputs are complementary d)any one of the above input combinations is present

16. Master-slave configuration is used in flip-flops to

a. increase its clocking rate b. reduce power dissipation

c. eliminate race-around condition d. improve its reliability

17. Flip-flop can be used to make

a. latches b .bounce-elimination switches

c. registers d. all of the above

18. The toggle mode for a j-k flip-flop is

a. J=0, K=0 b. J=1, K=0 C.J=0, K=1 d. J=1, K=1

19. The transparent latch is

a. an S-R flip-flop b .a D flip-flop C. a T flip-flop d. a J-K flip-flops

20. The characteristic equation of a J-K flip-flop is

a.Qn+1= Jn+ K Qn b. JQn +kn c) J n+ Qn d. J n+k Qn

Prepared by S.L.V SRAVAN KUMAR M.Tech (ph.d) Page 2

SRI VEDA ECET INSTITUTIONS

21. The characteristic equation of a D flip-flop is

a.Qn+1=D b) Qn+1=Qn c) Qn+1=1 d) Qn+1= n

22. The characteristic equation of a T flip-flop is

a. n+1= nT+ Qn T b) Qn+1= n T + QnT c) Qn+1= Qn d) Qn+1= n

23.The characteristic equation of a S-R flip-flop is

a. Qn+1= Qn R +S b) Qn+1= nR+S C) Qn+1= Qn R+ S d) Qn+1= Qn

24. A shift register using flip-flop is called a

a. dynamic shift register b. flip-flop shift register

c. static shift register d. buffer shift register

25. A universal register

a. accepts serial input b. accepts parallel input

c. gives serial and parallel outputs d. is capable of all of the above

26. How many states a 6-bit ripple counter can have?

a.6 b.12 c.32 d.64

27. How many flip-flops are needed to divide the input frequency by 40?

a.4 b.5 c.6 d.40

28. The number of flip-flops required for decade counter is

a.3 b.4 c.5 d.10

29. The minimum number of flip-flops required for a mod -12 ripple counter is

a.3 b.4 c.6 d.12

30. The maximum number that can obtained by a ripple counter using five flip-flop is

a.32 b.5 c.16 d.31

31. The number of flip-flops required for a mod-16 ring counter is

a.4 b.8 c.15 d.16

32. The number of flip-flops required for a mod-12 Johnson counter is

a.4 b.6 c.12 d.24

33. In a counter circuit consisting of four J-K flip-flops, all the flip-flops get triggered simultaneously .this counter circuit

a. is a combinational circuit b. is an asynchronous circuit

c. is a synchronous circuit d. may be a combinational or a sequential circuit

Prepared by S.L.V SRAVAN KUMAR M.Tech (ph.d) Page 3

SRI VEDA ECET INSTITUTIONS

34. In a 4-bit binary ripple counter, for every input clock pulse

a. all the flip-flops get clocked simultaneously

b. only one flip-flops gets clocked at a time

c. only two flip-flops get clocked at a time

d. all the above statements are false

35. A 4 bit binary ripple counter uses flip-flops with propagation delay time of 25 ns each. The maximum possible time required

for change of state will be

a. 25ns b.50ns c.75ns d.100ns

36. A4 bit synchronous counter uses flip-flops with propagation delay time of 25 ns each. The maximum possible time required

for change of state will be

a. 25ns b.50ns c.75ns d.100ns

37. A mod-2 counter followed by a mod-5 counter is

a. the same as amod-5 counter followed by a mod-2 counter b. a decade counter

c. amod-7 counter d. none of the above

38. A 4-bit preset table up-counter has present input 0101.the presetting operation takes place as soon as the counter becomes

maximum, i.e .1111.the modulus of this counter is

a. 5 b.10 c.11 d.15

39. In general, a sequential logic circuit consists of

a. only flip-flop b. only gates

c. flip-flops and combinational logic circuits d. only combinational logic circuit

40. The output frequency of amod-16 counter, clocked from a 20 -kHz clock input signal is

a. 20 kHz b. 52 kHz c. 625 Hz d. 1250 Hz

41. The output frequency of amod-12 counter is 6 kHz .its input frequency is

a. 6kHz b. 500 kHz c. 24 kHz d. 72 kHz

42. A sequential circuit with ten states will have

a. 10 flip-flops b.5 flip-flops c.4 flip-flops d.0 flip-flops

43.

Prepared by S.L.V SRAVAN KUMAR M.Tech (ph.d) Page 4

SRI VEDA ECET INSTITUTIONS

A ripple counter using negative edge triggered flip flop as shown above. The flip-flops are cleared to 0 at R input.The feed

back logic Is to be degined to obtain the count sequence shown in the same figure.The correct feed back logic is

44. The figure shows a mod N counter where n is equal to

(a)1 (b)2 (c)3 (d)4

45. The given shows a ripple counter using positive edge triggered flip flops. If the present state of the counter Q 2Q1Q0= 011 .

Then its next state Q2Q1Q0 will be

(a)011 (b)100 (c)010 (d)110

46. Two flip-flops are to be connected as a synchronous as shown below that goes through the following Q 1Q0 sequence 00

01 11 10. The inputs D0&D1 respectively should be connected as

Prepared by S.L.V SRAVAN KUMAR M.Tech (ph.d) Page 5

SRI VEDA ECET INSTITUTIONS

47. For the circuit shown in figure the counter state Q1Q0 will follows the sequence

(a)00,01,10,11,00--- (b)00,01,10,00,01---- (c)00,01,11,00,01----- (d)00,10,11,00,10----

48. What are the counting stages (Q1,Q2)for the counter shown below? Assume k2=1

(a) 11, 10, 00, 11, 10. (b) 01, 10, 11, 00, 01.. (c) 00, 11, 01, 10, 00. (d) 01, 10, 00, 01, 10.

49. Assuming all the flip flops are in reset condition only, the count sequence observed at Q A in the circuit shown as shown figure

(a) 0010111 (b) 0001011 (c) 0101111 (d)0110100..

50. Two D Flip-flops are connected as a synchronous counter that goes through the following Q B QA sequence 00 11 01

10 00 .The connections of the inputs DA and DB are

Prepared by S.L.V SRAVAN KUMAR M.Tech (ph.d) Page 6

SRI VEDA ECET INSTITUTIONS

51. The output of the two flip-flops Q1,Q2 in the figure shown initialized to 00, The sequence generated at Q1 upon application

of clock signal is

(a) 01110 (b)01010. (c) 00110.. (d)01100.

52. The circuit shown in figure is

(a) Toggle flip-flop (b)JK Flip flop (c) SR LATCH (D)Master-slave D FLIP-FLOP

53. The mod-n counter using synchronous binary up counter with synchronous clear input is shown in figure. The value of n

is----------------------

Prepared by S.L.V SRAVAN KUMAR M.Tech (ph.d) Page 7

SRI VEDA ECET INSTITUTIONS

(a)2 (b)3 (c)4 (d)6

54. The figure shows a binary counter with synchronous clear input. With the decoding logic circuit the counter works as

(a) Mod-2 counter (b)mod-4 counter (c) mod-5 counter (d)mod-6 counter

55. The circuit shown consists of J-K Flip Flops, each with an active low synchronous reset input. The counter corresponding to

this circuit is

(a) Mod-5 counter (b) mod-6 counter (c) mod-7counter (d) mod-8 counter

56. A three bit pseudo random number generator is shown. Initially the value of output Y= Y 2 Y1 Y0. The value of output after

three clock pulses.

(a) 000 (b)010 (c)010 (d)100

Prepared by S.L.V SRAVAN KUMAR M.Tech (ph.d) Page 8

SRI VEDA ECET INSTITUTIONS

57. In the following sequential ckt the initial state of the circuit is Q0Q1=00. The state Q1Q0 immediately after 333 rd clock

pulse is

(a) 00 (b)01 (c)10 (d)11

58. The figure shown is a digital circuit constructed using negative edge triggered J-K Flip-Flops. Assuming a starting state of

Q2Q1Q0=000. This state Q2Q1Q0=000 will repeat after ------------------ number of clock pulses

(a) 1 (b)2 (c)4 (d) 6

59. Assume that all the digital gates in the circuit shown in the figure are ideal, the resistor and the supply voltage is 5V. The D

flip-flops D1, D2, D3, D4 and D5 are initialized with logicvalues 0,1,0,1 and 0, respectively. The clock has a 30% duty cycle R

10k.

(a) 1.1mw (b)1.5mw (c)5mw (d)10mw

60. For the circuit shown in the figure, the delay of the bubbled NAND gate is 2 ns and that of the counter is assumed to be zero.

If the clock (Clk) frequency is 1 GHz, then the counter behaves as a

Prepared by S.L.V SRAVAN KUMAR M.Tech (ph.d) Page 9

SRI VEDA ECET INSTITUTIONS

(A)Mod3 (b)mod4 (c) mod7 (d) mod8

61. The current state QA QB of a two JK flip-flop system is 00. Assume that the clock rise-time is much smaller than the delay of

the JK flip-flop. The next state of the system is

(a) 00 (b)01 (c)11 (d) 10

62. A 4-bit shift register circuit configured for right-shift operation in is shown. If the present state of the shift register is ABCD

= 1101, the number of clock cycles required to reach the state ABCD = 1111 is _________.

(a) 5 (b) 4 (c)8 (d)10

Prepared by S.L.V SRAVAN KUMAR M.Tech (ph.d) Page 10

SRI VEDA ECET INSTITUTIONS

Prepared by S.L.V SRAVAN KUMAR M.Tech (ph.d) Page 11

Você também pode gostar

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- History Paper 2 IB Study GuideDocumento6 páginasHistory Paper 2 IB Study Guidersuresh1995100% (4)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- BattleRope Ebook FinalDocumento38 páginasBattleRope Ebook FinalAnthony Dinicolantonio100% (1)

- B25217 Electrical Shock EngDocumento1 páginaB25217 Electrical Shock EngLeela KrishnaAinda não há avaliações

- A Study On Mistakes and Errors in Consecutive Interpretation From Vietnamese To English. Dang Huu Chinh. Qhf.1Documento38 páginasA Study On Mistakes and Errors in Consecutive Interpretation From Vietnamese To English. Dang Huu Chinh. Qhf.1Kavic100% (2)

- Accounting TheoryDocumento192 páginasAccounting TheoryABDULLAH MOHAMMEDAinda não há avaliações

- AICTE Training and Learning (ATAL) Academy: Data-Driven Strategies in Smart Power System and Control - 2021Documento2 páginasAICTE Training and Learning (ATAL) Academy: Data-Driven Strategies in Smart Power System and Control - 2021Leela KrishnaAinda não há avaliações

- Abstract of Salar Power Satellite (Bhagya)Documento1 páginaAbstract of Salar Power Satellite (Bhagya)Leela KrishnaAinda não há avaliações

- R16B TECHEEESyllabusDocumento382 páginasR16B TECHEEESyllabusLeela KrishnaAinda não há avaliações

- BEE CO PO Mapping 2018 ExternalQPDocumento1 páginaBEE CO PO Mapping 2018 ExternalQPLeela KrishnaAinda não há avaliações

- Sequence Impedances of Alternator Aim: Apparatus RequiredDocumento10 páginasSequence Impedances of Alternator Aim: Apparatus RequiredLeela KrishnaAinda não há avaliações

- Professor in The Department of Electrical and Electronics Engineering Completed Five Years ofDocumento1 páginaProfessor in The Department of Electrical and Electronics Engineering Completed Five Years ofLeela KrishnaAinda não há avaliações

- G.Narayanamma Institute of Technology & Science: (Autonomous) (For Women) Course PlanDocumento3 páginasG.Narayanamma Institute of Technology & Science: (Autonomous) (For Women) Course PlanLeela KrishnaAinda não há avaliações

- Topic Beyond SyllabusDocumento1 páginaTopic Beyond SyllabusLeela KrishnaAinda não há avaliações

- mid /EEE - (,A.Y. - 2016-17)Documento26 páginasmid /EEE - (,A.Y. - 2016-17)Leela KrishnaAinda não há avaliações

- Blue LightDocumento1 páginaBlue LightLeela KrishnaAinda não há avaliações

- 3 Eee A PE AttainmntsDocumento9 páginas3 Eee A PE AttainmntsLeela KrishnaAinda não há avaliações

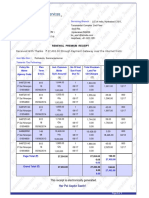

- Renewal Premium Receipt: Collecting Branch: E-Mail: Phone: Transaction No.: Date (Time) : Servicing BranchDocumento1 páginaRenewal Premium Receipt: Collecting Branch: E-Mail: Phone: Transaction No.: Date (Time) : Servicing BranchLeela KrishnaAinda não há avaliações

- Received With Thanks ' 18,426.00 Through Payment Gateway Over The Internet FromDocumento1 páginaReceived With Thanks ' 18,426.00 Through Payment Gateway Over The Internet FromLeela KrishnaAinda não há avaliações

- ElektraDocumento2 páginasElektraLeela KrishnaAinda não há avaliações

- Received With Thanks ' 27,402.00 Through Payment Gateway Over The Internet FromDocumento2 páginasReceived With Thanks ' 27,402.00 Through Payment Gateway Over The Internet FromLeela KrishnaAinda não há avaliações

- IGNIUM 2K18 Registration Form Elektra: Parallel EventDocumento1 páginaIGNIUM 2K18 Registration Form Elektra: Parallel EventLeela KrishnaAinda não há avaliações

- Received With Thanks ' 8,976.00 Through Payment Gateway Over The Internet FromDocumento2 páginasReceived With Thanks ' 8,976.00 Through Payment Gateway Over The Internet FromLeela KrishnaAinda não há avaliações

- Bike Insurance Policy Till 2018Documento5 páginasBike Insurance Policy Till 2018Leela KrishnaAinda não há avaliações

- Resistor ValuesDocumento8 páginasResistor ValuesLeela KrishnaAinda não há avaliações

- Decision Making and Problem Solving & Managing - Gashaw PDFDocumento69 páginasDecision Making and Problem Solving & Managing - Gashaw PDFKokebu MekonnenAinda não há avaliações

- Asher - Bacteria, Inc.Documento48 páginasAsher - Bacteria, Inc.Iyemhetep100% (1)

- A Neural Network Based System For Intrusion Detection and Classification of AttacksDocumento6 páginasA Neural Network Based System For Intrusion Detection and Classification of AttacksbharadwajrohanAinda não há avaliações

- G12 PR1 AsDocumento34 páginasG12 PR1 Asjaina rose yambao-panerAinda não há avaliações

- Eco - Module 1 - Unit 3Documento8 páginasEco - Module 1 - Unit 3Kartik PuranikAinda não há avaliações

- Dcat2014 - Simulated Set B - Section 3 - Reading Comprehension - Final v.4.7.2014Documento6 páginasDcat2014 - Simulated Set B - Section 3 - Reading Comprehension - Final v.4.7.2014Joice BobosAinda não há avaliações

- You Are Loved PDFDocumento4 páginasYou Are Loved PDFAbrielle Angeli DeticioAinda não há avaliações

- Ramin Shamshiri Risk Analysis Exam2 PDFDocumento8 páginasRamin Shamshiri Risk Analysis Exam2 PDFRedmond R. ShamshiriAinda não há avaliações

- Sections 3 7Documento20 páginasSections 3 7ninalgamaryroseAinda não há avaliações

- Question No. 2: (Type Here)Documento5 páginasQuestion No. 2: (Type Here)temestruc71Ainda não há avaliações

- B2 First Unit 11 Test: Section 1: Vocabulary Section 2: GrammarDocumento1 páginaB2 First Unit 11 Test: Section 1: Vocabulary Section 2: GrammarNatalia KhaletskaAinda não há avaliações

- Contents:: Project ProgressDocumento22 páginasContents:: Project ProgressJosé VicenteAinda não há avaliações

- FR-A800 Plus For Roll To RollDocumento40 páginasFR-A800 Plus For Roll To RollCORTOCIRCUITANTEAinda não há avaliações

- Chapter (1) The Accounting EquationDocumento46 páginasChapter (1) The Accounting Equationtunlinoo.067433100% (3)

- Compare and Contrast Two Cultures Celebrate Between Bali and JavaDocumento1 páginaCompare and Contrast Two Cultures Celebrate Between Bali and JavaqonitazmiAinda não há avaliações

- Case Digest: Pedro Elcano and Patricia Elcano Vs - Reginald Hill and Marvin HillDocumento5 páginasCase Digest: Pedro Elcano and Patricia Elcano Vs - Reginald Hill and Marvin Hillshirlyn cuyongAinda não há avaliações

- Resume UngerDocumento2 páginasResume UngerMichelle ClarkAinda não há avaliações

- Iml601 Week 4 AbsDocumento69 páginasIml601 Week 4 AbsNur Nazurah NordinAinda não há avaliações

- RARC Letter To Tan Seri Razali Ismail July 26-2013Documento4 páginasRARC Letter To Tan Seri Razali Ismail July 26-2013Rohingya VisionAinda não há avaliações

- 208 C - Algebras: Marc Rieffel Notes by Qiaochu Yuan Spring 2013Documento55 páginas208 C - Algebras: Marc Rieffel Notes by Qiaochu Yuan Spring 2013Nikos AthanasiouAinda não há avaliações

- Exercise On Relative ClausesDocumento5 páginasExercise On Relative ClausesSAmuel QuinteroAinda não há avaliações

- Fsi GreekBasicCourse Volume1 StudentTextDocumento344 páginasFsi GreekBasicCourse Volume1 StudentTextbudapest1Ainda não há avaliações

- Bragg Waveguide and Its DescriptionDocumento22 páginasBragg Waveguide and Its DescriptionPratibha Karki RawatAinda não há avaliações

- Week 4 CasesDocumento38 páginasWeek 4 CasesJANNAinda não há avaliações

- Classics and The Atlantic Triangle - Caribbean Readings of Greece and Rome Via AfricaDocumento12 páginasClassics and The Atlantic Triangle - Caribbean Readings of Greece and Rome Via AfricaAleja KballeroAinda não há avaliações

- People V Galano, Caubang v. PeopleDocumento2 páginasPeople V Galano, Caubang v. PeopleHermay Banario50% (2)