Escolar Documentos

Profissional Documentos

Cultura Documentos

Actividad 20112017

Enviado por

Marco Lema0 notas0% acharam este documento útil (0 voto)

24 visualizações2 páginasTítulo original

ACTIVIDAD 20112017.docx

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

DOCX, PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato DOCX, PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

24 visualizações2 páginasActividad 20112017

Enviado por

Marco LemaDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato DOCX, PDF, TXT ou leia online no Scribd

Você está na página 1de 2

ESCUELA SUPERIOR POLITCNICA DE CHIMBORAZO

FACULTAD DE INFORMTICA Y ELECTRNICA

ESCUELA DE INGENIERA ELECTRNICA EN TELECOMUNICACIONES Y REDES

VHDL

PRIMER PARCIAL DE VHDL

NOMBRE: Marco Lema

CDIGO: 509 FECHA: 20/11/2017

PROGRAMACIN DE UN CODIFICADOR DE PRIORIDAD EN EL MDULO DE2

Cdigo del Programa

library ieee;

use ieee.std_logic_1164.all;

entity De2 is

port

(

E : in bit_vector(3 downto 0);

AB: out bit_vector(1 downto 0)

);

end De2;

architecture Arq of De2 is

begin

with E select

AB <= "11" when "1000"|"1001"|"1010"|"1011"|

"1100"|"1101"|"1110"|"1111",

"10" when "0100"|"0101"|"0110"|"0111",

"01" when "0010"|"0011",

"00" when others;

end Arq;

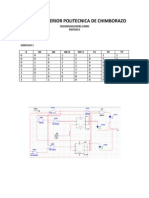

DIAGRAMA RTL

Você também pode gostar

- Autores de EcologiaDocumento4 páginasAutores de EcologiaMarco LemaAinda não há avaliações

- Regresion ResueltosDocumento4 páginasRegresion ResueltosJuan Jose MartinezAinda não há avaliações

- Cuadro ComparativoDocumento1 páginaCuadro ComparativoMarco Lema100% (1)

- Curso básico de japonés: gramática, números, calendarioDocumento46 páginasCurso básico de japonés: gramática, números, calendariogbalvesAinda não há avaliações

- Marco Lema 509 Quinto A Resumen AntenasDocumento10 páginasMarco Lema 509 Quinto A Resumen AntenasMarco LemaAinda não há avaliações

- Curso básico de japonés: gramática, números, calendarioDocumento46 páginasCurso básico de japonés: gramática, números, calendariogbalvesAinda não há avaliações

- Actividad VHDLDocumento18 páginasActividad VHDLMarco LemaAinda não há avaliações

- Redundancia en RouterDocumento13 páginasRedundancia en RouterMarco LemaAinda não há avaliações

- AmplificadorDocumento5 páginasAmplificadorMarco LemaAinda não há avaliações

- Generador de CarcajadasDocumento7 páginasGenerador de CarcajadasMarco LemaAinda não há avaliações

- Digitales MooreDocumento4 páginasDigitales MooreMarco LemaAinda não há avaliações

- Patrón de Propagación AntenasDocumento4 páginasPatrón de Propagación AntenasMarco LemaAinda não há avaliações

- DBMSDocumento1 páginaDBMSMarco LemaAinda não há avaliações

- Funciones Trigonometricas InversasDocumento10 páginasFunciones Trigonometricas InversasMarco LemaAinda não há avaliações

- Laboratorio de Digitales Grupo 14Documento2 páginasLaboratorio de Digitales Grupo 14Marco LemaAinda não há avaliações

- Ventajas y Desventajas de La CibercomunicaciónDocumento2 páginasVentajas y Desventajas de La CibercomunicaciónMarco LemaAinda não há avaliações

- KOF 2002 trucos combosDocumento1 páginaKOF 2002 trucos combosMarco Lema33% (6)

- Efectos en Las Salud Del Los NoxDocumento2 páginasEfectos en Las Salud Del Los NoxMarco LemaAinda não há avaliações

- Gráficas MarcoDocumento5 páginasGráficas MarcoMarco LemaAinda não há avaliações