Escolar Documentos

Profissional Documentos

Cultura Documentos

Koki

Enviado por

CristianCamiloHernandezSuarezTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Koki

Enviado por

CristianCamiloHernandezSuarezDireitos autorais:

Formatos disponíveis

CALCULADORA

MÓNICA GISSELLE HERNÁNDEZ VARGAS

1090503100

UNIVERSIDAD DE PAMPLONA

FACULTA DE INGENIERÍAS Y ARQUITECTURA

VILLA DEL ROSARIO

2017

PARQUEADERO

Una universidad incluyente y comprometida con el desarrollo integral 1

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

MÓNICA GISSELLE HERNÁNDEZ VARGAS

1090503100

CIRCUITOS DE TRANSMISION

Grupo AR

SERGIO STIVENSON PINTO SERRANO

UNIVERSIDAD DE PAMPLONA

FACULTA DE INGENIERÍAS Y ARQUITECTURA

VILLA DEL ROSARIO

2017

Una universidad incluyente y comprometida con el desarrollo integral 2

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

TABLA DE CONTENIDO

1. Introducción

2. Objetivos

2.1. Objetivo general

2.2. Objetivos específicos

3. Marco teórico

4. Materiales

5. Etapas del circuito

5.1 Diagrama de bloques

5.2 Circuito esquemático

6. Conclusiones

Una universidad incluyente y comprometida con el desarrollo integral 3

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

1. INTRODUCCIÓN

En el presente informe se realizará el diseño y la presentación de una calculadora

de señales la cual mediante configuraciones de dispositivos electrónicos como son

los amplificadores operacionales permitirá realizar operaciones entre ellas, las

fundamentales como son la suma, resta, división y multiplicación de las mismas.

Teniendo en las ventajas que dan las configuraciones de sumador de un

amplificador operacionales gracias a las entradas inversoras y no inversoras del

mismo, se podrán realizar estas operaciones, apartes de la configuración para

multiplicar y dividir la cual se logran mediante el uso de la configuración de los

amplificadores operaciones como logarítmicas y anti logarítmicas, se basa en las

propiedades que posean los logaritmos naturales para conseguir en las salidas, la

división o multiplicación de las señales correspondientes.

Una universidad incluyente y comprometida con el desarrollo integral 4

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

2. OBJETIVOS

2.1 Objetivo general

Diseñar y ejecutar un circuito el cual me permita realizar la suma, resta, división, y

multiplicación de dos señales de entrada para obtener a la salida una sola la cual

dependerá de la opción escogida.

2.2 Objetivos específicos

Configurar los elementos y amplificadores operacionales para lograr a la

salida la suma y resta de las señales teniendo como principio la

configuración de amplificador operacional sumador no inversor.

Configurar los elementos y amplificadores operacionales para lograr a la

salida la multiplicación y división de las señales teniendo como principio la

configuración de amplificador operacional logarítmico y anti logarítmico.

Visualizar el comportamiento o señal resultado luego de haber escogido la

correspondiente operación a realizar con las señales.

Una universidad incluyente y comprometida con el desarrollo integral 5

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

3. MARCO TEÓRICO

Un circuito integrado (CI) es un cristal semiconductor de silicio, llamado pastilla,

que contiene componentes eléctricos tales como transistores, diodos, resistencias

y capacitores, los diversos componentes están interconectados dentro de la

pastilla para forma un circuito electrónico. La pastilla está montada en un empaque

plástico (cerámico) con sus conexiones soldadas a las patillas externas para

conformar el circuito integrado.

Una puerta lógica, o compuerta lógica, es un dispositivo electrónico el cual es la

expresión física de un operador booleano en la lógica de conmutación. Cada

puerta lógica consiste en una red de dispositivos interruptores que cumple las

condiciones booleanas para el operador particular. Son esencialmente circuitos de

conmutación integrados en un chip.

Puerta AND

Puerta AND con transistores

Símbolo de la función lógica Y:

Una universidad incluyente y comprometida con el desarrollo integral 6

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

a)

Contactos, b) Normalizado y c) No normalizado

La puerta lógica Y, más conocida por su nombre en inglés AND (

), realiza la función booleana de producto lógico. Su símbolo es

un punto (·), aunque se suele omitir. Así, el producto lógico de las variables A y B

se indica como AB, y se lee A y B o simplemente A por B.

La ecuación característica que describe el comportamiento de la puerta AND es:

Su tabla de verdad es la siguiente:

Tabla de verdad puerta AND

Entrada Entrada Salida

0 0 0

0 1 0

1 0 0

1 1 1

CONTADORES: Son circuitos integrados donde vienen incluidos los flip-flops

conectados según el tipo de contador y las puertas. Estos contadores se pueden

llamar de propósito general.

Una universidad incluyente y comprometida con el desarrollo integral 7

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

4. MATERIALES

En el proyecto de parqueadero controlado por compuertas circuitos integrados se

usaron los siguientes componentes.

PROTOBOARD: es un tablero con orificios que se encuentran conectados

eléctricamente entre sí de manera interna, habitualmente siguiendo

patrones de líneas, en el cual se pueden insertar componentes electrónicos

y cables para el armado circuitos electrónicos.

Una universidad incluyente y comprometida con el desarrollo integral 8

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

RESISTENCIAS: Oposición al flujo de electrones al moverse a través de un

conductor. La unidad de resistencia en el Sistema Internacional es el ohmio,

que se representa con la letra griega omega (Ω).

COMPUERTA AND (74LS08) Y (74LS11): es una puerta lógica digital que

implementa la conjunción lógica. Ésta entregará una salida ALTA (1),

dependiendo de los valores de las entradas.

Una universidad incluyente y comprometida con el desarrollo integral 9

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

FUENTE DE VOLTAJE REGULABLE es un dispositivo que convierte el

voltaje Vrms de alterna en una señal de voltaje directo, mediante un

proceso de transformación, rectificación, filtración y regulación.

EL DISPLAY 7 SEGMENTOS es un componente electrónico muy utilizado

para representar visualmente números y letras, es de gran utilidad dado su

simpleza para implementar en cualquier proyecto electrónico.

Una universidad incluyente y comprometida con el desarrollo integral 10

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

Está compuesto por 7 dispositivos lumínicos (Diodo Led) que forman un “8”,

de esta forma controlando el encendido y apagado de cada led, podremos

representar el numero o letra que necesitamos.

CONTADOR 74LS191: Este contador binario puede hacer el conteo de manera

ascendente o descendente. Además podemos precargar un valor para que

empiece a contar. El conteo es síncrono y la carga asíncrona. Puede llegar a

funcionar hasta un máximo de 35 MHZ.

CLK Entrada de reloj.

DOWN/UP Entrada de contaje descendente o ascendente.

LOAD Entrada de carga paralela asíncrona.

P0 – P3 Entrada de datos paralela.

Q0 – Q3 Salida de los flip-flops.

CE Selección de chip.

MAX Salida máximo / mínimo.

RCO Salida ripple clock.

Una universidad incluyente y comprometida con el desarrollo integral 11

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

COMPUERTA OR (74LS32):

La puerta OR o compuerta OR es una puerta lógica digital que implementa la

disyunción lógica -se comporta de acuerdo a la tabla de verdad mostrada a la

derecha. Cuando todas sus entradas están en 0 (cero) o en BAJA, su salida está

en 0 o en BAJA.

SUMADOR (74LS83): Circuito Integrado. TTL 74LS83. Sumador binario de 4-Bit

donde las sumas (Σ) se proporcionan para cada bit y el acarreo resultante (C4) se

obtiene a partir del cuarto bit. Estos agregadores cuentan con una mirada interna

completa a través de los cuatro Bits Cuenta con una implementación de ripple-

carry. La lógica del sumador, incluido el carry, se implementa en su forma

verdadera, lo que significa que el logrado sin necesidad de inversión lógica o de

nivel.

Una universidad incluyente y comprometida con el desarrollo integral 12

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

DECODIFICADOR (74LS47): es un circuito integrado que convierte el código

binario de entrada en formato BCD a niveles lógicos que permiten activar un

display de 7 segmentos de ánodo común en donde la posición de cada barra

forma el número decodificado.

Una universidad incluyente y comprometida con el desarrollo integral 13

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

5. ETAPAS DEL CIRCUITO

5.1 Diagrama por bloques

Una universidad incluyente y comprometida con el desarrollo integral 14

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

ENTRADA DE DATOS CONTADOR LÓGICA

SUMADOR DECODIFICACIÓN

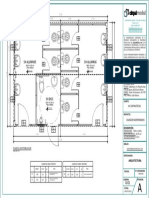

5.2 Circuito esquemático simulado

En el circuito se evidencian 5 etapas, las cuales son:

Una universidad incluyente y comprometida con el desarrollo integral 15

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

1) Etapa de entrada de datos: En esta etapa se puede ver como la fotocelda será la

que activará el pulso del reloj (que será la salida del 555) el cual al estar en

ausencia de luz en el pin 4(RESET) habrá un “1” y empezará la etapa de conteo,

caso contrario si hay luz mandar un “0”.

2) Etapa de contador: El recibir la señal del 555 dependiendo del estado de la

fotocelda contará ascendente o descendente, esto dependerá de si el pin D/U esta

en bajo (Ascendente) o en alto(Descendente).

3) Etapa lógica: En esta etapa se realiza una comparación que al mandar un 1 se

complete el número 1 en el primer siete segmentos y un 6 en el sumador.

4) Etapa de sumador: En esta etapa se suma el número del contador con el 6 que

forma la respuesta de la etapa anterior, esto para poder completar el número 6 en

los decodificadores.

5) Etapa de decodificación: los números se dirigen a los siete segmentos para

poder visualizarse del 1 al 15, cuando se encuentre en el número 15 este

encenderá un led para indicar que el parqueadero esta lleno.

6. CONCLUSIONES

La entrada de reloj del contador, están dadas por las fotoceldas, a su vez están

determina que cuente de manera ascendente o descendente.

Una universidad incluyente y comprometida con el desarrollo integral 16

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

Como solo se puede visualizar 9 dígitos en el siete segmentos, se debió separar

los números en 2 siete segmentos utilizando un sumador.

La etapa lógica funciona para cuando llegue un 9 ya que el siguiente número es el

10 que tiene dos dígitos y debe empezar a separarse con los siete segmentos.

El led verde indica que el parqueadero está a su máxima capacidad.

Si se usara la compuerta 74LS193 que es un contador el cual posee las mismas

características que el usado (74LS191), su diferencia radica en que la 74LS193

posee dos CLK independientes para un conteo ascendente y otro descendente,

mientras que la 74LS191 solo posee un reloj y depende del estado del pin D/U

para contar de forma creciente o decreciente. Esto influye en que no se tendría

que usar un switch para cambiar de estado sino simplemente mandar una señal de

reloj para cada tipo de conteo las cuales serán diferentes pues dependerá si se

ingresa o sale un auto del parqueadero.

7. BIBLIOGRAFIA

Fundamentos de Sistemas Digitales. 7ma Edición. Thomas L. Floyd.

Sistemas Digitales. 8va Edición. Ronald. J. Tocci.

Una universidad incluyente y comprometida con el desarrollo integral 17

Universidad de Pamplona - Pamplona - Norte de Santander - Colombia

Tels: (7) 5685303 - 5685304 - 5685305 - Fax: 5682750 - www.unipamplona.edu.co

Você também pode gostar

- Lineas Capitulo 5 PDFDocumento12 páginasLineas Capitulo 5 PDFCristianCamiloHernandezSuarezAinda não há avaliações

- Trafos PensadosDocumento1 páginaTrafos PensadosCristianCamiloHernandezSuarezAinda não há avaliações

- PARQUEADERODocumento16 páginasPARQUEADEROCristianCamiloHernandezSuarez100% (1)

- Propuesta Cambio Plan de Estudios v2.0Documento12 páginasPropuesta Cambio Plan de Estudios v2.0CristianCamiloHernandezSuarezAinda não há avaliações

- Hislqmcbe El IfDocumento1 páginaHislqmcbe El IfCristianCamiloHernandezSuarezAinda não há avaliações

- Trabajo Line As 2017Documento27 páginasTrabajo Line As 2017CristianCamiloHernandezSuarezAinda não há avaliações

- C/nivel-1 Cantidad 10 1 63 7 64 8 70 10 216 36 3 3 Total 426 65Documento2 páginasC/nivel-1 Cantidad 10 1 63 7 64 8 70 10 216 36 3 3 Total 426 65CristianCamiloHernandezSuarezAinda não há avaliações

- Formulacion Y Evaluacion de Proyectos de Inversion (5 Ed)Documento1 páginaFormulacion Y Evaluacion de Proyectos de Inversion (5 Ed)CristianCamiloHernandezSuarezAinda não há avaliações

- Hislqmcbe El IfDocumento1 páginaHislqmcbe El IfCristianCamiloHernandezSuarezAinda não há avaliações

- Menu PDFDocumento2 páginasMenu PDFCristianCamiloHernandezSuarezAinda não há avaliações

- 200W Amplificador1Documento4 páginas200W Amplificador1CristianCamiloHernandezSuarezAinda não há avaliações

- 1Documento4 páginas1CristianCamiloHernandezSuarezAinda não há avaliações

- IntroducciónDocumento4 páginasIntroducciónCristianCamiloHernandezSuarezAinda não há avaliações

- Lasbobinasjaimez 121019153914 Phpapp02Documento3 páginasLasbobinasjaimez 121019153914 Phpapp02CristianCamiloHernandezSuarezAinda não há avaliações

- Grfaficas 2 eDocumento4 páginasGrfaficas 2 eCristianCamiloHernandezSuarezAinda não há avaliações

- Grfaficas 2 eDocumento4 páginasGrfaficas 2 eCristianCamiloHernandezSuarezAinda não há avaliações

- Construccion Instalacion Pilotes AnexosDocumento22 páginasConstruccion Instalacion Pilotes AnexosARLSAinda não há avaliações

- Manual Calentador ChallengerDocumento10 páginasManual Calentador ChallengerJose Velez75% (4)

- Calculo de ChimeneasDocumento57 páginasCalculo de ChimeneasDavidMañanes100% (1)

- Diseño Del Soporte de Una Obra SubterraneaDocumento62 páginasDiseño Del Soporte de Una Obra SubterraneaJose PepeAinda não há avaliações

- Espe - Tecnicas EstructurasDocumento8 páginasEspe - Tecnicas EstructurasMiguel NinaAinda não há avaliações

- Hidraloy 300Documento3 páginasHidraloy 300Jessica Arratea MoránAinda não há avaliações

- G - SSHH 01 - PlantaDocumento1 páginaG - SSHH 01 - PlantaRaúl Manuel Espinoza RetamozoAinda não há avaliações

- Boca Mina A Puerto MataraniDocumento15 páginasBoca Mina A Puerto MataraniMax Bryan Rodriguez GarciaAinda não há avaliações

- Elección de Un DisyuntorDocumento6 páginasElección de Un DisyuntorMarco Esteban Godoy MoyaAinda não há avaliações

- Clase de FrasadoDocumento34 páginasClase de FrasadoJeann JeanAinda não há avaliações

- Catalizador Universal Max-SeguridadDocumento14 páginasCatalizador Universal Max-SeguridadAndres SantanaAinda não há avaliações

- Trabajo Final - Sensores de InvernaderoDocumento34 páginasTrabajo Final - Sensores de InvernaderoENIC-AITCGAinda não há avaliações

- NTC 4114 - Lesdan Maletas-DesarrolloDocumento21 páginasNTC 4114 - Lesdan Maletas-DesarrolloEMELY JULIETH BECERRA BECERRAAinda não há avaliações

- Circuitos en Serie y Paralelo PDFDocumento13 páginasCircuitos en Serie y Paralelo PDFleafarsur100% (1)

- D.E VW Fox BHLDocumento24 páginasD.E VW Fox BHLboris abrahamAinda não há avaliações

- El ProyectorDocumento4 páginasEl ProyectorFelix HuarachiAinda não há avaliações

- Cinemática II OkDocumento3 páginasCinemática II Okwilfredo Nelson Berrios MarceloAinda não há avaliações

- Tipos y Ejemplos de Sistemas de Información en Una EmpresaDocumento2 páginasTipos y Ejemplos de Sistemas de Información en Una EmpresajanojimenezAinda não há avaliações

- Materia OrganicaDocumento7 páginasMateria OrganicaLizbeth MonteroAinda não há avaliações

- Viga en Z-Estudio 1-2Documento9 páginasViga en Z-Estudio 1-2WarlexAinda não há avaliações

- CF Ahumada MCDocumento176 páginasCF Ahumada MCckinastAinda não há avaliações

- Estandares y ProtocolosDocumento22 páginasEstandares y ProtocolosLaura FabiolaAinda não há avaliações

- DPR-1020 A1 Manual v1.00 (ES)Documento196 páginasDPR-1020 A1 Manual v1.00 (ES)Alfonso Estuardo BejaranoAinda não há avaliações

- Turbo ElectronicoDocumento13 páginasTurbo Electronicorobyn100Ainda não há avaliações

- Medición de Temperatura - Trabajo PracticoDocumento11 páginasMedición de Temperatura - Trabajo PracticoPamela Rojas Díaz de VivarAinda não há avaliações

- Termofisica y TermoquimicaDocumento7 páginasTermofisica y TermoquimicaRuben Manuel Moyer ManzurAinda não há avaliações

- AMEFDocumento8 páginasAMEFtributo415Ainda não há avaliações

- Armado y Desarme de AndamiosDocumento9 páginasArmado y Desarme de AndamiosJavier Antonio Villarroel GajardoAinda não há avaliações

- 3 0Documento139 páginas3 0robsandanAinda não há avaliações

- Consulta Polvos CeramicosDocumento8 páginasConsulta Polvos CeramicosCamila PáezAinda não há avaliações