Escolar Documentos

Profissional Documentos

Cultura Documentos

AES FMC DVI G 01 SCH - 041310 - Pinlloc PDF

Enviado por

Mauricio Reyna CameroTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

AES FMC DVI G 01 SCH - 041310 - Pinlloc PDF

Enviado por

Mauricio Reyna CameroDireitos autorais:

Formatos disponíveis

5 4 3 2 1

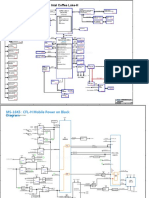

AES-FMC-DVI-G

D

01.Cover D

02.FMC-A,B,C,D,E

03.FMC-F,G,H,J,K

04.IPMI,I2C & Clock

05.DVI Input

06.DVI Output

07.DP & GPIO

C C

DP Out GPIO Header

DVI In

FMC-HPC Connector

B B

DVI Out

A A

Avnet Design Services

Title

Cover

Size Document Number Rev

B AES-FMC-DVI-G <RevCode>

Date: Monday, August 31, 2009 Sheet 1 of 7

5 4 3 2 1

5 4 3 2 1

D D

3,5 DVII_D[0..23]

J1E J1D J1C J1B J1A

Jack/FMC-HPC Jack/FMC-HPC Jack/FMC-HPC Jack/FMC-HPC Jack/FMC-HPC

E1 D1 C1 B1 A1

GND 4 PG_C2M PG_C2M GND RES1 GND

E2 D2 C2 B2 A2

HA01_P_CC GND 7 DP_ML0+ DP0_C2M_P GND DP1_M2C_P

E3 D3 C3 B3 A3

HA01_N_CC GND 7 DP_ML0- DP0_C2M_N GND DP1_M2C_N

E4 4 GTB_CLK0+ D4 C4 B4 A4

GND GBTCLK0_M2C_P GND DP9_M2C_P GND

E5 4 GTB_CLK0- D5 C5 B5 A5

GND GBTCLK0_M2C_N GND DP9_M2C_N GND

E6 D6 C6 B6 A6

HA05_P GND DP0_M2C_P GND DP2_M2C_P

E7 D7 C7 B7 A7

HA05_N GND DP0_M2C_N GND DP2_M2C_N

E8 D8 C8 B8 A8

GND 7 DP1_AUX+ LA01_P_CC GND DP8_M2C_P GND

E9 D9 C9 B9 A9

HA09_P 7 DP1_AUX- TP1 Pad LA01_N_CC GND DP8_M2C_N GND

E10 D10 7 DP1_AUX+ C10 B10 A10

HA09_N GND LA06_P GND DP3_M2C_P

E11 D11 C11 B11 A11

GND LA05_P 7 DP1_AUX- LA06_N GND DP3_M2C_N

E12 D12 C12 B12 A12

HA13_P LA05_N TP3 Pad GND DP7_M2C_P GND

E13 D13 C13 B13 A13

HA13_N TP2 Pad GND GND DP7_M2C_N GND

C E14 D14 C14 B14 A14 C

GND 4 MUX_SDA LA09_P LA10_P GND DP4_M2C_P

E15 4 MUX_SCL

D15 5 DVII_DE C15 B15 A15

HA16_P LA09_N LA10_N GND DP4_M2C_N

E16 D16 C16 B16 A16

HA16_N DVII_D23 GND GND DP6_M2C_P GND

E17 D17 C17 B17 A17

GND DVII_D20 LA13_P DVII_D19 GND DP6_M2C_N GND

E18 D18 C18 B18 A18

HA20_P LA13_N DVII_D18 LA14_P GND DP5_M2C_P

E19 5 DVII_CLK D19 C19 B19 A19

HA20_N GND LA14_N GND DP5_M2C_N

E20 D20 C20 4 GTB_CLK1+ B20 A20

GND DVII_D11 LA17_P_CC GND GBTCLK1_M2C_P GND

E21 D21 C21 4 GTB_CLK1- B21 A21

HB03_P LA17_N_CC DVII_D10 GND GBTCLK1_M2C_N GND

E22 D22 C22 B22 A22

HB03_N DVII_D9 GND LA18_P_CC GND 7 DP_ML1+ DP1_C2M_P

E23 D23 C23 B23 A23

GND DVII_D4 LA23_P 6 DVIO_CLK+ LA18_N_CC GND 7 DP_ML1- DP1_C2M_N

E24 D24 C24 B24 A24

HB05_P LA23_N GND DP9_C2M_P GND

E25 D25 C25 B25 A25

HB05_N DVII_D2 GND DVII_D3 GND DP9_C2M_N GND

E26 D26 C26 B26 A26

GND DVIO_D11 LA26_P DVIO_D10 LA27_P GND 7 DP_ML2+ DP2_C2M_P

E27 D27 C27 B27 A27

HB09_P LA26_N LA27_N GND 7 DP_ML2- DP2_C2M_N

E28 D28 C28 B28 A28

HB09_P GND GND DP8_C2M_P GND

E29 D29 C29 B29 A29

GND TCK GND DP8_C2M_N GND

E30 D30 4 FMC_SCL C30 B30 7 DP_ML3+ A30

HB13_P TDI SCL GND DP3_C2M_P

E31 D31 C31 B31 A31

HB13_N TDO 4 FMC_SDA SDA GND 7 DP_ML3- DP3_C2M_N

E32 33VAUX D32 C32 B32 A32

GND 3P3VAUX GND DP7_C2M_P GND

E33 D33 C33 B33 A33

HB19_P TMS GND DP7_C2M_N GND

E34 D34 C34 B34 A34

HB19_N TRST_L 4 FMC_GA0 GA0 GND DP4_C2M_P

E35 4 FMC_GA1 D35 C35 B35 A35

GND GA1 12P0V GND DP4_C2M_N

E36 D36 C36 B36 A36

HB21_P 3P3V GND DP6_C2M_P GND

E37 D37 +12V C37 B37 A37

HB21_N GND 12P0V DP6_C2M_N GND

B E38 D38 C38 B38 A38 B

GND 3P3V GND GND DP5_C2M_P

VADJ E39 D39 +3.3V C39 B39 A39

VADJ GND 3P3V GND DP5_C2M_N

E40 +3.3V D40 C40 B40 A40

GND 3P3V GND RES0 GND

GND GND GND GND GND

3,6 DVIO_D[0..11]

+3.3V

C93 C94 C95

0.1uF 0.1uF 0.1uF

GND GND GND

A A

Avnet Design Services

Title

FMC-A,B,C,D,E

Size Document Number Rev

B AES-FMC-DVI-G <RevCode>

Date: Thursday, November 19, 2009 Sheet 2 of 7

5 4 3 2 1

5 4 3 2 1

D D

2,5 DVII_D[0..23]

J1K J1J J1H J1G J1F

Jack/FMC-HPC Jack/FMC-HPC Jack/FMC-HPC Jack/FMC-HPC Jack/FMC-HPC

K1 J1 H1 G1 F1

VREF_B_M2C GND VREF_A_M2C GND PG_M2C

K2 J2 4 PRSTN_M2C H2 G2 F2

GND CLK1_C2M_P PRSNT_M2C_L CLK0_C2M_P GND

K3 J3 H3 G3 F3

GND CLK1_C2M_N GND CLK0_C2M_N GND

K4 J4 4 VIDEO_CLK2 H4 G4 F4

CLK1_M2C_P GND CLK0_M2C_P GND HA00_P_CC

K5 J5 4 VIDEO_CLK1 H5 G5 F5

CLK1_M2C_N GND CLK0_M2C_N GND HA00_N_CC

K6 J6 H6 G6 F6

GND HA03_P GND 7 DP2_AUX+ LA00_P_CC GND

K7 J7 H7 G7 F7

HA02_P HA03_N 7 DP2_AUX+ LA02_P 7 DP2_AUX- LA00_N_CC HA04_P

K8 J8 H8 G8 F8

HA02_N GND 7 DP2_AUX- LA02_N GND HA04_N

K9 J9 H9 7 DP1_HPD G9 F9

GND HA07_P GND LA03_P GND

K10 J10 7 DP_HPD H10 7 DP2_HPD G10 F10

HA06_P HA07_N LA04_P LA03_N HA08_P

K11 J11 4 EXTIO_INT H11 G11 F11

HA06_N GND LA04_N GND HA08_N

K12 J12 H12 G12 F12

GND HA11_P GND 7 DP_AUX+ LA08_P GND

C K13 J13 H13 G13 F13 C

HA10_P HA11_N 7 DP_AUX+ LA07_P 7 DP_AUX- LA08_N HA12_P

K14 J14 7 DP_AUX-

H14 G14 F14

HA10_N GND LA07_N GND HA12_N

K15 J15 H15 G15 F15

GND HA14_P GND 4 I2C_RST LA12_P GND

K16 J16 H16 G16 F16

HA17_P_CC HA14_N 5 DVII_HS DVII_D22 LA11_P 5 DVII_VS LA12_N HA15_P

K17 J17 H17 G17 F17

HA17_N_CC GND LA11_N DVII_D21 GND HA15_N

K18 J18 H18 G18 F18

GND HA18_P DVII_D16 GND DVII_D17 LA16_P GND

K19 J19 H19 G19 F19

HA21_P HA18_N DVII_D15 LA15_P LA16_N HA19_P

K20 J20 H20 G20 F20

HA21_N GND LA15_N DVII_D13 GND HA19_N

K21 J21 H21 G21 F21

GND HA22_P DVII_D14 GND DVII_D12 LA20_P GND

K22 J22 H22 G22 F22

HA23_P HA22_N DVII_D8 LA19_P LA20_N HB02_P

K23 J23 H23 G23 F23

HA23_N GND LA19_N DVII_D6 GND HB02_N

K24 J24 H24 G24 F24

GND HB01_P DVII_D7 GND DVII_D5 LA22_P GND

K25 J25 H25 G25 F25

HB00_P_CC HB01_N DVII_D1 LA21_P LA22_N HB04_P

K26 J26 H26 G26 F26

HB00_N_CC GND LA21_N DVII_D0 GND HB04_N

K27 J27 H27 G27 F27

GND HB07_P DVIO_D8 GND DVIO_D9 LA25_P GND

K28 J28 H28 G28 F28

HB06_P_CC HB07_N DVIO_D7 LA24_P LA25_N HB08_P

K29 J29 H29 G29 F29

HB06_N_CC GND LA24_N DVIO_D5 GND HB08_P

K30 J30 H30 G30 F30

GND HB11_P DVIO_D6 GND DVIO_D4 LA29_P GND

K31 J31 H31 G31 F31

HB10_P HB11_N DVIO_D3 LA28_P LA29_N HB12_P

K32 J32 H32 G32 F32

HB10_N GND LA28_N DVIO_D1 GND HB12_N

K33 J33 H33 G33 F33

GND HB15_P DVIO_D2 GND DVIO_D0 LA31_P GND

K34 J34 H34 G34 F34

HB14_P HB15_N LA30_P LA31_N HB16_P

K35 J35 H35 G35 F35

HB14_N GND 6 DVIO_DE LA30_N GND HB16_P

K36 J36 H36 G36 F36

GND HB18_P GND 6 DVIO_VS LA33_P GND

B K37 J37 H37 G37 F37 B

HB17_P_CC HB18_N 6 DVIO_HS LA32_P 6 DVIO_RST LA33_N HB20_P

K38 J38 6 DVIO_HPD H38 G38 F38

HB17_N_CC GND LA32_N GND HB20_N

K39 J39 H39 VADJ G39 F39

GND VIO_B_M2C GND VADJ GND

K40 J40 VADJ H40 G40 VADJ F40

VIO_B_M2C GND VADJ GND VADJ

GND GND GND GND GND

2,6 DVIO_D[0..11]

VADJ

C96 C97

0.1uF 0.1uF

GND GND

A A

Avnet Design Services

Title

FMC-F,G,H,J,K

Size Document Number Rev

B AES-FMC-DVI-G <RevCode>

Date: Thursday, November 19, 2009 Sheet 3 of 7

5 4 3 2 1

5 4 3 2 1

33VAUX

A1 A0: I2C Addr

0 0 : 0xA0 FB1 U1

0 1 : 0xA2 +3.3V Bead/80R TPS71718DCK +1.8V

1 0 : 0xA4 U2 C1 R1 R2 1 5

1 1 : 0xA6 24LC02 0.1uF NC NC C2 IN OUT C3

2

R3 10K 1uF GND 1uF

2 FMC_GA0 1 8 3 4

D R4 10K A0 VCC EN NR/FB C4 D

2 FMC_GA1 2 7

R5 10K A1 WP 0.01uF

3 6 FMC_SCL 2

3 PRSTN_M2C A2 SCL GND GND

4 5 FMC_SDA 2

GND SDA

GND GND +1.8V GND +1.8V

X1

33VAUX

10K

10K

27MHz

U3 C5

SN74LVC1G14DCK C6 0.1uF R6 R7

1 5 0.1uF 10K 10K U4

NC VCC CDCE913

2 PG_C2M 2

A

R8

R9

R39 NC 3 4 SW_ON 5,6,7 GND 1 14

GND Y Xin/Clk Xout DEV_CLK_SDA

2 13

FB2 S0 S1/SDA DEV_CLK_SCL

3 12

GND GND FB3 VADJ Bead/80R Vdd S2/SCL R10 22R

4 11 VIDEO_CLK1 3

Bead/80R Vctr Y1

5 10

C7 GND GND R11 22R

VADJ 6 9 VIDEO_CLK2 3

C8 0.1uF Vddout Y2

7 8

VADJ 0.1uF Vddout Y3

R13 R14

U5 10K 10K I2C Addr:0xCA

R50 PCA9546ADGVR GND GND GND

C

10K 1 16 C

R12 10K A0 Vcc

2 15 MUX_SDA 2

A1 SDA

3 I2C_RST 3 14 MUX_SCL 2

RST SCL

4 13

5 DVII_SDA SD0 A2 DEV_CLK_SCL

5 12

5 DVII_SCL SC0 SC3 DEV_CLK_SDA

6 11

6 DVIO_SDA SD1 SD3 X2

6 DVIO_SCL 7 10 DEV_SCL 5,6

SC1 SC2 27MHz VCC33

8 9 DEV_SDA 5,6

GND SD2

C9

GND I2C Addr:0xE0 GND 10pF

C13 C14

FB12 10uF/16V 10uF/16V VCC_PLL

R58 10K Bead/80R GND GND GND

+3.3V

C24

R60 R59 0.1uF FB4

U25 10K 10K U6 +3.3V Bead/80R VCC33

24

23

22

21

20

19

18

17

PCA9555 CDCM61002

1 24 GND C10 C11 C12

Gnd1

XIn

Vcc_In

Reg_Cap1

Vcc_Pll1

Reg_Cap2

NC

OSC_Out

3 EXTIO_INT INT VCC DEV_SDA 0.1uF 0.1uF 0.1uF

2 23

A1 SDA DEV_SCL

3 22

A2 SCL CLKGEN_PR0

4 21 25 16

5 DVII_SCDT P00 A0 Pr0 Vcc_Pll2

10K

10K

5 20 CLKGEN_OS1 CLKGEN_PR1 26 15 CLKGEN_OD2 GND GND GND

5 DVII_ST P01 P17 Pr1 OD2

B 6 19 CLKGEN_OS0 27 14 CLKGEN_OD1 B

5 DVII_PD P02 P16 CLKGEN_RST NC OD1 CLKGEN_OD0 FB5

5 DVII_CLKINV 7 18 28 13

P03 P15 CLKGEN_OD0 NC OD0 CLKGEN_RST VCC33 Bead/80R VCC_PLL

8 17 29 12

P04 P14 CLKGEN_OD1 NC RSTN CLKGEN_OS0

9 16 30 11

P05 P13 NC OS0

R55

R56

10 15 CLKGEN_OD2 31 10 CLKGEN_OS1 C15 C16 C17

P06 P12 NC OS1

10K

10K

11 14 CLKGEN_PR0 32 9 0.1uF 0.1uF 0.1uF

P07 P11 NC Vcc_VCO

Vcc_Out

Vcc_Out

12 13 CLKGEN_PR1 EP

GND P10 EP

OutN1

OutN0

OutP1

OutP0

NC

GND GND GND GND

CE

GND I2C Addr:0x40 GND GND

R15

R18

1

2

3

4

5

6

7

8

R20 NC

+12V L1

+12V +5V VCC33

C18 0.01uF 47uH GND

C26 C77 C81 0.1uF GND GTB_CLK1+ 2

22uF/16V R16 47uF/10V C82 0.1uF GTB_CLK1- 2

2

U7 10K C83 0.1uF GTB_CLK0+ 2

TPS5410 D1 C84 0.1uF GTB_CLK0- 2

GND 1 8 MBR130 GND

BOOT PH

2 7

NC VIN R19

3 6

1

NC GND 3.24K

A

4

Vsen ENA

5 The CDCM61002 device is configured to generate LVDS clock sources. A

EP

EP

GND GND GND

Avnet Design Services

Title

IPMI,I2C & Clock

Size Document Number Rev

B AES-FMC-DVI-G <RevCode>

Date: Tuesday, April 13, 2010 Sheet 4 of 7

5 4 3 2 1

5 4 3 2 1

VDD_33I

C21 C22

DVI_50I + EC3 C19 0.1uF 0.1uF

4.7uF/16V 0.01uF

VDD_33I

C20 GND GND

D 0.1uF U8 R21 R22 D

24LC02 47K 47K VADJ

1 8

A0 VCC C23 C25

2 7

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

A1 WP 0.1uF 0.1uF

3 6 DVII_SCL 4

A2 SCL R37

4 5

QO22

QO21

QO20

QO19

QO18

QO17

Q016

QO15

QO14

QO13

QO12

QO11

QO10

QO9

QO8

QO7

QO6

QO5

QO4

QO3

QO2

DGND

OGND

OVDD

CAP

GND SDA DVII_SDA 4

47K

76 50 GND GND

GND GND OGND QO1

77 49

VDD_33A QO23 QO0

78 48

OVDD HSYNC VDD_33I U10 VADJ

79 47

D2 DVII_RX2+ AGND VSYNC SN74AVCH16T245VR

80 46

J2 BAT54C +5V DVII_RX2- RX2+ DE

81 45 1 48 SW_ON 4,6,7

Jack/HDMI-A DVI_50I RX2- OGND 1DIR 1QE

1 82 44 2 47 DVII_HS 3

VDD_33I DVII_RX1+ AVDD ODCK 1B1 1A1

3 83 43 3 46 DVII_VS 3

R23 1K DVII_RX1- RX1+ OVDD 1B2 1A2

2 84 42 4 45

RX1- RSVD GND GND

19 85 41 5 44 DVII_DE 2

HPD AVDD CLT2 1B3 1A3

10K

10K

10K

10K

18 DVII_RX0+ 86 40 6 43 DVII_CLK 2

+5V DVII_RX0- RX0+ CLT1 1B4 1A4

17 87 39 7 42

DDCgnd DVII_SDA RX0- U9 DGND VCCB VCCA DVII_D23

20 16 88 38 8 41

Shell SDA DVII_SCL DVII_RXC+ AVDD TFP403/501 DVDD 1B5 1A5 DVII_D22

21 15 89 37 9 40

Shell SCL DVII_RXC- RXC+ QE23 1B6 1A6

14 90 36 10 39

Res. RXC- QE22 GND GND

R52

R51

R54

R53

13 91 35 11 38 DVII_D21

CEC DVII_RXC- AVDD QE21 1B7 1A7 DVII_D20

C 12 4,6 DEV_SCL 92 34 12 37 C

CLK- RSVD/DDC_SCL QE20 1B8 1A8 DVII_D19

11 4,6 DEV_SDA 93 33 13 36

CLKgnd DVII_RXC+ RSVD/DDC_SDA QE19 2B1 2A1 DVII_D18

10 94 32 14 35

CLK+ DVII_RX0- RSVD/DDC_SA QE18 2B2 2A2

9 95 31 15 34

D0- RSVD/PROM_SCL QE17 GND GND DVII_D17

8 96 30 16 33

D0gnd DVII_RX0+ RSVD/PROM_SDA QE16 2B3 2A3 DVII_D16

7 97 29 17 32

D0+ DVII_RX1- U19 PVDD OVDD 2B4 2A4

6 98 28 18 31

D1- VDD_33I Open/24LC04 VDD_33I PGND OGND VCCB VCCA DVII_D15

22 5 VDD_33PI 99 27 19 30

Shell D1gnd DVII_RX1+ PVDD QE15 2B5 2A5 DVII_D14

23 4 1 8 100 26 20 29

Shell D1+ A0 VCC OCK_INV QE14 2B6 2A6

OGND

DGND

OVDD

DVDD

SCDT

STAG

DVII_RX2- C78

QE10

QE11

QE12

QE13

3 2 7 EP 21 28

PIXS

PDO

DFO

QE0

QE1

QE2

QE3

QE4

QE5

QE6

QE7

QE8

QE9

D2- 0.1uF A1 WP EP GND GND DVII_D13

PD

2 3 6 22 27

ST

D2gnd DVII_RX2+ A2 SCL 2B7 2A7 DVII_D12

1 4 5 23 26

D2+ GND SDA GND 2B8 2A8

24 25 DVII_D[0..23] 2,3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

GND 2DIR 2QE

GND GND GND GND

GND GND

VDD_33I

R24 10K

4 DVII_CLKINV GND

VDD_33I U12 VADJ

4 DVII_PD GND SN74AVCH16T245VR

4 DVII_ST

1 48 SW_ON 4,6,7

4 DVII_SCDT 1DIR 1QE DVII_D11

B 2 47 B

R57 1B1 1A1 DVII_D10

3 46

470R 1B2 1A2

4 45

GND GND DVII_D9 VDD_33I

5 44

1B3 1A3

1

FB6 6 43 DVII_D8

+3.3V Bead/80R VDD_33PI LED1 1B4 1A4 C29 C30

7 42

VCCB VCCA DVII_D7 0.1uF 0.1uF

LED 8 41

1B5 1A5 DVII_D6

9 40

+ EC4 C27 C28 1B6 1A6

10 39

2

4.7uF/6.3V 0.1uF 0.1uF GND GND DVII_D5 GND GND

11 38

GND 1B7 1A7 DVII_D4

12 37

1B8 1A8 DVII_D3 VADJ

13 36

GND GND GND 2B1 2A1 DVII_D2

14 35

2B2 2A2 C31 C32

15 34

FB7 GND GND DVII_D1 0.1uF 0.1uF

16 33

+3.3V Bead/80R VDD_33A 2B3 2A3 DVII_D0

17 32

2B4 2A4

18 31 DVII_D[0..23] 2,3

RP1 10K VCCB VCCA GND GND

19 30

+ EC5 C33 C34 C35 C36 2B5 2A5

1 8 20 29

4.7uF/6.3V 0.1uF 0.1uF 0.1uF 0.1uF 2B6 2A6

2 7 21 28

GND GND

3 6 22 27

2B7 2A7

4 5 23 26

GND GND GND GND GND 2B8 2A8

24 25

2DIR 2QE

A FB8 GND A

+3.3V Bead/80R VDD_33I GND GND

+ EC6 C37 C38 C39 C40 C41 C42 C43 Avnet Design Services

4.7uF/6.3V 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF Title

DVI Input

GND GND GND GND GND GND GND GND Size Document Number Rev

B AES-FMC-DVI-G <RevCode>

Date: Thursday, November 19, 2009 Sheet 5 of 7

5 4 3 2 1

5 4 3 2 1

RP2 10K

VDD_33O VDD_33O 1 8

D D

2 7

U13 3 6

VADJ SN74CB3T1G125DCKR R25 R26 R28 R27 R44 4 5

5 1 10K 10K 4.7K 4.7K 1K

C46 VCC QE R38 R49 C57 0.1uF VDD_33O U16 VADJ

2 DVIO_HPD 3

0.1uF A NC NC SN74AVCH20T245VR GND

4 3

B GND

4,5 DEV_SDA 1 56 SW_ON 4,5,7

R29 1K 4,5 DEV_SCL 1DIR 1QE

2 55

GND GND 1B1 1A1

3 54

1B2 1A2

4 53

J3 DVI_50O GND GND

5 52

Jack/HDMI-A 1B3 1A3

6 51 DVIO_RST 3

GND GND 1B4 1A4

7 50

16

15

14

13

12

11

10

VCCB VCCA

9

8

7

6

5

4

3

2

1

R30 R31 8 49

1B5 1A5 DVIO_VS 3

19 2K 2K 9 48

ISEL/RST

VREF

BSEL/SCL

CTL1/A1/DK1

CTL2/A2/DK2

A3/DK3

MSEN/PO1

EDGE/HTPLG

DGND

DVDD

PD

VSYNC

HSYNC

DVDD

DE

DSEL/SDA

HPD 1B6 1A6 DVIO_HS 3

18 10 47 DVIO_DE 3

+5V VDD_33O VDD_33PO VDD_33T 1B7 1A7

17 EP 11 46

DDCgnd EP GND GND DVIO_D0

20 16 DVIO_SDA 4 17 64 12 45

Shell SDA R32 510R/1% PGND DGND 1B8 1A8 DVIO_D1

21 15 DVIO_SCL 4 18 63 13 44

Shell SCL PVDD D0 1B9 1A9 DVIO_D2

14 19 62 14 43

Res. TFADJ D1 1B10 1A10 DVIO_D3

13 20 61 15 42

CEC DVIO_TXC- DVIO_TXC- TGND D2 2B1 2A1 DVIO_D4

12 21 60 16 41

CLK- DVIO_TXC+ TXC- D3 2B2 2A2 DVIO_D5

11 22 59 17 40

CLKgnd DVIO_TXC+ TXC+ D4 2B3 2A3

C 10 23 58 18 39 DVIO_D[0..11] 2,3 C

CLK+ DVIO_TX0- DVIO_TX0- TVDD D5 R42 10K GND GND

9 24 57 19 38 DVIO_CLK+ 2

D0- DVIO_TX0+ TX0- U15 IDCK+ 2B4 2A4 DVIO_D6

8 25 56 20 37

D0gnd DVIO_TX0+ TX0+ TFP410 IDCK- 2B5 2A5 DVIO_D7

7 26 55 21 36 DVIO_D[0..11] 2,3

D0+ DVIO_TX1- DVIO_TX1- TGND D6 2B6 2A6

6 27 54 22 35

D1- DVIO_TX1+ TX1- D7 VCCB VCCA DVIO_D8

22 5 28 53 23 34

Shell D1gnd DVIO_TX1+ TX1+ D8 2B7 2A7 DVIO_D9

23 4 29 52 24 33

Shell D1+ DVIO_TX2- DVIO_TX2- TVDD I2C Addr:0x70 D9 2B8 2A8

3 30 51 25 32

D2- DVIO_TX2+ TX2- D10 GND GND DVIO_D10

2 31 50 26 31

D2gnd DVIO_TX2+ TX2+ D11 2B9 2A9 DVIO_D11

1 32 49 27 30

D2+ TGND NC 2B10 2A10

28 29

2DIR 2QE

DGND

DVDD

RSVD

DKEN

D23

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

GND GND GND GND

GND GND

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

VDD_33O

GND

VDD_33O VADJ

C48 C49 C50 C51

B 0.1uF 0.1uF 0.1uF 0.1uF B

FB9

+3.3V Bead/80R VDD_33PO

GND GND GND GND

+ EC7 C47 C85

4.7uF/6.3V 0.1uF 2200pF

GND GND GND

DVI_50O U14 +5V FB10

TPS22942 +3.3V Bead/80R VDD_33T

C44 1 5 C45

1uF Vout Vin 1uF

2

GND + EC8 C52 C53 C86

3 4

OC ON 4.7uF/6.3V 0.1uF 0.1uF 2200pF

GND Current Limit: GND

55mA<=Current<=500mA GND GND GND GND

FB11

+3.3V Bead/80R VDD_33O

A A

+ EC9 C54 C55 C56 C87 C88 C89

4.7uF/6.3V 0.1uF 0.1uF 0.1uF 2200pF 2200pF 2200pF

Avnet Design Services

GND GND GND GND GND GND GND Title

DVI Output

Size Document Number Rev

B AES-FMC-DVI-G <RevCode>

Date: Thursday, November 19, 2009 Sheet 6 of 7

5 4 3 2 1

5 4 3 2 1

DP_33 DP_33 DP_33

C90 C91 C92

0.1uF 0.1uF 0.1uF

U18

15

14

13

U17 TPD8S009

6

5

4

D TPD4E001DRLR GND GND GND D

VCC

NC

VCC

IO2 IO4

GND IO3

IO1 VCC

DP_33 VADJ

GNDE

GND

GND

GND

D0+

D1+

D2+

D3+

D0-

D1-

D2-

D3-

100K

100K

J4 C79

Jack/DP 0.1uF U22

DP_HPD_IN

DP_33 SN74CB3T1G125DCKR

1

2

3

1

2

3

4

5

6

7

8

9

10

11

12

R41

R40

5 1 SW_ON 4,5,6

GND VCC QE

20 2 DP_HPD 3

PWR DP_HPD_IN A

21 19 4 3

Shell Gnd B GND

22 18

Shell HPD C61 0.1uF R46

17 DP_AUX- 3

AUX_CH- GND GND 100K GND

16

Gnd R35 1M C62 0.1uF

15 DP_AUX+ 3

AUX_CH+

14

Config2

13

Config1 C63 0.1uF GND

12 DP_ML3- 2

ML_L3- R36 1M GND

11

Gnd C64 0.1uF VADJ

10 DP_ML3+ 2

ML_L3+ C65 0.1uF

9 DP_ML2- 2

ML_L2- C80

8

Gnd C66 0.1uF 0.1uF U23

7 DP_ML2+ 2

ML_L2+ C67 0.1uF SN74CB3T1G125DCKR

6 DP_ML1- 2

ML_L1-

C 5 5 1 SW_ON 4,5,6 C

Gnd C68 0.1uF GND VCC QE

4 DP_ML1+ 2 2 DP1_HPD 3

ML_L1+ C69 0.1uF DP1_HPD_IN A

23 3 DP_ML0- 2 4 3

ShellML_L0- B GND

24 2

Shell Gnd C70 0.1uF R47

1 DP_ML0+ 2

ML_L0+ 100K GND

GND GND

GND

VADJ

Current or Power Limit:

Current<=500mA,Powert>=1.5W R45 U24

4,5,6 SW_ON 10K SN74LVC1G14DCK DP2_33

U20 DP_33 1 5

+3.3V TPS2041BDBV NC VCC

3 DP2_HPD 2

C75 A DP2_HPD_OUT

4 3 3 4

C76 EN OC 22uF/16V GND Y

2

1uF GND R48

5 1

IN OUT GND 100K

GND GND

B B

GND

U26

TPS2082

+3.3V 1 8 DP2_33 DP1_33

GND OC

2 7

IN1 OUT1 DP1_33 DP2_33

3 6

C58 IN2 OUT2

4 5

1uF EN1 EN2 C59 C60 DP1_HPD_IN DP2_HPD_OUT

1 2

22uF/16V 22uF/16V 3 4

C72 0.1uF 5 6 C71 0.1uF DP1_AUX+ 2

2 DP1_AUX-

7 8

GND GND GND C74 0.1uF 9 10 C73 0.1uF DP2_AUX+ 3

3 DP2_AUX-

4,5,6 SW_ON

H1

GND Hea/2.54/2X5 GND

MT1 MT2

MTH MTH

A A

Avnet Design Services

GND GND Title

DP & GPIO

Size Document Number Rev

B AES-FMC-DVI-G <RevCode>

Date: Thursday, November 19, 2009 Sheet 7 of 7

5 4 3 2 1

Você também pode gostar

- Acer Aspire Revo R3700 Foxconn TDPS05 PDFDocumento42 páginasAcer Aspire Revo R3700 Foxconn TDPS05 PDFNicolás TorresAinda não há avaliações

- Acer fShenzhen AIO FDI connection diagramDocumento45 páginasAcer fShenzhen AIO FDI connection diagramluis felipezAinda não há avaliações

- Acer Aspire Aod 532h Nav50 Compal La-5651p 0104 r1.0Documento41 páginasAcer Aspire Aod 532h Nav50 Compal La-5651p 0104 r1.0Marcio SilvaAinda não há avaliações

- Anais Do Workshop De Micro-ondasNo EverandAnais Do Workshop De Micro-ondasAinda não há avaliações

- OrangePi OnePlus Schematics v2.0Documento13 páginasOrangePi OnePlus Schematics v2.0Ernesto Montera jr.Ainda não há avaliações

- 8f0e1f54c07d7af3fc747f5d4ad1a4a7(1)Documento10 páginas8f0e1f54c07d7af3fc747f5d4ad1a4a7(1)Waelghanii GhaniAinda não há avaliações

- GPIO control system guideDocumento13 páginasGPIO control system guideAndres Alegria80% (15)

- Pad App4 STD V1 40 20120927Documento18 páginasPad App4 STD V1 40 20120927Henrique VianaAinda não há avaliações

- Wistron - Mockingbird - N - V - 14 - 15 - TGL - & - Hellcat - 14 - 15 - 17 - TGL - 19861 - 19862 1986-1 Dell Inspiron 5402Documento105 páginasWistron - Mockingbird - N - V - 14 - 15 - TGL - & - Hellcat - 14 - 15 - 17 - TGL - 19861 - 19862 1986-1 Dell Inspiron 5402German ValenciaAinda não há avaliações

- Diagrama de Alimentación Electrica para Bombas de Pozo ProfundoDocumento1 páginaDiagrama de Alimentación Electrica para Bombas de Pozo ProfundoAmairani MartínezAinda não há avaliações

- Rpi CM V1 - 1 Schematic PDFDocumento4 páginasRpi CM V1 - 1 Schematic PDFStephen J. RobertsAinda não há avaliações

- IPC-P01-Z02-sch-2022Documento17 páginasIPC-P01-Z02-sch-2022Rostislav NikitinAinda não há avaliações

- DAV02PI16E0Documento9 páginasDAV02PI16E0Chami NdaAinda não há avaliações

- NS-A031 ODD to VGA board schematic compal)Documento17 páginasNS-A031 ODD to VGA board schematic compal)zigmund zigmundAinda não há avaliações

- Acer One 14 z1402 Mbpndbu144-0320Documento31 páginasAcer One 14 z1402 Mbpndbu144-0320achmed28Ainda não há avaliações

- Duo Schematic v1.1Documento7 páginasDuo Schematic v1.1David GomezAinda não há avaliações

- V313 40 (00017967) DecryptDocumento15 páginasV313 40 (00017967) DecryptDiego TernavasioAinda não há avaliações

- Dell Precision M4800 VAQ10 LA-9771P Rev 1.0Documento65 páginasDell Precision M4800 VAQ10 LA-9771P Rev 1.0Jan FiserAinda não há avaliações

- V313 50 (00017967) DecryptDocumento15 páginasV313 50 (00017967) DecryptDiego TernavasioAinda não há avaliações

- Pegatron BOSTON BS BS-TK Colay REV 1.0 - Toshiba Satellite C670Documento77 páginasPegatron BOSTON BS BS-TK Colay REV 1.0 - Toshiba Satellite C670Serwis MagazynAinda não há avaliações

- Confidential weilu (盧偉 客戶服務部 孫飛: MSI 60000121 RD (C) 2016072112102Documento71 páginasConfidential weilu (盧偉 客戶服務部 孫飛: MSI 60000121 RD (C) 2016072112102Jonathan ChaAinda não há avaliações

- SCH - 501 1 01180 - A0 01Documento11 páginasSCH - 501 1 01180 - A0 01imran khanAinda não há avaliações

- Compal GH52T LA-L051P Rev 1.0Documento121 páginasCompal GH52T LA-L051P Rev 1.0Павел В. (Bis Nival - IrBis Snow)Ainda não há avaliações

- gigabyte_ga-g41m-es2l_rev_1.4_schDocumento11 páginasgigabyte_ga-g41m-es2l_rev_1.4_schwrprogramas serviçosAinda não há avaliações

- Dell Alienwarem 15 r2 Compal Edq51 La-h351p La-f552p La-f553p 1.0 (Xa00)(1)Documento109 páginasDell Alienwarem 15 r2 Compal Edq51 La-h351p La-f552p La-f553p 1.0 (Xa00)(1)ml5801088Ainda não há avaliações

- Schematic FS2-Camera FS2Documento1 páginaSchematic FS2-Camera FS2anon_289738722Ainda não há avaliações

- Acer Nitro AN515-34 Compal FH50Q LA-J621P Rev 1.0 SchematicDocumento100 páginasAcer Nitro AN515-34 Compal FH50Q LA-J621P Rev 1.0 SchematicSolder PanasAinda não há avaliações

- Acer Nitro AN517-52 Compal FH51M LA-J871P Rev 1.0 СхемаDocumento112 páginasAcer Nitro AN517-52 Compal FH51M LA-J871P Rev 1.0 Схемаpdg com0% (1)

- MSI Confidential 60000014 FOR RMA維修 (劉松林) : Shark Bay PlatformDocumento44 páginasMSI Confidential 60000014 FOR RMA維修 (劉松林) : Shark Bay PlatformjorgeAinda não há avaliações

- 1 - Block DiagramDocumento1 página1 - Block DiagramHungAinda não há avaliações

- Abit ZX-G31LM Rev1.4Documento28 páginasAbit ZX-G31LM Rev1.4datamarce2016 marceAinda não há avaliações

- HP ProBook 6560b - FoxConn Cure DIS Rev 0Documento52 páginasHP ProBook 6560b - FoxConn Cure DIS Rev 0amitintime4uAinda não há avaliações

- Lenovo Yoga 700-14isk Byg43 Nm-A601 Rev 1.0 PDFDocumento46 páginasLenovo Yoga 700-14isk Byg43 Nm-A601 Rev 1.0 PDFA Meza BautiztaAinda não há avaliações

- Hasee E310 E360Documento40 páginasHasee E310 E360NICSTRONAinda não há avaliações

- Analog Grayscale sensor circuit diagramDocumento2 páginasAnalog Grayscale sensor circuit diagramRafael Pereira AzevedoAinda não há avaliações

- GA-G41MT-S2PT Block Diagram and Sheet IndexDocumento33 páginasGA-G41MT-S2PT Block Diagram and Sheet Indexxxx21Ainda não há avaliações

- Compal MB schematic documentDocumento112 páginasCompal MB schematic documentjulio cesar mina100% (1)

- V Nitro VN7-791 791G 14203-2 4PD02G010001 14203 Rev - 2Documento71 páginasV Nitro VN7-791 791G 14203-2 4PD02G010001 14203 Rev - 2Guillermo OspinaAinda não há avaliações

- Adp 3060 PDFDocumento1 páginaAdp 3060 PDFsasha21123Ainda não há avaliações

- Mars ST3-R1-1 User Schematics V2Documento13 páginasMars ST3-R1-1 User Schematics V2gunrjsAinda não há avaliações

- Anexo 3 - Orange Pi - Zero2 - H616 - Schematic - v1.3Documento11 páginasAnexo 3 - Orange Pi - Zero2 - H616 - Schematic - v1.3drmwndrrAinda não há avaliações

- Compal La-C571pDocumento44 páginasCompal La-C571pJhones CAMAinda não há avaliações

- V313 60 (00017967) DecryptDocumento15 páginasV313 60 (00017967) DecryptDiego TernavasioAinda não há avaliações

- Compal LA-G021P r1.BDocumento49 páginasCompal LA-G021P r1.BAnalia Madeled Tovar JimenezAinda não há avaliações

- Pegatron AIC70 Rev.2.0 (2011)Documento77 páginasPegatron AIC70 Rev.2.0 (2011)Алекс ХомичAinda não há avaliações

- Lenovo E531 VILE1 - VILE2 NM-A043 NM-A044 NM-A041 SchematicDocumento59 páginasLenovo E531 VILE1 - VILE2 NM-A043 NM-A044 NM-A041 SchematicSaulo Dote100% (1)

- Philco DVH 429Documento9 páginasPhilco DVH 429ffabiannAinda não há avaliações

- Banan Pi BPI-R1 MP Schematic-SD - V3-20140922Documento14 páginasBanan Pi BPI-R1 MP Schematic-SD - V3-20140922Tuan AnhAinda não há avaliações

- MS-17631 2.0 PDFDocumento49 páginasMS-17631 2.0 PDFpedro arthur AlvesAinda não há avaliações

- Ecs V10il1 37GV10000 C0 Rev C PDFDocumento32 páginasEcs V10il1 37GV10000 C0 Rev C PDFSigit SandjajaAinda não há avaliações

- MS-16Q2 - MS-16Q21 Rev1.0Documento73 páginasMS-16Q2 - MS-16Q21 Rev1.0CarlosAinda não há avaliações

- Acer Travelmate 5744 BIC50 BA52 CPDocumento67 páginasAcer Travelmate 5744 BIC50 BA52 CPAcomputer Nathon100% (1)

- BAP41/BAP51/SJM52: UMA+Discrete (SW GFX) Main BoardDocumento49 páginasBAP41/BAP51/SJM52: UMA+Discrete (SW GFX) Main BoardMihohohoAinda não há avaliações

- Block DiagramDocumento32 páginasBlock DiagramBelkis Amion AlbonigaAinda não há avaliações

- HP Pavilion 20 DA0WJBMB6C0 REV CDocumento52 páginasHP Pavilion 20 DA0WJBMB6C0 REV CMustafa FanuswalaAinda não há avaliações

- Arduino Primo Core v02 SchematicsDocumento4 páginasArduino Primo Core v02 SchematicsSamudera Al HakamAinda não há avaliações

- 2012 FDM Apc000842Documento9 páginas2012 FDM Apc000842Mauricio Reyna CameroAinda não há avaliações

- The New ISO 527Documento25 páginasThe New ISO 527rubenssan100% (1)

- Avnet Aes FMC Imageov G Hardware GuideDocumento17 páginasAvnet Aes FMC Imageov G Hardware GuideMauricio Reyna CameroAinda não há avaliações

- Aes FMC Dvi G 01 SCH 041310 PinllocDocumento7 páginasAes FMC Dvi G 01 SCH 041310 PinllocMauricio Reyna CameroAinda não há avaliações

- Ug381 Spartan6 selectIOrResourcesDocumento98 páginasUg381 Spartan6 selectIOrResourcesMauricio Reyna CameroAinda não há avaliações

- TQG144Documento364 páginasTQG144Nguyễn Công CườngAinda não há avaliações

- Aes-z7pz-Sdr2-Dev-g-fmc Revc Schem 02 039799c Top 0Documento12 páginasAes-z7pz-Sdr2-Dev-g-fmc Revc Schem 02 039799c Top 0Mauricio Reyna CameroAinda não há avaliações

- DVI I/O FMC Module: Hardware GuideDocumento19 páginasDVI I/O FMC Module: Hardware GuideMauricio Reyna CameroAinda não há avaliações

- Uni Genoa Alberto Lagazzo enDocumento1 páginaUni Genoa Alberto Lagazzo enMauricio Reyna CameroAinda não há avaliações

- DVI I/O FMC Module: Hardware GuideDocumento19 páginasDVI I/O FMC Module: Hardware GuideMauricio Reyna CameroAinda não há avaliações

- TQG144Documento364 páginasTQG144Nguyễn Công CườngAinda não há avaliações

- Adventures With The AtariDocumento372 páginasAdventures With The AtariIman MirblokiAinda não há avaliações

- Adolescents and The MediaDocumento4 páginasAdolescents and The MediaashleyAinda não há avaliações

- Edward Winter - Chessy WordsDocumento4 páginasEdward Winter - Chessy WordsHarcownik Rafał100% (1)

- 1625408-Expanded Tomb of Annihilation - Part 2 Needles BonesDocumento35 páginas1625408-Expanded Tomb of Annihilation - Part 2 Needles BonesMichel Pret100% (2)

- Through The Looking Glass Resumen MAFE SALAZARDocumento2 páginasThrough The Looking Glass Resumen MAFE SALAZARDeisy Marcela FernandezAinda não há avaliações

- Get Up!: More Thoughts On The 100 Rep ChallengeDocumento4 páginasGet Up!: More Thoughts On The 100 Rep ChallengeStasha100% (1)

- 1.2.a Physical TrainingDocumento17 páginas1.2.a Physical TrainingRICA ELACIONAinda não há avaliações

- Australia - Bocce and PetanqueDocumento4 páginasAustralia - Bocce and PetanqueSachin SachdevAinda não há avaliações

- Ultra Catan Rules - Special Building PhaseDocumento4 páginasUltra Catan Rules - Special Building Phasepmerta11Ainda não há avaliações

- Tiger & Dragon RulesDocumento2 páginasTiger & Dragon RulesRic100% (1)

- Spell-Less Ranger For DND 5e and Primeval ThuleDocumento4 páginasSpell-Less Ranger For DND 5e and Primeval Thuleapi-298079750Ainda não há avaliações

- Anagram GenDocumento51 páginasAnagram Genvinay999Ainda não há avaliações

- PkgiDocumento382 páginasPkgiBlack CatAinda não há avaliações

- 46cb PDFDocumento8 páginas46cb PDFstreamer75Ainda não há avaliações

- Block CadDocumento9 páginasBlock CadJ Perez SanchezAinda não há avaliações

- Pokemon CheatsDocumento300 páginasPokemon CheatsCarlson G. DavidAinda não há avaliações

- Informatics Practices XIDocumento44 páginasInformatics Practices XIDivyesh Shukla88% (8)

- Executive+Committee+Roster+ +february+2014Documento6 páginasExecutive+Committee+Roster+ +february+2014George SkinnerAinda não há avaliações

- 2012 RO S London - V2Documento317 páginas2012 RO S London - V2Sabrina Daniela GrozaAinda não há avaliações

- D&D 3.0 Level 12 Adventure - Fait Accompli PDFDocumento14 páginasD&D 3.0 Level 12 Adventure - Fait Accompli PDFmichael100% (1)

- Delmo - L. Chapter 2Documento18 páginasDelmo - L. Chapter 2At Sa Wakas AyAinda não há avaliações

- BF2 CommanderDocumento14 páginasBF2 CommanderHery GiacchinoAinda não há avaliações

- Rubik's Cube Classic 3x3 Solution Hints! BookletDocumento7 páginasRubik's Cube Classic 3x3 Solution Hints! BookletJustinAinda não há avaliações

- ChatlogDocumento26 páginasChatlogSteven KaEneAinda não há avaliações

- Nintendo Power 002Documento107 páginasNintendo Power 002Adam Glassner100% (3)

- D&D THAC0 TableDocumento1 páginaD&D THAC0 TableDustin RoscoeAinda não há avaliações

- Harry Potter RPG Core Rule BookDocumento163 páginasHarry Potter RPG Core Rule BookBlackananke100% (1)

- Acuesta AquaSci1 Activity2-1-1 PDFDocumento2 páginasAcuesta AquaSci1 Activity2-1-1 PDFAngel Mae AcuestaAinda não há avaliações

- Lewis Le Val - The FallDocumento18 páginasLewis Le Val - The Fallmagojuank100% (2)