Escolar Documentos

Profissional Documentos

Cultura Documentos

Tutorial FPGA Espanol

Enviado por

Jose Ignacio Gonzalez BeltramoDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Tutorial FPGA Espanol

Enviado por

Jose Ignacio Gonzalez BeltramoDireitos autorais:

Formatos disponíveis

Adscripción Ingeniero Ruben VRECH

Implementación de un FPGA

En esta clase se muestra la edición en VHDL y la simulación de un contador básico utilizando la

herramienta de diseño ISE 10.1 de Xilinx. Está basado en la guía del “Quick Start Tutorial”

Implementaremos un contador que consta de dos entradas (reloj, dirección) y una salida

(cuenta).

La señal reloj es el reloj del contador, la señal dirección indica la dirección de la cuenta (0

para descendente y 1 para ascendente). La señal cuenta indica el número actual en la salida

del contador.

ESTRUCTURA

Se utilizará programación VHDL a partir del siguiente algoritmo:

1. Declarar señales reloj y dirección como entradas de un bit, y cuenta como salida de

cuatro bits.

2. Declarar en la arquitectura la señal n como un número binario de cuatro bits

inicializado en 0.

3. Definir el comportamiento del contador en un proceso:

Si ocurre un flanco positivo de reloj

Si dirección es ascendente: n=n+1

Sino: n=n–1

4. Asignar la salida:

cuenta = n

Los pasos 3 y 4 son concurrentes, es decir, sus sentencias tienen efecto al mismo tiempo. El

orden en el que aparecen en la descripción no determina el orden de ejecución. En cambio,

dentro del proceso el orden sí es importante. En este caso las asignaciones se realizan de

acuerdo a las condiciones cumplidas.

En ISE 10.1 existen ejemplos de VHDL para varias construcciones típicas de circuitos

lógicos.

Los ejemplos se eligen de un menú y luego se editan para ajustar la descripción al diseño

lógico.

Electrónica Digital I Página 1-12

Adscripción Ingeniero Ruben VRECH

METODOLOGÍA DE DISEÑO

A. Creación de un proyecto nuevo. Los diseños lógicos se preparan en un proyecto de

diseño. Los proyectos de diseño constan generalmente de un grupo de archivos fuentes

y otros generados por las herramientas del software. Para este proyecto usaremos dos

archivos fuentes, uno de descripción VHDL y otro de señales de prueba.

B. Creación de un archivo VHDL. Este archivo contendrá la descripción del contador.

C. Revisión de la sintaxis. Verifica que la descripción textual cumple con las reglas de

sintaxis del lenguaje.

D. Creación de un archivo de la simulación de ondas. Sirve para definir las señales de

entrada en el tiempo.

E. Simulación del diseño. Se realiza para comprobar el funcionamiento del circuito

especificado.

Electrónica Digital I Página 2-12

Adscripción Ingeniero Ruben VRECH

EL PROYECTO

A. CREACIÓN DE UN PROYECTO NUEVO

1. Seleccione File > New Project… Aparece una ventana que lleva el título New Project

Wizard – Create New Project (Figura 1). Haga lo siguiente:

• En el campo Project name escriba Contador como nombre del proyecto.

• En el campo Project location ingrese un nombre de directorio (carpeta) o busque un

directorio para el proyecto. Si el nombre no existe se creará un nuevo directorio (o

subdirectorio) automáticamente.

• En la lista desplegable Top-level source type verifique que esté activa la opción HDL.

.

Figura 1

2. Presione el botón Next. Aparece una ventana para definir las propiedades del dispositivo.

Establezca las propiedades siguientes y deje las demás tal como están (Figura 2):

• Product Category : All

• Family : Spartan3

• Device : XC3S200

• Package : FT256

• Speed Grade : -4

• Top-Level Source Type : HDL

• Synthesis Tool : XST (VHDL/Verilog)

• Simulator : ISE Simulator (VHDL/Verilog)

• Preferred Language : VHDL

• Verifique que la opción Enable Enhanced Design Summary esté seleccionada

Electrónica Digital I Página 3-12

Adscripción Ingeniero Ruben VRECH

Figura 2

3. Click Next. Aparece una ventana para crear un nuevo archivo fuente (Figura 3).

Figura 3

Electrónica Digital I Página 4-12

Adscripción Ingeniero Ruben VRECH

4. Pulse sobre el botón New Source…. Aparece una ventana para seleccionar el tipo de

archivo (Figura 4):

• Seleccione VHDL Module como el tipo de archivo fuente.

• En File name escriba Contador como el nombre del archivo (en este trabajo coincide

con el nombre del proyecto, pero puede ser otro nombre cualquiera).

• Verifique que la casilla Add to project esté seleccionada.

Figura 4

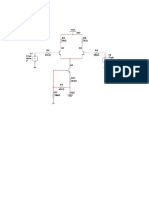

5. Pulse en Next. Aparece una ventana para definir la interfaz del módulo. Establezca los

puertos de entrada y salida tal como se muestra en la Figura 5:

• Las señales reloj y dirección son entradas de un bit.

• La señal cuenta es un bus de salida de cuatro bits. Su MSB está indexado con 3 y su

LSB con 0, es decir, el bit de cuenta de mayor peso es cuenta(3) y el de menor peso es

cuenta(0).

Figura 5

Electrónica Digital I Página 5-12

Adscripción Ingeniero Ruben VRECH

6. Click Next. Aparece un resumen (figura 6) del archivo fuente.

Figura 6

7. Pulse en Finish. Si aparece un mensaje

notificando que el directorio no existe, se pedirá

una confirmación para crearlo. Presione en Yes en

ese caso.

8. Pulse en Next, y otra vez en Next. Aparece un

resumen del proyecto (figura 8).

Figura 8

Electrónica Digital I Página 6-12

Adscripción Ingeniero Ruben VRECH

9. Pulse en el botón Finish. En el entorno de trabajo aparece el archivo fuente (figura 9).

Algunas líneas de comentarios han sido removidas del archivo original.

Figura 9

Electrónica Digital I Página 7-12

Adscripción Ingeniero Ruben VRECH

B. EDICIÓN DEL ARCHIVO VHDL

10. La edición del circuito puede hacerse a partir de una plantilla para acelerar el tiempo de

escritura y evitar errores comunes de sintaxis:

a) Sitúe el cursor después de la línea de begin y antes de la última línea de texto (después

de la línea 34 y antes de la línea 37 de la figura 9).

b) Abra las plantillas del lenguaje seleccionando Edit > Language Templates…

c) Pulse sobre los símbolos "+" siguiendo la secuencia:VHDL > Synthesis Constructs

>Coding Examples > Counters > Binary > Up/Down Counters > Simple Counter.

d) Con Simple Counter seleccionado, elija Edit > Use in File, o pulse sobre el botón

Use Template in File de la barra de herramientas. Esta acción copia la plantilla

seleccionada en el archivo de texto VHDL

e) Cierre la ventana de las plantillas.

11. Edite el archivo de la siguiente manera:

a) Declare la señal n, que servirá como contador del circuito:

signal n: std_logic_vector(3 downto 0) := "0000"

b) Modifique la plantilla para hacer coincidir los nombres de las señales con los

indicados en la plantilla. Realice lo siguiente:

Remplace <clock> con reloj

Remplace <count_direction> con dirección

Remplace <count> con n

c) Agregue la línea siguiente (puede ir en cualquier parte del cuerpo de la arquitectura,

mas por legibilidad colóquela después de la sentencia del proceso): cuenta <= n;

d) Guarde el archivo File > Save. El archivo lucirá como en la figura10.

Figura 10

Electrónica Digital I Página 8-12

Adscripción Ingeniero Ruben VRECH

C. REVISIÓN DE LA SINTAXIS.

12. Verifique que la opción Implementation esté

seleccionada en la lista despegable de la ventana

Sources.-------------------------------------

13. Seleccione la fuente de diseño Contador en la

ventana Sources para visualizar los procesos en la

ventana Processes. -------------------------

14. Pulse en la marca "+" al lado del proceso Synthesize-

XST para expandir este grupo.---

15. Haga doble click en Check Syntax.---- ---

Comenzará la revisión de la sintaxis del diseño Contador.

Si se producen errores ellos aparecen en la pestaña

Console de la ventana Transcript. Si aparecen errores

revise la sintaxis, corrija los errores y vuelva a revisar la sintaxis.

Si existe un antivirus activado en la computadora, es probable que aparezca el siguiente

mensaje de error (la ruta y nombre de archivo puede variar):

* HDL Compilation *

===============================================

========

ERROR:HDLParsers - Cannot reanme dependency database for library "work",

file is "xst/work/hdpdeps.ref". Temporary database file

"D:\\VHDL\Xilinx\ISE10.1\Tutorial\xst\work\xil_2552_6" will remain.

System error message is: No such file or directory

La solución es desactivar el antivirus, antes desconecte su computador de la red y no abra

ningún otro programa por medidas de seguridad.

Electrónica Digital I Página 9-12

Adscripción Ingeniero Ruben VRECH

D. EDICIÓN DE LAS ONDAS DE SEÑALES

16. Para crear las ondas de las señales de entrada, que servirán como estímulos para validar el

funcionamiento del diseño a través de las respuestas en la onda de la señal de salida,

realice los siguientes pasos:

a) Seleccione el archivo Contador en la ventana Sources.

b) Seleccione Project > New Source.

c) En New Source Wizard elija Test Bench WaveForm y escriba

Contador_tbw en el campo File Name.

Figura 12

17. Pulse en Next. Aparece la página Associated Source donde se indica que está

asociándose la forma de onda con el archivo Contador.

18. Pulse en Next. La página Summary muestra que el archivo fuente será agregado al

proyecto, y muestra el directorio, tipo y nombre.

19. Pulse en Finish. Aparece una ventana para inicializar y configurar la temporización del

diseño. Para este diseño la frecuencia de reloj es 25 MHz, la entrada dirección debe ser

válida 10 ns antes del flanco de subida del reloj y la salida cuenta debe ser válida 10 ns

después del flanco positivo del reloj. Complete los datos siguientes (Figura 13):

• Clock High Time : 20 ns

• Clock Low Time : 20 ns

• Input Setup Time : 10 ns

• Output Valid Delay : 10 ns

• Global Signals : GSR (FPGA)

• Offset : 0 ns

• Initial Length of Test Bench : 1500 ns

Deje los demás valores tal como están.

Electrónica Digital I Página 10-12

Adscripción Ingeniero Ruben VRECH

Figura 13

20. Pulse en Finish. Aparecerá una ventana con las formas de las ondas. Si prefiere, edite la

onda de dirección para realizar una cuenta ascendente o mixta.

21. Guarde el archivo de ondas.

Electrónica Digital I Página 11-12

Adscripción Ingeniero Ruben VRECH

E. SIMULACIÓN LÓGICA (FUNCIONAL) DEL DISEÑO

22. En la ventana Sources, seleccione Behavioral

Simulation. -------------------------------------------------

23. Seleccione Contador_tbw--------------------------------

24. En la ventana Processes pulse en + para expandir el

proceso Xilinx ISE Simulator y pulse dos veces seguidas

sobre Simulate Behavioral Model (pulse en la pestaña

Process si no los viera inicialmente). El simulador

aparecerá y ejecutará la simulación hasta el final del

archivo de simulación. -------------

25. Para observar los resultados de simulación, seleccione la

pestaña Simulation. Observará un patrón como el de la

Figura 16.

26. Finalmente, verifique el funcionamiento del contador.

Realice los cambios que crea conveniente en el archivo

de ondas para cubrir más casos de simulación y vuelva a

ejecutar el simulador para actualizar las salidas.

Figura 16

Electrónica Digital I Página 12-12

Você também pode gostar

- Tutorial de Diseño Con VivadoDocumento27 páginasTutorial de Diseño Con VivadoLorena NgongangAinda não há avaliações

- Practica 1 Compuertas Multiplexor VHDLDocumento10 páginasPractica 1 Compuertas Multiplexor VHDLshujidanAinda não há avaliações

- Compilador C CCS y Simulador Proteus para Microcontroladores PICNo EverandCompilador C CCS y Simulador Proteus para Microcontroladores PICNota: 2.5 de 5 estrelas2.5/5 (5)

- Quartus Compuerta XnorDocumento24 páginasQuartus Compuerta XnorDavid Gamboa GuzmánAinda não há avaliações

- Conexión SQL SERVER & C# (Manual para principiantes)No EverandConexión SQL SERVER & C# (Manual para principiantes)Nota: 1 de 5 estrelas1/5 (1)

- L11 - FPGA (Casi Terminado)Documento21 páginasL11 - FPGA (Casi Terminado)Gonzalo PereyraAinda não há avaliações

- Desarrollo de circuitos lógicos con CPLD Xilinx ISEDocumento22 páginasDesarrollo de circuitos lógicos con CPLD Xilinx ISEerick mondragon quintana0% (1)

- Guía 1 SDI 115 2013Documento10 páginasGuía 1 SDI 115 2013Estevis MongeAinda não há avaliações

- Programación con lenguajes de guión en páginas web. IFCD0110No EverandProgramación con lenguajes de guión en páginas web. IFCD0110Ainda não há avaliações

- DevC++ Manual Con Interpretacion de ErroresDocumento17 páginasDevC++ Manual Con Interpretacion de ErroresFelipe Aun100% (1)

- Creacion Del Primer Proyecto en MIKROC PRO FOR AVRDocumento12 páginasCreacion Del Primer Proyecto en MIKROC PRO FOR AVRELPICHUEAinda não há avaliações

- Tutorial CodeWarrior v10 MicrocontroladoresDocumento15 páginasTutorial CodeWarrior v10 MicrocontroladoresCarlos OcampoAinda não há avaliações

- SDI Práctica 5Documento5 páginasSDI Práctica 5Jordy Leonardo Figueroa LoorAinda não há avaliações

- Practica Con VHDLDocumento9 páginasPractica Con VHDLAle KeyAinda não há avaliações

- Contador BCD a 7 segmentos en XilinxDocumento18 páginasContador BCD a 7 segmentos en XilinxJosset Aldridge AguilaAinda não há avaliações

- P01 IDE MikroC Edicion Compilacion Simulacion y Depuracion de Un ProgramaDocumento15 páginasP01 IDE MikroC Edicion Compilacion Simulacion y Depuracion de Un ProgramaaLciLAinda não há avaliações

- Guía 1 SDI-SDU-115-2014Documento10 páginasGuía 1 SDI-SDU-115-2014Patho CortzAinda não há avaliações

- VHDL ProyectosDocumento92 páginasVHDL ProyectosLander Arturo Rubio JuarezAinda não há avaliações

- P05 Programacion en Lenguaje C Con El IDE MikroC Pro For PICDocumento12 páginasP05 Programacion en Lenguaje C Con El IDE MikroC Pro For PICMarco Antonio Ergueta Yujra0% (1)

- Lab 01 - POO en C# y Desarrollo de Aplicaciones Windows FormDocumento6 páginasLab 01 - POO en C# y Desarrollo de Aplicaciones Windows FormLeonardo fabrizio Quispe PazAinda não há avaliações

- Sistemas Digitales Lab 1Documento17 páginasSistemas Digitales Lab 1Pedro MartosAinda não há avaliações

- Tutorial CodeblocksDocumento50 páginasTutorial CodeblocksErick GarcíaAinda não há avaliações

- Diseño Digital Con Esquemáticos y VHDL, Implementado en La FPGA Spartan 2Documento4 páginasDiseño Digital Con Esquemáticos y VHDL, Implementado en La FPGA Spartan 2Camilo RolónAinda não há avaliações

- Manual GalaxyDocumento16 páginasManual GalaxyCésar Ulises ZamoraAinda não há avaliações

- Code Blocks 1Documento50 páginasCode Blocks 1Reyna CamachoAinda não há avaliações

- Code BlockDocumento50 páginasCode BlockAnonymous gUkr7L29O4Ainda não há avaliações

- Xilinx ISE TutorialDocumento30 páginasXilinx ISE TutorialJavier Balam BasoraAinda não há avaliações

- SD1 PR2 Introduccion VHDL 2023-1Documento27 páginasSD1 PR2 Introduccion VHDL 2023-1Antonio MuroAinda não há avaliações

- Tarea 1 SDI 115 2015Documento11 páginasTarea 1 SDI 115 2015Javiier UmañaAinda não há avaliações

- Practicas RealizadasDocumento28 páginasPracticas RealizadasRaysha Ross Enciso RaveloAinda não há avaliações

- Mux2a1 TutorialDocumento30 páginasMux2a1 TutorialelkillyAinda não há avaliações

- Practica 101 Compuertas Logicas BasicasDocumento4 páginasPractica 101 Compuertas Logicas BasicasPaola VazquezAinda não há avaliações

- Como Programar y Cargar Un Programa en Una Nexys 2 (FPGA)Documento26 páginasComo Programar y Cargar Un Programa en Una Nexys 2 (FPGA)Josue BustamanteAinda não há avaliações

- Tuto - Altera Max PlusDocumento12 páginasTuto - Altera Max PlusCarol SaldarriagaAinda não há avaliações

- Guia Completa Programacion en C/C++Documento47 páginasGuia Completa Programacion en C/C++william erikAinda não há avaliações

- Manual GalaxyDocumento16 páginasManual GalaxyfpalacioguzmanAinda não há avaliações

- Manual Code BlocksDocumento8 páginasManual Code Blocks413x4nd3r0100% (1)

- LAB1 Introduccion Al CodeWarriorDocumento10 páginasLAB1 Introduccion Al CodeWarriorJossue Calvo MedinaAinda não há avaliações

- Práctica # 2 Sentencias Secuenciales VHDL-3Documento12 páginasPráctica # 2 Sentencias Secuenciales VHDL-3NadiaAinda não há avaliações

- Assembler Visual C++Documento12 páginasAssembler Visual C++Francisco Martin VazquezAinda não há avaliações

- Programación de Circuitos Lógicos en VHDLDocumento26 páginasProgramación de Circuitos Lógicos en VHDLCheynAinda não há avaliações

- Sistemas DigitalesDocumento7 páginasSistemas DigitalesKevin ZambranoAinda não há avaliações

- Guía para Diseño Con El MAX PLUS II V PDFDocumento8 páginasGuía para Diseño Con El MAX PLUS II V PDFMarco Agapito VasquezAinda não há avaliações

- Tutorial Vivado: Diseño digital simple con VHDLDocumento23 páginasTutorial Vivado: Diseño digital simple con VHDLDaniela Galvan ChavezAinda não há avaliações

- ME Lab02 - Introducción Al Entorno de XilinxDocumento20 páginasME Lab02 - Introducción Al Entorno de XilinxDIONEL ROPERO TORRESAinda não há avaliações

- 03 - Lab Intro Quartus Con IntroDocumento9 páginas03 - Lab Intro Quartus Con IntroDaniel ToroAinda não há avaliações

- Manual Sobre El Entorno Visual de DEV C++Documento50 páginasManual Sobre El Entorno Visual de DEV C++Cesar MenaAinda não há avaliações

- Instalación y uso básico de la librería gráfica winbgim con Dev CDocumento3 páginasInstalación y uso básico de la librería gráfica winbgim con Dev CJassael PereiraAinda não há avaliações

- Vivado - Tutorial Esp PDFDocumento22 páginasVivado - Tutorial Esp PDFGenesis RosarioAinda não há avaliações

- Guía para Utilizar El CodeBlockDocumento8 páginasGuía para Utilizar El CodeBlockcarlosAinda não há avaliações

- Ejercicio Practico 1 Sobre C++Documento10 páginasEjercicio Practico 1 Sobre C++CharbelMesaAinda não há avaliações

- Tarea 1 SDI-SDUDocumento18 páginasTarea 1 SDI-SDUEdwin Rafael Quintanilla GuillénAinda não há avaliações

- Electrónica Analógica II - Respuesta en Frecuencia - 2012Documento60 páginasElectrónica Analógica II - Respuesta en Frecuencia - 2012Guillermo QuinterosAinda não há avaliações

- Simetria ComplementariaDocumento14 páginasSimetria ComplementariaJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Reglamento Convocatoria 2020Documento10 páginasReglamento Convocatoria 2020Nadia SalattinoAinda não há avaliações

- HyST 7 (Incendio) PDFDocumento106 páginasHyST 7 (Incendio) PDFJose Ignacio Gonzalez BeltramoAinda não há avaliações

- TP6 EaiiDocumento3 páginasTP6 EaiiJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Analisis Rectificador Semicontrolado MonofásicoDocumento9 páginasAnalisis Rectificador Semicontrolado MonofásicoJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Guía TPLab. #7Documento2 páginasGuía TPLab. #7Jose Ignacio Gonzalez BeltramoAinda não há avaliações

- TP3 EaiiDocumento2 páginasTP3 EaiiJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Trabajo Practico 4Documento2 páginasTrabajo Practico 4Jose Ignacio Gonzalez BeltramoAinda não há avaliações

- Práctico Polarización BJT para Máxima Excursión SimétricaDocumento1 páginaPráctico Polarización BJT para Máxima Excursión SimétricaJose Ignacio Gonzalez BeltramoAinda não há avaliações

- HyST 6 (Carga Termica) PDFDocumento35 páginasHyST 6 (Carga Termica) PDFJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Bases para La Convocatoria Bevc 2018Documento2 páginasBases para La Convocatoria Bevc 2018Hachi TresjolieAinda não há avaliações

- Clase 7 - Procedimiento de Rectificación ControladaDocumento15 páginasClase 7 - Procedimiento de Rectificación ControladaJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Gobierno Del SCRDocumento13 páginasGobierno Del SCRDavid CoronadoAinda não há avaliações

- Teorico de Osciladores Con AODocumento10 páginasTeorico de Osciladores Con AOJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Practico Seleccion SCRDocumento28 páginasPractico Seleccion SCRJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Producción de Una Balanza ComercialDocumento8 páginasProducción de Una Balanza ComercialJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Clase 7 - Rectificación ControladaDocumento42 páginasClase 7 - Rectificación ControladaJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Introduccion Arquiterctura ARMDocumento60 páginasIntroduccion Arquiterctura ARMJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Optativa Arquitecturas de ComputadorasDocumento7 páginasOptativa Arquitecturas de ComputadorasJose Ignacio Gonzalez BeltramoAinda não há avaliações

- DFT y convolución circularDocumento27 páginasDFT y convolución circularJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Sistemas de Control DigitalDocumento19 páginasSistemas de Control DigitalJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Sistemas No Lineales PT 1Documento18 páginasSistemas No Lineales PT 1Jose Ignacio Gonzalez BeltramoAinda não há avaliações

- Sistema de Control Digital Capitulo1Documento13 páginasSistema de Control Digital Capitulo1Jose Ignacio Gonzalez BeltramoAinda não há avaliações

- Material Clases SCIIDocumento16 páginasMaterial Clases SCIIJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Familia Lógica CMOS - Sergio NoriegaDocumento134 páginasFamilia Lógica CMOS - Sergio NoriegaHenry Jonathan Perez Valdez67% (3)

- Monografia EMIDocumento6 páginasMonografia EMIJose Ignacio Gonzalez BeltramoAinda não há avaliações

- Kakuan - Diez TorosDocumento10 páginasKakuan - Diez TorosnidiarosarioAinda não há avaliações

- Manual de Electrónica DigitalDocumento11 páginasManual de Electrónica Digitalmckenzy99Ainda não há avaliações

- Tecnología de NubeDocumento2 páginasTecnología de NubeAlexandra CruzAinda não há avaliações

- Métodos constructores y destructores en POODocumento12 páginasMétodos constructores y destructores en POODANIELA ALEXANDRA EMBUS GAVIRIAAinda não há avaliações

- Manual WPFDocumento6 páginasManual WPFOrlando HernándezAinda não há avaliações

- Instalar Jenkins Desde CerosDocumento23 páginasInstalar Jenkins Desde CerosHervin CamargoAinda não há avaliações

- Metodología Orientado A ObjetosDocumento2 páginasMetodología Orientado A ObjetosPaola Andrea GarciaAinda não há avaliações

- Algoritmos y su representación mediante diagramas de flujo y pseudocódigoDocumento44 páginasAlgoritmos y su representación mediante diagramas de flujo y pseudocódigoAzrael DomínguezAinda não há avaliações

- Landing PreseaERP NeuralSoftDocumento4 páginasLanding PreseaERP NeuralSoftask mingAinda não há avaliações

- Ejercicio 3Documento4 páginasEjercicio 3RicardoAinda não há avaliações

- 1 Linux AngelDocumento42 páginas1 Linux AngelManu SantanderAinda não há avaliações

- Pilares de La Programación Orientada A Objetos PDFDocumento2 páginasPilares de La Programación Orientada A Objetos PDFSh4Dow1100% (1)

- Kit ODBC funciones avanzadasDocumento373 páginasKit ODBC funciones avanzadasLuckJjasAinda não há avaliações

- Mop de Trabajos 08-09-2021-Icr-Peru-SaDocumento4 páginasMop de Trabajos 08-09-2021-Icr-Peru-SaRon LrcAinda não há avaliações

- Estructuras de ControlDocumento24 páginasEstructuras de ControlVanessaAinda não há avaliações

- Algoritmo en La Vida Cotidiana Se Emplean Algoritmos Frecuentemente para Resolver Algunos Ejemplos Son Los Manuales de Usuario Que Muestran AlgoritmosDocumento3 páginasAlgoritmo en La Vida Cotidiana Se Emplean Algoritmos Frecuentemente para Resolver Algunos Ejemplos Son Los Manuales de Usuario Que Muestran Algoritmosjhonatan paternina rojasAinda não há avaliações

- Guia - de - Taller - Configuración - Hmi - DeltaDocumento12 páginasGuia - de - Taller - Configuración - Hmi - Deltafelipoe sandovalAinda não há avaliações

- CURSO BASICO CSharpDocumento28 páginasCURSO BASICO CSharpIJ3ffAinda não há avaliações

- BPRG U2 A2 JobgDocumento3 páginasBPRG U2 A2 JobgYhoss Zahyd Badillo RomeroAinda não há avaliações

- Lenguaje de Programacion IV Power Builder IDocumento71 páginasLenguaje de Programacion IV Power Builder IJeyson MendozaAinda não há avaliações

- Listas EnlazadasDocumento29 páginasListas EnlazadasDon TitoAinda não há avaliações

- TPW S03Documento23 páginasTPW S03ginahuertascamachoAinda não há avaliações

- Ejercicio Numero #13 AlgoritmosDocumento4 páginasEjercicio Numero #13 AlgoritmosVanessa MesaAinda não há avaliações

- Informatica Basica 2022Documento2 páginasInformatica Basica 2022Amir Ormeño100% (2)

- Justificacion Ingenieria Informatica UCADocumento2 páginasJustificacion Ingenieria Informatica UCAAlex CruzAinda não há avaliações

- Tema 4Documento20 páginasTema 4sergio albarranAinda não há avaliações

- Alvaro Figueroa Tarea6Documento13 páginasAlvaro Figueroa Tarea6Alvaro Figueroa60% (5)

- Tipode Sistemas OperativosDocumento6 páginasTipode Sistemas OperativosVázquez Martínez MichelleAinda não há avaliações

- Proyecto Modelamiento FinancieraDocumento30 páginasProyecto Modelamiento FinancieraHugo OréAinda não há avaliações

- Taller de Subconsultas en SQL - 1.2Documento2 páginasTaller de Subconsultas en SQL - 1.2lady-morenoAinda não há avaliações

- Curso Big Data (Tema 1)Documento32 páginasCurso Big Data (Tema 1)CORAL ALONSO JIMÉNEZAinda não há avaliações

- Interface Gráfica de ExcelDocumento17 páginasInterface Gráfica de ExcelCielo Guerra100% (1)

- Influencia. La psicología de la persuasiónNo EverandInfluencia. La psicología de la persuasiónNota: 4.5 de 5 estrelas4.5/5 (14)

- El trading online de una forma sencilla: Cómo convertirse en un inversionista online y descubrir las bases para lograr un trading de éxitoNo EverandEl trading online de una forma sencilla: Cómo convertirse en un inversionista online y descubrir las bases para lograr un trading de éxitoNota: 4 de 5 estrelas4/5 (30)

- Auditoría de seguridad informática: Curso prácticoNo EverandAuditoría de seguridad informática: Curso prácticoNota: 5 de 5 estrelas5/5 (1)

- Clics contra la humanidad: Libertad y resistencia en la era de la distracción tecnológicaNo EverandClics contra la humanidad: Libertad y resistencia en la era de la distracción tecnológicaNota: 4.5 de 5 estrelas4.5/5 (116)

- Investigación de operaciones: Conceptos fundamentalesNo EverandInvestigación de operaciones: Conceptos fundamentalesNota: 4.5 de 5 estrelas4.5/5 (2)

- ¿Cómo piensan las máquinas?: Inteligencia artificial para humanosNo Everand¿Cómo piensan las máquinas?: Inteligencia artificial para humanosNota: 5 de 5 estrelas5/5 (1)

- Excel para principiantes: Aprenda a utilizar Excel 2016, incluyendo una introducción a fórmulas, funciones, gráficos, cuadros, macros, modelado, informes, estadísticas, Excel Power Query y másNo EverandExcel para principiantes: Aprenda a utilizar Excel 2016, incluyendo una introducción a fórmulas, funciones, gráficos, cuadros, macros, modelado, informes, estadísticas, Excel Power Query y másNota: 2.5 de 5 estrelas2.5/5 (3)

- Estructuras de Datos Básicas: Programación orientada a objetos con JavaNo EverandEstructuras de Datos Básicas: Programación orientada a objetos con JavaNota: 5 de 5 estrelas5/5 (1)

- ChatGPT Ganar Dinero Desde Casa Nunca fue tan Fácil Las 7 mejores fuentes de ingresos pasivos con Inteligencia Artificial (IA): libros, redes sociales, marketing digital, programación...No EverandChatGPT Ganar Dinero Desde Casa Nunca fue tan Fácil Las 7 mejores fuentes de ingresos pasivos con Inteligencia Artificial (IA): libros, redes sociales, marketing digital, programación...Nota: 5 de 5 estrelas5/5 (4)

- Inteligencia artificial: Lo que usted necesita saber sobre el aprendizaje automático, robótica, aprendizaje profundo, Internet de las cosas, redes neuronales, y nuestro futuroNo EverandInteligencia artificial: Lo que usted necesita saber sobre el aprendizaje automático, robótica, aprendizaje profundo, Internet de las cosas, redes neuronales, y nuestro futuroNota: 4 de 5 estrelas4/5 (1)

- Reparar (casi) cualquier cosa: Cómo ajustar los objetos de uso cotidiano con la electrónica y la impresora 3DNo EverandReparar (casi) cualquier cosa: Cómo ajustar los objetos de uso cotidiano con la electrónica y la impresora 3DNota: 5 de 5 estrelas5/5 (6)

- EL PLAN DE MARKETING EN 4 PASOS. Estrategias y pasos clave para redactar un plan de marketing eficaz.No EverandEL PLAN DE MARKETING EN 4 PASOS. Estrategias y pasos clave para redactar un plan de marketing eficaz.Nota: 4 de 5 estrelas4/5 (51)

- La biblia del e-commerce: Los secretos de la venta online. Más de mil ideas para vender por internetNo EverandLa biblia del e-commerce: Los secretos de la venta online. Más de mil ideas para vender por internetNota: 5 de 5 estrelas5/5 (7)

- Gestión de Proyectos con Microsoft Project 2013: Software de gestión de proyectosNo EverandGestión de Proyectos con Microsoft Project 2013: Software de gestión de proyectosNota: 5 de 5 estrelas5/5 (3)

- AngularJS: Conviértete en el profesional que las compañías de software necesitan.No EverandAngularJS: Conviértete en el profesional que las compañías de software necesitan.Nota: 3.5 de 5 estrelas3.5/5 (3)

- Manual Técnico del Automóvil - Diccionario Ilustrado de las Nuevas TecnologíasNo EverandManual Técnico del Automóvil - Diccionario Ilustrado de las Nuevas TecnologíasNota: 4.5 de 5 estrelas4.5/5 (14)

- LAS VELAS JAPONESAS DE UNA FORMA SENCILLA. La guía de introducción a las velas japonesas y a las estrategias de análisis técnico más eficaces.No EverandLAS VELAS JAPONESAS DE UNA FORMA SENCILLA. La guía de introducción a las velas japonesas y a las estrategias de análisis técnico más eficaces.Nota: 4.5 de 5 estrelas4.5/5 (54)

- Lean Seis Sigma: La guía definitiva sobre Lean Seis Sigma, Lean Enterprise y Lean Manufacturing, con herramientas para incrementar la eficiencia y la satisfacción del clienteNo EverandLean Seis Sigma: La guía definitiva sobre Lean Seis Sigma, Lean Enterprise y Lean Manufacturing, con herramientas para incrementar la eficiencia y la satisfacción del clienteNota: 4.5 de 5 estrelas4.5/5 (5)

- Guía De Hacking De Computadora Para Principiantes: Cómo Hackear Una Red Inalámbrica Seguridad Básica Y Pruebas De Penetración Kali Linux Su Primer HackNo EverandGuía De Hacking De Computadora Para Principiantes: Cómo Hackear Una Red Inalámbrica Seguridad Básica Y Pruebas De Penetración Kali Linux Su Primer HackAinda não há avaliações