Escolar Documentos

Profissional Documentos

Cultura Documentos

025

Enviado por

Fernando Santos0 notas0% acharam este documento útil (0 voto)

3 visualizações8 páginasLeite de arquitetura 25/25

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

PDF ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoLeite de arquitetura 25/25

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

3 visualizações8 páginas025

Enviado por

Fernando SantosLeite de arquitetura 25/25

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF ou leia online no Scribd

Você está na página 1de 8

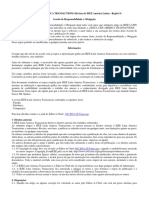

LUNIVERSIDADE FEDERAL DE CAMPINA GRANDE

- CENTRO DE CIENCIAS E TECNOLOGIA

DEPARTAMENTO DE ENGENHARIA ELETRICA

DISCIPLINA: ARQUITETURA DE SISTEMAS DIGITAIS (2013.1) Data: 09/07/2013

Alunola),_ sagen Matricula:

1 Avallagdo Escolar &

1. Um verificador tem como entradas dois sinais (R) e Ack (A), que tem yrecer segundo a ordem vista na

figura sbaho.O cut poz ums sale En (Euan aden for egulia €-0be slguma trans estve fre

de ordem E torna-se 1 e fica assim até que ocorra un jue os passos abaixo: (3.0)

a) Desenhe o diagrama de estados cy

b) Defina e informe o significado de

cada estado; Rg

.)indque o estado nica Tt .

‘)Calouleonimerominimodebts A _ AiO."

para codificarlo dos estads; i

@) Escolha e Informe uma Err

codificaréo para osestados. 0) Ca

2. Escreva uma descriglo em Verilog de um circuito de Uma calculadora simples como mostrado na figura abaixo. €

ddado 0 decodificador de sete segmentos dec7seg{input [3:0] in, output [0:6] out). Os registradores deslocam para a

‘esquerda. Cada digito¢ inserido nas chaves de EO a E9 e um dos clocks (A ou 8) é aplicado. G0)

a

_ ase Registradorde Lap pec |.

By tes} Deslocamento | - 708

zm 4x4 its 3K apoE]

E47] Codificador 3309

EST] Decimal somador| 4 Fa

feo] bits IG bits sb

a rt

a a [bec

8 ish

3. Acrescenta a CPU em estudo a instrucio Load PC (LDPC), que realiza a microoperago RIDR]¢-PC, modificando

apenas a unidade de controle. Escolha e indique um Opcode para esta instruco. Desenhe as altera¢des e explique a

operacéo. ® * (2.0)

4. Simule o resultado da execusdo da seguinte sequéncia de instrugdes na CPU lem estudo (original) sabendo que ©

Feglstrado RO possul o codigo ASCI da primeira letra (maliscula) de seu nome, conformeatabela aba. (2.0)

Gifo[ A,B c]o|e| Fi G/H|il[i[x[ut[m[WlolrPlalris ulviw[x[y[z

Dee [6s] 66] 67| a] 69| 70] 71] 72| 73] 74] 75| 76| 77| 78 73] 20| ax] e2| e3| e4| 8586] 87] 95/89] 90,

Hexa [41] 42[ 43] 44] 45| 46] 47] 48] 49] 4a] 48] 4c] 20] ae ar s0/ 51| 52] 53] 54] 55] 56] 57] 58] 59| 5A

instru Tegitrador ou meméria modiiada

TADIR2RG,S x Ea

SHR RS, RO

OR 2, RO, 2

DIRS, 4

STRS, A

OR RS, RRO

Universidade Federal de Campina Grande~ UFCG

Departamento de Engenharia Elétrica ~ DEE

Arquiteturas de Sistemas Digitals~ 2011.2

Data: 01/04/2011

Aluno: Matricula

PRIMEIRA AVALIACAO ESCOLAR

4. Descreva em Verilog um circuito que aceite um nero n e produza como sais 0 enésimo nimero de Fibonacci

‘apés alguns pulsos de clock. Este circulto possu uma entrada n de 5 bits, uma entrada de clock, uma entrada de reset

assincrono, uma saida de valarvilido, val, e uma salda fb de 16 bits. O enésimo nimero de Fibonacci, Fib(n) €a soma

{dos niimeros de Fibonacci pars (n-1) (0-2), ou sejaFib(n) = Fib{n-1) + Flb(n-2), sendo Fib(0) = 0 eFib(1) = 1, O maior

~alor de entrada possivel serd n=24, cua saida correspondente Fib(24) = 46.368. Apds 0 calculo do nlmero o sinal val

deve fcarativo por um ciclo de clock. O seguinte cédigo em linguagem C realiza este sigoritmo: (2.5)

tat ib tant ar

(

int i, tmps0, atua

0, anter:

for (4 = 0; deny 144) (

tmp = atual;

atual = anter + atualy —// atual <- atual + anterior

anter = tmp; 1) entexior <- atual

}

return atual;

»

2, Projete e descreva em Verilog uma mégulna de estados com uma entradz Din e uma saida Val A sada Vol (NAA)

deve indicar a acorréncia da seguinte sequéncia de fatos: Ocorreu uma borda negativa na entrada Din (valor 1 em uma

borda de clock e valar 0 na borda seguinte); Apés isso, Din pode ter qualquer valor nas préximas 6 bordas de clack e

{deve ter valor 0 em pelo menos 2 das 3 bordas seguintes, A salda Val entio terd seu valor setado durante um pulso de

clock e resetado no pulso seguinte. APs Is0 0 sistema deve votar a esperar nova sequéncia (2.5)

Modifique a implementago éa Instrugso LO! (Load Immediate) no processador em estudo, de forma que possa

Utizar constantes de 11 bits em complemento de 2. O edciga da instrugsa seré formado par um Opcode de 2 bits (ot

15 = 1e bit 14 = 0}, O valor da constante serd formado pelos demais bits, excivindo os 3 bits que determinam ©

registrador de destino (campo DR, bits 8 2 6). As ateragies devem ser feltas apenas na Unidade de Controle. Ou seja,

‘no modifique a Unidade Funcional nem o Banco de Reglstradores. Desenhe 0 circuito com as alteragbes. As figuras

com a CPU e os detalhes da unidade de controle e das Instrugdes esto em anexo, Indique a falxa de valores que

rpodem ser obtidos. Outra instcugdo tera que ser retrada do processador. Qual? Explique. Mostre em uma links de

Verilog coma o valor da constante &calculado a partir do valor dos bits de I (cédigo da instrucéo}. (2.5)

@Projete uma sequéncia de instrugBes para o processador em estudo que coloque o valor ASCII da primeira letra de

eu primeiro nome (erm maldscula) nos & bits menos significativos da posi¢do de meméria 10 (decimal). Simule

‘manualmente a execugio desta sequéncia, indicando o valor dos regstradores alterades, Esta CPU possui palavra de

so bits. (25)

Tabela Asc

aio [Al 8[c[o[e[r[s]a[ i]s] x[ tlm Nol e

[ee J si-66| 67 | 68| 69| 70] 71] 72| 73] 74] 75| 76] 77| 78] 79] 80

(Tex:fi pea [43] 44] 45 [a5] 47] 48 | 49 [en] aa] 4c] 40] ae] 4F| 50]

ST Tuy wy xyz

3] 86) 85 86) 87] 88] 89] 90

53/54) 55| 56) 57| 58] 59] sal

Figuras:

a S=

i AT

oo Rota

|b ea}

TTT Bf

LLL ] |OU,

See DTT | Pee]

corset eh LE

Mave a, cok? MOVA RD.RA — RIDR|- RISA" NZ —_ inns

a ee ae

‘Suberact Goud SUB RD.RA, AB RIDR]— RiSAl~ Rist NZ Fear .

ccm a ae ROEM MORRIS aRALcAO RE es

sont Se ae SE au

Soon ae OO eke en neta att

Senrvon Garth he MARARMERIC RECARO RE Leer

liege “Ue ens oe ame reels

Sih RSI Mer, noes mal” eget ae

SS ca RE ea a att

site sane aie aaa Brae ton

Aca "TE Ant TRA ap RTE Bor cat Frass ate

Lond wires LD RDLRA’ RIOR] MaSAP faa —

‘Stoee 1eKN00 ST RARB MISA} e RISB) pre te

rmchon Zoo MDW BRZ RAAB MRA] Ree PCascanl NZ Fee uni

cece) Poses ae

voor ant nano ARMICRC pea Ue

feeenrse sy

nan ade eae

nm ES ww eee —

Funcionaeitopeatinewing —@ 0X 8 Pw RK | Te eS ~

oor, = [se

‘Pimetion-usit operations 1eGn 13 t ae x —_ vias | donee | Sima

‘ager and consaat eee wwe

Gnamavmamme) 11 00 XX 0 0100

eco s t st a S| ,

Universidade Federal de Campina Grande ~ UFCG

Departamento de Engenharia Elétrica~ DEE

‘Arquiteturas de Sistemas Dgitais~ 2021.1

Data: 01/04/2081

‘Aluno: Matrcule:

PRIMEIRA AVALIAGAO ESCOLAR

4. besereva em Verog um ercuito que acelte um nmero ne preduza como saids 0 enésimo nimero de Fibonace

apes clgune pulos de dock. Este cco possi uma entrada nde 5 bits, uma entrada de clock, ume eneraca Se rose

agin foe sida de valor vido, vale uma sida fit de 16 bis, O enésimo nimere de Flbonacc Fb) ¢= some

ances de Fibonacl pare (v2) (n-2}, ou sea Fib(n)= iba} + Fib(n2),sendo Fb(0) = 0 Flb() = 2-0 melon

see ie cntrada possvel seré 22, cu saldacorrespondente Fib(2A) = 4,368. Apés 0 célculo do ndmero osinal vo!

Jove fearativ por um cielo de clock. © seguinte cigo em linguagem Creallza este algoitmo: (25)

int fibtint a)

(

int 4, tmp=0, atual=0, ante:

for (i = 07 deny iH)

emp = atuals

Staal - anter + atualy // atual <- atual + anterior

lex = tmp; 7) anterior < atual

return atuals

d Pa

2. rojete edescreva em Verilog uma maquina de estatos com uma entrada Dine uma sida Vol. Asada Val (NAA)

aero reara ocorrenca da segulnte sequéncia de fatos: Ocorreu uma bordanegativana entrada Din (valor 1 er wna

aoe nye clock e valor Ona borda seguinte); Ap6S iso, Din pode ter qualquer valor nas préximas 6 bordas de cock ©

aor ae er em pelo menos 2 das 3 bordasseguintes. A sida Vol eno tré sev valor setad durante um puko de

ceric rosetado no pulsa seguinte, Apés iso 0istema deve voltar a esperar nova sequéncia. (25)

Moslique a implementacdo da instrugso LD (Load Immediate) no processador em estudo, de forms au Port

Bio ied 11 bite em complemento de 2.0 cédig da instrugto seré formado por um Opcode de 2 bis (bt

sane corn dO), valor de constante serd formado pelos demas bits, exuindo os 3 bits aue determina ©

‘Rajrador de destin (ampo OR, bits 836) AsltergBes devem ser feitas apenas na Unidade de Controle, OF sy

orsitque a Unidade Funcional nem o Banco de Repstradores, Desenhe o cirauto com as alteravies, As fiwras

rae arp Ue os detalhes da unidade de controle e das Instrugbes estBo em anexo.indique a fava de valores cue

Sete ser abides. Outro insrugdo teré que ser retrada do processador Qual? Exslique, Mestre em wna linha de

Verilog come ovaler da constant écalculado a partir dovalr dos bits de IR (digo da instrusdo}. (25)

projete uma sequéncia de instrugbes para 0 processador em estudo que coloque valor ASC da primetra letra de

SO senire nome {em maidsculo) nos & bits menos significaivos da posilo de memério 10 (decimal Simute

se ertmente 9 execurdo desta sequéncia indicando o valor dos registradores alterados. Esta CPU possulpolava de

6 bits. (25)

Tabela Asai

aerate eTo LET ep ayes e(emnyole paral str futviwh xt 2

Dec au eo 70] 7a 7273 [74] 75] 76] 77| 78 79 | ws |w2| Bs | 2a] 85 | 86] @7| 88] 89| 90

$6.

Peeters as aa] as| 46|47| 48) 09[ an] a8) 2c| 40 | 2e] aF[ 0[ 51] 52| 53 [se] 85] 56/5756] 52158

UNIVERSIDADE FEDERAL DE CAMPINA GRANDE OK

CENTRO DE CIENCIAS E TECNOLOGIA

DEPARTAMENTO DE ENGENHARIA ELETRICA

DISCIPLINA: ARQUITETURA DE SISTEMAS DIGITAIS {2013.1) Data: 09/07/2013

Aluno(a) Maticula

| i i Ee i a

d 42 AvaliacSo Escolar

2 Um verfcador tem como entradas dos sinais Req (R)e Ack (A), que tem que aparecer segundo a ordem vste ne

figura abaxo. O cireuito possul uma saida Err (E). Enquanto a ordem for seguida E=0. Se alguma transieao estver fora

Gcordem € tona-se.e fica asim até que ocorra Um resetassincrono na entrada RESET, Efetue os pose0s abeine, (2, 0)

a) Desenhe odiagrama deestados; cy

b)einaelnonneo aentitece f

ductor a er oh!

Sj indquee edo inc

d) Calcule o ndmero minimo de bits A 8 4

par tee toc ae = a

) Escolha informe uma Ef ;

codificagdo para os estados,

crea umn desr;do om Verilog de um crelto de uma calelaora simples coma mostrado na flgusakno. €

Sado o decoiicadr de sete sepmentosdcreoglnput [0m euput [0] eur). Onregtaore decor Pee

‘esquerda. Cada digit ¢ inserido nas chaves de £0 a ES’ um dos clocks (A ou 8) é aplicado. =(3.0)

A, * a

Lf CAS pepistrador de afer]!

7 BY Rexel Destocamento Zea | e,

By rt aca bs Oe afpeis 113

el wees pel Lee

: EE] abits Alpe |. 5

oot EE Registradorde pee 3

' sy ReseY —eslocamento Af Der]

cue 4x4 bits Liseg |™ ©

a fa fa a é

2 Acreseenta a CPU em estudo a instruglo Load PC (LDPC), que reliza a microoperagSo RIDRIC-PC, modificando

speras 2 nidade de controle Escolha e indique um Opeade para esta instrugSo, Desenhe as ateragBes e explque

operacdo, (20)

4 Smuleo resutado da execusdo da segunte sequéncia de instufes na CPU em estudo (original) sabendo que 0

reaistrado RO poss océdigo ASC! da primeira letra (maiiscula) de seu nome, conforme atabelaabaixo, (20)

+ x

Dec 165! 66| 67{ 68] ¢9[ 70] 74{ 72] 73] 74] 75] 76| 77] 78] 79] a0] et] aa| 83|84| a5] a6] 871 wel do

ss eiatatal laa aatela alee

20

teva |41| 42] 43| 40] 45] 46|47| 48] 49 aal 4B] 4c] 40] se ar [50[ Si] 52] 55] sal Sef Se] 57 s6[ oe

[nseeio ——[Reiertersonentemomicam ———py

AOI, RO 3 4

SH RS, Ro

Fon 2, Ro, Ra aoe

oie LCSTRegiIgDIS An :

STRS, R2 MCT 0100 (144

[eon ts. 3.R0 [prey ety tee ‘

9/040

gan = 04 0077

Figuras:

LOAD

Opcop

ie a

t

tt

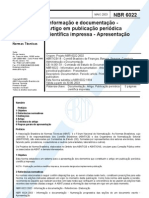

Mamcton ope ie Fmat__ Deseret =

Moved iin woes BORA Male a

Tucrmest ——maOL INC RDLRA IDR] =RISA} =

Aah “66E0)0) ADD RDRA.RE RIDR|+ RISA! + RIS) 000.

Sabet xoIo1 SUR RDLRA.RI RIDR| RISA” RSH" oo

Decrement OWOHIP DEC RD.RA RIDRIRISA|= I" ono

AND UIE AND RDURALRE RIDR}C RISA} RISO) no

on niin: OF -—RORALKE RIOR} RISA RSH

EhsieOR UNIO KOR RO-RALRG RIOR] = RSA) 8S 0100

Not an Nor, AO.RS Apa Ba uot

Nowe oociieo MOVE RDRB IDR RSH" '

Shite OWIET SHR” ROVRD—RIDRc=eR(sOy ono

Shite bono SAL RDARBRIDRI-Ma RSH. ou

Sigaiemegan feu Lot RDO 4 ON AOR 1000

‘Aa tamedate [}9fO10 ADI RO. RA.GP RIOR] RISA 2 ee

tet mito LD -RD-RA” RI MISAT

Sire Sumo st Rens Seale nba oo

BranenonZero OMI BRE RAAD —I{RIGAI=O)PCH PCs sD. NZ i011

inisa|og ec eco 00

Baanchoe 1100 BRN RA,AD—HERISAI

Você também pode gostar

- TCC Ufcs para ApreDocumento74 páginasTCC Ufcs para ApreFernando SantosAinda não há avaliações

- InversorPowerFlex 20Documento1 páginaInversorPowerFlex 20Fernando SantosAinda não há avaliações

- Projeto 3Documento1 páginaProjeto 3Fernando SantosAinda não há avaliações

- Monitoração E Diagnósticos de Pára-Raios A ZnoDocumento7 páginasMonitoração E Diagnósticos de Pára-Raios A ZnoRamón MirelesAinda não há avaliações

- IEEE RegrasDocumento5 páginasIEEE RegrasFernando SantosAinda não há avaliações

- TFC Viol PDFDocumento78 páginasTFC Viol PDFFernando SantosAinda não há avaliações

- Sistemas de medição remota de energia elétrica: comparação entre WebEnergy e HemeraDocumento68 páginasSistemas de medição remota de energia elétrica: comparação entre WebEnergy e HemeraFernando SantosAinda não há avaliações

- PE - Fachada (Pontalete) PDFDocumento2 páginasPE - Fachada (Pontalete) PDFFernando SantosAinda não há avaliações

- Eletr Pot1 22Documento25 páginasEletr Pot1 22Bruno GiffoniAinda não há avaliações

- ASD 2017.2 - 1o EstagioDocumento2 páginasASD 2017.2 - 1o EstagioFernando SantosAinda não há avaliações

- Eletr Pot1 25Documento24 páginasEletr Pot1 25Daniel Gonçalves AraujoAinda não há avaliações

- 06Documento10 páginas06Fernando SantosAinda não há avaliações

- 09Documento4 páginas09Fernando SantosAinda não há avaliações

- Slides Material ArquiteturaDocumento7 páginasSlides Material ArquiteturaFernando SantosAinda não há avaliações

- NBR 6022 ArtigoDocumento5 páginasNBR 6022 ArtigoAndréAinda não há avaliações

- NDU 009 - Critérios para Compartilhamento de Infra-Estrutura Da Rede Elétrica de DistribuiçãoDocumento55 páginasNDU 009 - Critérios para Compartilhamento de Infra-Estrutura Da Rede Elétrica de DistribuiçãoFernando Santos100% (1)

- ElepotDocumento163 páginasElepotFernando SantosAinda não há avaliações

- NDU 013 - Critérios para A Conexão de Acessantes de GD Ao Sistema de Distribuição Da Energisa - Conexão em BT V3Documento74 páginasNDU 013 - Critérios para A Conexão de Acessantes de GD Ao Sistema de Distribuição Da Energisa - Conexão em BT V3Fernando Santos100% (1)

- Lista Exercicios Aula2 Rev CircDocumento2 páginasLista Exercicios Aula2 Rev CircFernando SantosAinda não há avaliações

- Avaliação Do Desempenho de Isoladores Quanto À RadiointerferênciaDocumento6 páginasAvaliação Do Desempenho de Isoladores Quanto À RadiointerferênciaFernando SantosAinda não há avaliações

- Ndu 004Documento1 páginaNdu 004Fernando SantosAinda não há avaliações

- Queda de TensãoDocumento1 páginaQueda de TensãoFernando SantosAinda não há avaliações

- Respostas Da Lista 2Documento5 páginasRespostas Da Lista 2Fernando SantosAinda não há avaliações

- 024Documento6 páginas024Fernando SantosAinda não há avaliações

- Antenna Measurement TheoryDocumento21 páginasAntenna Measurement Theorybrahmamtech100% (1)

- Caderno WillDocumento16 páginasCaderno WillFernando SantosAinda não há avaliações

- LASD Modulo 0 InstDocumento11 páginasLASD Modulo 0 InstFernando SantosAinda não há avaliações

- Proteção de Sistemas ElétricosDocumento6 páginasProteção de Sistemas ElétricosFernando SantosAinda não há avaliações

- NDU 015 - Critérios para A Conexão de Acessantes G. Ao Sistema de Distribuição Da Energisa - Conexão em MT V3Documento122 páginasNDU 015 - Critérios para A Conexão de Acessantes G. Ao Sistema de Distribuição Da Energisa - Conexão em MT V3Fernando SantosAinda não há avaliações

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5784)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (119)