Escolar Documentos

Profissional Documentos

Cultura Documentos

An 6004

Enviado por

Pedro DominguezDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

An 6004

Enviado por

Pedro DominguezDireitos autorais:

Formatos disponíveis

www.fairchildsemi.

com

Application Note 6004

500W Power-Factor-Corrected (PFC) Converter Design with FAN4810

This application note describes the theory of operation and Selecting the Value of the Bulk Capacitor

step-by-step process to design a high performance Power A major factor affecting bulk capacitor selection is hold up

Factor Corrected (PFC) power supply using the FAN4810 time (Thld). “Hold-up-time” is a time during which output of

controller IC. A complete application circuit is shown in power supply remains in specified range, after interruption of

Figure 10 and an evaluation board using this design is avail- AC power. Energy Jthd stored in the bulk capacitor supplies

able from Fairchild Sales. The evaluation board provides the down-steam converter during power disruption. Voltage

500W at 400VDC and 1.25A, while operating from 90V to across bulk capacitor drops during hold-up time, as capacitor

264VAC line input. discharges. You should calculate the minimum bus voltage

VO_MIN, where output voltage stays in regulation, trans-

Selection of Power Train former properly resets and components stress are inside the

Components derating guidelines.

The FAN4810 can be used in any active PFC pre-regulator 1 2 2

J THD = P O × T HLD J THD = --- ( C × V O – C × V O_MIN )

employing Continuous Conduction Mode (CCM) that has to 2

comply with the IEC 3000-3-2 standard. This section of the 2 × P O × THLD

application note covers calculation parameters and selection C = --------------------------------------

2 2

- (6)

V O – V O_MIN

of pre-regulator power train components: boost inductor,

output capacitor and semiconductors.

Selecting the Value of the Boost Inductor

Setting the Oscillator Frequency

The FAN4810 operates in a continuous conduction code to Resistor R6 and capacitor C18 set the oscillator frequency.

minimize peak current and maximize available power. The Let’s assume a value of C18 = 470 pF. The following equa-

value boost inductance found by setting ∆I, the peak-to- peak tion determines the value of R6

value of high-frequency current, is typically in the area of

20% of the peak value of the maximum line current. 1

R6 = -------------------------------------- (7)

C18 × 0.51 × f S

2P IN PO

I _LINE_PK = ---------------

- (1) P IN = ------ (2)

V MIN η Selecting Parameters of Gain

Modulator Input Circuits

Where I_LINE_PK is a peak value of input current occurred at

The FAN4810 Gain Modulator employs three inputs:

low line, VMIN is RMS value of minimum line voltage, PO is

output power and η is efficiency. Value I_LINE_PK will define

1. A current representing a profile of input voltage.

value of ∆I , where dI is the specified percentage rate.

This current is proportional to the instantaneous value

I_LMAX is the inductor maximum current.

of the input voltage at any given time. This current

programmed by resistor R1, see Fig 1.

∆I = dI × I _LINE_PK (3)

∆I 2. A voltage proportional to the average value of the

I_L MAX = I _LINE_PK + ------

2 line voltage. To obtain this voltage the input voltage is

filtered and scaled. A two-stage filter consists of resis-

Another factor influencing inductor selection is duty cycle D tors R2,R3,R4 and capacitors C2,C3.

and switching frequency fS.

3. Output of voltage error amplifier.

V O – 2V MIN D × 2V MIN

D = ----------------------------------- (4) L = -------------------------------

- (5)

VO f S × ∆I

REV. 1.0.1 10/31/03

AN6004 APPLICATION NOTE

16 1 480

VEAO IEAO

VARIABLE GAIN BLOCK CONSTANT (K)

420

VFB VEA

15 – 360

3.6kΩ IEA

2.5V + +

300

IAC –

2

240

GAIN

VRMS

MODULATOR

4

3.6kΩ 180

ISENSE

3

120

60

Figure 1. Gain Modulator and Voltage Error Amplifier

0

The program resistor for Pin 2 (IAC) current input of the 0 1 2 3 4 5

Gain Modulator is based on the following formula: VRMS(V)

Figure 3. Gain Modulator Transfer Characteristic

2 × V MIN × G MAX × R MO

R1 ≥ -------------------------------------------------------------------- (8)

V GM_OUT_MAX The voltage at Pin 4 sets VRMS and must be well-filtered

and yet able to respond well to transient line voltage

Where GMAX is the maximum gain of the Gain Modulator, changes. A two-stage RC low pass filter consisting of R2,

RMO is the output resistor of Gain Modulator and R3, R4, C3 and C2 as shown in Figure. 2 is selected to meet

VGM_OUT_MAX is the maximum output voltage of the Gain this requirement. The resisitive divider ratio gives an average

Modulator. See the FAN4810 Datasheet for reference. DC voltage of 1.1 volts at Pin 4 at minimum line voltage.

The voltage divider and necessary filters for providing the 2

V AV = --- 2V MIN (9)

scaled value of average input voltage for the Gain Modulator π

Pin 4 (VRMS) input are shown in Figure 2.

Vav is the value of average line voltage and VMIN is the

minimum RMS value of line voltage. Assume R2=R1 and

R3=100k. These values are a common choice for Fairchild

R2 PFC applications.

V AV – V GM_IN_MAX V

GM_IN_MAX

I RD1 = -------------------------------------------------

- - (11)

(10) R4 = -------------------------------

R2 + R3 I RD1

R3

Where VGM_IN_MAX =1.1V and IRD1 is the current flowing

through the divider.

R4 C3

C2 R TOTAL = R2 + R3 + R4 (12)

R TOTAL

C3 = ---------------------------------------------------------------

- (13)

2 × π × f1 × R2 ( R3 + R4 )

R4 × R TOTAL

1 + ---------------------------------

Figure 2. Two-Stage Filter Schematic -

R2 ( R3 + R4 )

C2 = ------------------------------------------------- (14)

This resistive divider ratio should provide 1.1V at the lowest 2 × π × f2 × R4

line voltage. The value of 1.1V is chosen based on the

FAN4810 datasheet and Gain Modulator Transfer Character- Two poles circuits presented in Figure 2 has demonstrated

istic presented in Figure 3. The characteristic curve includes good performance with f1 = 15Hz and f2 = 23Hz.

two segments: the right segment is the area of normal opera-

tion conditions with line voltages from 80VAC to 264VAC

and the left segment is the area of brown-out conditions

where the line voltage drops below 80VAC. Maximum gain

occurs at VRMS(V) =1.1V, see curve in Figure 3. The

VRMS(V) of 1.1V, corresponding to the maximum gain,

defines the criteria selection or resistor divider.

2 REV. 1.0.1 10/31/03

APPLICATION NOTE AN6004

Selection Parameters of Current current and to enhance Total Harmonic Distortion (THD)

Sense Circuit performance when a small boost inductor is used and is

operating in Discontinuous Conduction Mode (DCM) at

A current sense circuit includes a current sense resistor and a light loads.

filter.

1

f_cf = --------------------------------------------- (16)

Selection of Current Sense Resistor 2 × π × R16 × C19

The voltage drop across the current sense resistor should not

exceed the maximum output voltage of the gain modulator, The f_cf filter frequency should be set between fS and fS/6;

whose output is connected to the inverting input of the cur- fS/6 < f_cf < fS.

rent error amplifier. See Figure 5. The non-inverting input of R16 = 100 Ω or less is recommended.

the current error amplifier is connected to the ground and its

inverting input acts as a summing node for summing the Selection Parameters of Current

Gain Modulator output with the negative voltage on the Error Amplifier Compensation

current sense resistor as shown in Figure 4.

Network

V GM_OUT_MAX ∆I The FAN4810 employs two control loops for power factor

- (15)

R5 = ------------------------------------ I_L_ MAX = I_ LINE_PK + ------ correction: a current control loop and a voltage control loop.

I_L_ MAX 2

The current control loop shapes current based on the refer-

ence signal from the IAC Pin 2. The voltage loop stabilizes

Selection of Current Sense Filter output voltage and defines THD balance.

3.5K The output of the Gain Modulator is a current proportional to

– VREF

10 the output of the error amplifier and full sine current IAC on

GND

EAO Pin 2 and is inverse-proportional to the VRMS voltage on Pin

VEAO +

4. Output current of the Gain Modulator generates a voltage

IAC on internal resistor RMO (3.6k). This voltage subtracts from

the voltage on sense resistor R5. The difference between the

resulting voltage on the inverting pin of the current error

Rfilter 3.5K

amplifier and virtual ground on the non-inverting pin gener-

100Ω ISENSE

3 ates an output voltage that is applied to the non-inverting

input of comparator. The ramp signal applied to the inverting

R5 Cfilter input of the comparator controls the output signal on Pin 12.

100nF

For example, if the output voltage is decreasing, the output

of the current error amplifier increases the duty cycle.

Figure 4: Current Sense Amplifier Circuit Increasing the duty cycle will in turn increase the output

voltage, thereby closing the control loop.

The current sense filter is needed to protect the Isense pin

from voltage surges at start-up caused by a high inrush

16 1 13

VEAO IEAO POWER FACTOR CORRECTOR VCC

VCC

TRI-FAULT OVP

VFB VEA 0.5V + 17V VREF

+ 7.5V

15 – 14

3.6kΩ IEA – REFERENCE

2.75V –

2.5V + +

+ S Q

IAC -

2 – -1V +

VRMS GAIN R Q

MODULATOR –

4 PFC OUT

3.6kΩ

ISENSE PFC ILIMIT S Q 12

3

RAMP 1 R Q

7 OSCILLATOR

Figure 5. FAN4810 PFC Block Diagram

REV. 1.0.1 10/31/03 3

AN6004 APPLICATION NOTE

Figure 6 shows a simplified block-diagram of the current fs. To ensure stability of the converter and fast transient

control loop. The PWM block is comprised of a comparator, response, the gain plot of close loop system should intersect

flip-flop and output MOSFET driver. The voltage-controlled the frequency axis at the crossover frequency (fc_cl) with a

voltage source combines input voltage source, rectifier, slope of -20 dB/dec. A type two compensation network is

MOSFET, and boost diode. The current control loop is selected. Assume placement of the zero at fcl_z=0.2*fcl and

closed around the LR5 pole, essentially eliminating the the placement of the pole at fcl_p=10*fcl.

inductor from consideration during voltage control loop

analysis.

V_L Vs

L

R5

Gca Gc_c

D

fcl_z fc_cl fcl_p

Ramp PWM Rmo

Vca 100kHz Gconverter

1kHz 10kHz

Gain Modulator

C7 R12

Rmo

Vref C6

Gpwm_boost

Figure 6. Simplified Diagram of Current Loop

Figure 7. Current Control Loop Bode Plots

Now determine the transfer function between Vs on the For the conditions listed above, an open loop system will

sense resistor and VCA output of the current amplifier or have the following gain at crossover frequency.

transfer function of open loop system. This transfer function

will be a combination of the transfer function of the boost VO × RS

and PWM blocks of the open loop system. G PWM_BOOST = ------------------------------------------------------------------

- (17)

V RAMP × 2 × π × f C_CL × L

The duty cycle, voltage applied to the boost inductor, and the

inductor current are determined by the following expres- The peak-to-peak value of VRAMP is the difference between

sions: the peak voltage and the peak valley values. These parame-

ters are listed in the FAN4810 datasheet.

V CA V_L

D = ------------------ V_L = D × V O I_L = --------------

V RAMP ω×L In Log scale GPWM_BOOST_LG = 20 × log (GPWM_BOOST) (18)

Voltage across the sense resistor is given by: Gain of the current error amplifier at crossover frequency is

found from the following expression.

D × VO × RS V CA × V O × R S

V S = ------------------------------

- = --------------------------------------

-

ω×L V RAMP × ω × L Gpwm_boost_lg

-------------------------------------------

20

Gc_c = 10 (19)

The current loop transfer function is given by the following

expression: This gain ensures that the closed loop Gain plot will inter-

sect the frequency axe on the Bode plots at unity gain.

VS VO × RS VO × RS The current error amplifier is the transconductance amplifier,

- = --------------------------------------

---------- - = ----------------------------------------------------------

V CA V RAMP × ω × L V RAMP × 2 × π × f S × L with the transconductance value of g_ca. Refer to the

FAN4810 Datasheet. The value of R12 can be determined

In this case, the open loop gain of current loop from following operation:

(GPWM_BOOST)is:

Gc_c 1

R12 = ------------ (20) C6 = ------------------------------------------------ (21)

VO × RS g_ca 2 × π × fcl_z × R12

G PWM_BOOST = ----------------------------------------------------------

V RAMP × 2 × π × f S × L

1

C7 = ------------------------------------------------ (22)

2 × π × fcl_p × R12

Figure 7 presents the key bode plots of the current control

loop. The bottom curve is the gain of the PWM-boost section

The values of C6 and C7 can be found based on the zero and

as a function of frequency. The LR pole produces a curve

pole expressions for a type-two compensation network at

with a slope of -20 dB/dec. Fairchild recommends a cross-

frequencies fcl_z and fcl_p.

over frequency defined as 1/10 of the switching frequency,

4 REV. 1.0.1 10/31/03

APPLICATION NOTE AN6004

Selection Parameters of Voltage To prevent increasing the amplitude of third harmonics in the

Error Amplifier Compensation current waveform and to decrease distortion the bandwidth

of the voltage control loop should be kept in a range from 10

Network Hz to 30 Hz. Low bandwidth will minimize the appearance

This section discusses the selection of the voltage divider of second harmonics in the input of the current loop and lim-

and compensation of the voltage error amplifier. ited THD.

Selection of Resistor Divider The main reason for using a low-bandwidth voltage control

loop is due to the phase difference between the waveforms of

16 the input voltage and ripple voltage on the output of PFC, as

VEAO shown in Figure 17. The reactive nature of the PFC load

determines the phase difference. If not attenuated, the ripple

VFB VEA

voltage appears on the input and output of the gain modula-

15 –

tor and the current waveforms can be distorted. Roll-off

2.5V +

capacitor C9 is usually used for second harmonic attenua-

tion. However, too low of a bandwidth of the voltage loop

Figure 8. Resistor Divider can create transient response problems, so some second har-

monic ripple is acceptable. This approach helps to determine

The non-inverting input of the error amplifier connects to a a compromise between THD and transient response require-

2.5V reference voltage as shown in Figure 8. Output of the ments.

voltage divider should set at this voltage level. We are

recommending R8=2.37k, in this case a second resistor R8 Assuming crossover frequency fc_vl= 30 Hz for the voltage

can be found from following formula. loop and location of a zero at fvl_z=3 Hz, we will place a

voltage loop pole at the crossover frequency.

V REF V BUS – V REF

I RD2 = ------------- R7 = ---------------------------------

-

R8 I RD2

Voltage Loop Compensation

Figure 9 shows a simplified block diagram of the voltage

Gea Gea_fc

loop control. This approach is based on the notion that the

voltage control loop can be characterized by the voltage con-

trolled current source feeding output capacitor. We assume Gea_sh

fvl_z fc_vl

that the current loop generates full sine current waveforms 1

that feed capacitor C5 and a resistive load. The voltage error 1 10 100 Gclose_loop

amplifier controls the amplitude of this current and the entire

voltage loop closed around the current loop. In other words,

the voltage controlled current source combined together with Gbst+Gvd

the input voltage source, rectifier, boost inductor, and diode

generates full sine waveforms with a magnitude proportional

to the output of the voltage error amplifier.

Figure 10. Voltage Loop Bode Plots

+ Let’s find the second harmonic voltage ripple (VR_SH) across

C5 bulk capacitor C5.

– R7

R_Load

P IN 1

I IN_AV = -------- (25) Z O_SH = --------------------------------------------------- (26)

VO 2 × π × 2 × f_ln × C5

R8

– VR_SH = IIN_AV × ZO_SH (27) dVEA = VEA_OVH – VEA_OVL (28)

+

R11 Where f_ln is the line frequency, ZO_SH is the impedance of

the bulk capacitor at the second harmonic,VR_SH is the

C9

2.5V

second harmonic ripple voltage, dVEA is the output voltage

C8 range of the voltage error amplifier, VEA_OVH and VEA_OVL

are the voltage error amplifier’s maximum and minimum

output voltages respectively.

Figure 9. Simple Diagram of Voltage Loop

REV. 1.0.1 10/31/03 5

AN6004 APPLICATION NOTE

According to the block diagram in Figure 9, the combined 0.9 × G EA_FC 1

gain of the voltage error amplifier and the resistor divider can - (38)

R11 = ------------------------------- C8 = ----------------------------------------------- (39)

g_ea 2 × π × fvl_z × R11

be shown as:

dV EA × THD This concludes the calculation and selection of power and

G VD_EA = --------------------------------- (29) control components for PFC applications based on the

V R_SH

FAN4810 IC.

Where THD is the total harmonics balance and dVEA is the

output range of the voltage amplifier.

Step-by-step Instructions for

Selecting External Components for

R8

G VD = --------------------- (30)

a PFC Circuit

R7 + R8

A PFC design tool is also available on Fairchild’s web site.

GVD is the voltage divider gain. See www.fairchildsemi.com/xxxx for details.

The following equation shows the gain of the voltage error Example Design of a FAN4810 Controller with

amplifier at the second harmonic. the Following Specifications

Po= 500W Output power

Gvd_ea G EA_SH VMIN = 80 VAC Minimum voltage RMS

G EA_SH = ------------------- Z EA_SH = ------------------

- (31)

Gvd g_va VMAX = 264 VAC Maximum voltage RMS

η = 0.93 Efficiency

GEA_SH and ZEA_SH are error amplifier gain and impedance Vo = 400 VDC Output (bus) voltage nominal value

at second harmonic frequency. g_va is voltage error ampli- VO_MIN= 300 VDC Output (bus) voltage minimal value

fier transconductance. To ensure sufficient roll-off of voltage fS = 100 kHz Switching frequency

gain at second harmonic frequency C9 is found from the THDL = 20 ms Hold-up time

following expression. THD = 5% Total Harmonics Distortion

1

dI_RIPPLE = 20% Ripple current

C9 = -------------------------------------------------------------- (32) f_ln = 60 Hz Line frequency

2 × π × 2 × f_ln × Z EA_SH

FAN4810 specifications

To find the values of R11 and C8, use the same approach

described above in a current loop. The following formula

tD = 500 ns Oscillator dead time

defines gain of the boost section at crossover frequency

VRAMP = 2.5V Oscillator Ramp Valley to Peak

(GBT_FCS).

voltage

1 RMO = 3.6k Gain modulator output resistor

I IN_AV × --------------------------------------------

2 × π × fc_vl × C5 VGM_OUT_MAX = 0.75V Gain modulator output voltage

G BST_FC = ------------------------------------------------------------------- (33)

dV EA Gmax = 2 Gain Modulator maximum gain

VGM_IN_MAX = 1.1 V Gain Modulator input voltage that

A log equivalent of GBT_FCS is: produces maximum gain

VREF_EA = 2.5 V Voltage Error Amplifier reference

GBST_FC_LOG = 20*log(GBST_FC) (34) voltage

VEA_OVH = 6.7V Voltage Error Amplifier maximum

The gain of the voltage divider in log form is shown in equa- output voltage

tion 35. VEA_OVL = 0.1V Voltage Error Amplifier minimum

output voltage

GVD_LOG = 20*log(GVD) (35) g_ea = 65 uS Voltage Error Amplifier

transconductance

The gain of the error amplifier in log form is determined by g_ca = 100 uS Current Error Amplifier

the following expression: transconductance

RGND = 3.6 k Current Error Amplifier termination

GEA_FC_LOG = –(GBST_FC_LOG + GVD_LOG) (36) resistor

VREF = 7.5V Reference voltage

The gain of the error amplifier at cross-over frequency is:

Gea_fc_log

-----------------------------

20

G EA_FC = 10 (37)

6 REV. 1.0.1 10/31/03

APPLICATION NOTE AN6004

Selecting the Power Components Selection Parameters of Current Error

Value of boost inductor L1 calculated based on formulas (1), Amplifier Compensation Network

(2), (3), (4), (5). Let’s set fc_cl = 10.0 kHz, fcl_z = 2.0 kHz, fc_p = 100 kHz.

PIN = 537. 6 W I_LINE_PK = 9.5A dI = 1.9A The value of R12 can be calculated based on (17) – (20).

I_LMAX_PK = 10.45 A D = 0.717 GPWM_BOOST = 0.303, GPWM_BOOST_LG = -10.4, and

Gc_c = 3.3. R12 is determined to be 32.986 k. We will use a

Calculated value of L1 is 426 µH. Value of inductor L1 = 420 standard value of R12 = 33.2 k. The values of C6 and C7 are

µH is selected. determined from (21) and (20). From these equations C6 is

found to be 2.392E-9 F and C7 is found to be 4.79E-11 F.

The value of bulk capacitor C5 is selected based on formula We will use 2.2 nF and 47 pF for C6 and C7, respectively

(6). The calculated value of C5 = 2.857 µF. A standard value

of C5 = 330 µF/450V is selected for the bulk capacitor. Selection Parameters of Voltage Error

Amplifier Compensation Network

The value of the current sense resistor selected is based on

Let’s assume R7 = 2.37 k, R8 is determined by (23, 24).

formula (15). The calculated value is 0.072 Ω. A standard

From equation 23, IRD2 is found to be 1.055E-3 A, R7 is

value R5 = 0.050 Ω is selected for the current sense resistor.

determined to be 3.768E+5 Ω. To reduce the voltage across

Parameters of current sense filter selected based on (16) R17

each resistor, R7 is composed of three resistors of 127 k

= 100 Ω, C19 = 0.047µF. Corner frequency of the filter,

each.

calculated based on (16) is 33.8 kHz, that is inside the

specified range between 16.6 kHz and 100 kHz.

To determine the value of resistor C9, a number of interme-

diate variables should be calculated. Using expressions (25)

The boost diode D1 and switch Q1 are chosen for a voltage

– (32), the following can be calculated:

rating of 500V or greater to withstand safely the 400V boost

potential. Current I_LMAX_PK = 10.45 A is also the peak

GVD_EA = 0.045, GEA_SH = 7.33, ZEA_SH = 11.29E+4 Ω and

current for the boost diode D1 and switch Q1.

C9 = 1.17E-8 F is selected. A standard value of C9 = 0.01 µF

is selected.

It is very difficult to recommend particular semiconductors

for specific applications, because these decisions are usually

To determine the values of R11 and C8 a number of interme-

made based on the unpredictable factors such as customer’s

diate variables should be calculated. Using expressions (33)

inventory, airflow, and size of the heatsink. Refer to Table 1

– (39), the following is calculated: GBST_FC = 4.41,

for recommended MOSFETs, IGBTs and diodes.

GBST_FC_LOG = 12.9, GVD_LOG = -44.2, GEA_FC_LOG =

31.13, GEA_FC = 36.7. R11 = 5.08E+5 and C8 = 1.117E-7 F.

Selecting Control Components Standard values of R11 = 510 k and C8 = 0.1µF are selected.

For setting the oscillator frequency value, R6 is calculated

based on formula (7) and the assumption C18 = 470 pF, PFC Controller Application Tips

yields R6 = 41720 Ω. Let’s select a standard value

FAN4810 start-up takes place when C15 is charged to 13V

R6 = 41.2 k.

through R13 and R14. PFC switching action now boosts the

voltage on C5 to 400V via boost inductor L1. Through aux-

Selecting Parameters of Gain Modulator Input iliary winding of boost inductor L1, the circuit receives a

Circuit regulated 15V from a full wave rectifier that consists of D3,

R1 is based on formula (8). To minimize the voltage rating of D4, C12, and C16. For proper circuit operation, high fre-

each resistor, two 453K resistors in series are selected for quency bypass capacitors are required on Vcc and VREF.

R1. The calculated value of R8 = 1.06 M. Low ESR ceramic or film capacitors are highly recom-

mended. Orderly PFC operation at start-up is guaranteed

Let’s use the same resistors that were selected above for when D2 quick charges C5 to the peak AC line voltage

R2, R2 = 906 k and R3=100 k. R4 can be found using before the boost switch Q1 turned on. This sequence ensures

formulas (9), (10), and (11). Vav = 72.1V, Ird1 = 70.5 µA, the boost inductor current is zero before the PFC action

R4 = 15.67 k. R4 = 15.8 k selected. begins. The regulated voltage on C5 must always be greater

than the peak value of the maxi-mum line voltage delivered

The value of capacitors C3, C2 are calculated based on to the supply.

formulas (12), (13), and (14). Using these formulas

C3 = 1.035E-7 F and C2 = 5.11E-7 F. Standard values The soft start circuit is comprised of components Q4, R16 and

C3 = 0.1 µF and C2 = 0.47 µF are selected. C20. The error amplifier’s output voltage, VEAO, is forced to

follow the charging voltage of C20 by Q4. As C20 charges

toward VREF, Q4 is biased off. The PFC duty cycle is propor-

tional to VEAO, where zero VEAO gives zero duty cycle.

REV. 1.0.1 10/31/03 7

AN6004 APPLICATION NOTE

Circuit Performance

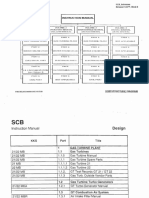

Figure 11 is a complete schematic of this application circuit.

Figures 12 and 13 show the efficiency and THD perfor-

mance. Figure 14 shows input current waveforms. Figures

15-17 show start-up waveforms.

D2 1N5406

D1

TP4 L1 420µH TP1 TP2

ISL9R1560P2

12, 11 7, 8

400VDC

F1 BR1

J1 R7A J3

GBPC2506

127k

AC INPUT C1 R2A

.47µF 453k R7B

R1A 127k

453k R14 R13

R2B 39k 39k R7C

453k 2W 2W TP5 127k

J2 R19 22

Q1

FQA24N50 C5 C4

R1B 330µF .047µF

R5A R3 453k

D6 .025 C3 100k

1N5401 3W .1µF

R8 2.37k

D5 R9 C17

1N4747A 10k 1.0nF

R5B C2

D7 .47µF R4 TP3

1N5401 .025

3W 15.8k

400VDCRTN

TP6 J4

R10 47

D3 RGF1A

R18 10

R15 2N3904 6

0

TP7 C12

Q2

C10 C21 1.0µF L1

1.0µF 1.0µF

C15 5

1500µF

R17 47pF Q3

100 2N3906 C16

1.0µF

C7

R6 R12 33.2k

C6 2.2nF D4

41.2k RGF1A

1 VEAO 16

IEAO

2 IAC FB 15

3 ISENSE 14 Q4

VREF

R16 2N3906

4 VRMS VCC 13

200k

5 CLKSD PFC OUT 12

TP8

6 CLK OUT 11

NC

7 RAMP1 10

GND

C19

8 NC GND 9

.047µF C20

C18 1.0µF

FAN4810 R11

470pF

C13 510k C11

C14 1.0µF C9 1.0µF

1.0µF .01µF

C8

.1µF

D8

MBR052L

Figure 11. Schematic of 500W Power-Factor-Corrected Boost Converter

8 REV. 1.0.1 10/31/03

APPLICATION NOTE AN6004

97 7.5

500 Watt Load

96 7

95

6.5

Efficiency (%)

94

THD (%)

6

93

5.5

92

5

91

90 Efficiency 4.5

THD

89 4

90 110 130 150 170 190 210 230 250

Vline (RMS)

Figure 12. Efficiency and THD Performance vs.

Figure 15. Turn-ON, Vo=405.3V, Io=0.5A

Input Line Voltage

98 18

230 Vrms Line Voltage

96

16

94

14

Efficiency (%)

92

THD (%)

90 12

88 Efficiency

THD 10

86

8

84

82 6

0 100 200 300 400 500 600

Power Output (W)

Figure 13. Efficiency and THD Performance vs.

Output Power Figure 16. Turn-ON, Vo=405.3V, Po=500W

Figure 14. Input Current Waveform Figure 17. Input Voltage and Output

Voltage Ripple Waveform

REV. 1.0.1 10/31/03 9

AN6004 APPLICATION NOTE

Table 1: Recommended Components

MOSFETs

Power Level Voltage rating P/Ns

75_100W 500,600V FQP6N50,FQP9N50, FQA13N50, FQA16N50,FDH15N50

100_400W 500,600V FQA16N50, FQA24N50, FQA19N60, FQA28N50

>400W 500,600V FDH44N50 ,FQL40N50, FQA28N50 , FDH27N50,

FQA19N60,FDH15N50 ,

IGBTs

Power Level P/Ns for frequency < 75 kHz

75_100W FGH20N6S2D,HGTG7N60A4D

100_400W FGH30N6S2D,HGTG12N60A4D

>400W FGH40N6S2D, HGTG20N60A4D, FGH50N6S2D, HGTG30N60A4D, FGK60N6S2D

Boost Diodes

Power Level P/Ns

75_100W ISL9R460P32 ISL9R860P2,

100_400W ISL9R860P2,ISL9R1560P2,

>400W ISL9R1560P2,ISL9R3060P2

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY

PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY

LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER

DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES

OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR

CORPORATION. As used herein:

1. Life support devices or systems are devices or systems 2. A critical component is any component of a life support

which, (a) are intended for surgical implant into the body, device or system whose failure to perform can be

or (b) support or sustain life, or (c) whose failure to perform reasonably expected to cause the failure of the life support

when properly used in accordance with instructions for use device or system, or to affect its safety or effectiveness.

provided in the labeling, can be reasonably expected to

result in significant injury to the user.

www.fairchildsemi.com

10/31/03 0.0m 002

Stock#AN00006004

2003 Fairchild Semiconductor Corporation

Você também pode gostar

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5795)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (345)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- Gas Turbine Manual PDFDocumento721 páginasGas Turbine Manual PDFZakki Afifi100% (2)

- (Task Specific Risk Assessment) : No Name Signature Position Date N Name Signature Position DateDocumento5 páginas(Task Specific Risk Assessment) : No Name Signature Position Date N Name Signature Position DateRavi Shankar TurlapatiAinda não há avaliações

- Biogas Presentation PDFDocumento44 páginasBiogas Presentation PDFAli Aamir100% (1)

- Pipe Welding ProceduresDocumento257 páginasPipe Welding ProceduresKhaeril Anwar100% (1)

- Laplace MPNI 1150Documento20 páginasLaplace MPNI 1150mansyur yadi67% (3)

- Design Loadbearing Masonry StructuresDocumento9 páginasDesign Loadbearing Masonry StructuresthushtikaAinda não há avaliações

- IT Dashboard Dec2013Documento870 páginasIT Dashboard Dec2013Dolly SinghAinda não há avaliações

- Cmus Cheat SheetDocumento1 páginaCmus Cheat Sheetvoll macuserAinda não há avaliações

- PSD Coarse AggregateDocumento3 páginasPSD Coarse AggregateMohd Syafiq AkmalAinda não há avaliações

- FrictionDocumento4 páginasFrictionMuzafar ahmadAinda não há avaliações

- s7 1500 Compare Table en MnemoDocumento88 páginass7 1500 Compare Table en MnemoPeli JorroAinda não há avaliações

- Certification - Speech Testing - Assistant PartnersDocumento2 páginasCertification - Speech Testing - Assistant PartnersRodrigo Freire BragaAinda não há avaliações

- Network TopologyDocumento36 páginasNetwork TopologykanagalasasankAinda não há avaliações

- Land SurvayingDocumento14 páginasLand Survayingajay negiAinda não há avaliações

- pLINES Datasheet FP V2.22Documento2 páginaspLINES Datasheet FP V2.22TrinhDinhLoc0% (1)

- Geology 1Documento2 páginasGeology 1Mike SantosAinda não há avaliações

- Datalogic Gryphon GM4100 User GuideDocumento52 páginasDatalogic Gryphon GM4100 User Guidebgrabbe92540% (1)

- Klauke - Bi-Metal Lugs & ConnectorsDocumento6 páginasKlauke - Bi-Metal Lugs & ConnectorsBiplab PaulAinda não há avaliações

- TRM34 Preparation of Calculations Rev5Documento5 páginasTRM34 Preparation of Calculations Rev5TuanAinda não há avaliações

- BUTLER 1924 PAPER Studies in Heterogeneous EquilibriaDocumento6 páginasBUTLER 1924 PAPER Studies in Heterogeneous Equilibriaglen19Ainda não há avaliações

- Foreword by Brett Queener - Agile Product Management With Scrum - Creating Products That Customers LoveDocumento3 páginasForeword by Brett Queener - Agile Product Management With Scrum - Creating Products That Customers LoveJoao Paulo MouraAinda não há avaliações

- En Webclima ManualDocumento44 páginasEn Webclima ManualGajendra RathoreAinda não há avaliações

- Schneider ElectricCahier Technique No. 199Documento36 páginasSchneider ElectricCahier Technique No. 199Alda EnglandAinda não há avaliações

- Iec 04Documento10 páginasIec 04Habeeb RahmanAinda não há avaliações

- Gujarat Technological University: A Project Report On:-Automatic Water Purification SystemDocumento11 páginasGujarat Technological University: A Project Report On:-Automatic Water Purification SystemJay KakadiyaAinda não há avaliações

- ODAA Support LetterDocumento2 páginasODAA Support LetterStatesman JournalAinda não há avaliações

- CPP Schematic Diagram Duplex Complete 9 Jan 2019Documento1 páginaCPP Schematic Diagram Duplex Complete 9 Jan 2019BdSulianoAinda não há avaliações

- Little Book of RubyDocumento104 páginasLittle Book of RubynoboAinda não há avaliações

- Certificate of Analysis: CertificationDocumento2 páginasCertificate of Analysis: CertificationGunawan Alim CahyoAinda não há avaliações

- GRE Sentence CompletionDocumento3 páginasGRE Sentence Completionapi-3699142Ainda não há avaliações