Escolar Documentos

Profissional Documentos

Cultura Documentos

M48T02 M48T12: 5.0 V, 16 Kbit (2 KB X 8) TIMEKEEPER Sram

Enviado por

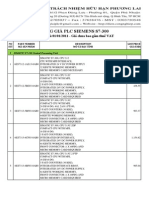

Mgc ElektronikTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

M48T02 M48T12: 5.0 V, 16 Kbit (2 KB X 8) TIMEKEEPER Sram

Enviado por

Mgc ElektronikDireitos autorais:

Formatos disponíveis

M48T02

M48T12

5.0 V, 16 Kbit (2 Kb x 8) TIMEKEEPER® SRAM

Features

■ Integrated, ultra low power SRAM, real-time

clock, and power-fail control circuit

■ BYTEWIDE™ RAM-like clock access

■ BCD coded year, month, day, date, hours,

minutes, and seconds

■ Typical clock accuracy of ±1 minute a month,

at 25 °C

■ Software controlled clock calibration for high

accuracy applications

■ Automatic power-fail chip deselect and WRITE

24

protection

1

■ WRITE protect voltages

(VPFD = power-fail deselect voltage):

– M48T02: VCC = 4.75 to 5.5 V;

4.5 V ≤ VPFD ≤ 4.75 V

– M48T12: VCC = 4.5 to 5.5 V; PCDIP24

4.2 V ≤ VPFD ≤ 4.5 V battery/crystal

CAPHAT™

■ Self-contained battery and crystal in the

CAPHAT™ DIP package

■ Pin and function compatible with JEDEC

standard 2 K x 8 SRAMs

■ RoHS compliant

– Lead-free second level interconnect

June 2011 Doc ID 2410 Rev 9 1/25

www.st.com 1

Contents M48T02, M48T12

Contents

1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Operation modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.1 READ mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.2 WRITE mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.3 Data retention mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3 Clock operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.1 Reading the clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.2 Setting the clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.3 Stopping and starting the oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.4 Calibrating the clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.5 VCC noise and negative going transients . . . . . . . . . . . . . . . . . . . . . . . . . 16

4 Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5 DC and AC parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

6 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

7 Part numbering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

8 Environmental information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

9 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2/25 Doc ID 2410 Rev 9

M48T02, M48T12 List of tables

List of tables

Table 1. Signal names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Table 2. Operating modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 3. READ mode AC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 4. WRITE mode AC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 5. Register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 6. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 7. Operating and AC measurement conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 8. Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 9. DC characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 10. Power down/up AC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 11. Power down/up trip points DC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 12. PCDIP24 – 24-pin plastic DIP, battery CAPHAT™, package mech. data . . . . . . . . . . . . . 21

Table 13. Ordering information scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 14. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Doc ID 2410 Rev 9 3/25

List of figures M48T02, M48T12

List of figures

Figure 1. Logic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 2. DIP connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 3. Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 4. READ mode AC waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 5. WRITE enable controlled, WRITE AC waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 6. Chip enable controlled, WRITE AC waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 7. Checking the BOK flag status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 8. Crystal accuracy across temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 9. Clock calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 10. Supply voltage protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 11. AC testing load circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 12. Power down/up mode AC waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 13. PCDIP24 – 24-pin plastic DIP, battery CAPHAT™, package outline . . . . . . . . . . . . . . . . . 21

Figure 14. Recycling symbols . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4/25 Doc ID 2410 Rev 9

M48T02, M48T12 Description

1 Description

The M48T02/12 TIMEKEEPER® RAM is a 2 Kb x 8 non-volatile static RAM and real-time

clock which is pin and functional compatible with the DS1642.

A special 24-pin, 600 mil DIP CAPHAT™ package houses the M48T02/12 silicon with a

quartz crystal and a long life lithium button cell to form a highly integrated battery-backed

memory and real-time clock solution.

The M48T02/12 button cell has sufficient capacity and storage life to maintain data and

clock functionality for an accumulated time period of at least 10 years in the absence of

power over the operating temperature range.

The M48T02/12 is a non-volatile pin and function equivalent to any JEDEC standard

2 Kb x 8 SRAM. It also easily fits into many ROM, EPROM, and EEPROM sockets,

providing the non-volatility of PROMs without any requirement for special WRITE timing or

limitations on the number of WRITEs that can be performed.

Figure 1. Logic diagram

VCC

11 8

A0-A10 DQ0-DQ7

W M48T02

M48T12

E

VSS

AI01027

Table 1. Signal names

A0-A10 Address inputs

DQ0-DQ7 Data inputs / outputs

E Chip enable

G Output enable

W WRITE enable

VCC Supply voltage

VSS Ground

Doc ID 2410 Rev 9 5/25

Description M48T02, M48T12

Figure 2. DIP connections

A7 1 24 VCC

A6 2 23 A8

A5 3 22 A9

A4 4 21 W

A3 5 20 G

A2 6 M48T02 19 A10

A1 7 M48T12 18 E

A0 8 17 DQ7

DQ0 9 16 DQ6

DQ1 10 15 DQ5

DQ2 11 14 DQ4

VSS 12 13 DQ3

AI01028

Figure 3. Block diagram

OSCILLATOR AND 8 x 8 BiPORT

CLOCK CHAIN SRAM ARRAY

32,768 Hz

CRYSTAL A0-A10

POWER

DQ0-DQ7

2040 x 8

SRAM ARRAY

LITHIUM

CELL E

VPFD

VOLTAGE SENSE W

AND

SWITCHING BOK G

CIRCUITRY

VCC VSS AI01329

6/25 Doc ID 2410 Rev 9

M48T02, M48T12 Operation modes

2 Operation modes

As Figure 3 on page 6 shows, the static memory array and the quartz controlled clock

oscillator of the M48T02/12 are integrated on one silicon chip. The two circuits are

interconnected at the upper eight memory locations to provide user accessible

BYTEWIDE™ clock information in the bytes with addresses 7F8h-7FFh. The clock locations

contain the year, month, date, day, hour, minute, and second in 24-hour BCD format.

Corrections for 28, 29 (leap year - valid until 2100), 30, and 31 day months are made

automatically.

Byte 7F8h is the clock control register. This byte controls user access to the clock

information and also stores the clock calibration setting.

The eight clock bytes are not the actual clock counters themselves; they are memory

locations consisting of BiPORT™ READ/WRITE memory cells. The M48T02/12 includes a

clock control circuit which updates the clock bytes with current information once per second.

The information can be accessed by the user in the same manner as any other location in

the static memory array.

The M48T02/12 also has its own power-fail detect circuit. The control circuitry constantly

monitors the single 5 V supply for an out of tolerance condition. When VCC is out of

tolerance, the circuit write protects the SRAM, providing a high degree of data security in the

midst of unpredictable system operation brought on by low VCC. As VCC falls below

approximately 3 V, the control circuitry connects the battery which maintains data and clock

operation until valid power returns.

Table 2. Operating modes

Mode VCC E G W DQ0-DQ7 Power

Deselect VIH X X High Z Standby

4.75 to 5.5 V

WRITE VIL X VIL DIN Active

or

READ VIL VIL VIH DOUT Active

4.5 to 5.5 V

READ VIL VIH VIH High Z Active

VSO to

Deselect X X X High Z CMOS standby

VPFD(min)(1)

Deselect ≤ VSO(1) X X X High Z Battery backup mode

1. See Table 11 on page 20 for details.

Note: X = VIH or VIL; VSO = Battery backup switchover voltage.

2.1 READ mode

The M48T02/12 is in the READ mode whenever W (WRITE enable) is high and E (chip

enable) is low. The device architecture allows ripple-through access of data from eight of

16,384 locations in the static storage array. Thus, the unique address specified by the 11

Address Inputs defines which one of the 2,048 bytes of data is to be accessed. Valid data

will be available at the data I/O pins within address access time (tAVQV) after the last

address input signal is stable, providing that the E and G access times are also satisfied. If

the E and G access times are not met, valid data will be available after the latter of the chip

enable access time (tELQV) or output enable access time (tGLQV).

Doc ID 2410 Rev 9 7/25

Operation modes M48T02, M48T12

The state of the eight three-state data I/O signals is controlled by E and G. If the outputs are

activated before tAVQV, the data lines will be driven to an indeterminate state until tAVQV. If

the address inputs are changed while E and G remain active, output data will remain valid

for output data hold time (tAXQX) but will go indeterminate until the next address access.

Figure 4. READ mode AC waveforms

tAVAV

A0-A10 VALID

tAVQV tAXQX

tELQV tEHQZ

tELQX

tGLQV tGHQZ

tGLQX

DQ0-DQ7 VALID

AI01330

Note: WRITE enable (W) = High.

Table 3. READ mode AC characteristics

M48T02/M48T12

Symbol Parameter(1) –70 –150 –200 Unit

Min Max Min Max Min Max

tAVAV READ cycle time 70 150 200 ns

tAVQV Address valid to output valid 70 150 200 ns

tELQV Chip enable low to output valid 70 150 200 ns

tGLQV Output enable low to output valid 35 75 80 ns

tELQX Chip enable low to output transition 5 10 10 ns

tGLQX Output enable low to output transition 5 5 5 ns

tEHQZ Chip enable high to output Hi-Z 25 35 40 ns

tGHQZ Output enable high to output Hi-Z 25 35 40 ns

tAXQX Address transition to output transition 10 5 5 ns

1. Valid for ambient operating temperature: TA = 0 to 70 °C; VCC = 4.75 to 5.5 V or 4.5 to 5.5 V (except where noted).

8/25 Doc ID 2410 Rev 9

M48T02, M48T12 Operation modes

2.2 WRITE mode

The M48T02/12 is in the WRITE mode whenever W and E are active. The start of a WRITE

is referenced from the latter occurring falling edge of W or E. A WRITE is terminated by the

earlier rising edge of W or E. The addresses must be held valid throughout the cycle. E or W

must return high for a minimum of tEHAX from chip enable or tWHAX from WRITE enable prior

to the initiation of another READ or WRITE cycle. Data-in must be valid tDVWH prior to the

end of WRITE and remain valid for tWHDX afterward. G should be kept high during WRITE

cycles to avoid bus contention; although, if the output bus has been activated by a low on E

and G, a low on W will disable the outputs tWLQZ after W falls.

Figure 5. WRITE enable controlled, WRITE AC waveform

tAVAV

A0-A10 VALID

tAVWH

tAVEL tWHAX

tWLWH

tAVWL

W

tWLQZ tWHQX

tWHDX

DQ0-DQ7 DATA INPUT

tDVWH

AI01331

Figure 6. Chip enable controlled, WRITE AC waveforms

tAVAV

A0-A10 VALID

tAVEH

tAVEL tELEH tEHAX

tAVWL

tEHDX

DQ0-DQ7 DATA INPUT

tDVEH AI01332B

Doc ID 2410 Rev 9 9/25

Operation modes M48T02, M48T12

Table 4. WRITE mode AC characteristics

M48T02/M48T12

Symbol Parameter(1) –70 –150 –200 Unit

Min Max Min Max Min Max

tAVAV WRITE cycle time 70 150 200 ns

tAVWL Address valid to WRITE enable low 0 0 0 ns

tAVEL Address valid to chip enable low 0 0 0 ns

tWLWH WRITE enable pulse width 50 90 120 ns

tELEH Chip enable low to chip enable high 55 90 120 ns

tWHAX WRITE enable high to address transition 0 10 10 ns

tEHAX Chip enable high to address transition 0 10 10 ns

tDVWH Input valid to WRITE enable high 30 40 60 ns

tDVEH Input valid to chip enable high 30 40 60 ns

tWHDX WRITE enable high to input transition 5 5 5 ns

tEHDX Chip enable high to input transition 5 5 5 ns

tWLQZ WRITE enable low to output Hi-Z 25 50 60 ns

tAVWH Address valid to WRITE enable high 60 120 140 ns

tAVEH Address valid to chip enable high 60 120 140 ns

tWHQX WRITE enable high to output transition 5 10 10 ns

1. Valid for ambient operating temperature: TA = 0 to 70 °C; VCC = 4.75 to 5.5 V or 4.5 to 5.5 V (except where

noted).

2.3 Data retention mode

With valid VCC applied, the M48T02/12 operates as a conventional BYTEWIDE™ static

RAM. Should the supply voltage decay, the RAM will automatically power-fail deselect, write

protecting itself when VCC falls within the VPFD (max), VPFD (min) window. All outputs

become high impedance, and all inputs are treated as “don't care.”

Note: A power failure during a WRITE cycle may corrupt data at the currently addressed location,

but does not jeopardize the rest of the RAM's content. At voltages below VPFD (min), the

user can be assured the memory will be in a write protected state, provided the VCC fall time

is not less than tF. The M48T02/12 may respond to transient noise spikes on VCC that reach

into the deselect window during the time the device is sampling VCC. Therefore, decoupling

of the power supply lines is recommended.

The power switching circuit connects external VCC to the RAM and disconnects the battery

when VCC rises above VSO. As VCC rises, the battery voltage is checked. If the voltage is too

low, an internal battery not oK (BOK) flag will be set. The BOK flag can be checked after

power up. If the BOK flag is set, the first WRITE attempted will be blocked. The flag is

automatically cleared after the first WRITE, and normal RAM operation resumes. Figure 7

on page 11 illustrates how a BOK check routine could be structured.

For more information on a battery storage life refer to the application note AN1012.

10/25 Doc ID 2410 Rev 9

M48T02, M48T12 Operation modes

Figure 7. Checking the BOK flag status

POWER-UP

READ DATA

AT ANY ADDRESS

WRITE DATA

COMPLEMENT BACK

TO SAME ADDRESS

READ DATA

AT SAME

ADDRESS AGAIN

IS DATA

COMPLEMENT NO (BATTERY LOW)

OF FIRST

READ?

NOTIFY SYSTEM

(BATTERY OK) YES OF LOW BATTERY

(DATA MAY BE

CORRUPTED)

WRITE ORIGINAL

DATA BACK TO

SAME ADDRESS

CONTINUE

AI00607

Doc ID 2410 Rev 9 11/25

Clock operations M48T02, M48T12

3 Clock operations

3.1 Reading the clock

Updates to the TIMEKEEPER® registers should be halted before clock data is read to

prevent reading data in transition. The BiPORT™ TIMEKEEPER cells in the RAM array are

only data registers and not the actual clock counters, so updating the registers can be halted

without disturbing the clock itself.

Updating is halted when a '1' is written to the READ bit, the seventh bit in the control

register. As long as a '1' remains in that position, updating is halted. After a halt is issued,

the registers reflect the count; that is, the day, date, and the time that were current at the

moment the halt command was issued.

All of the TIMEKEEPER registers are updated simultaneously. A halt will not interrupt an

update in progress. Updating is within a second after the bit is reset to a '0.'

3.2 Setting the clock

The eighth bit of the control register is the WRITE bit. Setting the WRITE bit to a '1,' like the

READ bit, halts updates to the TIMEKEEPER registers. The user can then load them with

the correct day, date, and time data in 24-hour BCD format (on Table 5 on page 13).

Resetting the WRITE bit to a '0' then transfers the values of all time registers (7F9-7FF) to

the actual TIMEKEEPER counters and allows normal operation to resume. The FT bit and

the bits marked as '0' in Table 5 on page 13 must be written to '0' to allow for normal

TIMEKEEPER and RAM operation.

See the application note AN923, “TIMEKEEPER® rolling into the 21st century” for

information on century rollover.

12/25 Doc ID 2410 Rev 9

M48T02, M48T12 Clock operations

Table 5. Register map

Data Function/range

Address

D7 D6 D5 D4 D3 D2 D1 D0 BCD format

7FF 10 years Year Year 00-99

7FE 0 0 0 10 M Month Month 01-12

7FD 0 0 10 date Date Date 01-31

7FC 0 FT 0 0 0 Day Day 01-07

7FB 0 0 10 hours Hours Hours 00-23

7FA 0 10 minutes Minutes Minutes 00-59

7F9 ST 10 seconds Seconds Seconds 00-59

7F8 W R S Calibration Control

Keys:

S = SIGN bit

FT = FREQUENCY TEST bit (set to '0' for normal clock operation)

R = READ bit

W = WRITE bit

ST = STOP bit

0 = Must be set to '0'

3.3 Stopping and starting the oscillator

The oscillator may be stopped at any time. If the device is going to spend a significant

amount of time on the shelf, the oscillator can be turned off to minimize current drain on the

battery. The STOP bit is the MSB of the seconds register. Setting it to a '1' stops the

oscillator. The M48T02/12 is shipped from STMicroelectronics with the STOP bit set to a '1.'

When reset to a '0,' the M48T02/12 oscillator starts within one second.

3.4 Calibrating the clock

The M48T02/12 is driven by a quartz-controlled oscillator with a nominal frequency of

32,768 Hz. A typical M48T02/12 is accurate within 1 minute per month at 25°C without

calibration. The devices are tested not to exceed ± 35 ppm (parts per million) oscillator

frequency error at 25°C, which equates to about ±1.53 minutes per month.

The oscillation rate of any crystal changes with temperature. Figure 8 on page 15 shows the

frequency error that can be expected at various temperatures. Most clock chips compensate

for crystal frequency and temperature shift error with cumbersome “trim” capacitors. The

M48T02/12 design, however, employs periodic counter correction. The calibration circuit

adds or subtracts counts from the oscillator divider circuit at the divide by 256 stage, as

shown in Figure 9 on page 15. The number of times pulses are blanked (subtracted,

negative calibration) or split (added, positive calibration) depends upon the value loaded into

the five-bit calibration byte found in the control register. Adding counts speeds the clock up,

subtracting counts slows the clock down.

The calibration byte occupies the five lower order bits in the control register. This byte can

be set to represent any value between 0 and 31 in binary form. The sixth bit is the sign bit;

Doc ID 2410 Rev 9 13/25

Clock operations M48T02, M48T12

'1' indicates positive calibration, '0' indicates negative calibration. Calibration occurs within a

64 minute cycle. The first 62 minutes in the cycle may, once per minute, have one second

either shortened by 128 or lengthened by 256 oscillator cycles. If a binary '1' is loaded into

the register, only the first 2 minutes in the 64 minute cycle will be modified; if a binary 6 is

loaded, the first 12 will be affected, and so on.

Therefore, each calibration step has the effect of adding 512 or subtracting 256 oscillator

cycles for every 125,829,120 actual oscillator cycles; that is +4.068 or –2.034 ppm of

adjustment per calibration step in the calibration register. Assuming that the oscillator is in

fact running at exactly 32,768 Hz, each of the 31 increments in the calibration byte would

represent +10.7 or –5.35 seconds per month which corresponds to a total range of +5.5 or

–2.75 minutes per month.

Two methods are available for ascertaining how much calibration a given M48T02/12 may

require. The first involves simply setting the clock, letting it run for a month and comparing it

to a known accurate reference (like WWV broadcasts). While that may seem crude, it allows

the designer to give the end user the ability to calibrate his clock as his environment may

require, even after the final product is packaged in a non-user serviceable enclosure. All the

designer has to do is provide a simple utility that accesses the calibration byte.

The second approach is better suited to a manufacturing environment, and involves the use

of some test equipment. When the Frequency Test (FT) bit, the seventh-most significant bit

in the day register, is set to a '1,' and the oscillator is running at 32,768 Hz, the LSB (DQ0) of

the seconds register will toggle at 512 Hz. Any deviation from 512 Hz indicates the degree

and direction of oscillator frequency shift at the test temperature. For example, a reading of

512.01024 Hz would indicate a +20 ppm oscillator frequency error, requiring

–10 (WR001010) to be loaded into the calibration byte for correction.

Note: Setting or changing the calibration byte does not affect the frequency test output frequency.

The device must be selected and addresses must be stable at address 7F9 when reading

the 512 Hz on DQ0.

The FT bit must be set using the same method used to set the clock: using the WRITE bit.

The LSB of the seconds register is monitored by holding the M48T02/12 in an extended

READ of the seconds register, but without having the READ bit set. The FT bit MUST be

reset to '0' for normal clock operations to resume.

Note: It is not necessary to set the WRITE bit when setting or resetting the frequency test bit (FT)

or the stop bit (ST).

For more information on calibration, see the application note AN924, “TIMEKEEPER®

calibration.”

14/25 Doc ID 2410 Rev 9

M48T02, M48T12 Clock operations

Figure 8. Crystal accuracy across temperature

ppm

20

-20

-40

ΔF = -0.038 ppm (T - T )2 ± 10%

0

-60 F C2

T0 = 25 °C

-80

-100

0 5 10 15 20 25 30 35 40 45 50 55 60 65 70 °C AI02124

Figure 9. Clock calibration

NORMAL

POSITIVE

CALIBRATION

NEGATIVE

CALIBRATION

AI00594B

Doc ID 2410 Rev 9 15/25

Clock operations M48T02, M48T12

3.5 VCC noise and negative going transients

ICC transients, including those produced by output switching, can produce voltage

fluctuations, resulting in spikes on the VCC bus. These transients can be reduced if

capacitors are used to store energy which stabilizes the VCC bus. The energy stored in the

bypass capacitors will be released as low going spikes are generated or energy will be

absorbed when overshoots occur. A ceramic bypass capacitor value of 0.1 µF (as shown in

Figure 10 on page 16) is recommended in order to provide the needed filtering.

In addition to transients that are caused by normal SRAM operation, power cycling can

generate negative voltage spikes on VCC that drive it to values below VSS by as much as

one volt. These negative spikes can cause data corruption in the SRAM while in battery

backup mode. To protect from these voltage spikes, it is recommended to connect a

Schottky diode from VCC to VSS (cathode connected to VCC, anode to VSS). Schottky diode

1N5817 is recommended for through hole and MBRS120T3 is recommended for surface

mount.

Figure 10. Supply voltage protection

VCC

VCC

0.1μF DEVICE

VSS

AI02169

16/25 Doc ID 2410 Rev 9

M48T02, M48T12 Maximum ratings

4 Maximum ratings

Stressing the device above the rating listed in the absolute maximum ratings table may

cause permanent damage to the device. These are stress ratings only and operation of the

device at these or any other conditions above those indicated in the operating sections of

this specification is not implied. Exposure to absolute maximum rating conditions for

extended periods may affect device reliability.

Table 6. Absolute maximum ratings

Symbol Parameter Value Unit

TA Ambient operating temperature 0 to 70 °C

TSTG Storage temperature (VCC off, oscillator off) –40 to 85 °C

TSLD(1)(2) Lead solder temperature for 10 seconds 260 °C

VIO Input or output voltages –0.3 to 7 V

VCC Supply voltage –0.3 to 7 V

IO Output current 20 mA

PD Power dissipation 1 W

1. Soldering temperature of the IC leads is to not exceed 260 °C for 10 seconds. Furthermore, the devices

shall not be exposed to IR reflow nor preheat cycles (as performed as part of wave soldering). ST

recommends the devices be hand-soldered or placed in sockets to avoid heat damage to the batteries.

2. For DIP packaged devices, ultrasonic vibrations should not be used for post-solder cleaning to avoid

damaging the crystal.

Caution: Negative undershoots below –0.3 V are not allowed on any pin while in the battery backup

mode.

Doc ID 2410 Rev 9 17/25

DC and AC parameters M48T02, M48T12

5 DC and AC parameters

This section summarizes the operating and measurement conditions, as well as the DC and

AC characteristics of the device. The parameters in the following DC and AC characteristic

tables are derived from tests performed under the measurement conditions listed in the

relevant tables. Designers should check that the operating conditions in their projects match

the measurement conditions when using the quoted parameters.

Table 7. Operating and AC measurement conditions

Parameter M48T02 M48T12 Unit

Supply voltage (VCC) 4.75 to 5.5 4.5 to 5.5 V

Ambient operating temperature (TA) 0 to 70 0 to 70 °C

Load capacitance (CL) 100 100 pF

Input rise and fall times ≤5 ≤5 ns

Input pulse voltages 0 to 3 0 to 3 V

Input and output timing ref. voltages 1.5 1.5 V

Note: Output Hi-Z is defined as the point where data is no longer driven.

Figure 11. AC testing load circuit

5V

1.8kΩ

DEVICE

UNDER OUT

TEST

1kΩ CL = 100pF

CL includes JIG capacitance

AI01019

Table 8. Capacitance

Symbol Parameter(1)(2) Min Max Unit

CIN Input capacitance - 10 pF

CIO (3) Input / output capacitance - 10 pF

1. Effective capacitance measured with power supply at 5 V. Sampled only, not 100% tested.

2. At 25 °C, f = 1 MHz.

3. Outputs deselected.

18/25 Doc ID 2410 Rev 9

M48T02, M48T12 DC and AC parameters

Table 9. DC characteristics

Symbol Parameter Test condition(1) Min Max Unit

ILI Input leakage current 0V ≤ VIN ≤ VCC ±1 µA

ILO(2) Output leakage current 0V ≤ VOUT ≤ VCC ±1 µA

ICC Supply current Outputs open 80 mA

ICC1(3) Supply current (standby) TTL E = VIH 3 mA

(3)

ICC2 Supply current (standby) CMOS E = VCC – 0.2 V 3 mA

VIL Input low voltage –0.3 0.8 V

VIH Input high voltage 2.2 VCC + 0.3 V

VOL Output low voltage IOL = 2.1 mA 0.4 V

VOH Output high voltage IOH = –1 mA 2.4 V

1. Valid for ambient operating temperature: TA = 0 to 70 °C; VCC = 4.75 to 5.5 V or 4.5 to 5.5 V (except where noted).

2. Outputs deselected.

3. Measured with control bits set as follows: R = '1'; W, ST, FT = '0.'

Figure 12. Power down/up mode AC waveforms

VCC

VPFD (max)

VPFD (min)

VSO

tF tDR tR

tPD tFB tRB trec

INPUTS RECOGNIZED DON'T CARE NOTE RECOGNIZED

HIGH-Z

OUTPUTS VALID VALID

(PER CONTROL INPUT) (PER CONTROL INPUT)

AI00606

Note: Inputs may or may not be recognized at this time. Caution should be taken to keep E high as

VCC rises past VPFD (min). Some systems may perform inadvertent WRITE cycles after VCC

rises above VPFD (min) but before normal system operations begin. Even though a power on

reset is being applied to the processor, a reset condition may not occur until after the system

clock is running.

Doc ID 2410 Rev 9 19/25

DC and AC parameters M48T02, M48T12

Table 10. Power down/up AC characteristics

Symbol Parameter(1) Min Max Unit

tPD E or W at VIH before power down 0 - µs

tF(2) VPFD (max) to VPFD (min) VCC fall time 300 - µs

tFB(3) VPFD (min) to VSS VCC fall time 10 - µs

tR VPFD (min) to VPFD (max) VCC rise time 0 - µs

tRB VSS to VPFD (min) VCC rise time 1 - µs

trec E or W at VIH before power-up 2 - ms

1. Valid for ambient operating temperature: TA = 0 to 70 °C; VCC = 4.75 to 5.5 V or 4.5 to 5.5 V (except where

noted).

2. VPFD (max) to VPFD (min) fall time of less than tF may result in deselection/write protection not occurring

until 200 µs after VCC passes VPFD (min).

3. VPFD (min) to VSS fall time of less than tFB may cause corruption of RAM data.

Table 11. Power down/up trip points DC characteristics

Symbol Parameter(1)(2) Min Typ Max Unit

M48T02 4.5 4.6 4.75 V

VPFD Power-fail deselect voltage

M48T12 4.2 4.3 4.5 V

VSO Battery backup switchover voltage 3.0 V

(3)

tDR Expected data retention time 10 YEARS

1. All voltages referenced to VSS.

2. Valid for ambient operating temperature: TA = 0 to 70 °C; VCC = 4.75 to 5.5 V or 4.5 to 5.5 V (except where

noted).

3. At 25 °C; VCC = 0 V.

20/25 Doc ID 2410 Rev 9

M48T02, M48T12 Package mechanical data

6 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK® packages, depending on their level of environmental compliance. ECOPACK®

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK® is an ST trademark.

Figure 13. PCDIP24 – 24-pin plastic DIP, battery CAPHAT™, package outline

A2 A

A1 L C

B1 B e1

eA

e3

1

PCDIP

Note: Drawing is not to scale.

Table 12. PCDIP24 – 24-pin plastic DIP, battery CAPHAT™, package mech. data

mm inches

Symb

Typ Min Max Typ Min Max

A 8.89 9.65 0.350 0.380

A1 0.38 0.76 0.015 0.030

A2 8.38 8.89 0.330 0.350

B 0.38 0.53 0.015 0.021

B1 1.14 1.78 0.045 0.070

C 0.20 0.31 0.008 0.012

D 34.29 34.80 1.350 1.370

E 17.83 18.34 0.702 0.722

e1 2.29 2.79 0.090 0.110

e3 27.94 1.1

eA 15.24 16.00 0.600 0.630

L 3.05 3.81 0.120 0.150

N 24 24

Doc ID 2410 Rev 9 21/25

Part numbering M48T02, M48T12

7 Part numbering

Table 13. Ordering information scheme

Example: M48T 02 –70 PC 1

Device type

M48T

Supply voltage and write protect voltage

02 = VCC = 4.75 to 5.5 V; VPFD = 4.5 to 4.75 V

12 = VCC = 4.5 to 5.5 V; VPFD = 4.2 to 4.5 V

Speed

–70 = 70 ns (M48T02/12)

–150 = 150 ns (M48T02/12)

–200 = 200 ns (M48T02/12)(1)

Package

PC = PCDIP24

Temperature range

1 = 0 to 70 °C

Shipping method

blank = ECOPACK® package, tubes

1. Not recommended for new design. Contact ST sales office for availability.

For other options, or for more information on any aspect of this device, please contact the

ST sales office nearest you.

22/25 Doc ID 2410 Rev 9

M48T02, M48T12 Environmental information

8 Environmental information

Figure 14. Recycling symbols

This product contains a non-rechargeable lithium (lithium carbon monofluoride chemistry)

button cell battery fully encapsulated in the final product.

Recycle or dispose of batteries in accordance with the battery manufacturer's instructions

and local/national disposal and recycling regulations.

Doc ID 2410 Rev 9 23/25

Revision history M48T02, M48T12

9 Revision history

Table 14. Document revision history

Date Revision Changes

Jul-2000 1.0 First issue

13-Jul-2000 1.1 trec change (Table 10)

07-May-2001 2.0 Reformatted; temp. / voltage info. added to tables (Table 8, 9, 3, 4, 10, 11)

14-May-2001 2.1 Note added to clock calibration section; table footnote correction (Table 2)

16-Jul-2001 2.2 Basic formatting / content changes (cover page, Table 8, 9)

20-May-2002 2.3 Add countries to disclaimer

26-Jun-2002 2.4 Add footnote to table (Table 11)

28-Mar-2003 3.0 v2.2 template applied; test conditions updated (Table 10)

Reformatted; lead-free (Pb-free) package information update (Table 6,

31-Mar-2004 4.0

13)

12-Dec-2005 5.0 Updated template, lead-free text, removed footnote (Table 9, 13)

Added lead-free second level interconnect information to cover page and

21-Sep-2007 6

Section 6: Package mechanical data.

Added Section 8: Environmental information; updated text in Section 6:

13-Jan-2009 7

Package mechanical data; minor formatting changes.

02-Aug-2010 8 Reformatted document; updated Section 4, Table 12, 13.

Updated footnote 1 of Table 6: Absolute maximum ratings; updated

07-Jun-2011 9

Section 8: Environmental information.

24/25 Doc ID 2410 Rev 9

M48T02, M48T12

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2011 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 2410 Rev 9 25/25

Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

STMicroelectronics:

M48T12-150PC1 M48T02-150PC1 M48T02-70PC1 M48T12-70PC1 M48T12-200PC1 M48T02-200PC1

Você também pode gostar

- M48T35AV: 3.3 V, 256 Kbit (32 Kbit X 8) TIMEKEEPER SramDocumento29 páginasM48T35AV: 3.3 V, 256 Kbit (32 Kbit X 8) TIMEKEEPER SramDawood AhmedAinda não há avaliações

- Chiller MemoryDocumento21 páginasChiller MemoryminguelameazzaAinda não há avaliações

- M48T08 M48T08Y, M48T18: 5 V, 64 Kbit (8 KB X 8) TIMEKEEPER SramDocumento31 páginasM48T08 M48T08Y, M48T18: 5 V, 64 Kbit (8 KB X 8) TIMEKEEPER SramWaleed Ah-DhaifiAinda não há avaliações

- m48t08 150pc1 PDFDocumento31 páginasm48t08 150pc1 PDFMariuszChreptakAinda não há avaliações

- M41T11Documento29 páginasM41T11ЮрийAinda não há avaliações

- 1 Mbit (128 Kbit X 8) UV EPROM and OTP EPROM: FeaturesDocumento24 páginas1 Mbit (128 Kbit X 8) UV EPROM and OTP EPROM: FeaturesStuxnetAinda não há avaliações

- STMicroelectronics M48Z08 100PC1 DatasheetDocumento20 páginasSTMicroelectronics M48Z08 100PC1 Datasheetotniel marchanAinda não há avaliações

- M48T08 M48T08Y, M48T18: 5V, 64 Kbit (8 KB x8) TIMEKEEPER SramDocumento26 páginasM48T08 M48T08Y, M48T18: 5V, 64 Kbit (8 KB x8) TIMEKEEPER SramLuis Fernando Garcia SAinda não há avaliações

- M48T35AY M48T35AV: 5.0 or 3.3V, 256 Kbit (32 KB x8) TIMEKEEPER SramDocumento26 páginasM48T35AY M48T35AV: 5.0 or 3.3V, 256 Kbit (32 KB x8) TIMEKEEPER SramDawood AhmedAinda não há avaliações

- Jameco Part Number 697961: Distributed byDocumento25 páginasJameco Part Number 697961: Distributed byElwanAinda não há avaliações

- M95320 M95320-W M95320-R M95640 M95640-W M95640-R: 32 Kbit and 64 Kbit Serial Spi Bus Eeproms With High-Speed ClockDocumento46 páginasM95320 M95320-W M95320-R M95640 M95640-W M95640-R: 32 Kbit and 64 Kbit Serial Spi Bus Eeproms With High-Speed Clockbigpala2007Ainda não há avaliações

- Numonyx Forté™ Serial Flash Memory M25P40Documento61 páginasNumonyx Forté™ Serial Flash Memory M25P40fabioakioAinda não há avaliações

- Jameco Part Number 39790ST: Distributed byDocumento23 páginasJameco Part Number 39790ST: Distributed byZaenul MustaqimAinda não há avaliações

- M41T0Documento23 páginasM41T0AndreaAinda não há avaliações

- 24c64 DatasheetDocumento26 páginas24c64 DatasheetNom AkAinda não há avaliações

- 16 Kbit and 8 Kbit Serial SPI Bus EEPROM With High Speed ClockDocumento45 páginas16 Kbit and 8 Kbit Serial SPI Bus EEPROM With High Speed ClockRick CastilloAinda não há avaliações

- ST STM8L051F3 8-Bit Microcontroller DatasheetDocumento93 páginasST STM8L051F3 8-Bit Microcontroller Datasheettaj.nezami1660Ainda não há avaliações

- 24C16Documento33 páginas24C16Jair2808Ainda não há avaliações

- 24 C 16 WDocumento34 páginas24 C 16 WmaldomattAinda não há avaliações

- 64 Mbit, Low Voltage, Serial Flash Memory With 75 MHZ Spi Bus InterfaceDocumento55 páginas64 Mbit, Low Voltage, Serial Flash Memory With 75 MHZ Spi Bus InterfaceomottoAinda não há avaliações

- Datasheet 95160Documento48 páginasDatasheet 95160Alexandre Da Silva PintoAinda não há avaliações

- z86l81 z86l98Documento88 páginasz86l81 z86l98david.gjeorgevskiAinda não há avaliações

- AN2586 Application Note: STM32F10xxx Hardware Development: Getting StartedDocumento28 páginasAN2586 Application Note: STM32F10xxx Hardware Development: Getting StartedRouaissi RidhaAinda não há avaliações

- Spider - Tle7238Gs: 8 Channel High-Side and Low-Side Relay Switch With Limp Home ModeDocumento37 páginasSpider - Tle7238Gs: 8 Channel High-Side and Low-Side Relay Switch With Limp Home ModeHelal ShamesAinda não há avaliações

- 128-Mbit, Low-Voltage, Serial Flash Memory With 54-Mhz Spi Bus InterfaceDocumento47 páginas128-Mbit, Low-Voltage, Serial Flash Memory With 54-Mhz Spi Bus InterfaceregyamataAinda não há avaliações

- M24C64-W M24C64-R M24C64-F M24C64-DF: 64-Kbit Serial I C Bus EEPROMDocumento42 páginasM24C64-W M24C64-R M24C64-F M24C64-DF: 64-Kbit Serial I C Bus EEPROMRoozbeh BahmanyarAinda não há avaliações

- L9758 PDFDocumento29 páginasL9758 PDFsumitsalviAinda não há avaliações

- M68HC12BDocumento334 páginasM68HC12BAnonymous OFfJVrQY6Ainda não há avaliações

- MC68HC812A4 Datashett PDFDocumento242 páginasMC68HC812A4 Datashett PDFTar-Alcarin OrtizAinda não há avaliações

- STM32F103 DatasheetDocumento80 páginasSTM32F103 DatasheetmikyduudeAinda não há avaliações

- M34E04Documento32 páginasM34E04quemasda quiensoyAinda não há avaliações

- Infineon TLE8110EE DS v01!03!01 enDocumento74 páginasInfineon TLE8110EE DS v01!03!01 enEduardo FloresAinda não há avaliações

- Datasheet TLE8264EDocumento99 páginasDatasheet TLE8264Ecj002Ainda não há avaliações

- STM8 L101 FXDocumento88 páginasSTM8 L101 FXReVAinda não há avaliações

- TLE6240GP: Automotive PowerDocumento37 páginasTLE6240GP: Automotive Powerилья мантровAinda não há avaliações

- Glow Plug System Control IC: FeaturesDocumento27 páginasGlow Plug System Control IC: FeaturesPiotr PodkowaAinda não há avaliações

- Microprocessor Programming and Applications for Scientists and EngineersNo EverandMicroprocessor Programming and Applications for Scientists and EngineersAinda não há avaliações

- DatasheetDocumento36 páginasDatasheetAndres GuerreroAinda não há avaliações

- STM8L151G4 Ufqfpn28Documento124 páginasSTM8L151G4 Ufqfpn28Faisal AbdullahAinda não há avaliações

- M24C64 M24C32: 64kbit and 32kbit Serial I C Bus EEPROMDocumento27 páginasM24C64 M24C32: 64kbit and 32kbit Serial I C Bus EEPROMlangthangru83Ainda não há avaliações

- M95320 M95320-W M95320-R: 32 Kbit Serial Spi Bus Eeproms With High-Speed ClockDocumento44 páginasM95320 M95320-W M95320-R: 32 Kbit Serial Spi Bus Eeproms With High-Speed ClockRobinson PaulinoAinda não há avaliações

- Datasheet de Uma Memória Eeprom - 95640Documento46 páginasDatasheet de Uma Memória Eeprom - 95640Anthony AndreyAinda não há avaliações

- Features: 6-Pin Smart Reset™Documento24 páginasFeatures: 6-Pin Smart Reset™Tejas KumarAinda não há avaliações

- TLE8208Documento41 páginasTLE8208Luis VilchezAinda não há avaliações

- 128-Mbit, Low-Voltage, Serial Flash Memory With 54-Mhz Spi Bus InterfaceDocumento47 páginas128-Mbit, Low-Voltage, Serial Flash Memory With 54-Mhz Spi Bus InterfaceteomondoAinda não há avaliações

- CD00251732 PDFDocumento88 páginasCD00251732 PDFdavideosto3560Ainda não há avaliações

- STM32F103V8T6 STMicroelectronicsDocumento99 páginasSTM32F103V8T6 STMicroelectronicsMike SharpeAinda não há avaliações

- Stm32f4 Hardware DevelopmentDocumento43 páginasStm32f4 Hardware DevelopmentrevaAinda não há avaliações

- M27C1001 15FDocumento24 páginasM27C1001 15FkisjoskaAinda não há avaliações

- DS01Documento17 páginasDS01Vikas BansalAinda não há avaliações

- 7601Documento211 páginas7601Dan EsentherAinda não há avaliações

- ST Micro - An3338Documento73 páginasST Micro - An3338smhbAinda não há avaliações

- M95320 M95320-W M95320-R M95640 M95640-W M95640-R: 32 Kbit and 64 Kbit Serial Spi Bus Eeproms With High Speed ClockDocumento44 páginasM95320 M95320-W M95320-R M95640 M95640-W M95640-R: 32 Kbit and 64 Kbit Serial Spi Bus Eeproms With High Speed ClockDj ICEAinda não há avaliações

- LIS331DLH Accelerometer DatasheetDocumento38 páginasLIS331DLH Accelerometer Datasheetbartford100% (1)

- Tdoct1377a EngDocumento44 páginasTdoct1377a Enghacene omarAinda não há avaliações

- High Precision Automotive Unipolar Hall Effect Switch TLE4964-1MDocumento27 páginasHigh Precision Automotive Unipolar Hall Effect Switch TLE4964-1MDhashana MoorthyAinda não há avaliações

- M25P80Documento53 páginasM25P80api-3736976Ainda não há avaliações

- TLE4997E2: Programmable Linear Hall SensorDocumento34 páginasTLE4997E2: Programmable Linear Hall SensortanmaysutariaAinda não há avaliações

- nanoLOC TRX NA5TR1 DatasheetDocumento62 páginasnanoLOC TRX NA5TR1 DatasheetHugo Loureiro50% (2)

- Jvm-407b Ba 4012 ManualDocumento300 páginasJvm-407b Ba 4012 ManualMgc ElektronikAinda não há avaliações

- Euro XPK Puck Type Programmable SensorDocumento2 páginasEuro XPK Puck Type Programmable SensorMgc ElektronikAinda não há avaliações

- Drive Motor Stock Comlec UnitsDocumento96 páginasDrive Motor Stock Comlec UnitsMgc Elektronik100% (1)

- c140 Compair Compressor Parts Manual You Are Looking For A Book c140 Compair CompressorDocumento7 páginasc140 Compair Compressor Parts Manual You Are Looking For A Book c140 Compair CompressorMgc ElektronikAinda não há avaliações

- Compact InclinometersDocumento1 páginaCompact InclinometersMgc ElektronikAinda não há avaliações

- Can Bus Systems Overview HirschmannDocumento22 páginasCan Bus Systems Overview HirschmannMgc ElektronikAinda não há avaliações

- G11002 G11003 G12002 G12003: TransistorDocumento2 páginasG11002 G11003 G12002 G12003: TransistorMgc ElektronikAinda não há avaliações

- Tadano Fault CodesDocumento1 páginaTadano Fault CodesMgc Elektronik100% (5)

- Compuload CL6000-WEB VersionDocumento2 páginasCompuload CL6000-WEB VersionMgc ElektronikAinda não há avaliações

- Pegasus 2 PDFDocumento4 páginasPegasus 2 PDFMgc ElektronikAinda não há avaliações

- WWW Gottwald Com Gottwald Site Gottwald de News PDF HMK 260 Eeg Uk PDFDocumento1 páginaWWW Gottwald Com Gottwald Site Gottwald de News PDF HMK 260 Eeg Uk PDFMgc ElektronikAinda não há avaliações

- DMSCP Manual EngDocumento58 páginasDMSCP Manual EngMgc ElektronikAinda não há avaliações

- Loader / Tractor Scales: Advanced On-Board Weighing SystemsDocumento2 páginasLoader / Tractor Scales: Advanced On-Board Weighing SystemsMgc ElektronikAinda não há avaliações

- Valtek Mark One Control Valves Valtek Mark One Control ValvesDocumento21 páginasValtek Mark One Control Valves Valtek Mark One Control ValvesMgc ElektronikAinda não há avaliações

- Htl4017 Au BDDocumento2 páginasHtl4017 Au BDMgc ElektronikAinda não há avaliações

- Survey Paper On Soldiers Health Tracking System Using Internet of Things (IOT)Documento5 páginasSurvey Paper On Soldiers Health Tracking System Using Internet of Things (IOT)International Journal of Innovative Science and Research TechnologyAinda não há avaliações

- Samsung SMART Signage - PHF - PMF Series Datasheet - WWDocumento12 páginasSamsung SMART Signage - PHF - PMF Series Datasheet - WWsorin_tvAinda não há avaliações

- DWDM Sfp10g 40km c17 Transceiver Module 141108Documento10 páginasDWDM Sfp10g 40km c17 Transceiver Module 141108GLsun MallAinda não há avaliações

- Osmeoisis 2022-09-06 15-33-19PIC - Enh-Mig - C - 9Documento20 páginasOsmeoisis 2022-09-06 15-33-19PIC - Enh-Mig - C - 9Tomás BurónAinda não há avaliações

- East West CircuitsDocumento120 páginasEast West Circuitsricardo_MassisAinda não há avaliações

- Theory Lecture Week 4M MES DR RukonuzzamanDocumento38 páginasTheory Lecture Week 4M MES DR Rukonuzzamanshuvochandro6254Ainda não há avaliações

- Common Flash Interface Version 1.4Documento8 páginasCommon Flash Interface Version 1.4Gastón LutriAinda não há avaliações

- BITX20 - A Bidirectional SSB Transceiver: Ham News June - July 2004Documento9 páginasBITX20 - A Bidirectional SSB Transceiver: Ham News June - July 2004dayaaolAinda não há avaliações

- Performance Analysis of FC-TCR: Abstract:-This Paper Deals With Open Loop Study of FixedDocumento3 páginasPerformance Analysis of FC-TCR: Abstract:-This Paper Deals With Open Loop Study of FixedDP Technical ClassesAinda não há avaliações

- CBSE Class 9 Computer Science Sample Paper 2017Documento1 páginaCBSE Class 9 Computer Science Sample Paper 2017Vaibhav bhandari0% (1)

- Phase Locking in High Performance Systems PDFDocumento512 páginasPhase Locking in High Performance Systems PDFShahzad IslahiAinda não há avaliações

- Device Parameter Extraction of 14Nm, 10nmand 7Nm FinfetDocumento43 páginasDevice Parameter Extraction of 14Nm, 10nmand 7Nm FinfetKrisumraj PurkaitAinda não há avaliações

- Ece MagazineDocumento73 páginasEce MagazineA C MADHESWARANAinda não há avaliações

- Electric Vehicle Charging Station With An Energy Storage Stage For Split-Dc Bus Voltage BalancingDocumento3 páginasElectric Vehicle Charging Station With An Energy Storage Stage For Split-Dc Bus Voltage BalancingJohn AjishAinda não há avaliações

- What's The Difference Between IEEE 802.11af and 802.11ah - PDFDocumento10 páginasWhat's The Difference Between IEEE 802.11af and 802.11ah - PDFsorinproiecteAinda não há avaliações

- AC 800PEC Sales BrochureDocumento12 páginasAC 800PEC Sales BrochureMohd Lutfi MahaliAinda não há avaliações

- Getting Started With Power System BlocksetDocumento33 páginasGetting Started With Power System BlocksetIrfan AliAinda não há avaliações

- Combinatio Nal Logic: Design & Analysis of VLSI SystemDocumento9 páginasCombinatio Nal Logic: Design & Analysis of VLSI Systemnajmun_cseduAinda não há avaliações

- Toshiba Strata DK 24-56-96 ManualDocumento676 páginasToshiba Strata DK 24-56-96 ManualRobert MerrittAinda não há avaliações

- XFP 10G SM 40Km TRF7052FN (Opnext)Documento29 páginasXFP 10G SM 40Km TRF7052FN (Opnext)Ayan ChakrabortyAinda não há avaliações

- LAB 4-PE-LabDocumento7 páginasLAB 4-PE-LabLovely JuttAinda não há avaliações

- 8410 ManualDocumento45 páginas8410 Manualviatr0nicAinda não há avaliações

- V AntennaDocumento5 páginasV Antennaማሙየ አይቸውAinda não há avaliações

- Bang Gia PLC Siemens s7 300Documento11 páginasBang Gia PLC Siemens s7 300916153Ainda não há avaliações

- Antenna Specifications: Electrical PropertiesDocumento6 páginasAntenna Specifications: Electrical PropertiesАлександр100% (1)

- MMTDocumento36 páginasMMTAvoyAinda não há avaliações

- Apex DC Motor Drive ICDocumento1 páginaApex DC Motor Drive ICSuman RachaAinda não há avaliações

- Physics Project 12Documento12 páginasPhysics Project 12Nishant Attri100% (1)

- PPA Push AppnoteDocumento31 páginasPPA Push AppnoteShantiSwaroopAinda não há avaliações

- Voltage Dip Mitigation Using Statcom: BY Sumit Kumar Singh Mtech 1 Year 17PEE020Documento12 páginasVoltage Dip Mitigation Using Statcom: BY Sumit Kumar Singh Mtech 1 Year 17PEE020Sumit SinghAinda não há avaliações