Escolar Documentos

Profissional Documentos

Cultura Documentos

Practice 7

Enviado por

Yadira MorenoDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Practice 7

Enviado por

Yadira MorenoDireitos autorais:

Formatos disponíveis

1

VII informe Sistemas Digitales

Grupo No.

Sistemas Digitales I Nota

Nelsy Yadira Moreno Daza cod. 19195

Andres Felipe Dacuara Reyes cod. 19135

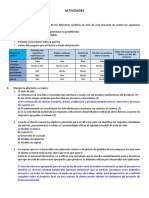

I. OBJETIVOS

Realizar código para lograr mostrar en la tarjeta FPGA una

ALU con dos operaciones, sumar y restar y adicional con dos 5. CODIGO:

compuertas una NOT y una NAND.

II. OBJETIVOS ESPECIFICOS

Aplicar los conocimientos y ejercicios propuestos en clase y

publicados en el portal web del docente.

Identificar eventos asociados a procesos secuenciales y

realizados.

LABORATORIO I

1. FPGA: es una matriz de puertas programables, dispositivo

que contiene bloques de lógica cuya conexión y funcionalidad

puede ser configurada mediante un leguaje VHDL.

2. VHDL: (Very High Speed Integrated Circuits) Es

un lenguaje de descripción de circuitos electrónicos digitales

que utiliza distintos niveles descripción de lenguaje. Esto

significa que VHDL permite acelerar el proceso de diseño.

3. Qué características tiene la FPGA: Cuenta con bloques de

entrada y salida. Los componentes de la FPGA son muy

versátiles, pueden funcionar a velocidades de medio billón de

operaciones por segundo y soportan transferencias de datos

de varios gigabits por segundo.

4. MATERIALES:

FPGA

Xilin

Sistemas Digitales Octubre de 2018

2

VII informe Sistemas Digitales

Sistemas Digitales Octubre de 2018

3

VII informe Sistemas Digitales

## Connected to Basys2 onBoard USB controller

#NET "EppAstb" LOC = "F2"; # Bank = 3

#NET "EppDstb" LOC = "F1"; # Bank = 3

#NET "EppWR" LOC = "C2"; # Bank = 3

#NET "EppWait" LOC = "D2"; # Bank = 3

#NET "EppDB<0>" LOC = "N2"; # Bank = 2

#NET "EppDB<1>" LOC = "M2"; # Bank = 2

#NET "EppDB<2>" LOC = "M1"; # Bank = 3

#NET "EppDB<3>" LOC = "L1"; # Bank = 3

#NET "EppDB<4>" LOC = "L2"; # Bank = 3

#NET "EppDB<5>" LOC = "H2"; # Bank = 3

#NET "EppDB<6>" LOC = "H1"; # Bank = 3

#NET "EppDB<7>" LOC = "H3"; # Bank = 3

DECLARACION DE PUERTOS

#

## clock pin for Basys2 Board

#

NET "CLK_IN" LOC = "B8"; # Bank = 0, Signal name = MCLK

## Pin assignment for DispCtl

#NET "uclk" LOC = "M6"; # Bank = 2, Signal name = UCLK

## Connected to Basys2 onBoard 7seg display

NET "CLK_IN" CLOCK_DEDICATED_ROUTE = FALSE;

#NET "seg<0>" LOC = "L14"; # Bank = 1, Signal name = CA

#NET "uclk" CLOCK_DEDICATED_ROUTE = FALSE;

#NET "seg<1>" LOC = "H12"; # Bank = 1, Signal name = CB

#

#NET "seg<2>" LOC = "N14"; # Bank = 1, Signal name = CC

## Pin assignment for EppCtl

#NET "seg<3>" LOC = "N11"; # Bank = 2, Signal name = CD

Sistemas Digitales Octubre de 2018

4

VII informe Sistemas Digitales

#NET "seg<4>" LOC = "P12"; # Bank = 2, Signal name = CE NET "A(3)" LOC = "G3"; # Bank = 3, Signal name = SW4

#NET "seg<5>" LOC = "L13"; # Bank = 1, Signal name = CF NET "B(0)" LOC = "B4"; # Bank = 3, Signal name = SW3

#NET "seg<6>" LOC = "M12"; # Bank = 1, Signal name = CG NET "B(1)" LOC = "K3"; # Bank = 3, Signal name = SW2

#NET "dp" LOC = "N13"; # Bank = 1, Signal name = DP NET "B(2)" LOC = "L3"; # Bank = 3, Signal name = SW1

# NET "B(3)" LOC = "P11"; # Bank = 2, Signal name = SW0

#NET "an<3>" LOC = "K14"; # Bank = 1, Signal name = AN3 #

#NET "an<2>" LOC = "M13"; # Bank = 1, Signal name = AN2 NET "RESET" LOC = "A7"; # Bank = 1, Signal name = BTN3

#NET "an<1>" LOC = "J12"; # Bank = 1, Signal name = AN1 #NET "CLK_IN" LOC = "M4"; # Bank = 0, Signal name = BTN2

#NET "an<0>" LOC = "F12"; # Bank = 1, Signal name = AN0 #NET "btn<1>" LOC = "C11"; # Bank = 2, Signal name = BTN1

# #NET "btn<0>" LOC = "G12"; # Bank = 0, Signal name = BTN0

## Pin assignment for LEDs #

NET "R(0)" LOC = "G1" ; # Bank = 3, Signal name = LD7 ## Loop back/demo signals

NET "R(1)" LOC = "P4" ; # Bank = 2, Signal name = LD6 ## Pin assignment for PS2

NET "R(2)" LOC = "N4" ; # Bank = 2, Signal name = LD5 #NET "PS2C" LOC = "B1" | DRIVE = 2 | PULLUP ; # Bank =

3, Signal name = PS2C

NET "R(3)" LOC = "N5" ; # Bank = 2, Signal name = LD4

#NET "PS2D" LOC = "C3" | DRIVE = 2 | PULLUP ; # Bank =

#NET "Led<3>" LOC = "P6" ; # Bank = 2, Signal name = LD3 3, Signal name = PS2D

#NET "Led<2>" LOC = "P7" ; # Bank = 3, Signal name = LD2 #

#NET "Led<1>" LOC = "M11" ; # Bank = 2, Signal name = LD1 ## Pin assignment for VGA

#NET "Led<0>" LOC = "M5" ; # Bank = 2, Signal name = LD0 #NET "HSYNC" LOC = "J14" | DRIVE = 2 | PULLUP ; # Bank =

1, Signal name = HSYNC

#

#NET "VSYNC" LOC = "K13" | DRIVE = 2 | PULLUP ; # Bank =

## Pin assignment for SWs 1, Signal name = VSYNC

NET "A(0)" LOC = "N3"; # Bank = 2, Signal name = SW7 #

NET "A(1)" LOC = "E2"; # Bank = 3, Signal name = SW6 #NET "OutRed<2>" LOC = "F13" | DRIVE = 2 | PULLUP ; #

Bank = 1, Signal name = RED2

NET "A(2)" LOC = "F3"; # Bank = 3, Signal name = SW5

Sistemas Digitales Octubre de 2018

5

VII informe Sistemas Digitales

#NET "OutRed<1>" LOC = "D13" | DRIVE = 2 | PULLUP ; # #NET "PIO<79>" LOC = "B7" | DRIVE = 2 | PULLUP ; # Bank =

Bank = 1, Signal name = RED1 1, Signal name = JB4

#NET "OutRed<0>" LOC = "C14" | DRIVE = 2 | PULLUP ; # #

Bank = 1, Signal name = RED0

#NET "PIO<80>" LOC = "A9" | DRIVE = 2 | PULLUP ; # Bank =

#NET "OutGreen<2>" LOC = "G14" | DRIVE = 2 | PULLUP ; # 1, Signal name = JC1

Bank = 1, Signal name = GRN2

#NET "PIO<81>" LOC = "B9" | DRIVE = 2 | PULLUP ; # Bank =

#NET "OutGreen<1>" LOC = "G13" | DRIVE = 2 | PULLUP ; # 1, Signal name = JC2

Bank = 1, Signal name = GRN1

#NET "PIO<82>" LOC = "A10" | DRIVE = 2 | PULLUP ; # Bank =

#NET "OutGreen<0>" LOC = "F14" | DRIVE = 2 | PULLUP ; # 1, Signal name = JC3

Bank = 1, Signal name = GRN0

#NET "PIO<83>" LOC = "C9" | DRIVE = 2 | PULLUP ; # Bank =

#NET "OutBlue<2>" LOC = "J13" | DRIVE = 2 | PULLUP ; # 1, Signal name = JC4

Bank = 1, Signal name = BLU2

#

#NET "OutBlue<1>" LOC = "H13" | DRIVE = 2 | PULLUP ; #

Bank = 1, Signal name = BLU1 #NET "PIO<84>" LOC = "C12" | DRIVE = 2 | PULLUP ; # Bank

= 1, Signal name = JD1

#

#NET "PIO<85>" LOC = "A13" | DRIVE = 2 | PULLUP ; # Bank

## Loop Back only tested signals = 2, Signal name = JD2

#NET "PIO<72>" LOC = "B2" | DRIVE = 2 | PULLUP ; # Bank = #NET "PIO<86>" LOC = "C13" | DRIVE = 2 | PULLUP ; # Bank

1, Signal name = JA1 = 1, Signal name = JD3

#NET "PIO<73>" LOC = "A3" | DRIVE = 2 | PULLUP ; # Bank = #NET "PIO<87>" LOC = "D12" | DRIVE = 2 | PULLUP ; # Bank

1, Signal name = JA2 = 2, Signal name = JD4

#NET "PIO<74>" LOC = "J3" | DRIVE = 2 | PULLUP ; # Bank = #

1, Signal name = JA3

#NET "PIO<75>" LOC = "B5" | DRIVE = 2 | PULLUP ; # Bank =

1, Signal name = JA4

#NET "PIO<76>" LOC = "C6" | DRIVE = 2 | PULLUP ; # Bank =

1, Signal name = JB1

#NET "PIO<77>" LOC = "B6" | DRIVE = 2 | PULLUP ; # Bank =

1, Signal name = JB2

#NET "PIO<78>" LOC = "C5" | DRIVE = 2 | PULLUP ; # Bank =

1, Signal name = JB3

Sistemas Digitales Octubre de 2018

6

VII informe Sistemas Digitales

III. CONCLUSIONES:

Durante la realización del presente trabajo, se

implementaron los procesos descritos en clase de lenguaje

VHDL, se programaron en la FPGA se realizó conexión de los

puertos haciendo posible su comunicación y se comprobó el

correcto funcionamiento del sistema implementado de una

ALU.

Sistemas Digitales Octubre de 2018

Você também pode gostar

- ACTIVIDAD No. 5. Limites FinitosDocumento11 páginasACTIVIDAD No. 5. Limites FinitosDAVID JIMENEZ ORTIZAinda não há avaliações

- Sintaxis y Semantica, Lenguajes de ProgramacionDocumento14 páginasSintaxis y Semantica, Lenguajes de Programacionpomelo09Ainda não há avaliações

- Actividad Semana 7Documento7 páginasActividad Semana 7Oscar DaliAinda não há avaliações

- Presentacion FreeRTOSDocumento79 páginasPresentacion FreeRTOSOscar Beltrán GómezAinda não há avaliações

- Guia TablasDocumento2 páginasGuia TablasShirley Andrea MENESES PATINOAinda não há avaliações

- Instalacion Elm327 Usb VgateDocumento9 páginasInstalacion Elm327 Usb VgateYang GomezAinda não há avaliações

- EvidencianESTUDIOnDEnCASOnnGLOSAnENnUNAnFACTURAnnMARITZA 476136a371431d7Documento2 páginasEvidencianESTUDIOnDEnCASOnnGLOSAnENnUNAnFACTURAnnMARITZA 476136a371431d7Maritza Mayorga100% (1)

- Bases de Datos Bibliograficas Diapositivas Yesid PeñaDocumento9 páginasBases de Datos Bibliograficas Diapositivas Yesid PeñaYeto PeñaAinda não há avaliações

- Outlook CalendarioDocumento13 páginasOutlook CalendarioCarlos J. LYAinda não há avaliações

- Cuadro ComparativoDocumento6 páginasCuadro ComparativoEdirmary ParraAinda não há avaliações

- ISI502 Orientaciones Actividad Sumativa Semana 4 Forma A 2022Documento3 páginasISI502 Orientaciones Actividad Sumativa Semana 4 Forma A 2022Carlos Eduardo Pérez CastroAinda não há avaliações

- Recetas Mexicanas para El 4 de JulioDocumento2 páginasRecetas Mexicanas para El 4 de JulioRodrigo BarrazaAinda não há avaliações

- 3 Base de Datos Upea 2020-65-80Documento16 páginas3 Base de Datos Upea 2020-65-80Vladimir Alarcon RamosAinda não há avaliações

- Catalina Mojica-77421510-1Documento3 páginasCatalina Mojica-77421510-1LAURA CATALINA MOJICA MONTOYAAinda não há avaliações

- Taller de Actividad Técnica de Aprendizaje Insercion de Imagen en Pagina WebDocumento4 páginasTaller de Actividad Técnica de Aprendizaje Insercion de Imagen en Pagina WebCarlos valencia valenciaAinda não há avaliações

- Redes neuronales, lógica difusa y control difusoDocumento12 páginasRedes neuronales, lógica difusa y control difusoJorge Alberto ParedesAinda não há avaliações

- Pagina WebDocumento6 páginasPagina WebCarlos FloresAinda não há avaliações

- Instalacion Linux MintDocumento15 páginasInstalacion Linux MintEnrique GrijalvaAinda não há avaliações

- Monografia de TelecomunicacionesDocumento8 páginasMonografia de TelecomunicacionesSergioAugustoBaldeonAinda não há avaliações

- Ciclo de vida de ActivityDocumento3 páginasCiclo de vida de ActivityRaúl Antelo JuradoAinda não há avaliações

- Búsqueda BibliográficaDocumento20 páginasBúsqueda BibliográficaVALERIA OSORNO ARROYAVEAinda não há avaliações

- Tarea Model de Ciclo de Vida - FinalDocumento3 páginasTarea Model de Ciclo de Vida - FinalJuan SilvaAinda não há avaliações

- TDSP LMCGDocumento2 páginasTDSP LMCGLaura Melisa Cañon GómezAinda não há avaliações

- Android PieDocumento4 páginasAndroid PieJoseph Lewis TRAinda não há avaliações

- Packet Tracer Configure Ajustes Iniciales Del SwitchDocumento5 páginasPacket Tracer Configure Ajustes Iniciales Del SwitchMoises PinedaAinda não há avaliações

- Cisco TemasDocumento30 páginasCisco TemasLourdez ViGilAinda não há avaliações

- Ejemplo Pilas y ColasDocumento13 páginasEjemplo Pilas y Colassilvergirl137Ainda não há avaliações

- Estudio de Los Requerimientos Técnicos para Integrar Máquinas Vending Con Recarga de Tarjetas "Tu Llave"Documento4 páginasEstudio de Los Requerimientos Técnicos para Integrar Máquinas Vending Con Recarga de Tarjetas "Tu Llave"ANDRES GERARDO PEREZ ROJASAinda não há avaliações

- Saberes Previo InformaticaDocumento15 páginasSaberes Previo InformaticaAlexa OsorioAinda não há avaliações

- Tesis - 1° PresentacionDocumento5 páginasTesis - 1° PresentacionAnthony Paoly Garrido MauriolaAinda não há avaliações