Escolar Documentos

Profissional Documentos

Cultura Documentos

Design and Analysis of Two-Stage OP-AMP in 180nm and 45nm Technology

Enviado por

Nam Luu Nguyen NhatTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Design and Analysis of Two-Stage OP-AMP in 180nm and 45nm Technology

Enviado por

Nam Luu Nguyen NhatDireitos autorais:

Formatos disponíveis

International Journal of Engineering Research & Technology (IJERT)

ISSN: 2278-0181

Vol. 4 Issue 05, May-2015

Design and Analysis of CMOS Two Stage

OP-AMP in 180nm and 45nm Technology

R Bharath Reddy Shilpa K Gowda

M.Tech, Dept. of ECE, Asso Prof, Dept of ECE

S J B Institute of technology S J B Institute of technology

Bengaluru, India Bengaluru, India

Abstract— This paper presents the buffered CMOS two stage

op-amp which uses 180nm and 45nm process for design and

analysis of CMOS two stage op-amp. Keeping 1.8V power

supply, 20µA bias current, aspect ratio W/L, slew rate 20V/µs,

input common mode ratio constant. The trade-off among

various parameters such as Open loop gain, Phase margin,

Gain Bandwidth Product and Power consumption are

measured. It has been demonstrated that due to recent

development through scaling the size of transistors decreases

power dissipated through the device also decreases. This

design has been carried out in Cadence design tools.

Keywords—CMOS Analog circuit, buffered Opamp,

180nm,45nm, CADENCE, Power consumption

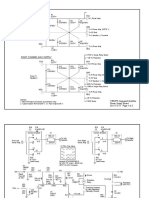

Fig1. General block diagram of two stage Op-Amp

I.INTRODUCTION

The operational amplifier, which has become one of the II. LITERATURE SURVEY

most versatile and important building blocks in analog In [4], document gives the information about an unbuffered

circuit design. Operational amplifiers are amplifiers that (Operational-transconductance amplifiers or OTAs) two

have sufficiently high forward gain so that when negative stage operational amplifier which was designed for

feedback is applied, the closed-loop transfer function is moderate DC gain, high output swing and reasonable open

practically independent of gain. Operational amplifier that loop Gain Band product (GBW).Results shows that a two

use two or more gain stages are widely used when higher stage op-amp has been designed with gain of 48dB, unity

gains are needed. One of the most popular op amps is a gain frequency of 40MHz, Phase margin of

two-stage op amp. CMOS op amps are very similar in 89degree.Design has been carried out in GPDK180

architecture to their bipolar counterparts. A good portion of Cadence design tools.

overall gain is provided by differential-input stage, which

improves noise and offset performance. If op-amp drive a In [5], document gives the information about an operational

low-resistance load, the second stage must be followed by amplifier which uses an adaptive biasing circuitry along

a buffer stage whose objective is to lower the output with an auxiliary circuit to improve the slew rate. Auxiliary

resistance and maintain a large swing. Biasing circuits are circuit gets used when there is large transient or slewing

provided to establish the proper operating point for each period. Auxiliary circuit improves slew rate and at high

transistor in its quiescent state. Compensation is required to frequencies less power is dissipated. Results shows that a

achieve stable closed-loop performance. two stage op-amp has been designed with slew rate of

31.31V/µs, gain of 40.09dB,unity gain frequency of

52MHz,Phase margin of 88degree.Design has been carried

out in GPDK90 Cadence design tools.

In [6], document gives the information about a buffered

two stage operational amplifier which was designed in both

180nm and 45nm.And the results of these designs have

been compared. Results shows that 180nm two stage op-am

gives gain of 47.85dB,unity gain frequency of

668.42MHz,Phase margin of 63.22 degree and 45nm two

IJERTV4IS051024 www.ijert.org 1100

(This work is licensed under a Creative Commons Attribution 4.0 International License.)

International Journal of Engineering Research & Technology (IJERT)

ISSN: 2278-0181

Vol. 4 Issue 05, May-2015

stage op-am gives gain of 52.68dB,unity gain frequency of

2.22GHz,Phase margin of 60.92 degree. Power dissipated

through 45nm is very less compared to180nm. Design has

been carried out in GPDK180 and GPDK45 Cadence

design tools.

In [7], document gives the information about an unbuffered

(Operational-transconductance amplifiers or OTAs) two

stage operational amplifier which was designed for gain of

71dB,unity gain frequency of 37KHz,Slew Rate of

2.344V/µsec and power dissipation of 10mW. Design has

been carried out in GPDK180 Cadence design tools.

III. DESIGN PROCEDURE

Relationships describing the op-amp performance[1]:

𝐼5

Slew rate SR = .(i)

𝐶𝑐

Fig.2 Two stage Op-Amp

𝑔𝑚1 −2𝑔𝑚1

First − stage gain Av1 = − = .(ii)

𝑔𝑑𝑠2 +𝑔𝑚4 𝐼5 (𝜆2 +𝜆4 )

1) The design procedure begins by choosing a device

−𝑔𝑚6 −𝑔𝑚6

Second-stage Av2 = = .(iii) length to be used throughout the circuit.

𝑔𝑚6 +𝑔𝑚7 𝐼6 (𝜆6 +𝜆7 )

𝑔𝑚1 2) The minimum value for the compensation capacitor Cc

Gain bandwidth GB = .(iv) should be 0.22 times more than CL to get phase margin 60º.

𝐶𝑐

−𝑔𝑚6 3) Based on slew rate requirements the value of tail current

Output pole p2 = . (v)

𝐶𝐿 I5 is determined.

𝑔𝑚6

RHP zero Z1 = .(vi) 4) The aspect ratio of M3 can be determined by positive

𝐶𝑐

input common mode ratio range by using the equation (vii).

𝐼5

Positive CMR Vin(max) = Vdd -√ + |𝑉𝑡 |(max) 5) Aspect ratio of M1 can be determined through

𝛽3

transconductance gm1 by using equation (iv).

+VT1(min) .(vii)

5) To calculate the saturation voltage of transistor M5

Negative CMR Vin(min) =Vss+ Vt1(max)+VDs5(sat) negative input common mode ratio range is used by

equation (viii).

𝐼

+√ 5 .(viii) 6) For reasonable phase margin, the value of g m6 is

𝛽 1

approximately ten times the input stage transconductance

2𝐼𝑑𝑠

gm1.To achieve proper mirroring of the first stage current

Saturation voltage VDS(sat) = √ .(ix) mirror load of M3 and M4 requires VSG4 = VSG6. By VSG6 we

𝛽

can get the aspect ratio of M6.

7) The device size of M7 can be determined from the I 6

current flowing through M6 and balanced equation.

8) The total amplifier gain against the specifications is

given by[1]

(2)(𝑔𝑚2 )(𝑔𝑚6 )

Av = 𝐼

5 (𝜆2 +𝜆4 )𝐼6 ( 𝜆6 +𝜆7 )

IJERTV4IS051024 www.ijert.org 1101

(This work is licensed under a Creative Commons Attribution 4.0 International License.)

International Journal of Engineering Research & Technology (IJERT)

ISSN: 2278-0181

Vol. 4 Issue 05, May-2015

IV. SIMULATION RESULTS

Fig.6 Open loop gain and Phase margin in 45nm .

Fig.3Schematic diagram of two stage CMOS Op-Amp

Fig.7 Transient Analysis of 45nm.

Fig3. shows schematic diagram of two stage CMOS op-

amp which was designed according to the procedure. For

Fig.4 Open loop gain and Phase margin in 180nm . the frequency response plot, an ac signal of 1V is swept

with 5 points per decade from a frequency of 100Hz to

100MHz. Fig4 illustrates the frequency response of 180nm

op-amp which shows a dc gain in dB versus frequency in

Hz(in log scale) and phase margin of Op-Amp in open

loop. The dc gain is found to be 64.95dB and phase margin

600 which is good enough for an Op-Amp operating at a

high frequency. A dc gain of 64.95dB at unity gain

frequency of 34MHz and slew rate 20v/µs is excellent for

an Op-Amp when all the other parameters are also set at an

optimized value.Fig5.shows the transient analysis of

180nm CMOS Op-Amp. Similarly Fig.6 illustrates the

frequency response of 45nm op-amp which shows a dc

gain in dB versus frequency in Hz(in log scale) and phase

margin of Op-Amp in open loop. The dc gain is found to be

45 dB and phase margin 750 which is good enough for an

Op-Amp operating at a high frequency. Fig5.shows the

transient analysis of 45nm CMOS Op-Amp Power

Fig.5Transient Analysis of 180nm consumed by 45nm is very less compared to 180nm.

IJERTV4IS051024 www.ijert.org 1102

(This work is licensed under a Creative Commons Attribution 4.0 International License.)

International Journal of Engineering Research & Technology (IJERT)

ISSN: 2278-0181

Vol. 4 Issue 05, May-2015

TABLE I. COMPARISON WITH PREVIOUS RESULTS REFERENCES

[1] P. Allen and D. Holberg, CMOS Analog Circuit Design. New York:

Results Designed [4] [5] [6] [7] Holt Rinehart and Winston, 1987.

two-stage [2] Behzad Razavi, Design of Analog CMOS Integrated circuits,

Op-amp McGraw-Hill Company, New York, 2001.

[3] David Johns, Ken Martin, Analog integrated circuit design, John

Wiley & Sons, New York,1997.

Technology(nm) 180 45 180 90 180 180 [4] D. Nageshwar rao, K. Suresh Kumar, Y. Rajasree Rao, G. Jyothi.

“Implementation and simulation of CMOS two stage operational

Power supply(V) 1.8 1.8 3.5 1.2 - 1.8 amplifier”.

[5] Biplab Panda, S. K. Dash, S. N. Mishra. “High Slew Rate op-amp

design for low power Applications”.

Bias current(µA) 20 20 - - 160 - [6] Siddharth, Mehul Garg, Aditya Gahlaut. “ Comparative Study of

CMOS Op-Amp in 45nm And 180 Nm Technology”.

Cc(fF) 600 600 - - 100 [7] Shweta karnik, Ajay kumar kushwaha, Pramod kumar jain,D.S.Ajnar.

“Design of Operational Trans conductance Amplifier in 0.18μm

Open loop gain(dB) 65 45 48 40 53 71 Technology”

[8] Sanjay Kumar, Pathak Jay, Rajendra Prasad. “ Gain improvement

of two stage opamp through body bias in 45nm cmos technology ”.

Phase margin(deg) 60 75 89 89 60 [9] Muhammad Syamsi Mohd Taufik,Ahmad anwar Zaimuddin, Anis

Nurashikin Nordin.“Design and simulation of CMOS two-stage op-

amp for MEMS resonator”.

Gain Bandwidth 34 55 40 52 668 .037 [10] Basanta Bhowmik, Manisha Pattanaik, Pankaj Srivastava. “A Low

Product (Mhz) Power Low Noise Two Stage CMOS Operational Amplifier for

Biopotential Signal Acquisition System”.

Slew rate(v/µs) 20 20 - 31 - 2.34

ICMR(+)(V) 1.6 1.6 - - 1.6 -

Mr. R Bharath Reddy Received B.E Degree from

ICMR(-)(V) 0.8 0.8 - - 0.8 - BMS Institute of Technology, Bangalore and presently

pursuing M.Tech in VLSI Design and Embedded Systems

Power consumption 301 142 - 92 3582 from Dept. of ECE, SJBIT, Bangalore, Karnataka, India.

(µW)

Mrs. Shilpa K Gowda Received M.tech Degree from

SJCIT, Chikkaballapur and presently working as associate

professor in Dept. of ECE, SJBIT, Bangalore, Karnataka,

V.CONCLUSION India.

CMOS two stage op-amp is simulated and analyzed in both

180nm and 45nm. Suitable effort is made to improve the

open loop gain, phase margin, gain bandwidth product

keeping initial parameters and slew rate constant for both

180nm and 45nm. .The 180nm CMOS two stage op-amp is

giving high performance with gain 65dB,phase margin

50deg, Gain Bandwidth Product 30MHz, power

consumption 300µW which is very much suitable for

switched capacitor filters, analog to digital converters and

instrumentation amplifiers. Results shows power

consumption through 45nm op-amp is very less compared

to 180nm.

IJERTV4IS051024 www.ijert.org 1103

(This work is licensed under a Creative Commons Attribution 4.0 International License.)

Você também pode gostar

- Transistor Amplifier SummaryDocumento1 páginaTransistor Amplifier SummaryJhonAinda não há avaliações

- EC2 Exp2 F09Documento17 páginasEC2 Exp2 F09Nurul Hanim HashimAinda não há avaliações

- EKV v2.6 Parameter Extraction Tutorial Wladyslaw Grabinski: Geneva Modeling Center MotorolaDocumento15 páginasEKV v2.6 Parameter Extraction Tutorial Wladyslaw Grabinski: Geneva Modeling Center MotorolaMohammad Ayatullah MaktoomAinda não há avaliações

- Research Paper On Two Stage Single Ended CMOS AmplifierDocumento4 páginasResearch Paper On Two Stage Single Ended CMOS AmplifierDilip MathuriaAinda não há avaliações

- (Report) Design of A Low-Power Asynchronous SAR ADC in 45 NM CMOS TechnologyDocumento50 páginas(Report) Design of A Low-Power Asynchronous SAR ADC in 45 NM CMOS TechnologyMurod KurbanovAinda não há avaliações

- Kemper Profiler Stage - Factory Rigs - SeznamDocumento69 páginasKemper Profiler Stage - Factory Rigs - SeznampavelscribdAinda não há avaliações

- Design of 12-Bit DAC Using CMOS TechnologyDocumento5 páginasDesign of 12-Bit DAC Using CMOS TechnologysanthoshAinda não há avaliações

- OTA DesignDocumento18 páginasOTA DesignAnandAinda não há avaliações

- TCADDocumento33 páginasTCADvpsampathAinda não há avaliações

- Design of Microwave LNADocumento86 páginasDesign of Microwave LNANguyễn Trần TuấnAinda não há avaliações

- Cmos Two Stage OpamppublishedDocumento5 páginasCmos Two Stage Opamppublisheddeepak pandeyAinda não há avaliações

- Low Voltage CMOS SAR ADC DesignDocumento68 páginasLow Voltage CMOS SAR ADC DesignAyush SukaniAinda não há avaliações

- Two-Stage CMOS Op-Amp Circuit Design - Jianfeng SunDocumento17 páginasTwo-Stage CMOS Op-Amp Circuit Design - Jianfeng Sunjianfeng sun100% (2)

- Signal Integrity BasicsDocumento39 páginasSignal Integrity BasicsArvind HanumantharayappaAinda não há avaliações

- Amplifier Project GradDocumento5 páginasAmplifier Project Gradمحمد قاسم نفل سميرAinda não há avaliações

- Two-Stage Operational Amplifier Design Using Gm/Id MethodDocumento7 páginasTwo-Stage Operational Amplifier Design Using Gm/Id Methodabhinav kumarAinda não há avaliações

- Design and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierDocumento5 páginasDesign and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierChristian Montano GalvezAinda não há avaliações

- Question PDFDocumento12 páginasQuestion PDFjushwanth100% (1)

- Design of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)Documento2 páginasDesign of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)Shahin ShahAinda não há avaliações

- Parameters Extraction of Semiconductor DevicesDocumento75 páginasParameters Extraction of Semiconductor DevicesCarlos RodriguezAinda não há avaliações

- Vlsi Test Structures For Process CharacterizationDocumento76 páginasVlsi Test Structures For Process CharacterizationSumeet SauravAinda não há avaliações

- Cmos Electronic PDFDocumento356 páginasCmos Electronic PDFJustin WilliamsAinda não há avaliações

- Performance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using Cmos Technologies Using CadanceDocumento8 páginasPerformance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using Cmos Technologies Using CadanceAnonymous kw8Yrp0R5r100% (1)

- Spectral PLL Built-In Self-Test For Integrated Cellular TransmittersDocumento231 páginasSpectral PLL Built-In Self-Test For Integrated Cellular TransmittersChipmuenkAinda não há avaliações

- 018 RF Model Document V2d2Documento91 páginas018 RF Model Document V2d2Rogelio Manuel Higuera GonzalezAinda não há avaliações

- Device Parameter Extraction of 14Nm, 10nmand 7Nm FinfetDocumento43 páginasDevice Parameter Extraction of 14Nm, 10nmand 7Nm FinfetKrisumraj PurkaitAinda não há avaliações

- A 4.596 GHZ, High Slew Rate, Ultra Low PowerDocumento6 páginasA 4.596 GHZ, High Slew Rate, Ultra Low PowerAlberto DanAinda não há avaliações

- 14 NMDocumento23 páginas14 NMNikhilAKothariAinda não há avaliações

- Cmos Analog Ic Design Course Plan NewDocumento9 páginasCmos Analog Ic Design Course Plan Newjim2001Ainda não há avaliações

- Band Gap ReferencesDocumento115 páginasBand Gap ReferencesNam Luu Nguyen NhatAinda não há avaliações

- An Overview of Design Techniques For CMOS Phase DetectorsDocumento4 páginasAn Overview of Design Techniques For CMOS Phase DetectorsfypcommAinda não há avaliações

- RCA VICTOR MODELS 7-BX-6, 7-BX-7 (Ch. RC-1161, A) Repair ManualDocumento4 páginasRCA VICTOR MODELS 7-BX-6, 7-BX-7 (Ch. RC-1161, A) Repair Manualrop703406100% (1)

- An Adaptive Biased Single-Stage CMOS Operational Amplifier With A Novel Rail-To-Rail Constant-Gm Input StageDocumento8 páginasAn Adaptive Biased Single-Stage CMOS Operational Amplifier With A Novel Rail-To-Rail Constant-Gm Input Stagekhausar1785Ainda não há avaliações

- A 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliDocumento4 páginasA 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliAnika TahsinAinda não há avaliações

- Low Power Optimization of Full Adder Circuit Based On Gdi Logic For Biomedical ApplicationsDocumento11 páginasLow Power Optimization of Full Adder Circuit Based On Gdi Logic For Biomedical ApplicationsIJAR JOURNALAinda não há avaliações

- Design High Speed, Low Noise, Low Power Two Stage CMOSDocumento5 páginasDesign High Speed, Low Noise, Low Power Two Stage CMOSsanjeevsoni64Ainda não há avaliações

- MIM Cap ModelDocumento4 páginasMIM Cap ModelDuc DucAinda não há avaliações

- CMOS Design RulesDocumento21 páginasCMOS Design Rulesrakheep123Ainda não há avaliações

- Fully Differential CMOS Voltage AmplifierDocumento16 páginasFully Differential CMOS Voltage AmplifierAjit Narwal0% (1)

- Ese570 Mos Theory p206Documento41 páginasEse570 Mos Theory p206premkumar8719Ainda não há avaliações

- Cascode CS LNA Design ExampleDocumento8 páginasCascode CS LNA Design ExampleAnonymous VG6Zat1oAinda não há avaliações

- Differential Amplifier LayoutDocumento9 páginasDifferential Amplifier LayoutFrancisco De KamimoreAinda não há avaliações

- High Speed Vlsi DesignDocumento93 páginasHigh Speed Vlsi DesignDr Narayana Swamy RamaiahAinda não há avaliações

- A CMOS Bandgap Reference Circuit With Sub-1V OperationDocumento5 páginasA CMOS Bandgap Reference Circuit With Sub-1V Operationbooky_mookyAinda não há avaliações

- Two Stage Op-AmpDocumento4 páginasTwo Stage Op-AmpShreerama Samartha G BhattaAinda não há avaliações

- Lecture 12 SRAMDocumento37 páginasLecture 12 SRAMSachin MalikAinda não há avaliações

- Comparative Analysis of Different Architectures of CMOS ComparatorDocumento4 páginasComparative Analysis of Different Architectures of CMOS Comparatorj4everAinda não há avaliações

- Design and Simulation of LNA: (Cadence Spectre RF)Documento19 páginasDesign and Simulation of LNA: (Cadence Spectre RF)Kushal GajavellyAinda não há avaliações

- ECE 410: VLSI Design Course Lecture Notes: (Uyemura Textbook)Documento54 páginasECE 410: VLSI Design Course Lecture Notes: (Uyemura Textbook)BHANU PRAKASH0% (1)

- PROJECT1 S 2013 v2 PDFDocumento4 páginasPROJECT1 S 2013 v2 PDFHarshal SinghAinda não há avaliações

- Eletronics Lab Report - Current MirrorDocumento3 páginasEletronics Lab Report - Current MirrorThan Lwin AungAinda não há avaliações

- CMOS CM & Biasing CircuitsDocumento50 páginasCMOS CM & Biasing Circuitsabhi_jAinda não há avaliações

- Silicon FINFET Device in 3DDocumento9 páginasSilicon FINFET Device in 3DbhataviAinda não há avaliações

- Flash AdcDocumento15 páginasFlash AdcbittibssiAinda não há avaliações

- Folded Cascode ChopperDocumento4 páginasFolded Cascode ChoppergirishknathAinda não há avaliações

- Analog Integrated Circuit Design: Nagendra KrishnapuraDocumento26 páginasAnalog Integrated Circuit Design: Nagendra KrishnapuraAnkit Bhoomia0% (1)

- Advanced Communication Lab Manual: Visvesvaraya Technological UniversityDocumento46 páginasAdvanced Communication Lab Manual: Visvesvaraya Technological UniversityPunith Gowda M B100% (2)

- Cmos Analog Ic Design Problems and SolutionsDocumento206 páginasCmos Analog Ic Design Problems and SolutionsEdsel Silva100% (1)

- D-Band Frequency Tripler For Passive Imaging - Final 13th JulyDocumento4 páginasD-Band Frequency Tripler For Passive Imaging - Final 13th JulyTapas SarkarAinda não há avaliações

- Lecture 5Documento47 páginasLecture 5Ershad ShaikAinda não há avaliações

- Signal Integrity in The Real WorldDocumento52 páginasSignal Integrity in The Real WorldpatarinwAinda não há avaliações

- R09-Cmos Analog and Mixed Signal DesignDocumento1 páginaR09-Cmos Analog and Mixed Signal DesignbalashyamuAinda não há avaliações

- swapping Using Ref //swap - CS: Using Namespace Class Public Int Public Int Public Int IntDocumento4 páginasswapping Using Ref //swap - CS: Using Namespace Class Public Int Public Int Public Int IntNam Luu Nguyen NhatAinda não há avaliações

- A Low-Quiescent Current Full On-Chip 1.2 V CMOS Low Drop-Out RegulatorDocumento2 páginasA Low-Quiescent Current Full On-Chip 1.2 V CMOS Low Drop-Out RegulatorNam Luu Nguyen NhatAinda não há avaliações

- Design of Low Voltage Low Dropout Regulator With Wide Band High PSR Characteristic ISICT06Documento4 páginasDesign of Low Voltage Low Dropout Regulator With Wide Band High PSR Characteristic ISICT06Nam Luu Nguyen NhatAinda não há avaliações

- What Are Main Facts and Information About London?: River ThamesDocumento10 páginasWhat Are Main Facts and Information About London?: River ThamesNam Luu Nguyen NhatAinda não há avaliações

- Op-Amp Circuits, and Circuit Analysis. How To Measure: 2-Stage OpampDocumento2 páginasOp-Amp Circuits, and Circuit Analysis. How To Measure: 2-Stage OpampShachi P GowdaAinda não há avaliações

- Factory Content RIGSDocumento26 páginasFactory Content RIGSnurzacotreAinda não há avaliações

- Tutorial Sheet #1, Unit-1: Give The Definition of OPAMPDocumento5 páginasTutorial Sheet #1, Unit-1: Give The Definition of OPAMPNirmal Kumar PandeyAinda não há avaliações

- Power Supply BoardDocumento2 páginasPower Supply BoardciohaniAinda não há avaliações

- Super Mini Micro UCD DiscreteDocumento1 páginaSuper Mini Micro UCD DiscreteAnggas HadaianAinda não há avaliações

- ESC201 UDas Lec24Corrected OpAmp Aps PDFDocumento6 páginasESC201 UDas Lec24Corrected OpAmp Aps PDFPk KumarAinda não há avaliações

- G1 SRV - Texas Flood PDFDocumento1 páginaG1 SRV - Texas Flood PDFdimaswolv100% (1)

- Annamacharya Institute of Technology & Sciences TirupatiDocumento1 páginaAnnamacharya Institute of Technology & Sciences Tirupatisreekanth2728Ainda não há avaliações

- Chapter 12Documento38 páginasChapter 12Deivasigamani SubramaniyanAinda não há avaliações

- ECADDocumento110 páginasECADJanica Janelle ReloxeAinda não há avaliações

- Comsats University Islamabad Abbottabad Campus Lab AssigmentDocumento10 páginasComsats University Islamabad Abbottabad Campus Lab Assigmentyaseen ayazAinda não há avaliações

- Lab 7Documento3 páginasLab 7Walid Mohammed Suliman100% (1)

- Reference: OPAMP and Linear Integrated Circuits by Ramakant A. Gayakwad, PHIDocumento27 páginasReference: OPAMP and Linear Integrated Circuits by Ramakant A. Gayakwad, PHIchandra prakash purbiaAinda não há avaliações

- Weights N Dims - Mesa Boogie AmpsDocumento1 páginaWeights N Dims - Mesa Boogie AmpsdjgiumixAinda não há avaliações

- Laporan OpAmp Elektro TelekomunikasiDocumento9 páginasLaporan OpAmp Elektro Telekomunikasi2C JTD05 Bayu Eka SetyowatiAinda não há avaliações

- Eee2204 Experiment 3 SlidesDocumento27 páginasEee2204 Experiment 3 SlidesMohaimenul SohanAinda não há avaliações

- Audio PDFDocumento166 páginasAudio PDFZoranBogdanovicAinda não há avaliações

- Modul 9 Op AmpDocumento23 páginasModul 9 Op AmpassaAinda não há avaliações

- Diff Amp MultistageDocumento6 páginasDiff Amp MultistageBink Bonk0% (1)

- Difference Between Amplifier and Op-AmpDocumento16 páginasDifference Between Amplifier and Op-AmpNauman bajwaAinda não há avaliações

- Schuler Electronics Instructor CH08 Amplifiers Part 3Documento28 páginasSchuler Electronics Instructor CH08 Amplifiers Part 3Kumbirayi Nyachionjeka100% (1)

- Applied Electronics II: Chapter 1: Feedback AmplifiersDocumento200 páginasApplied Electronics II: Chapter 1: Feedback Amplifiersabel berhanemeskelAinda não há avaliações

- 400W at 4 Ohm MOSFET Amplifier - EwbDocumento13 páginas400W at 4 Ohm MOSFET Amplifier - EwbRaquel RodriguesAinda não há avaliações

- CH 10 FeebackDocumento127 páginasCH 10 Feeback鄭又嘉Ainda não há avaliações

- 100 Wwith 2 SC3281Documento1 página100 Wwith 2 SC3281CirrusVanceAinda não há avaliações

- Kef psw-2500Documento13 páginasKef psw-2500Ferenc HanolAinda não há avaliações

- EE201 Ch5 Operational Amplifiers (Part 1)Documento18 páginasEE201 Ch5 Operational Amplifiers (Part 1)Thịnh Nguyễn ViếtAinda não há avaliações