Escolar Documentos

Profissional Documentos

Cultura Documentos

9A04306 Digital Logic Design2

Enviado por

Mahaboob SubahanDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

9A04306 Digital Logic Design2

Enviado por

Mahaboob SubahanDireitos autorais:

Formatos disponíveis

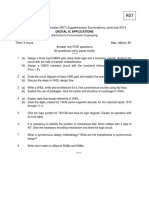

Code: 9A04306 SS

B.Tech II Year II Semester (R09) Supplementary Examinations January/February 2014

DIGITAL LOGIC DESIGN

(Computer Science and Engineering)

Time: 3 hours Max. Marks: 70

Answer any FIVE questions

All questions carry equal marks

*****

1 (a) Add the following using the 2’s complement method:

(i) and

(ii) and

(b) Write a short note on weighted and non-weighted codes.

(c) Express 324 in gray code form.

2 (a) If , then prove that .

(b) Find the complement of the expression

(c) Obtain the canonical product of sum expression of

3 (a) Obtain minimal sop expression for the function:

(b) Realize the following function using multilevel NAND-NAND network:

.

4 (a) Draw the logic diagram of 4-bit carry look ahead adder and explain.

(b) What is meant by a decoder? Explain BCD to decimal decoder.

5 (a) Explain the operation of a master - slave flip flop and show how the race around

condition is eliminated in it.

(b) Differentiate combinational and sequential circuits.

(c) What do you understand by state assignment?

6 (a) What is a ripple counter? Draw the logic diagram of a 4-bit binary ripple counter using

flip flops that trigger on the positive edge transition. Explain.

(b) What is a shift register? Name and explain different types of shift registers.

7 (a) Draw the basic circuit of a ROM cell and explain its working.

(b) What is a PLD? What are the steps used for implementing combinational circuit using

PLA?

8 (a) Design an asynchronous sequential circuit that has two inputs and one output .

The output if changes from 0 to 1, if changes from 0 to 1, and

otherwise. Realize the circuit using D flip flops.

(b) Explain the method to eliminate static hazard in an asynchronous circuit with an

example.

*****

Você também pode gostar

- 9A04306 Digital Logic Design3Documento1 página9A04306 Digital Logic Design3Mahaboob SubahanAinda não há avaliações

- 9A04401 Switching Theory & Logic Design1Documento1 página9A04401 Switching Theory & Logic Design1subbuAinda não há avaliações

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxNo EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxNota: 4 de 5 estrelas4/5 (2)

- SS 9A04306 Digital Logic DesignDocumento1 páginaSS 9A04306 Digital Logic DesignMahaboob SubahanAinda não há avaliações

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsNo EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsNota: 5 de 5 estrelas5/5 (1)

- 9A04306 Digital Logic DesignDocumento2 páginas9A04306 Digital Logic DesignsivabharathamurthyAinda não há avaliações

- 9A04306 Digital Logic Design1Documento4 páginas9A04306 Digital Logic Design1Mahaboob SubahanAinda não há avaliações

- DF - Summer 2020Documento2 páginasDF - Summer 2020Logo StudioAinda não há avaliações

- Jntuk 2 1 DLD Nov 2017 Q.PDocumento5 páginasJntuk 2 1 DLD Nov 2017 Q.PRoopa Krishna ChandraAinda não há avaliações

- ICT 9A04306 Digital Logic DesignDocumento1 páginaICT 9A04306 Digital Logic DesignMahaboob SubahanAinda não há avaliações

- 9A04504 Digital IC Applications6Documento4 páginas9A04504 Digital IC Applications6subbuAinda não há avaliações

- RT 21053112016Documento4 páginasRT 21053112016RaunaqAinda não há avaliações

- 9A12301 Digital Logic Design and Computer OrganizationDocumento4 páginas9A12301 Digital Logic Design and Computer OrganizationsivabharathamurthyAinda não há avaliações

- Rr310403-Digital Ic ApplicationsDocumento1 páginaRr310403-Digital Ic ApplicationssivabharathamurthyAinda não há avaliações

- 9a04306-Digital Logic DesignDocumento1 página9a04306-Digital Logic DesignSheikh Noor MohammadAinda não há avaliações

- Seat No.: InstructionsDocumento4 páginasSeat No.: InstructionsYogesh KuteAinda não há avaliações

- Be Winter 2020Documento2 páginasBe Winter 2020SonuAinda não há avaliações

- LDCA Previous Year PaperDocumento4 páginasLDCA Previous Year Paperflipkart6392Ainda não há avaliações

- 9A04504 Digital IC Applications4Documento1 página9A04504 Digital IC Applications4subbuAinda não há avaliações

- R7210504 Digital Logic DesignDocumento1 páginaR7210504 Digital Logic DesignsivabharathamurthyAinda não há avaliações

- 22323-2019-Winter-Question-Paper (Msbte Study Resources)Documento3 páginas22323-2019-Winter-Question-Paper (Msbte Study Resources)Parth patkarAinda não há avaliações

- R7310404 Digital IC ApplicationsDocumento1 páginaR7310404 Digital IC ApplicationssubbuAinda não há avaliações

- Digital Ic Applications: B.Tech II Year II Semester (R07) Supplementary Examinations, April/May 2013Documento1 páginaDigital Ic Applications: B.Tech II Year II Semester (R07) Supplementary Examinations, April/May 2013subbuAinda não há avaliações

- R7220404 Switching Theory and Logic DesignDocumento1 páginaR7220404 Switching Theory and Logic DesignsivabharathamurthyAinda não há avaliações

- QBank DPSD cs2202Documento6 páginasQBank DPSD cs2202kunarajAinda não há avaliações

- DIGITAL ELECTRONICS NovemberDecember-2020Documento1 páginaDIGITAL ELECTRONICS NovemberDecember-2020ethanAinda não há avaliações

- R7310404 Digital IC Applications2Documento1 páginaR7310404 Digital IC Applications2subbuAinda não há avaliações

- Code - No: 43216: Jawaharlal Nehru Technological University HyderabadDocumento1 páginaCode - No: 43216: Jawaharlal Nehru Technological University HyderabadKareem KhanAinda não há avaliações

- WWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic DesignDocumento4 páginasWWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic Designbadiganti tejakrishnaAinda não há avaliações

- 9A04401 Switching Theory & Logic DesignDocumento1 página9A04401 Switching Theory & Logic DesignsivabharathamurthyAinda não há avaliações

- R7221004 Digital IC Applications7Documento1 páginaR7221004 Digital IC Applications7subbuAinda não há avaliações

- TED (15) 3133 qp-1Documento2 páginasTED (15) 3133 qp-1Anna JoseAinda não há avaliações

- March-2022 (1) - 231101 - 193459Documento1 páginaMarch-2022 (1) - 231101 - 193459nanikarthikreddy2002Ainda não há avaliações

- Sample Question Paper Digital Techniques PDFDocumento5 páginasSample Question Paper Digital Techniques PDFAshutosh PatilAinda não há avaliações

- BCS302Documento2 páginasBCS302sagarblazaAinda não há avaliações

- Switching Theory and Logic Design April 2019 PDFDocumento4 páginasSwitching Theory and Logic Design April 2019 PDFTulasi LassiAinda não há avaliações

- 3 Hours / 70 Marks: Seat NoDocumento4 páginas3 Hours / 70 Marks: Seat No58 EX Ramawat PankajAinda não há avaliações

- CO Previous Year O.UDocumento7 páginasCO Previous Year O.UVistasAinda não há avaliações

- 2019 Summer Question Paper (Msbte Study Resources)Documento3 páginas2019 Summer Question Paper (Msbte Study Resources)Ashutosh PatilAinda não há avaliações

- Gujarat Technological UniversityDocumento2 páginasGujarat Technological UniversityJaineshAinda não há avaliações

- 9A04306 Digital Logic DesignDocumento4 páginas9A04306 Digital Logic DesignsivabharathamurthyAinda não há avaliações

- Digital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Documento4 páginasDigital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Vikash KumarAinda não há avaliações

- Computer Organization and ArchitectureDocumento3 páginasComputer Organization and ArchitecturecoolshubupaunikarAinda não há avaliações

- MST-I or II Paper FormatDocumento2 páginasMST-I or II Paper FormatAnonymous mRCnYKz7xBAinda não há avaliações

- Gtu Computer 3130704 Summer 2023Documento2 páginasGtu Computer 3130704 Summer 2023madhavjani06Ainda não há avaliações

- 9A12301 Digital Logic Design & Computer OrganizationDocumento4 páginas9A12301 Digital Logic Design & Computer OrganizationsivabharathamurthyAinda não há avaliações

- Switching Theory and Logic Design (CSE-203) (Makeup)Documento2 páginasSwitching Theory and Logic Design (CSE-203) (Makeup)Random ShitAinda não há avaliações

- B.Tech II Year I Semester (R13) Supplementary Examinations June 2017Documento2 páginasB.Tech II Year I Semester (R13) Supplementary Examinations June 2017Kareem KhanAinda não há avaliações

- Gujarat Technological UniversityDocumento2 páginasGujarat Technological UniversitymtbhoyeAinda não há avaliações

- C0-R4.B4 Page 1 of 2 January, 2019 (6+6+6)Documento2 páginasC0-R4.B4 Page 1 of 2 January, 2019 (6+6+6)sanjay sheeAinda não há avaliações

- NR Code No: NR-12/MCA MCA-I Semester Supplementary Examinations, July/Aug 2008. Computer Organization Time: 3hours Max. Marks: 60 Answer Any FIVE Questions All Questions Carry Equal MarksDocumento3 páginasNR Code No: NR-12/MCA MCA-I Semester Supplementary Examinations, July/Aug 2008. Computer Organization Time: 3hours Max. Marks: 60 Answer Any FIVE Questions All Questions Carry Equal MarksvirusyadavAinda não há avaliações

- 9A04504 Digital IC ApplicationsDocumento1 página9A04504 Digital IC ApplicationssubbuAinda não há avaliações

- Digital Logic DesignDocumento4 páginasDigital Logic DesignShareef KhanAinda não há avaliações

- Digital ElectronicsDocumento7 páginasDigital ElectronicsAlakaaa PromodAinda não há avaliações

- FAQs - CS1202 Digital Principles and System DesignDocumento13 páginasFAQs - CS1202 Digital Principles and System DesignsridharanchandranAinda não há avaliações

- Computer OrganizationDocumento1 páginaComputer OrganizationsubbuAinda não há avaliações

- (WWW - Entrance-Exam - Net) - JNTU ECE 3rd Year Computer Graphics Sample Paper 4Documento4 páginas(WWW - Entrance-Exam - Net) - JNTU ECE 3rd Year Computer Graphics Sample Paper 4Dr-Samson ChepuriAinda não há avaliações

- 9A04401 Switching Theory and Logic DesignDocumento4 páginas9A04401 Switching Theory and Logic DesignsivabharathamurthyAinda não há avaliações

- 9A04603 Digital Signal Processing24Documento1 página9A04603 Digital Signal Processing24Mahaboob SubahanAinda não há avaliações

- 9A04603 Digital Signal Processing31Documento1 página9A04603 Digital Signal Processing31Mahaboob SubahanAinda não há avaliações

- R5320201 Digital Signal Processing21Documento1 páginaR5320201 Digital Signal Processing21Mahaboob SubahanAinda não há avaliações

- 9A04603 Digital Signal Processing10Documento1 página9A04603 Digital Signal Processing10Mahaboob SubahanAinda não há avaliações

- 9A04603 Digital Signal Processing23Documento1 página9A04603 Digital Signal Processing23Mahaboob SubahanAinda não há avaliações

- 9A04603 Digital Signal Processing16Documento4 páginas9A04603 Digital Signal Processing16Mahaboob SubahanAinda não há avaliações

- 9A04603 Digital Signal Processing7Documento1 página9A04603 Digital Signal Processing7Mahaboob SubahanAinda não há avaliações

- 9A04306 Digital Logic DesignDocumento4 páginas9A04306 Digital Logic DesignMahaboob SubahanAinda não há avaliações

- 9A04603 Digital Signal Processing2Documento1 página9A04603 Digital Signal Processing2Mahaboob SubahanAinda não há avaliações

- 9A04306 Digital Logic Design4Documento4 páginas9A04306 Digital Logic Design4Mahaboob SubahanAinda não há avaliações

- R7210504 Digital Logic DesignDocumento1 páginaR7210504 Digital Logic DesignMahaboob SubahanAinda não há avaliações

- ICT 9A04306 Digital Logic DesignDocumento1 páginaICT 9A04306 Digital Logic DesignMahaboob SubahanAinda não há avaliações

- 13A04306 Digital Logic Design1Documento1 página13A04306 Digital Logic Design1Mahaboob SubahanAinda não há avaliações

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsNo EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsNota: 5 de 5 estrelas5/5 (3)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]No EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Nota: 5 de 5 estrelas5/5 (3)

- Chip War: The Fight for the World's Most Critical TechnologyNo EverandChip War: The Fight for the World's Most Critical TechnologyNota: 4.5 de 5 estrelas4.5/5 (82)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyNo EverandChip War: The Quest to Dominate the World's Most Critical TechnologyNota: 4.5 de 5 estrelas4.5/5 (229)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102No EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Nota: 5 de 5 estrelas5/5 (2)

- CompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)No EverandCompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Nota: 5 de 5 estrelas5/5 (2)

- Cyber-Physical Systems: Foundations, Principles and ApplicationsNo EverandCyber-Physical Systems: Foundations, Principles and ApplicationsHoubing H. SongAinda não há avaliações

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002No EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Nota: 5 de 5 estrelas5/5 (1)

- Raspberry PI: Learn Rasberry Pi Programming the Easy Way, A Beginner Friendly User GuideNo EverandRaspberry PI: Learn Rasberry Pi Programming the Easy Way, A Beginner Friendly User GuideAinda não há avaliações

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XNo EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XNota: 3 de 5 estrelas3/5 (2)

- Samsung Galaxy S22 Ultra User Guide For Beginners: The Complete User Manual For Getting Started And Mastering The Galaxy S22 Ultra Android PhoneNo EverandSamsung Galaxy S22 Ultra User Guide For Beginners: The Complete User Manual For Getting Started And Mastering The Galaxy S22 Ultra Android PhoneAinda não há avaliações

- Cancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionNo EverandCancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionNota: 5 de 5 estrelas5/5 (2)

- Essential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XNo EverandEssential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XNota: 5 de 5 estrelas5/5 (1)

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxNo EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxAinda não há avaliações

- The comprehensive guide to build Raspberry Pi 5 RoboticsNo EverandThe comprehensive guide to build Raspberry Pi 5 RoboticsAinda não há avaliações

- Arduino and Raspberry Pi Sensor Projects for the Evil GeniusNo EverandArduino and Raspberry Pi Sensor Projects for the Evil GeniusAinda não há avaliações

- The User's Directory of Computer NetworksNo EverandThe User's Directory of Computer NetworksTracy LaqueyAinda não há avaliações

- Raspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesNo EverandRaspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesAinda não há avaliações

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1715193157?v=1)