Escolar Documentos

Profissional Documentos

Cultura Documentos

Introduction To Integrated Digital Electron Nic S

Enviado por

Karajá PtahTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Introduction To Integrated Digital Electron Nic S

Enviado por

Karajá PtahDireitos autorais:

Formatos disponíveis

See discussions, stats, and author profiles for this publication at: https://www.researchgate.

net/publication/313900306

Introduction to Integrated Digital Electronics

Chapter · March 2017

CITATIONS READS

0 1,293

1 author:

Shree Krishna Khadka

Tribhuvan University

34 PUBLICATIONS 9 CITATIONS

SEE PROFILE

Some of the authors of this publication are also working on these related projects:

Energy Perspectives of Nepal View project

A Notebook on Integrated Digital Electronics View project

All content following this page was uploaded by Shree Krishna Khadka on 23 February 2017.

The user has requested enhancement of the downloaded file.

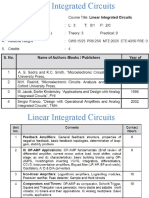

Chapter 1: Introduction to Integrated Digital Electronics

1.1 Integrated Circuits (ICs)

Digital circuits are invariably constructed with Integrated Circuits (ICs). An IC is a small silicon semiconductor

crystal called chip, containing electrical components such as transistors, diodes, resistors and capacitors.

These various components are interconnected inside the chip to form an electronic circuit. The chip is mounted

on a metal or plastic package, and the connections are welded to external pins to form the IC.

Unlike other electronic circuits, the individual component in the IC cannot be separated or disconnected and the

circuit inside the package is accessible only through the external pins.

ICs come in different types of packages as shown in figure below. The Dual-In-Line (DIP) package is the most

widely used type because of the low price and easy installation on circuit boards.

The envelope of IC package is made of plastic or ceramic. Most packages have standard sizes, and the number

of pins ranges from 8 to 64.

Each IC has a numeric designation printed on the surface of the package for identification. Each vendor publishes

a data book or catalog that provides the necessary information concerning the various products.

The size of the IC packages is very small. For example, four AND gates are enclosed inside a 14-pin DIP package

with dimension of 20x8x3 millimeters. An entire microprocessor is enclosed within a 40-pin DIP package with

dimensions of 50x15x4 millimeters.

# Advantages of ICs over Electronic Circuits

The cost of ICs is very low: which makes them economical to use.

Reduced power consumption: which makes the digital system more economical to operated.

High reliability against failure: so the digital system needs less repairs.

High operating speed: which makes them suitable for high speed operations.

Reduced number of external wiring connections: since many of the connections are internal to the package.

# Categories of IC

Integrated circuits are classified in two general categories:

(a) Linear ICs (Analog ICs): Which operates with continuous signals to provide electronic functions such as

amplifiers and voltage comparators

(b) Digital ICs: which operates with binary signals and are made up of interconnected digital gates such as adder,

subs tractor; encoder, decoder etc.

Prepared by: Er. Shree Krishna Khadka

Lecturer: AITM, KIST, MAMTS

# IC Technology

As the technology of ICs has improved, the number of gates that can be put on a single silicon chip has increased

considerably.

SSI (Small Scale Integration): Several logic gates (1 – 10) in a single package.

MSI (Medium Scale Integration): To qualify as a MSI device, the IC must perform a complete logic function

and have a complexity of 10 to 100 gates.

LSI (Large Scale Integration): A LSI device performs a logic function with more than 100 gates.

VLSI (Very Large Scale Integration): Contains thousands of gates in a single chip.

ULSI (Ultra Large Scale Integration): 10 thousand ++ gates on a single chip.

GSI (Giga Scale Integration): Up to 100 thousand gates on a single super chip.

1.2 Digital Logic Family

Logic gates and memory devices are fabricated as integrated circuits (ICs). The digital ICs operate with binary

signals and are made up of interconnected digital gates.

Digital IC gates are classified into various types on the basis of logic circuit family to which they belong. The

basic circuit in each IC digital logic family is either a NAND or a NOR gate.

These basic circuits are the primary building block from which more complex functions are obtained.

Figure: Various Digital Logic Families available in the Market

Legend:

RTL – Resistor Transistor Logic DCTL – Direct Coupled Transistor Logic

IIL – Integrated Injection Logic DTL – Diode Transistor Logic

HTL – High Threshold Logic STTL – Schottky TTL

pMOS – p-type MOSFET Logic nMOS – n-type MOSFET Logic

CMOS – Complimentary MOS Logic

The circuits in which transistors are driven into saturation are called saturated circuits. The circuits that avoids

saturations region during logical operation is non-saturated circuits; they only make use of active and cut-off

mode during logical operation.

Prepared by: Er. Shree Krishna Khadka

Lecturer: AITM, KIST, MAMTS

1.3 Characteristics of Digital Logic Families

Different logic function families are usually evaluated by comparing the characteristics of the basic gates in each

family. Some of these important characteristics are described below.

# Fan-In and Fan-Out

Fan-In is the number of inputs of a logic gate that it can handle without impairing its normal operation.

Propagation delay increases with number of inputs. Such as, a two input NAND gate is faster than four input

NAND gate.

Logical

Symbol

Fan-In 1 2 3

Fan-Out is the maximum number of digital inputs that the output of a single logic gate can feed where the gate

must be from same logic family. Each of the connected logic gate will be considered as a unit load. A unit load

determines how many connections we can make from the output from a single logic gate. In following figure,

the output of a driving NAND gate is fed to three-unit load (or load gates) during two states.

Figure: Current Sourcing in High State Figure: Current Sinking in Low State

⸫ High State Fan-Out = IOH(max)/IIH ⸫ Low State Fan-Out = IOL(max)/IIL

Prepared by: Er. Shree Krishna Khadka

Lecturer: AITM, KIST, MAMTS

# Propagation Delay

It is the time taken for the output of a gate to change after the input is applied. The output could be logic 0 or 1.

- If the output changes for logical 0 to logical 1 state, then the propagation delay = T pLH

- If the output changes for logical 1 to logical 0 state, then the propagation delay = T pHL (TpLH ≠ TpHL)

In timing diagram, propagation delay is calculated between a designated point on the input pulse and the

corresponding point on the output pulse. Usually the propagation delay times are indicated with 50% point on the

pulse edges used as reference. Since, the value of TpLH and TpHL is not equal, hence we calculate an average

propagation delay: Average Propagation Delay (Td) = (TpHL + TpLH)/2

# Power Dissipation & Speed Power Product

It is the power consumed by the gate when fully driven by all the inputs, which must be available from the power

supply. If the input keep changing frequently, then we will calculate an average power dissipation given by:

PAvg = VCC x ICC = VCC x (ICCH+ICCL)/2

Power Dissipation = VCC x ICCH Power Dissipation = VCC x ICCL

Speed-Power product is a common means of measuring and comparing the overall performance of IC family.

It is also known as figure of merit. It is the product of propagation delay (in Seconds) and power dissipation (in

Watts = Joules/Seconds). Since, we want a logic gate in which the propagation delay is minimum and consume

less power, so a low value of Speed-Power product is desirable.

⸫ Speed Power Product/Figure of Merit (J) = Propagation Delay (S) x Power Dissipation (J/S)

Prepared by: Er. Shree Krishna Khadka

Lecturer: AITM, KIST, MAMTS

# Noise Immunity and Noise Margin

- The logic circuits may encounter noise voltages from different part of the circuit. If the noise voltage exceeds

certain level or specific limit the logic circuit malfunctioned. This arises two terms Noise Immunity and Noise

Margin.

- Noise immunity is the circuit’s ability to tolerate noise at the input side. To measure the noise immunity of a

circuit we use a term Noise Margin. The amount of noise voltage for which the digital circuit will capable of to

tolerate that noise voltage is known as Noise Margin. It is a quantitative measure of noise immunity or the

amount of noise spike that the logic can withstand.

- Hence, two Noise Margins are specified for logic circuits, High Level Noise Margin (NMH) and Low Level

Noise Margin (NML), they are expressed as:

NMH = VOH(min) – VIH(min) and NML = VIL(max) – VOL(max)

Prepared by: Er. Shree Krishna Khadka

Lecturer: AITM, KIST, MAMTS

View publication stats

Você também pode gostar

- Digital Logic Families - Electronics TutorialDocumento7 páginasDigital Logic Families - Electronics TutorialrakeluvAinda não há avaliações

- IC Logic FamilyDocumento4 páginasIC Logic FamilyAsheque IqbalAinda não há avaliações

- Design and Implementation of Full Adder Using Different XOR GatesDocumento5 páginasDesign and Implementation of Full Adder Using Different XOR GatesEvans MuokiAinda não há avaliações

- Lecture5 Chapter2 - Positive and Negative LogicDocumento11 páginasLecture5 Chapter2 - Positive and Negative LogicAyesha HussainAinda não há avaliações

- EENG115 Introduction to Logic Design LabDocumento10 páginasEENG115 Introduction to Logic Design Labasdf lkjAinda não há avaliações

- Digital Integrared CircuitsDocumento27 páginasDigital Integrared CircuitsDeepa RangasamyAinda não há avaliações

- EI2353 DSDQbankDocumento24 páginasEI2353 DSDQbankRaja RockAinda não há avaliações

- Binary Logic Gates & Digital Circuits ExplainedDocumento15 páginasBinary Logic Gates & Digital Circuits Explainedajas777BAinda não há avaliações

- Unit 3Documento46 páginasUnit 3jana kAinda não há avaliações

- Sonali Manual - 2nd August 2007Documento78 páginasSonali Manual - 2nd August 2007sonalibhagwatkarAinda não há avaliações

- Ultra Low Power Design of Full Adder Circuit Using Adiabatic Logic TechniquesDocumento13 páginasUltra Low Power Design of Full Adder Circuit Using Adiabatic Logic TechniquesIJRASETPublicationsAinda não há avaliações

- University of Technology Computer Engineering Department: Second Class 2018 / 2019 Ass. Lecturer Suhad HaddadDocumento41 páginasUniversity of Technology Computer Engineering Department: Second Class 2018 / 2019 Ass. Lecturer Suhad HaddadwisamAinda não há avaliações

- DLD Assignment PDFDocumento3 páginasDLD Assignment PDFMuhammad AliAinda não há avaliações

- Digital LogicDocumento18 páginasDigital LogicPraches AcharyaAinda não há avaliações

- Ec1203 Digital ElectronicsDocumento20 páginasEc1203 Digital ElectronicsSiva Prasad PadilamAinda não há avaliações

- Digital Logic Families PDFDocumento49 páginasDigital Logic Families PDFdineep90% (10)

- Ability Enhancement Lab Manual Atria ITDocumento45 páginasAbility Enhancement Lab Manual Atria ITGayatri JoshiAinda não há avaliações

- Digital Electronics Question BankDocumento34 páginasDigital Electronics Question Banksujithaa13100% (1)

- Logic FamiliesDocumento49 páginasLogic Familiesnour hijaziAinda não há avaliações

- DEL ManualDocumento94 páginasDEL ManualAnand BongirAinda não há avaliações

- Two Mark Questions For DSDDocumento17 páginasTwo Mark Questions For DSDvnirmalacseAinda não há avaliações

- TTL and CMOS FamiliesDocumento7 páginasTTL and CMOS FamiliesFabian AvilaAinda não há avaliações

- Multiplexer-Based Design of Adders/Subtractors and Logic Gates For Low Power VLSI ApplicationsDocumento8 páginasMultiplexer-Based Design of Adders/Subtractors and Logic Gates For Low Power VLSI ApplicationssunilAinda não há avaliações

- IC Logic FamiliesDocumento5 páginasIC Logic FamiliesAdarsha BhattaraiAinda não há avaliações

- Gates Institute of Technology:: Gooty Digital Circuits and Systems 2 Marks With AnswersDocumento20 páginasGates Institute of Technology:: Gooty Digital Circuits and Systems 2 Marks With AnswersNaveen YallapuAinda não há avaliações

- Gates Institute of Technology:: Gooty Digital Circuits and Systems 2 Marks With AnswersDocumento17 páginasGates Institute of Technology:: Gooty Digital Circuits and Systems 2 Marks With AnswersNaveen YallapuAinda não há avaliações

- Analog and Digital ComponentsDocumento30 páginasAnalog and Digital ComponentsRajesh Kone100% (2)

- UntitledDocumento202 páginasUntitledSidharth KapoorAinda não há avaliações

- CS302 Short QS SolvedDocumento12 páginasCS302 Short QS SolvedattiqueAinda não há avaliações

- Digital Logic Gate FundamentalsDocumento21 páginasDigital Logic Gate FundamentalsRavi TejaAinda não há avaliações

- Digital Integrated Circuit: IntroductionDocumento5 páginasDigital Integrated Circuit: IntroductionPolkam SrinidhiAinda não há avaliações

- IC Logic Families 1Documento27 páginasIC Logic Families 1Shahin ShuvoAinda não há avaliações

- Digital Logic Family Guide - Characteristics & TypesDocumento2 páginasDigital Logic Family Guide - Characteristics & TypesJamesAinda não há avaliações

- SADGUNmajortheory MiniDocumento52 páginasSADGUNmajortheory MiniKotagiri AravindAinda não há avaliações

- Analog Digital Logic Gates Circuits IntroductionDocumento4 páginasAnalog Digital Logic Gates Circuits IntroductionMichele RogersAinda não há avaliações

- DEL Lab ManualDocumento68 páginasDEL Lab ManualMohini AvatadeAinda não há avaliações

- WINSEM2023-24 BECE102L TH CH2023240502095 Reference Material I 17-01-2024 Logic FamiliesDocumento9 páginasWINSEM2023-24 BECE102L TH CH2023240502095 Reference Material I 17-01-2024 Logic Familiesmatlabdec12Ainda não há avaliações

- Chap. 8 Integrated-Circuit Logic Families: Chapter Outcomes (Objectives)Documento62 páginasChap. 8 Integrated-Circuit Logic Families: Chapter Outcomes (Objectives)estraj1954Ainda não há avaliações

- Wair Ya 2010Documento6 páginasWair Ya 2010abhishek shuklaAinda não há avaliações

- IC ApplicationsDocumento164 páginasIC ApplicationsSam SelinAinda não há avaliações

- Lecture3 Chapter2 - Positive and Negative LogicDocumento11 páginasLecture3 Chapter2 - Positive and Negative LogicDaniyal ChaudharyAinda não há avaliações

- Logic Families in Digital Electronics - TTL, Cmos, and EclDocumento35 páginasLogic Families in Digital Electronics - TTL, Cmos, and EclSameer A.AAinda não há avaliações

- Logic Family Introduction and OverviewDocumento96 páginasLogic Family Introduction and OverviewNikhil DattaAinda não há avaliações

- 15A04802-Low Power VLSI Circuits & Systems-CDF-5 UnitsDocumento61 páginas15A04802-Low Power VLSI Circuits & Systems-CDF-5 UnitsA PoojithaAinda não há avaliações

- AAIT Logic Circuits Lecture OverviewDocumento36 páginasAAIT Logic Circuits Lecture OverviewTsinat WondimuAinda não há avaliações

- Verify Four Voltage and Current Parameters For TTL and Cmos (Ic 74Lsxx, 74Hcxx)Documento8 páginasVerify Four Voltage and Current Parameters For TTL and Cmos (Ic 74Lsxx, 74Hcxx)sonalibhagwatkar100% (1)

- Delay Analysis of Half Subtractor using CMOS and Pass Transistor LogicDocumento6 páginasDelay Analysis of Half Subtractor using CMOS and Pass Transistor LogicSaravanan NsAinda não há avaliações

- CPE 361 Electrical, Electronics, and Logic Components Chapter 3Documento26 páginasCPE 361 Electrical, Electronics, and Logic Components Chapter 3France Mae CamogaoAinda não há avaliações

- 3.unit 01Documento73 páginas3.unit 01sanjayAinda não há avaliações

- ELE128 Unit 4A Integrated CircuitsDocumento23 páginasELE128 Unit 4A Integrated CircuitsjcarloslunaAinda não há avaliações

- Deld End Sem 5,6Documento6 páginasDeld End Sem 5,6The GK TalksAinda não há avaliações

- Verilog Implementation of Reversible Logic GateDocumento7 páginasVerilog Implementation of Reversible Logic GateDhamini GowdaAinda não há avaliações

- ECEG-3201-DLD-Lec - 04 - Digital IC FamiliesDocumento37 páginasECEG-3201-DLD-Lec - 04 - Digital IC FamiliesMekdem AlemuAinda não há avaliações

- Mixed Signal IssuesDocumento18 páginasMixed Signal IssuesSkvkAinda não há avaliações

- Information Sheet 1.3-2: Learning ObjectivesDocumento4 páginasInformation Sheet 1.3-2: Learning ObjectivesDan JamesAinda não há avaliações

- Transistor Info SheetDocumento4 páginasTransistor Info SheetDan JamesAinda não há avaliações

- The Lecture Contains:: Lecture 4: Introducing Digital Video and Digital Video StandardsDocumento6 páginasThe Lecture Contains:: Lecture 4: Introducing Digital Video and Digital Video StandardsKarajá PtahAinda não há avaliações

- Silicon Ingot Production: Czochralski-And Float-Zone TechniqueDocumento2 páginasSilicon Ingot Production: Czochralski-And Float-Zone TechniqueKarajá PtahAinda não há avaliações

- Chapter 8 Ion Implantation - IDocumento40 páginasChapter 8 Ion Implantation - IKarajá PtahAinda não há avaliações

- AnalogTV BW PDFDocumento51 páginasAnalogTV BW PDFRafael SurbanoAinda não há avaliações

- DBMS - Chapter-2Documento73 páginasDBMS - Chapter-2MasterAinda não há avaliações

- From Sand to Silicon: The Fascinating World of SemiconductorsDocumento7 páginasFrom Sand to Silicon: The Fascinating World of SemiconductorsKarajá PtahAinda não há avaliações

- ER DiagramDocumento12 páginasER DiagramKarajá PtahAinda não há avaliações

- AU7860A Datasheet: USB Host MP3/WMA Decoder SOCDocumento14 páginasAU7860A Datasheet: USB Host MP3/WMA Decoder SOCsdsAinda não há avaliações

- b8 Digi Anywhereusb Plus DsDocumento4 páginasb8 Digi Anywhereusb Plus DsClem CZAinda não há avaliações

- Accenture - Sustaining Success in The Digital Era - The New Challenge For CableDocumento16 páginasAccenture - Sustaining Success in The Digital Era - The New Challenge For CableAndrey PritulyukAinda não há avaliações

- Service Manual: CSD-TD51 CSD-TD52 CSD-TD53Documento30 páginasService Manual: CSD-TD51 CSD-TD52 CSD-TD53parascoliAinda não há avaliações

- Best Practices Location-Aware WLAN DesignDocumento70 páginasBest Practices Location-Aware WLAN Designkin_tak6238Ainda não há avaliações

- Melsec PLC Ladder Logic for 7 Segment Display Parallel DrivingDocumento7 páginasMelsec PLC Ladder Logic for 7 Segment Display Parallel Drivinglue-ookAinda não há avaliações

- Analysis and Design of Sequential Circuits: Examples: COSC3410Documento36 páginasAnalysis and Design of Sequential Circuits: Examples: COSC3410markolzAinda não há avaliações

- AN3116 ADC Modes and ApplicationsDocumento18 páginasAN3116 ADC Modes and ApplicationsHarinadha ReddyAinda não há avaliações

- G5725 1MHz 1A Synchronous Step-Down RegulatorDocumento2 páginasG5725 1MHz 1A Synchronous Step-Down RegulatorM. M.Ainda não há avaliações

- DS POSITION INDICATOR EN Rev01Documento3 páginasDS POSITION INDICATOR EN Rev01Ronak PatelAinda não há avaliações

- Wireless Power System For Implantable Heart Pumps Based On Energy Injection ControlDocumento5 páginasWireless Power System For Implantable Heart Pumps Based On Energy Injection ControlkeplanAinda não há avaliações

- DS - GS04B P 1 50 M8 3 - Eng - 50146164Documento5 páginasDS - GS04B P 1 50 M8 3 - Eng - 50146164Dong HungAinda não há avaliações

- Detailed Syllabus - Optical CommunicationDocumento3 páginasDetailed Syllabus - Optical Communicationiamitgarg7Ainda não há avaliações

- (Source: BS: 162) : ANNEXE To Safety Standards (Transmission Lines & Sub Stations)Documento11 páginas(Source: BS: 162) : ANNEXE To Safety Standards (Transmission Lines & Sub Stations)naveen prasadAinda não há avaliações

- Baofeng UV-5R - Reference 4x6Documento8 páginasBaofeng UV-5R - Reference 4x6compte emailAinda não há avaliações

- SQ11 Manual Ord-InfoDocumento4 páginasSQ11 Manual Ord-InfoMahmoud Saeed100% (4)

- MADYA COMPUTER SERVICE CENTER OFFERS LAPTOPS, PCs AND MOREDocumento2 páginasMADYA COMPUTER SERVICE CENTER OFFERS LAPTOPS, PCs AND MOREcl3o.frAinda não há avaliações

- Lanewatch Switch 0 1Documento1 páginaLanewatch Switch 0 1Quốc Phú ĐinhAinda não há avaliações

- Flyer - ibaPADU 8 HI I - EN PDFDocumento2 páginasFlyer - ibaPADU 8 HI I - EN PDFc.a.g.p.Ainda não há avaliações

- Alinco DR-138 438 UserDocumento41 páginasAlinco DR-138 438 UserDe JavuAinda não há avaliações

- CSC-339 Introduction to Computer NetworksDocumento79 páginasCSC-339 Introduction to Computer NetworksRaffay aliAinda não há avaliações

- Zelda Welding Machine CatalogDocumento72 páginasZelda Welding Machine CatalogJuan Manuel Suarez OreAinda não há avaliações

- Shannon-Weaver Model of Communication - 7 Key Concepts (2020)Documento10 páginasShannon-Weaver Model of Communication - 7 Key Concepts (2020)Afif Kim100% (1)

- Datasheet PDFDocumento3 páginasDatasheet PDFpichon1Ainda não há avaliações

- RS-485 to RS-232 Converter InstructionDocumento1 páginaRS-485 to RS-232 Converter InstructionSeka Vilar SorucoAinda não há avaliações

- 43UH6030-SB - 43UH603T-DB - 3702 - 0022 - SmartGuide 2 PDFDocumento54 páginas43UH6030-SB - 43UH603T-DB - 3702 - 0022 - SmartGuide 2 PDFoscar ortiz0% (1)

- GPFM115 Medical: 115 Watt Global Performance SwitchersDocumento3 páginasGPFM115 Medical: 115 Watt Global Performance Switchersbruno barbosaAinda não há avaliações

- One Cell Lithium-ion Battery Protection ICDocumento12 páginasOne Cell Lithium-ion Battery Protection ICHeraclio Camacho UlloaAinda não há avaliações

- Eee ADocumento6 páginasEee ASundaravadivel ArumugamAinda não há avaliações

- مكبرات العمليات PDFDocumento55 páginasمكبرات العمليات PDFmahmoud DawoodAinda não há avaliações