Escolar Documentos

Profissional Documentos

Cultura Documentos

Guide To Passing LVS (Layout vs. Schematic) : A Cadence Help Document Document Contents

Enviado por

anusha12344321Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Guide To Passing LVS (Layout vs. Schematic) : A Cadence Help Document Document Contents

Enviado por

anusha12344321Direitos autorais:

Formatos disponíveis

Guide to Passing LVS (Layout vs.

Schematic)

A Cadence Help Document

Document Contents

Introduction

Golden Rules

Understanding the LVS Output File

Example LVS Output File

Solutions to Common LVS Problems

Tools and Techniques for Passing LVS

Introduction

Cadence Tutorial B describes the steps for running an LVS (Layout vs. Schematic) comparison

to verify the layout and schematic for a cell exactly match. This document describes techniques

for tracking down and fixing problems that cause LVS to fail or not pass. Passing LVS for a

circuit is critical to ensure the physical design will perform as intended when the circuit is

fabricated. However, passing LVS can be one of the most difficult and time consuming tasks of

the design flow because often the problems are hard to track down. The Cadence LVS tool

provides several sources of information which can be used to find and debug the problems that

caused LVS to fail or not pass. This document briefly describes some of these information

sources and provides some techniques for solving common LVS problems.

Golden Rules

• Always verify the operation of a circuit via simulations at the schematic level before

attempting to layout the cell. LVS only verifies the schematic and layout match, so if the

schematic does not work the layout will not either. If the schematic does not function

properly, there is no reason to spend time debugging the LVS.

• Always design in a hierarchical fashion, building smaller (lower level) cells before

constructing larger circuit blocks from the lower level cells.

• Always pass LVS on lower level cells before attempting to check LVS on a higher-level

cell. If the lower level cells do not pass LVS, it is much easier to debug them on their

own than after you have added the cell to a higher level circuit.

• Always re-check LVS on a cell if you make any changes to the schematic or layout.

• If you modify a layout to correct a problem found in an LVS check, always re-extract the

layout and save it before running the LVS checker again.

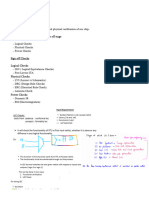

Understanding the LVS Output File

The LVS Output File provides a lot of useful information about a cell, including the number of

devices, nets, etc. within the cell. It also lists some results that can be useful in tracking down

errors that caused LVS not to pass. An example LVS Output File for a cell that has passed LVS

is given below. The five color-coded and numbered subsections of the LVS output file are:

1. The Netlist summary for the layout and the schematic.

Guide to Passing LVS 1

• This is a very important indicator of problems. If the netlists match, as they do above,

you will notice that the numbers for the Nets, Terminals, NMOS, and PMOS all match.

A quick description of these:

o NETS – These are the wires or connections in a device. In your inverter the

output which connects the drain of you PMOS to the drain of your NMOS is

considered an NET.

o Terminals – These are the pins in your design. These Numbers must always

match completely.

o NMOS – The number of NMOS transistors in your design

o PMOS – The number of PMOS transistors in your design

2. Terminal correspondence points.

• A list of the terminals that match in your Layout and your schematic. ALL Pins

including vdd! and gnd! must show up. If all pins are not showing, your LVS probably

will not show a match.

3. Netlist Summary

• Provides a basic comparison summary of the netlists for your layout and schematic.

4. Probe file output for your schematic.

• Provides information about your schematic if there is not a match. If the netlists do

match, the file will look like the example given above.

5. Probe file output for your layout.

• Provides information about your layout if there is not a match. If the netlists do match,

the file will look like the example given above.

Example: Passed LVS Output File

@(#)$CDS: LVS version 4.4.6 24 nets

08/30/2001 16:57 (cds11612) $ 7 terminals

17 pmos

Like matching is enabled. 17 nmos

Net swapping is enabled.

Using terminal names as 2.

correspondence points.

Compiling Diva LVS rules... Terminal correspondence points

1 CLK

2 D

1. 3 Q

Net-list summary for 4 QBAR

/egr/classes/ece410/dotsonna/caden 5 R

ce/LVS/layout/netlist 6 gnd!

count 7 vdd!

24 nets

7 terminals 3.

17 pmos

17 nmos The net-lists match.

Net-list summary for layout

/egr/classes/ece410/dotsonna/caden schematic

ce/LVS/schematic/netlist instances

count un-matched 0 0

rewired 0 0

Guide to Passing LVS 2

size errors 0 0

pruned 0 0 termbad.out:

active 34 34

total 34 34 prunenet.out:

nets prunedev.out:

un-matched 0 0

merged 0 0 audit.out:

pruned 0 0

active 24 24 5.

total 24 24

Probe files from

terminals /egr/classes/ece410/dotsonna/caden

un-matched 0 0 ce/LVS/layout

matched but

different type 0 0 devbad.out:

total 7 7

netbad.out:

4. mergenet.out:

Probe files from

/egr/classes/ece410/dotsonna/caden termbad.out:

ce/LVS/schematic

prunenet.out:

devbad.out:

prunedev.out:

netbad.out:

audit.out:

mergenet.out:

Solutions to Common LVS Problems

LVS Fails

A very common problem is that your LVS will fail. If this happens you will need to know why.

The following steps will help you to identify the issue.

1. Once the LVS comparison fails, click OK on the window that pops up.

2. Click the Output button on the LVS window.

3. Click OK in the next window that pops up.

4. Next a “Display Run Information” window will pop up. In this window, click the LogFile

button.

5. A LogFile will then pop up. This file contains some information about the LVS run and why

it failed. The reason for failure is listed towards the bottom of the file. Many times, a

schematic or a layout was not saved or needs to be in order for the comparison to complete.

Number of Terminals do not Match

The number of terminals in your layout does not match the numbers for your schematic. (This

can be seen at the top of the output file in the netlist summary section). Below are some possible

conditions and solutions.

Guide to Passing LVS 3

1. You forgot to include jumper pins for your vdd! and gnd! Rails. In this case your LVS will

still pass, but your extracted circuit will not function correctly in simulations, so this problem

must be fixed.

2. You forgot to include all pins in your layout. Maybe one of the inputs or outputs was not

made in the layout or it was made improperly.

3. You did not name the pins in your layout EXACTLY the same as their counterparts in the

schematic. For example, a pin called Vdd! in the layout view will not match a pin called

vdd! in the schematic view.

Number of Nets do not Match

The number of nets in your layout does not match the number for your schematic. (This can be

seen at the top of the output file in the netlist summary section)

1. If the number of nets given for your layout is higher than that for your schematic, then there

are some connections between points in your layout that need to be made. Fixing this can

sometimes be very difficult. The “Layout Probe File Output” section in your output file

usually contains some useful information on this.

• The first scenario for this situation is that your probe file output will say something like “?

Net /net 027 merged with /R.” These problems are usually very easy to fix. What the

above line means is that net 027, which is some internal connection in the circuit, needs to

be connected to terminal R. This can be confusing because you might assume merged

means they are already connected, but in the Cadence LVS output file this means they need

to be connected.

• The second scenario for this situation is that your probe file output will say something like

“terminal gnd! in layout fails to match any terminal in the schematic” These problems

are usually not so easy to fix, if more than one terminal is not matching. In the given case,

a transistor that should be connected to gnd! probably is not connected, so you would need

to inspect your layout and find where a connection needs to be made. If you have multiple

terminals that are not matching, inspect each terminal listed very carefully to ensure that all

connections are made to the appropriate points in your layout. This is never an easy task

and can be quite time consuming, so use patience and try and locate your mistake.

2. If the number of nets given for your layout is lower than that for your schematic, then there

are some connections between points in your layout that are made and should not be. Fixing

this can again be very difficult. The “Schematic Probe File Output” and “Layout Probe File

Output” sections in your output file usually contain some useful information on this.

• The first scenario for this situation is that your Schematic probe file output will say

something like “? Net /net 027 merged with /R.” As above, these problems are usually

very easy to fix. What the above line means is that net 027, which is some internal

connection in the circuit, needs to be connected to terminal R in your schematic view.

However, remember that we are assuming that you have a correct functioning

schematic, so the issue is still with the layout. You need to go into your layout and find

the connection that you made between these points and then delete it.

Guide to Passing LVS 4

• The second scenario for this situation is that your Layout and Schematic probe file outputs

will say something like “terminal gnd! in layout fails to match any terminal in the

schematic” Again, these problems are usually not so easy to fix, if more than one terminal

is not matching. In the given case, a transistor that should be connected to gnd! probably is

not connected, so you would need to inspect your layout and find where a connection needs

to be made. If you have multiple terminals that are not matching, inspect each terminal

listed very carefully to ensure that all connections are made to the appropriate points in

your layout.

Tools and Techniques for Passing LVS

If you have taken care while laying out your circuits, problems usually fall under the scenarios

given above. But sometimes certain errors are still difficult to find from the information in the

LVS Output File, so below are a list of tools to help you locate other problems in your layout.

LVS Error Display

If you have a netlist that does not match, you can visually show the errors on your extracted

layout view. This can help you find the error so you can fix the problem in your layout.

1. To see this option, click LVS Error Display button in the LVS window.

2. This is a tip that will help you to see the errors on your extracted view. Change the Error

color to be highlighted, by clicking on that button, to white. This will make it much

easier to see the errors on your extracted view. The default color is pink and that is

sometimes hard to see.

3. After you have set this up, click the next button and your errors will be listed in the Error

display window and highlighted on your extracted window at the same time.

Shorts Locator

Many times the Output file will let you know that either connections are made that should not be

or connections should be made. Most of the time some net name is given and you have no idea

what that net is or how to find it, so this tool can be quite helpful.

1. Open the Extracted view for the cell on which you are running LVS.

2. In the extracted view window, click verify on the menu bar and then click on Shorts in

this menu.

3. The Shorts Locator window will then pop up. If it does not pop up immediately, click

OK on any small pop-ups until it does appear.

4. In the shorts locator window, type in the number of the net you wish to find and click the

run button. On your extracted view, the net will be highlighted in orange so you will be

able to see it pretty easily. If you wish to find a different net when you are finished

looking at the first, click the finish button in the shorts locator window and then just type

in the number of the next net you wish to find and click the run button.

Guide to Passing LVS 5

Você também pode gostar

- Basic PeopleSoft Query Updated 011702Documento58 páginasBasic PeopleSoft Query Updated 011702anusha12344321Ainda não há avaliações

- LabcbvDocumento9 páginasLabcbvRAZAinda não há avaliações

- Physical VerificationDocumento18 páginasPhysical VerificationSaurabh KumarAinda não há avaliações

- DRBD-Cookbook: How to create your own cluster solution, without SAN or NAS!No EverandDRBD-Cookbook: How to create your own cluster solution, without SAN or NAS!Ainda não há avaliações

- OpenVSwitch PDFDocumento21 páginasOpenVSwitch PDFShahid MehmoodAinda não há avaliações

- Training 3Documento17 páginasTraining 3Thomas George100% (1)

- Tutorial - Layout LVS & PEX With CalibreDocumento57 páginasTutorial - Layout LVS & PEX With CalibreMahendra Sakre100% (1)

- OpenStack Deep DiveDocumento36 páginasOpenStack Deep DiveLoris StrozziniAinda não há avaliações

- 16-Troubleshooting EtherChannel IDocumento11 páginas16-Troubleshooting EtherChannel Imansoorali_afAinda não há avaliações

- Microprocessor System Design: A Practical IntroductionNo EverandMicroprocessor System Design: A Practical IntroductionAinda não há avaliações

- Debugging OVS: Jus.n Pe0t April 14, 2011Documento20 páginasDebugging OVS: Jus.n Pe0t April 14, 2011Dimitris Alyfantis100% (1)

- LvsDocumento28 páginasLvsJasorsi GhoshAinda não há avaliações

- Guide To Passing LVS (Layout vs. Schematic)Documento5 páginasGuide To Passing LVS (Layout vs. Schematic)Brian SiewAinda não há avaliações

- Guide LVSDocumento5 páginasGuide LVSpdnoob100% (1)

- Virtuoso Lvs DRC v4Documento23 páginasVirtuoso Lvs DRC v4Ajay HoodaAinda não há avaliações

- DRC and LVS Checks Using Cadence VirtuosoDocumento21 páginasDRC and LVS Checks Using Cadence VirtuosoSrikanthAinda não há avaliações

- Lab-5 4410Documento6 páginasLab-5 4410Han hoAinda não há avaliações

- Cmos Vlsi Design Lab 4: Controller Design: 1. Standard Cell LibraryDocumento8 páginasCmos Vlsi Design Lab 4: Controller Design: 1. Standard Cell LibraryTrần TriềuAinda não há avaliações

- Homework #0: Inverter Sample: ECE 126 Homework #0 Page 1 of 7Documento7 páginasHomework #0: Inverter Sample: ECE 126 Homework #0 Page 1 of 7Mostafa M. SamiAinda não há avaliações

- Design ChecksDocumento1 páginaDesign Checkshumtum_shri5736Ainda não há avaliações

- Varun Palivela Lab1 ReportDocumento25 páginasVarun Palivela Lab1 ReportVarun PalivelaAinda não há avaliações

- Lab 0Documento16 páginasLab 0Huu Tri NguyenAinda não há avaliações

- ASIC Verification CalibreDocumento33 páginasASIC Verification CalibremaniroopAinda não há avaliações

- LabcxfbDocumento15 páginasLabcxfbRAZAinda não há avaliações

- Sign Off NewDocumento38 páginasSign Off Newsubha mounikaAinda não há avaliações

- Open Vswitch Cheat SheetDocumento8 páginasOpen Vswitch Cheat SheetJinuAinda não há avaliações

- TN 423: Vlsi Circuits: Lecture 9aDocumento41 páginasTN 423: Vlsi Circuits: Lecture 9aBernard Mkumbwa Jr.Ainda não há avaliações

- (Selected) LVS Is That Simple (Digital Backend Physical Verification) - Lvs Verification-CSDN BlogDocumento9 páginas(Selected) LVS Is That Simple (Digital Backend Physical Verification) - Lvs Verification-CSDN BlogAgnathavasiAinda não há avaliações

- LabcbzDocumento12 páginasLabcbzRAZAinda não há avaliações

- When I Worked in A NetworkDocumento17 páginasWhen I Worked in A Networkiftikhar ahmedAinda não há avaliações

- Digital-On-Top Physical Verification: LVS and DRC Using Innovus and CalibreDocumento58 páginasDigital-On-Top Physical Verification: LVS and DRC Using Innovus and CalibreKumar Kumar100% (1)

- Ex 10Documento17 páginasEx 10kavita4123Ainda não há avaliações

- One Pass Multi Pass Assembler and Implementation ExamplesDocumento17 páginasOne Pass Multi Pass Assembler and Implementation ExamplesShikha Jamwal67% (3)

- Ex12 PDFDocumento16 páginasEx12 PDFSiam HasanAinda não há avaliações

- IR Drop Reduction Via Via AdditionDocumento4 páginasIR Drop Reduction Via Via AdditionSeema JainAinda não há avaliações

- Exploring SMB: Andrew Tridgell May 8, 2000Documento6 páginasExploring SMB: Andrew Tridgell May 8, 2000ankit boxerAinda não há avaliações

- Importance of LEC: Fig-1. Logical Equivalence Check Flow DiagramDocumento7 páginasImportance of LEC: Fig-1. Logical Equivalence Check Flow DiagramSrinath M SAinda não há avaliações

- EE241B Lab 2Documento3 páginasEE241B Lab 2bashasvuceAinda não há avaliações

- Getting To Know PERC: - Calibre PERC Addresses A Number of Electrical Design IssuesDocumento14 páginasGetting To Know PERC: - Calibre PERC Addresses A Number of Electrical Design Issues劉彥均Ainda não há avaliações

- TransistorDocumento10 páginasTransistorlogiece89Ainda não há avaliações

- Rac Node Eviction Trouble ShootingDocumento2 páginasRac Node Eviction Trouble Shootingrlamtilaa100% (1)

- Assembly InstructionsDocumento22 páginasAssembly InstructionsMarcos GodoyAinda não há avaliações

- Verilog - Excellent ExplanationDocumento18 páginasVerilog - Excellent ExplanationRida AmjadAinda não há avaliações

- 4 LZWDocumento7 páginas4 LZWmayur morvekarAinda não há avaliações

- Guide To TannerEDA For VLSIDocumento32 páginasGuide To TannerEDA For VLSIPratik SinghAinda não há avaliações

- AOS-CX Switch Simulator - RPVST Lab GuideDocumento14 páginasAOS-CX Switch Simulator - RPVST Lab Guidetest testAinda não há avaliações

- RNASeq Command Line 25march2021 0Documento33 páginasRNASeq Command Line 25march2021 0prateek bhatiaAinda não há avaliações

- Lab 2. Standard Cell Layout.: Euler PathsDocumento8 páginasLab 2. Standard Cell Layout.: Euler PathsRenju TjAinda não há avaliações

- What's All This Mixed-Signal Simulation Stuff Anyway ?: Rich Klinger 2006Documento23 páginasWhat's All This Mixed-Signal Simulation Stuff Anyway ?: Rich Klinger 2006Rich100% (1)

- 14-Troubleshooting Spanning TreeDocumento13 páginas14-Troubleshooting Spanning Treemansoorali_afAinda não há avaliações

- Cmos Vlsi Design Lab 4: Full Chip Assembly: I. Core SchematicDocumento5 páginasCmos Vlsi Design Lab 4: Full Chip Assembly: I. Core SchematicdrhammoudaAinda não há avaliações

- EECS 373: Design of Microprocessor-Based SystemsDocumento29 páginasEECS 373: Design of Microprocessor-Based Systemsavinash_yuvarajAinda não há avaliações

- VerlogDocumento33 páginasVerlogbalashyamuAinda não há avaliações

- Lab 7.1.2 Waveform Decoding - Instructor Version: ObjectiveDocumento27 páginasLab 7.1.2 Waveform Decoding - Instructor Version: ObjectiveAntonio RomeroAinda não há avaliações

- P4 and Open VswitchDocumento13 páginasP4 and Open VswitchPavel YadvichukAinda não há avaliações

- Best Practices For Using Open Vswitch With XenServer PDFDocumento9 páginasBest Practices For Using Open Vswitch With XenServer PDFErin SmithAinda não há avaliações

- Discussion 1.1Documento14 páginasDiscussion 1.1MARY MAE MAGDALENE GREGOREAinda não há avaliações

- Chap2 RISC5 ISADocumento31 páginasChap2 RISC5 ISAAmanda Judy AndradeAinda não há avaliações

- CS/EE 5830/6830 - CAD Assignment #3Documento9 páginasCS/EE 5830/6830 - CAD Assignment #3Yermakov Vadim IvanovichAinda não há avaliações

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksNo EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksAinda não há avaliações

- Workcenter DocumentationDocumento7 páginasWorkcenter Documentationanusha12344321Ainda não há avaliações

- Number Systems and Codes Assignments: N n-1 n-2 0 N n-1 n-2 0 I N n-1 n-2 I N NDocumento1 páginaNumber Systems and Codes Assignments: N n-1 n-2 0 N n-1 n-2 0 I N n-1 n-2 I N Nanusha12344321Ainda não há avaliações

- Tuning Your PeopleSoft App Indexes and Temp TablesDocumento2 páginasTuning Your PeopleSoft App Indexes and Temp Tablesanusha12344321Ainda não há avaliações