Escolar Documentos

Profissional Documentos

Cultura Documentos

Computer Organisation and Architecture Module 3

Enviado por

nadheera ayishaTítulo original

Direitos autorais

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Computer Organisation and Architecture Module 3

Enviado por

nadheera ayishaDireitos autorais:

MODULE 3

KTU STUDNTS

Input Output Organization

For more study materials>www.ktustudents.in

Accessing I/O Devices:-

• Most modern computers use single bus arrangement for

connecting I/O devices to CPU & Memory

• The bus enables all the devices connected to it

to exchange information

• Bus consists of 3 set of lines : Address, Data & Control

Lines KTU STUDNTS

• Processor places a particular address (unique for an I/O

Dev.) on address lines

• Device which recognizes this address responds to

the commands issued on the Control lines

• Processor requests for either Read / Write

• The data will be placed on Data lines

For more study materials>www.ktustudents.in

I/O INETRFACE:-

KTU STUDNTS

For more study materials>www.ktustudents.in

I/O INETRFACE:-

• It is a special hardware used to connect the I/O device

to the bus , i.e, I/O interface.

• The I/O module has 3 section:-

• (a)Address decoder:- It enables the device to

recognize its address when this address appears on

KTU STUDNTS

the address lines.

• (b)Data register:- The data register holds the data

being transferred to or from the processor.

• The status register contains information relevant to

the operation of the I/O module.

• * Both the data and status register are connected to

the data bus.

For more study materials>www.ktustudents.in

KTU STUDNTS

For more study materials>www.ktustudents.in

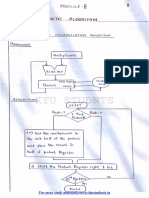

MODES OF DATA TRANSFER:-

1.Programmed I/O Mode:-

• In programmed I/O mode data are exchanged between the

processor and the I/O module. When a processor is executing a

program and encounters an instruction relating to I/O, it executes

that instruction by issuing a command to that appropriate I/O

module. With programmed I/O the I/O module will perform the

KTU STUDNTS

requested action and then set the appropriate bit in the I/O status

register .

• The I/O module takes no further action to alert the processor (it

doesn’t interrupt the processor).

• The I/O commands issued by the processor to the I/O module

Test

Control

Read

Write

For more study materials>www.ktustudents.in

2.Memory Mapped I/O:-

• There is a single address space for memory location and

I/O devices.( the address space is shared)

• With memory mapped I/O a single read line a single write

line are needed on the bus. The bus may be equipped with

KTU STUDNTS

memory read and write plus Input and output command

lines.

• Now the command lines specifies whether the address

refers to memory location or an I/O device.

• Most CPU uses memory mapped I/O.

• Always CPU assigns address to memory some of memory

space is stolen and assigned to I/O device.

• It deals with fewer address lines.

For more study materials>www.ktustudents.in

KTU STUDNTS

For more study materials>www.ktustudents.in

3.Interrupt Driven I/O:-

• In this method the program issues an I/O command and then

continues to execute untill it is interrupted by the I/O hardware to

signal the end of I/O operation.

• Here the program enters a wait loop in which it repeatedly checks

the device status. During this process the processor is not

KTU STUDNTS

performing any useful computation.

• There are many situations where tasks can be performed while

waiting for an I/O device to be ready, to allow this the I/O device

should alert the processor when it becomes ready. It can be done by

sending a hardware signal called an interrupt.

• The routine executed in response to an interrupt request is

called Interrupt Service Routine(ISR).

• The processor first completes execution of instruction then it loads

the program counter(pc) with the address of 1st instruction of ISR.

For more study materials>www.ktustudents.in

4.Direct Memory Access:-

• In this method the input and output devices read/write information from the main

memory without interference of the CPU through the system bus.

• For I/O transfer, processor determines the status of I/O by:

Polling

Waiting for interrupt signal.

• Considerable Overhead is incurred in above I/O transfer processing.

• By DMA approach , large blocks of data at high speed can be sent between

external device and main memory.

DMA CONTROLLER:-

KTU STUDNTS

• It allows the data transfer between I/O device and memory.

• DMA controllers acts a processor but it is controlled by the CPU. To initiate the

transfer of a block of words, the processor sends the following data to controller

• Starting address of memory block

The word count

Control to specify the mode of transfer such as read or write.

A control to start the DMA transfer.

• The DMA controller performs the required I/O operation and send a interrupt to

the processor upon completition.

For more study materials>www.ktustudents.in

KTU STUDNTS

For more study materials>www.ktustudents.in

Use Of DMA controller in Computer System

• DMA device have higher priority than processor over BUS control.

• Types of DMA Transfer:-

Cycle stealing

Brust mode

• Cycle Stealing:-

• DMA controller ‘steals’ memory cycles from the processor though

KTU STUDNTS

processor originates most memory access.

• Burst mode:-

• The DMA controller may be given exclusive access to the main

memory to tranasfer a block of data without interruption.

• Conflicts Of DMA:-

• ->Conflict between processor and DMA

• ->Two DMA Controller try to access the BUS at same time to access

the main memory

For more study materials>www.ktustudents.in

Interrupts

• Interrupts are external events that require the processor’s

attention.

– Peripherals and other I/O devices may need attention.

– Timer interrupts to mark the passage of time.

• These situations are not errors.

KTU STUDNTS

– They happen normally.

– All interrupts are recoverable:

• The interrupted program will need to be resumed after the interrupt is

handled.

• It is the operating system’s responsibility to do the right

thing, such as:

– Save the current state.

– Find and load the correct data from the hard disk

– Transfer data to/from the I/O device.

For more study materials>www.ktustudents.in

• Interrupts are provided primarily as a

way to improve processing efficiency

• the most common classes of

interrupts.

KTU STUDNTS

For more study materials>www.ktustudents.in

Program flow of control without and

with interrupts

KTU STUDNTS

For more study materials>www.ktustudents.in

INTERRUPTS AND THE INSTRUCTION

CYCLE

• With interrupts, the processor can be engaged in

executing other instructions while an I/O operation

is in progress.

• When the external device becomes ready to

accept more data from the processor,—the I/O

KTU STUDNTS

module for that external device sends an interrupt

request signal to the processor. The processor

responds by suspending operation of the current

program, branching off to a program to service

that particular I/O device, known as an interrupt

handler, and resuming the original execution after

the device is serviced.

For more study materials>www.ktustudents.in

• From the point of view of the user

program, an interrupt is just that: an

interruption of the normal sequence

of execution.

KTUWhen the interrupt

STUDNTS

processing is completed, execution

resumes

For more study materials>www.ktustudents.in

Instruction cycle with

interrupts

KTU STUDNTS

For more study materials>www.ktustudents.in

• In the interrupt cycle, the processor checks to see if any

interrupts have occurred. If no interrupts are pending, the

processor proceeds to the fetch cycle and fetches the next

instruction of the current program. If an interrupt is

pending, the processor does the following:

• It suspends execution of the current program being

KTU STUDNTS

executed and saves its context

• It sets the program counter to the starting address of an

interrupt handler routine. The processor now proceeds to

the fetch cycle and fetches the first instruction in the

interrupt handler program, which will service the interrupt.

When the interrupt handler routine is completed, the

processor can resume execution of the user program at the

point of interruption

For more study materials>www.ktustudents.in

KTU STUDNTS

For more study materials>www.ktustudents.in

MULTIPLE INTERRUPTS

• Multiple interrupts can occur. Two approaches can be

taken to dealing with multiple interrupts.

• The first is to disable interrupts while an interrupt is

being processed. A disabled interrupt simply means

that the processor can and will ignore that interrupt

KTU STUDNTS

request signal. Thus, when a user program is executing

and an interrupt occurs, interrupts are disabled

immediately. After the interrupt handler routine

completes, interrupts are enabled before resuming the

user program and the processor checks to see if

additional interrupts have occurred. This approach is

nice and simple, as interrupts are handled in strict

sequential order

For more study materials>www.ktustudents.in

• The drawback to the preceding

approach is that it does not take into

account relative priority or time-

critical needs

KTU ASTUDNTS

second approach is

to define priorities for interrupts and

to allow an interrupt of higher priority

to cause a lower-priority interrupt

handler to be itself interrupted

For more study materials>www.ktustudents.in

KTU STUDNTS

Nested interrupt processing

For more study materials>www.ktustudents.in

Buses

• A bus is a communication pathway

connecting two or more devices. A key

characteristic of a bus is that it is a shared

transmission medium. Multiple devices

connect to the bus, and a signal transmitted

KTU STUDNTS

by any one device is available for reception

by all other devices attached to the bus. If

two devices transmit during the same time

period, their signals will overlap and become

garbled. Thus, only one device at a time can

successfully transmit.

For more study materials>www.ktustudents.in

• Typically, a bus consists of multiple

communication pathways, or lines.

Each line is capable of transmitting

signals representing

KTU STUDNTS binary 1 and

binary 0. An 8-bit unit of data can be

transmitted over eight bus lines. A

bus that connects major computer

components (processor, memory,

I/O) is called a system bus.

For more study materials>www.ktustudents.in

Bus structure

KTU STUDNTS

For more study materials>www.ktustudents.in

• On any bus the lines can be classified into three functional

groups

• data, address, and control lines. In addition, there may be power

distribution lines that supply power to the attached modules

• The data lines provide a path for moving data among system

modules. These lines, collectively, are called the data bus. The

KTU STUDNTS

address lines are used to designate the source or destination of

the data on the data bus. For example, on an 8-bit address bus,

address 01111111 and below might reference locations in a

memory module (module 0) with 128 words of memory, and

address 10000000 and above refer to devices attached to an I/O

module (module 1). The control lines are used to control the

access to and the use of the data and address lines. Control

signals transmit both command and timing information among

system modules.

For more study materials>www.ktustudents.in

Timing signals indicate the validity of data and address information. Command

signals specify operations to be performed. Typical control lines include

• Memory write: Causes data on the bus to be written into the addressed location

• Memory read: Causes data from the addressed location to be placed on the bus

• I/O write: Causes data on the bus to be output to the addressed I/O port

• I/O read: Causes data from the addressed I/O port to be placed on the bus

• Transfer ACK: Indicates that data have been accepted from or placed on the bus

KTU STUDNTS

• Bus request: Indicates that a module needs to gain control of the bus

• Bus grant: Indicates that a requesting module has been granted control of the

bus

• Interrupt request: Indicates that an interrupt is pending

• Interrupt ACK: Acknowledges that the pending interrupt has been recognized

• Clock: Is used to synchronize operations

• Reset: Initializes all modules

For more study materials>www.ktustudents.in

• The operation of the bus is as follows. If one

module wishes to send data to another, it must do

two things:

• (1) obtain the use of the bus, and

• (2) transfer data via the bus. If one module wishes

KTU STUDNTS

to request data from another module, it must

• (1) obtain the use of the bus, and

• (2) transfer a request to the other module over

the appropriate control and address lines. It must

then wait for that second module to send the

data.

For more study materials>www.ktustudents.in

The classic physical arrangement of

a bus

KTU STUDNTS

For more study materials>www.ktustudents.in

• In this example, the bus consists of two vertical

columns of conductors. Each of the major system

components occupies one or more boards and

plugs into the bus at these slots. Thus, an on-chip

bus may connect the processor and cache memory,

KTU STUDNTS

whereas an on-board bus may connect the

processor to main memory and other components.

This arrangement is most convenient. A small

computer system may be acquired and then

expanded later (more memory, more I/O) by adding

more boards. If a component on a board fails, that

board can easily be removed and replaced.

For more study materials>www.ktustudents.in

Multiple-Bus Hierarchies

• In general, the more devices

attached to the bus, the greater the

bus length and hence the greater the

propagation

KTUdelay. STUDNTS

• . The bus may become a bottleneck

as the aggregate data transfer

demand approaches the capacity of

the bus.

• Most computer systems use multiple

buses, generally laid out in a

For more study materials>www.ktustudents.in

• There is a local bus that connects the processor to

a cache memory and that may support one or

more local devices The cache memory is

connected to a system bus to which all of the

main memory modules are attached. It is possible

KTU STUDNTS

to connect I/O controllers directly onto the system

bus. A more efficient solution is to make use of

one or more expansion buses for this purpose.

This arrangement allows the system to support a

wide variety of I/O devices and at the same time

insulate memory-to-processor traffic from I/O

traffic.

For more study materials>www.ktustudents.in

KTU STUDNTS

For more study materials>www.ktustudents.in

Elements of Bus Design

KTU STUDNTS

For more study materials>www.ktustudents.in

Elements of Bus Design

• There are a few design elements that serve to classify and differentiate buses.

• BUS TYPES Bus lines can be separated into two generic types: dedicated and

multiplexed.

A dedicated bus line is permanently assigned either to one function or to a

physical subset of computer components. Physical dedication refers to the use

of multiple buses, each of which connects only a subset of modules.

The potential advantage of physical dedication is high throughput, because

KTU STUDNTS

there is less bus contention.A disadvantage is the increased size and cost of

the system. Address and data information may be transmitted over the same

set of lines using an Address Valid control line.

At the beginning of a data transfer, the address is placed on the bus and the

Address Valid line is activated. The address is then removed from the bus, and

the same bus connections are used for the subsequent read or write data

transfer. This method of using the same lines for multiple purposes is known as

time multiplexing.

The advantage of time multiplexing is the use of fewer lines, which saves

space and, usually, cost. The disadvantage is that more complex circuitry is

needed within each module.

For more study materials>www.ktustudents.in

METHOD OF ABITRATION:

• The various methods can be roughly classified as being

either centralized or distributed. In a centralized scheme,

a single hardware device, referred to as a bus controller

or arbiter, is responsible for allocating time on the bus.

KTU STUDNTS

• In a distributed scheme, there is no central controller.

Rather, each module contains access control logic and

the modules act together to share the bus. With both

methods of arbitration, the purpose is to designate either

the processor or an I/O module, as master.

• The master may then initiate a data transfer (e.g., read

or write) with some other device, which acts as slave for

this particular exchange.

For more study materials>www.ktustudents.in

TIMING Buses

• use either synchronous timing or asynchronous timing.

With synchronous timing, the occurrence of events on the

bus is determined by a clock. A single 1–0 transmission is

referred to as a clock cycle or bus cycle and defines a time

slot KTU STUDNTS

• With asynchronous timing, the occurrence of one event on

a bus follows and depends on the occurrence of a previous

event.

• Synchronous timing is simpler to implement and test.

However, it is less flexible than asynchronous timing. With

asynchronous timing, a mixture of slow and fast devices,

using older and newer technology, can share a bus

For more study materials>www.ktustudents.in

KTU STUDNTS

For more study materials>www.ktustudents.in

KTU STUDNTS

For more study materials>www.ktustudents.in

BUS WIDTH

• The width of the data bus has an

impact on system performance: The

wider the

KTUdata bus, STUDNTS the greater the

number of bits transferred at one

time. The width of the address bus

has an impact on system capacity:

the wider the address bus, the

greater the range of locations that

can be referenced.

For more study materials>www.ktustudents.in

DATA TRANSFER TYPE Finally, a bus supports

various data transfer types, as illustrated in

Figure

KTU STUDNTS

For more study materials>www.ktustudents.in

• In the case of a multiplexed address/data bus, the bus is first

used for specifying the address and then for transferring the

data. For a read operation, there is typically a wait while the

data are being fetched from the slave to be put on the bus. For

either a read or a write, there may also be a delay if it is

necessary to go through arbitration to gain control of the bus for

KTU STUDNTS

the remainder of the operation.

• In the case of dedicated address and data buses, the address is

put on the address bus and remains there while the data are put

on the data bus. For a write operation, the master puts the data

onto the data bus as soon as the address has stabilized and the

slave has had the opportunity to recognize its address. For a

read operation, the slave puts the data onto the data bus as

soon as it has recognized its address and has fetched the data.

For more study materials>www.ktustudents.in

• A read–modify–write operation is simply a read

followed immediately by a write to the same

address

• Read-after-write is an indivisible operation

consisting of a write followed immediately by a

KTU STUDNTS

read from the same address.

• Some bus systems also support a block data

transfer. The first data item is transferred to or

from the specified address; the remaining data

items are transferred to or from subsequent

addresses

For more study materials>www.ktustudents.in

PCI (PHERIPHERAL COMPONENT

INTERCONNECT)

• The peripheral component

interconnect (PCI) is a popular high-

bandwidth, processorindependent

bus thatKTU

can function STUDNTS as a peripheral

bus. The current standard allows the

use of up to 64 data lines at 66 MHz,

for a raw transfer rate of 528

MByte/s, or 4.224 Gbps. It requires

very few chips to implement and

supports For

other buses attached

more study materials>www.ktustudents.in

to the

PCI

• Intel began work on PCI in 1990 for its

Pentium-based systems. The industry

association, the PCI Special Interest Group

(SIG), developed and further and maintained

the compatibility of the PCI specifications.

KTU STUDNTS

PCI is designed to support a variety of

microprocessor-based configurations,

including both single- and multiple-processor

systems. It makes use of synchronous timing

and a centralized arbitration scheme

For more study materials>www.ktustudents.in

KTU STUDNTS

For more study materials>www.ktustudents.in

• The bridge acts as a data buffer so

that the speed of the PCI bus may

differ from that of the processor’s I/O

capability. In a multiprocessor

KTU STUDNTS system

(Figure 1.23b), one or more PCI

configurations may be connected by

bridges to the processor’s system

bus. Again, the use of bridges keeps

the PCI independent of the processor

speed yetForprovides the ability

more study materials>www.ktustudents.in

to

Bus Structure

• PCI may be configured as a 32- or 64-bit bus. There are 49 mandatory signal lines for PCI which

are divided into the following functional groups:

• System pins: Include the clock and reset pins.

• Address and data pins: Include 32 lines that are time multiplexed for addresses and data. The

other lines in this group are used to interpret and validate the signal lines that carry the

addresses and data.

• Interface control pins: Control the timing of transactions and provide coordination among

initiators and targets.

KTU STUDNTS

• Arbitration pins: Unlike the other PCI signal lines, these are not shared lines. Rather, each PCI

master has its own pair of arbitration lines that connect it directly to the PCI bus arbiter.

• Error reporting pins: Used to report parity and other errors. In addition, the PCI specification

defines 51 optional signal lines, divided into the following functional groups:

• Interrupt pins: These are provided for PCI devices that must generate requests for service. As

with the arbitration pins, these are not shared lines. Rather, each PCI device has its own

interrupt line or lines to an interrupt controller.

• Cache support pins: These pins are needed to support a memory on PCI that can be cached in

the processor or another device.

• 64-bit bus extension pins: Include 32 lines that are time multiplexed for ad dresses and data

and that are combined with the mandatory address/data lines to form a 64-bit address/data

bus.

• JTAG/boundary scan pins: These signal lines support testing procedures

For more study materials>www.ktustudents.in

PCI Commands

Bus activity occurs in the form of transactions between an initiator, or master,

and a target. When a bus master acquires control of the bus, it determines

the type of transaction that will occur next The commands are as follows:

• Interrupt Acknowledge

• Special Cycle

• I/O Read

• I/O Write

• Memory Read KTU STUDNTS

• Memory Read Line

• Memory Read Multiple

• Memory Write

• Memory Write and Invalidate

• Configuration Read

• Configuration Write

• Dual address Cycle

For more study materials>www.ktustudents.in

• Interrupt Acknowledge is a read command

intended for the device that functions as an

interrupt controller on the PCI bus. The Special

Cycle command is used by the initiator to

broadcast a message to one or more targets.

KTU STUDNTS

The I/O Read and Write commands are used to

transfer data between the initiator and an I/O

controller. The memory read and write

commands are used to specify the transfer of

a burst of data, occupying one or more clock

cycles.

For more study materials>www.ktustudents.in

KTU STUDNTS

For more study materials>www.ktustudents.in

• The Memory Write command is used to transfer

data in one or more data cycles to memory. The

Memory Write and Invalidate command transfers

data in one or more cycles to memory. In addition,

it guarantees that at least one cache line is

written. KTU STUDNTS

• The two configuration commands enable a master

to read and update configuration parameters in a

device connected to the PCI. The Dual Address

Cycle command is used by an initiator to indicate

that it is using 64-bit addressing

For more study materials>www.ktustudents.in

Data Transfer

• Every data transfer on the PCI bus is

a single transaction consisting of one

address phase and one or more data

phases. KTU STUDNTS

For more study materials>www.ktustudents.in

KTU STUDNTS

For more study materials>www.ktustudents.in

Arbitration

• PCI makes use of a centralized,

synchronous arbitration scheme in

which each

KTU master STUDNTS has a unique

request (REQ) and grant (GNT)

signal. These signal lines are

attached to a central arbiter (Figure

1.25) and a simple request–grant

handshake is used to grant access to

the bus. For more study materials>www.ktustudents.in

KTU STUDNTS

For more study materials>www.ktustudents.in

Você também pode gostar

- Forensic Science From The Crime Scene To The Crime Lab 2nd Edition Richard Saferstein Test BankDocumento36 páginasForensic Science From The Crime Scene To The Crime Lab 2nd Edition Richard Saferstein Test Bankhilaryazariaqtoec4100% (25)

- Honda Wave Parts Manual enDocumento61 páginasHonda Wave Parts Manual enMurat Kaykun86% (94)

- S3 KTU-Solid State Devices Module 1Documento15 páginasS3 KTU-Solid State Devices Module 1nadheera ayisha67% (3)

- Change Management in British AirwaysDocumento18 páginasChange Management in British AirwaysFauzan Azhary WachidAinda não há avaliações

- IGCSE Chemistry Section 5 Lesson 3Documento43 páginasIGCSE Chemistry Section 5 Lesson 3Bhawana SinghAinda não há avaliações

- Top Malls in Chennai CityDocumento8 páginasTop Malls in Chennai CityNavin ChandarAinda não há avaliações

- Pub - Essentials of Nuclear Medicine Imaging 5th Edition PDFDocumento584 páginasPub - Essentials of Nuclear Medicine Imaging 5th Edition PDFNick Lariccia100% (1)

- I/O Management TechniquesDocumento41 páginasI/O Management TechniquesBrian MutukuAinda não há avaliações

- Operating Systems 8th Edition Cheat Sheet (Up To Chapter 6)Documento5 páginasOperating Systems 8th Edition Cheat Sheet (Up To Chapter 6)Michael Beswick0% (1)

- EMTL Lecture NotesDocumento210 páginasEMTL Lecture Notesnadheera ayishaAinda não há avaliações

- OS I/O Systems OverviewDocumento24 páginasOS I/O Systems OverviewKapil NagwanshiAinda não há avaliações

- 07 - Input OutputDocumento22 páginas07 - Input OutputSadiholicAinda não há avaliações

- AyilaraDocumento13 páginasAyilaraAremu FaisalAinda não há avaliações

- Unit2 Io Organization 97 2003Documento97 páginasUnit2 Io Organization 97 2003Apoorva JagtapAinda não há avaliações

- Lecture 4Documento34 páginasLecture 4KelvinAinda não há avaliações

- Interrupts I/O HardwareDocumento21 páginasInterrupts I/O HardwareYuvashree SundarAinda não há avaliações

- INTERFACING AND COMMUNICATION BASICSDocumento50 páginasINTERFACING AND COMMUNICATION BASICSVarun HuleAinda não há avaliações

- 10-Module 2 - System Call, Interrupts, Components of OS-29!04!2023Documento12 páginas10-Module 2 - System Call, Interrupts, Components of OS-29!04!2023Betha Sai Dheeraj 21BCE3046Ainda não há avaliações

- Embedded Microcontroller Systems: More Interfacing and ExamplesDocumento58 páginasEmbedded Microcontroller Systems: More Interfacing and ExamplesMahesh Rao SAinda não há avaliações

- Computer Organisation-Unit - IIIDocumento17 páginasComputer Organisation-Unit - IIIJust AndroAinda não há avaliações

- Computer Architecture: Von Neumann ModelDocumento28 páginasComputer Architecture: Von Neumann ModelDevan KaladharanAinda não há avaliações

- Os - Module-1Documento100 páginasOs - Module-1Fatema TahaAinda não há avaliações

- William Stallings Computer Organization and Architecture 8 EditionDocumento52 páginasWilliam Stallings Computer Organization and Architecture 8 EditionabbasAinda não há avaliações

- IO SystemDocumento32 páginasIO Systemnanekaraditya06Ainda não há avaliações

- I/O Organization and InterruptsDocumento95 páginasI/O Organization and Interruptsayush mittalAinda não há avaliações

- OS notes.docxDocumento39 páginasOS notes.docxpalkisbeevi25Ainda não há avaliações

- Top Level View of Computer Function and InterconnectionDocumento38 páginasTop Level View of Computer Function and Interconnectionhsi3Ainda não há avaliações

- Week 3 18032022 040218pmDocumento47 páginasWeek 3 18032022 040218pmmisbah AbidAinda não há avaliações

- Chapter7 Io OrganizationDocumento96 páginasChapter7 Io OrganizationnarendranvelAinda não há avaliações

- Module 1 - Operating-System ServicesDocumento78 páginasModule 1 - Operating-System ServicesKailashAinda não há avaliações

- Chapter7-Io OrganizationDocumento101 páginasChapter7-Io Organization684RICHA SINGHAinda não há avaliações

- Top Level View of Computer Function and InterconnectionDocumento62 páginasTop Level View of Computer Function and InterconnectionAhsan JameelAinda não há avaliações

- Lec 3 - Top View of SystemDocumento11 páginasLec 3 - Top View of SystemKimani MaithyaAinda não há avaliações

- Computer Hardware Requirements for Real-Time ApplicationsDocumento58 páginasComputer Hardware Requirements for Real-Time Applicationsnawnish kumarAinda não há avaliações

- External Devices and IO ModuleDocumento7 páginasExternal Devices and IO Modulekanaksanket100% (5)

- Chp6 Interrupt - StacknewDocumento11 páginasChp6 Interrupt - Stacknewheyfiez12Ainda não há avaliações

- Operating System Chapter 5 - MADocumento22 páginasOperating System Chapter 5 - MASileshi Bogale HaileAinda não há avaliações

- Top Level View of Computer Function and InterconnectionDocumento64 páginasTop Level View of Computer Function and Interconnectionbree789Ainda não há avaliações

- EvolutionDocumento8 páginasEvolutiontomasinaAinda não há avaliações

- Architectural Support For Operating SystemsDocumento57 páginasArchitectural Support For Operating SystemsarreyAinda não há avaliações

- EMBEDDED FIRMWARE DESIGNDocumento29 páginasEMBEDDED FIRMWARE DESIGNMurali Dhara Sesha Giri Rao GoddantiAinda não há avaliações

- Module 2 IO OrganizationDocumento104 páginasModule 2 IO OrganizationrrAinda não há avaliações

- CPU Organization ModifiedDocumento68 páginasCPU Organization ModifiedAbdalrhman juberAinda não há avaliações

- Input/Output Organization in Computer Organisation and ArchitectureDocumento99 páginasInput/Output Organization in Computer Organisation and ArchitectureAnand YadavAinda não há avaliações

- Accessing I/O Devices: Generic Model of IO ModuleDocumento14 páginasAccessing I/O Devices: Generic Model of IO ModuleAdarsha BhattaraiAinda não há avaliações

- Interrupt Mechanism ExplainedDocumento10 páginasInterrupt Mechanism ExplainedVijay PandeyAinda não há avaliações

- William Stallings Computer Organization and Architecture 7 Edition System BusesDocumento50 páginasWilliam Stallings Computer Organization and Architecture 7 Edition System BusesRubeshan ShanAinda não há avaliações

- Chapter3-Io OrganizationDocumento77 páginasChapter3-Io OrganizationPUNITH KUMAR VM100% (1)

- Computer Function: 1. Reading (Fetching) Instruction From Memory by CPU 2. Execution of Each Fetched InstructionDocumento19 páginasComputer Function: 1. Reading (Fetching) Instruction From Memory by CPU 2. Execution of Each Fetched Instructiondomainname9Ainda não há avaliações

- Real Time Computing and Programming - IntroDocumento19 páginasReal Time Computing and Programming - IntroNon ArtistsAinda não há avaliações

- Io Device ManagementDocumento56 páginasIo Device Managementbibek gautamAinda não há avaliações

- Operating System Module 5-Lecture 8: I/O HardwareDocumento10 páginasOperating System Module 5-Lecture 8: I/O HardwareBiswas LecturesAinda não há avaliações

- Name: S.Sai Ritheesh Reg No: 19BEC0847 Course Code: Ece3004 Faculty Name: Pradheep T Lab Slot: F1+TF1 DA: 1Documento9 páginasName: S.Sai Ritheesh Reg No: 19BEC0847 Course Code: Ece3004 Faculty Name: Pradheep T Lab Slot: F1+TF1 DA: 1Sai krishnaAinda não há avaliações

- Chapter 5Documento23 páginasChapter 5aliyiAinda não há avaliações

- UNIT-3: Processor and Control Unit by Anoop GuptaDocumento35 páginasUNIT-3: Processor and Control Unit by Anoop GuptaMingma Kanchhi SherpaAinda não há avaliações

- I/O Organizations and PeripheralsDocumento30 páginasI/O Organizations and PeripheralsSumit GuptaAinda não há avaliações

- OS Support Functions and ServicesDocumento65 páginasOS Support Functions and ServicesSadiholicAinda não há avaliações

- As Computer Science CH4Documento4 páginasAs Computer Science CH4Ahmed RazaAinda não há avaliações

- More Notes On ESDocumento25 páginasMore Notes On EScharles kiarieAinda não há avaliações

- William Stallings Computer Organization and Architecture 8 EditionDocumento59 páginasWilliam Stallings Computer Organization and Architecture 8 EditionjumarAinda não há avaliações

- OS Concepts: Hardware ReviewDocumento37 páginasOS Concepts: Hardware ReviewDimas setyaAinda não há avaliações

- I/O Management and Disk Scheduling (Chapter 11)Documento43 páginasI/O Management and Disk Scheduling (Chapter 11)anon_762600729Ainda não há avaliações

- I/O Organization and InterruptsDocumento15 páginasI/O Organization and InterruptsVarun VanaparthyAinda não há avaliações

- Chapter 7 - Input & OutputDocumento38 páginasChapter 7 - Input & OutputHPManchesterAinda não há avaliações

- CSC 205 - 2 Instruction Processing 2023-2024Documento35 páginasCSC 205 - 2 Instruction Processing 2023-2024hahnonimusAinda não há avaliações

- Operating System Assignment 1Documento11 páginasOperating System Assignment 1Utsav PreetAinda não há avaliações

- Processes: Lenmar T. Catajay, CoeDocumento62 páginasProcesses: Lenmar T. Catajay, Coebraynat kobeAinda não há avaliações

- Operating Systems Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesNo EverandOperating Systems Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesAinda não há avaliações

- 4) DSP-IIR Filters and Realization HW PDFDocumento29 páginas4) DSP-IIR Filters and Realization HW PDFnadheera ayishaAinda não há avaliações

- Design and Properties of FIR FiltersDocumento67 páginasDesign and Properties of FIR FiltersJohn NashAinda não há avaliações

- FFT AlgorithmsDocumento9 páginasFFT Algorithmsi_khandelwalAinda não há avaliações

- 7) DSP Finite Word Length-Hw PDFDocumento22 páginas7) DSP Finite Word Length-Hw PDFnadheera ayishaAinda não há avaliações

- Design and Properties of FIR FiltersDocumento67 páginasDesign and Properties of FIR FiltersJohn NashAinda não há avaliações

- 1.a) DSP - Frequency Analysis of DFT HWDocumento11 páginas1.a) DSP - Frequency Analysis of DFT HWnadheera ayishaAinda não há avaliações

- 3) DSP Filter Realization Structures HWDocumento20 páginas3) DSP Filter Realization Structures HWnadheera ayishaAinda não há avaliações

- 5) DSP - FIR Filters - 1 HW PDFDocumento25 páginas5) DSP - FIR Filters - 1 HW PDFnadheera ayishaAinda não há avaliações

- 2) DSP-IIR Filters HWDocumento23 páginas2) DSP-IIR Filters HWnadheera ayishaAinda não há avaliações

- MultivibratorsDocumento12 páginasMultivibratorsInam Rajj100% (1)

- 1) DSP FFT HWDocumento15 páginas1) DSP FFT HWnadheera ayishaAinda não há avaliações

- EC 2.analog ElectronicsDocumento258 páginasEC 2.analog ElectronicsBinoy NambiarAinda não há avaliações

- Digital Signal ProcessingDocumento5 páginasDigital Signal Processingnadheera ayishaAinda não há avaliações

- Computer Organisation and Architecture Module 2Documento18 páginasComputer Organisation and Architecture Module 2nadheera ayishaAinda não há avaliações

- Computer Organisation and Architecture Module 1Documento29 páginasComputer Organisation and Architecture Module 1nadheera ayishaAinda não há avaliações

- LIC ArunkumarDocumento520 páginasLIC ArunkumarPranavJoshiAinda não há avaliações

- Unit 4 - Clipper & Clamper by MehzabeenDocumento32 páginasUnit 4 - Clipper & Clamper by Mehzabeennadheera ayishaAinda não há avaliações

- AIC NotesFull Ktunotes - in PDFDocumento83 páginasAIC NotesFull Ktunotes - in PDFnadheera ayishaAinda não há avaliações

- Numerical Methods Chapter 10 SummaryDocumento8 páginasNumerical Methods Chapter 10 SummarynedumpillilAinda não há avaliações

- Pom Final On Rice MillDocumento21 páginasPom Final On Rice MillKashif AliAinda não há avaliações

- GlastonburyDocumento4 páginasGlastonburyfatimazahrarahmani02Ainda não há avaliações

- TDS Sibelite M3000 M4000 M6000 PDFDocumento2 páginasTDS Sibelite M3000 M4000 M6000 PDFLe PhongAinda não há avaliações

- 15142800Documento16 páginas15142800Sanjeev PradhanAinda não há avaliações

- DNA Gel Electrophoresis Lab Solves MysteryDocumento8 páginasDNA Gel Electrophoresis Lab Solves MysteryAmit KumarAinda não há avaliações

- Leaked David Fry II Conversation Regarding Loopholes and Embezzlement at AFK Gamer LoungeDocumento6 páginasLeaked David Fry II Conversation Regarding Loopholes and Embezzlement at AFK Gamer LoungeAnonymous iTNFz0a0Ainda não há avaliações

- The European Journal of Applied Economics - Vol. 16 #2Documento180 páginasThe European Journal of Applied Economics - Vol. 16 #2Aleksandar MihajlovićAinda não há avaliações

- Prenatal and Post Natal Growth of MandibleDocumento5 páginasPrenatal and Post Natal Growth of MandiblehabeebAinda não há avaliações

- Sharp Ar5731 BrochureDocumento4 páginasSharp Ar5731 Brochureanakraja11Ainda não há avaliações

- Motor Master 20000 SeriesDocumento56 páginasMotor Master 20000 SeriesArnulfo Lavares100% (1)

- Catalogoclevite PDFDocumento6 páginasCatalogoclevite PDFDomingo YañezAinda não há avaliações

- Data Sheet: Experiment 5: Factors Affecting Reaction RateDocumento4 páginasData Sheet: Experiment 5: Factors Affecting Reaction Ratesmuyet lêAinda não há avaliações

- Account Statement From 30 Jul 2018 To 30 Jan 2019Documento8 páginasAccount Statement From 30 Jul 2018 To 30 Jan 2019Bojpuri OfficialAinda não há avaliações

- Math5 Q4 Mod10 DescribingAndComparingPropertiesOfRegularAndIrregularPolygons v1Documento19 páginasMath5 Q4 Mod10 DescribingAndComparingPropertiesOfRegularAndIrregularPolygons v1ronaldAinda não há avaliações

- Level 3 Repair PBA Parts LayoutDocumento32 páginasLevel 3 Repair PBA Parts LayoutabivecueAinda não há avaliações

- 3 - Performance Measurement of Mining Equipments by Utilizing OEEDocumento8 páginas3 - Performance Measurement of Mining Equipments by Utilizing OEEGonzalo GarciaAinda não há avaliações

- Take This LoveDocumento2 páginasTake This LoveRicardo Saul LaRosaAinda não há avaliações

- ITU SURVEY ON RADIO SPECTRUM MANAGEMENT 17 01 07 Final PDFDocumento280 páginasITU SURVEY ON RADIO SPECTRUM MANAGEMENT 17 01 07 Final PDFMohamed AliAinda não há avaliações

- Towards A Human Resource Development Ontology Combining Competence Management and Technology-Enhanced Workplace LearningDocumento21 páginasTowards A Human Resource Development Ontology Combining Competence Management and Technology-Enhanced Workplace LearningTommy SiddiqAinda não há avaliações

- Rubber Chemical Resistance Chart V001MAR17Documento27 páginasRubber Chemical Resistance Chart V001MAR17Deepak patilAinda não há avaliações

- Petty Cash Vouchers:: Accountability Accounted ForDocumento3 páginasPetty Cash Vouchers:: Accountability Accounted ForCrizhae OconAinda não há avaliações

- Phys101 CS Mid Sem 16 - 17Documento1 páginaPhys101 CS Mid Sem 16 - 17Nicole EchezonaAinda não há avaliações

- If V2 would/wouldn't V1Documento2 páginasIf V2 would/wouldn't V1Honey ThinAinda não há avaliações