Escolar Documentos

Profissional Documentos

Cultura Documentos

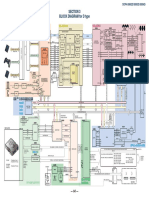

TLV320AIC3104 functional block diagram and register overview

Enviado por

Denis GomezDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

TLV320AIC3104 functional block diagram and register overview

Enviado por

Denis GomezDireitos autorais:

Formatos disponíveis

WCLK

DOUT

BCLK

DIN

4 5 2 3

TLV320AIC3104 Functional Block Diagram with Registers

All Output gains

All Output Volume gains HPLOUT Volume Are Positive in 1 dB steps

Sample Rate Select : (R2)

are in 0.5dB steps (0 to -78dB)

Codec Data Path Setup: (R7)

Audio Serial Data Interface Ctrl: (R8-R10 DAC_L1 Gain:

(R47) 0 to 9 dB

DAC_R1 (R50)

PGA_L (R46)

+

To enable Record-Only Digital Audio Processing PGA_R (R49) 19 HPLOUT

(shown with SW-Dx): DAC_L2 (R51)

1. Power Down Both DACs* (R37) All Register Numbers are in Decimal

Audio Serial Bus Interface and in Page 0 Unless Otherwise Noted

Left AGC control:

2. Enable ADC Digital Processing (R107)

(R26-R28, R32, R34, 3. 3-D Processing is not available in Record Mode

R103-R104) *DACs must be powered down in order to use ADC processing HPLCO M Volume

DOUTR

MIC2L

DOUTL

MIC2L/LINE2L/MICDET 14 (R37) Gain:

(0 to -78dB) HPLCOM

DINR

DINL

Gain: (R17, 0 to 9 dB

0 to -12 dB R18) DAC_L1 Drive Ctrl

(R54)

(R107-D3) (R43) DAC_R1 (R37)

1.5dB steps AGC (R57)

Gain: PGA_L (R53) + 20 HPLCOM

Volume PGA_R (R58)

0 to -63.5 dB (R56)

SW-D2 Control VCM

0.5dB steps

Bypass (R12-D3) Bypass (R12-D2)

(R8-D2) DAC_L1

PGA 1st 0 DAC (R37)

MIC1LP / LINE1LP 10 1st Ord DAC_L2 HPRCOM Volume Gain:

MIC1L + 0/59.5dB ADC Order 1 LB1 LB2 deemp

0 (0 to -78dB) 0 to 9 dB HPRCOM

MIC1LM / LINE1LM 11 L DAC_L3

Gain: (R19, 0.5dB steps L HP

SW-D1

1

DAC_L1 (R68) VCM Drive Ctrl

0 to -12 dB R24) Filter P1:R1-R6, P1:R7-R12,

(P1:R16-R21) (R41) DAC_R1 (R71) (R38)

R13-R16 R17-R20

1.5dB steps

(R15) (R12, D6-7) (R8-D2) PGA_L (R67) + 22 HPRCOM

(R107,D7) Normal Left Channel Processing PGA_R

(R70) (R72)

(P1:R65-R70)

PGA_L

Normal Processing and 3-D Processing are

HPROUT Volume

Left ADC PWR Mutually Exclusive. (R8-D2, 3-D Control)

(0 to -78dB)

Ctrl : (R19-D2)

DAC_L1 Gain:

(R61)

DAC_R1 0 to 9 dB

(R64)

Status Registers: L Ch + 1st

PGA_L (R60)

+

1. SC, BP, AGC, etc.(Sticky Int) – R96 (P1:R53-R54)

+ LB2

Ord DAC PGA_R (R63) 23 HPROUT

2. SC, BP, AGC, etc.(Realtime Int) – R97 + + PWR (R37)

3. ADC Flags – R36 + LB1 Atten DAC_R2 (R65)

- - DAC Current

1st

+ RB2

Ord CTL (R109) High Power

R Ch + Output Stage Ctrl SW-L2

Right AGC control: (R40) LINE2LP

(R29-R31, R33, R35,

SW-L1

R105-R106) 3-D Digital Audio Processing LINE1LP

DAC_L3

LEFT_LOP/M Gain:

0 to 9 dB SW-L0

(R107-D3) Volume

AGC (0 to -78dB) 27 LEFT_LOP

DAC_L1 (R82) SW-L3

SW-D4 DAC_R1 (R85) 28 LEFT_LOM

Bypass (R12-D3) Bypass (R12-D2)

(R41) PGA_L

(R81) + (R86)

SW-L4

DAC_R1 PGA_R (R84)

LINE1LM

PGA 1st 1 1 DAC DAC_R2

MIC1RP / LINE1RP 12 LINE1R

+ ADC Order 0 1st Ord R

0/59.5dB HP RB1 RB2 deemp

0 DAC_R3

MIC1RM / LINE1RM 13 (R21, R SW-D3

Gain: 0.5dB steps Filter (R8-D2)

0 to -12 dB R22) P1:R1-R6, P1:R7-R12, (R8-D2) Gain:

(P1:R16-R21) Volume

1.5dB steps (R12, D4-5) R13-R16 R17-R20 0 to -63.5 dB SW-Lx and SW-Rx switches

(R16) Control are programmed in R108

(R107,D6) Normal Left Channel Processing 0.5dB steps

(P1:R71-R76)

(R44)

PGA_R

SW-R2

RIGHT_LOP/M LINE2RP

Right ADC PWR

Ctrl : (R22-D2)

Relevant App notes: Volume

SW-R1

MIC2R/LINE2R 16 LINE2R 1. TLV320AIC3104 Programming Made Easy (SLAA403) (0 to -78dB)

LINE1RP

(R17, 2. Common Noise issues in audio Codecs (SLAA749) DAC_L1 (R89)

Gain:

R18) DAC_R1 (R92)

0 to -12 dB 3. The Built-In AGC Function (SLAA260) PGA_L + SW-R0

1.5dB steps (R88) 29

4. Out-of-Band Noise measurement Issues for Audio Codecs (SLAA313) PGA_R (R91)

SW-R3

5. The Built-In AGC Function (SLAA260)

30

6. Using AIC3x with TDM support (SLAA311) DAC_R3

(R93)

SW-R4

LINE1RM

PLL Regs : (R3-R6)

CODEC_CLKIN : (R101)

MICBIAS Ctrl: CLKDIV_IN/PLLCLK_IN Software Reset (R1)

(R25) Select : R102 I2C Status (R107)

Bias/ Audio Clock I2C Serial

Voltage Supplies Reference Generation Control Bus

BCLK

17 26 25 18 24 21 32 7 6 15 1 31 8 9

IOVDD

MICBIAS

DRVDD

DRVDD

Reset

MCLK

DVDD

AVSS1

AVSS2

SCL

SDA

DRVSS

AVDD

DVSS

Você também pode gostar

- N9 and N10 With SCR (2014 - 2016) : Engine Wiring Diagram Engine Control Module (ECM)Documento4 páginasN9 and N10 With SCR (2014 - 2016) : Engine Wiring Diagram Engine Control Module (ECM)Phil B.Ainda não há avaliações

- Section 3 Block Diagram For D Type: Reproduction ProhibitedDocumento37 páginasSection 3 Block Diagram For D Type: Reproduction ProhibitedBrahim TelliAinda não há avaliações

- Installation, Support, and Maintenance Guide: X7 Series Satellite RouterDocumento66 páginasInstallation, Support, and Maintenance Guide: X7 Series Satellite RouterEddy GuttyAinda não há avaliações

- Chapter 1 What Is Data Engineering PDFDocumento79 páginasChapter 1 What Is Data Engineering PDFChandra PutraAinda não há avaliações

- CCNP Exam Dumps Collection (3 - 2FFeb - 2F2018) - PDF - Cisco Systems - Cloud ComputingDocumento23 páginasCCNP Exam Dumps Collection (3 - 2FFeb - 2F2018) - PDF - Cisco Systems - Cloud ComputingapollokimoAinda não há avaliações

- SCADA System OverviewDocumento45 páginasSCADA System OverviewalexlakimikapestaAinda não há avaliações

- Service Manual: Rmx-40 DSPDocumento49 páginasService Manual: Rmx-40 DSPSándor VámosAinda não há avaliações

- TSL1401Documento8 páginasTSL1401Chế ThiệnAinda não há avaliações

- SCH TPM 8200ac-Dc 25-01-08 PDFDocumento9 páginasSCH TPM 8200ac-Dc 25-01-08 PDFLuis Manuel Alonso Salcedo100% (1)

- Alpha1 Series PC Communication Protocol561785 PDFDocumento1 páginaAlpha1 Series PC Communication Protocol561785 PDFpancawawanAinda não há avaliações

- Pin definitions and parts names for Delta HMI serial communicationDocumento2 páginasPin definitions and parts names for Delta HMI serial communicationCanek UnoAinda não há avaliações

- TLV1543 ADC SPI 10bits 11 VoiesDocumento30 páginasTLV1543 ADC SPI 10bits 11 Voiesloic.savorninAinda não há avaliações

- 530AOD01 DS en PDFDocumento4 páginas530AOD01 DS en PDFHatem LaadhariAinda não há avaliações

- Cmos, 330 MHZ Triple 10-Bit High Speed Video Dac Adv7123: Features Functional Block DiagramDocumento25 páginasCmos, 330 MHZ Triple 10-Bit High Speed Video Dac Adv7123: Features Functional Block Diagramhash defineAinda não há avaliações

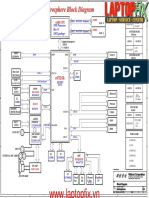

- WWW - Laptopfix.vn: Astrosphere Block DiagramDocumento44 páginasWWW - Laptopfix.vn: Astrosphere Block DiagramDaniel LiraAinda não há avaliações

- Ilive Range Block-Diagram 2Documento1 páginaIlive Range Block-Diagram 2Sandi SimonAinda não há avaliações

- 5002086X4 MC wiringDocumento1 página5002086X4 MC wiringzuntoy000Ainda não há avaliações

- E7f3e HP G60 AMD Wistron Astrosphere (MCP77 07241-3)Documento44 páginasE7f3e HP G60 AMD Wistron Astrosphere (MCP77 07241-3)Edward Franz Pizarro CasioAinda não há avaliações

- FX504GM 1.0 FX80GM SchematicDocumento60 páginasFX504GM 1.0 FX80GM SchematicSDFVBNAinda não há avaliações

- DA216ADocumento4 páginasDA216AEl KacrutoAinda não há avaliações

- D D D D D D: SN54ABT640, SN74ABT640 Octal Bus Transceivers With 3-State OutputsDocumento8 páginasD D D D D D: SN54ABT640, SN74ABT640 Octal Bus Transceivers With 3-State OutputsStuxnetAinda não há avaliações

- RGBW/RGB/CCT/Dimming 4 Channel LED RF Controller: Model No.: C4 (150-500ma) / C4 (350-1200ma)Documento2 páginasRGBW/RGB/CCT/Dimming 4 Channel LED RF Controller: Model No.: C4 (150-500ma) / C4 (350-1200ma)justfanloveAinda não há avaliações

- 3CPU板3Documento1 página3CPU板3MARIA FERNANDA MORA AREVALOAinda não há avaliações

- Wistron GodzillaDocumento61 páginasWistron Godzillarodrigootavio5Ainda não há avaliações

- High Quality, 10-Bit, Digital CCIR-601 To PAL/NTSC Video EncoderDocumento50 páginasHigh Quality, 10-Bit, Digital CCIR-601 To PAL/NTSC Video EncoderJuan HernándezAinda não há avaliações

- Sony Vaio PCG-K13 Quanta JE2Documento38 páginasSony Vaio PCG-K13 Quanta JE2luckyman7Ainda não há avaliações

- Compact 1 point relay terminal block specificationsDocumento1 páginaCompact 1 point relay terminal block specificationsFuck youAinda não há avaliações

- NTX-240 Substation Controller Cabinet LayoutDocumento9 páginasNTX-240 Substation Controller Cabinet LayoutJan Richardo GultomAinda não há avaliações

- TLC 7226Documento25 páginasTLC 7226vargasvAinda não há avaliações

- MT1389E DVD Demo BoardDocumento4 páginasMT1389E DVD Demo BoardEnya Andrea Ribba Hernandez100% (1)

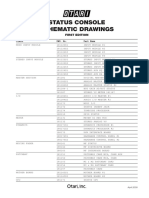

- Status Console Schematic Drawings: First EditionDocumento39 páginasStatus Console Schematic Drawings: First EditionMarcos AmadoAinda não há avaliações

- ADocumento1 páginaAalimorshedi100% (1)

- Gyro & LOG To NMEA Converter: Model SR01-40Documento3 páginasGyro & LOG To NMEA Converter: Model SR01-40sajujohnyAinda não há avaliações

- Service Manual: Model: APM200Documento55 páginasService Manual: Model: APM200VASILIY GRACHEVAinda não há avaliações

- AD9020Documento12 páginasAD9020RuslanAinda não há avaliações

- Hyundai h-cmd4004 dv7891Documento12 páginasHyundai h-cmd4004 dv7891MantasPuskoriusAinda não há avaliações

- Foxconn m9f1 r1.0 SchematicsDocumento47 páginasFoxconn m9f1 r1.0 SchematicsnivaldoAinda não há avaliações

- ASUS GL703GE 1.0 Schematic0 - 15 - 0 PDFDocumento59 páginasASUS GL703GE 1.0 Schematic0 - 15 - 0 PDFEnder özveriAinda não há avaliações

- CA I - Chapter 3 RISC V ProcessorDocumento100 páginasCA I - Chapter 3 RISC V ProcessorDuc ToanAinda não há avaliações

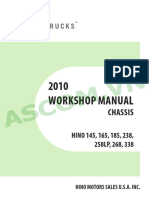

- 2010 Chassis Workshop ManualDocumento1.289 páginas2010 Chassis Workshop ManualXuân VinhAinda não há avaliações

- Quanta BKXB - SCHDocumento60 páginasQuanta BKXB - SCHTech CentralAinda não há avaliações

- 520AOD01 DS enDocumento5 páginas520AOD01 DS enDJ ThangAinda não há avaliações

- 23 Urban CruiserDocumento1 página23 Urban CruiserHEMIL ROBERTO RODRIGUEZ HERRERAAinda não há avaliações

- Application Note - DAC OutputDocumento4 páginasApplication Note - DAC OutputCosmin Popescu100% (1)

- Dolby Pro Logic II DecoderDocumento19 páginasDolby Pro Logic II DecoderrohanscreationsAinda não há avaliações

- LG Chassis Mc-994aDocumento2 páginasLG Chassis Mc-994aYaindolimasAinda não há avaliações

- Operation Panel Board FunctionsDocumento2 páginasOperation Panel Board FunctionsnickususAinda não há avaliações

- V0D0042305 Projector Services ManualDocumento2 páginasV0D0042305 Projector Services ManualkastruiAinda não há avaliações

- Wistron jv50-cp RSB SchematicsDocumento68 páginasWistron jv50-cp RSB SchematicsАлекс ХомичAinda não há avaliações

- Aspire E5-522 - ZRZL - ZRZDocumento40 páginasAspire E5-522 - ZRZL - ZRZAdmin 010% (1)

- Ag06 en Ts A0 PDFDocumento2 páginasAg06 en Ts A0 PDFKarina RoquelAinda não há avaliações

- VOX AC15C1 Service ManualDocumento22 páginasVOX AC15C1 Service Manualblondeb3Ainda não há avaliações

- Project code overviewDocumento42 páginasProject code overviewHamter YoAinda não há avaliações

- Class D Audio Amplifier Circuit DiagramDocumento1 páginaClass D Audio Amplifier Circuit Diagramnegrelli-rn100% (1)

- G14 document outlines vehicle battery and diagnostic connector pin functionsDocumento1 páginaG14 document outlines vehicle battery and diagnostic connector pin functionsSerg GarkushaAinda não há avaliações

- Sony Vaio VPC-M Series PCG-21313M (Foxconn M9F1) PDFDocumento46 páginasSony Vaio VPC-M Series PCG-21313M (Foxconn M9F1) PDFDanny CelyAinda não há avaliações

- Schematic Tpa3116d2-Xh-M543 Sheet 1 20191123193718Documento1 páginaSchematic Tpa3116d2-Xh-M543 Sheet 1 20191123193718dougftvc100% (2)

- Stepper Motor Speed Control using Cell PhoneDocumento49 páginasStepper Motor Speed Control using Cell PhoneUjwal JaiswalAinda não há avaliações

- SFBW01 Project System Block DiagramDocumento36 páginasSFBW01 Project System Block DiagramMario Rodriguez Jurado100% (3)

- Buffer memory functions and default valuesDocumento8 páginasBuffer memory functions and default valuesIGHORODJEAinda não há avaliações

- Electrical Wiring Diagram (KX015-4, KX016-4) : 60498-77721 W/H (Cab)Documento1 páginaElectrical Wiring Diagram (KX015-4, KX016-4) : 60498-77721 W/H (Cab)anna tóthAinda não há avaliações

- Anais Do Workshop De Micro-ondasNo EverandAnais Do Workshop De Micro-ondasAinda não há avaliações

- Eia Cea 608Documento154 páginasEia Cea 608Максим РадионовAinda não há avaliações

- Sip LogDocumento173 páginasSip LogCristy EaddyAinda não há avaliações

- Cisco Catalyst 2960X-24PS-L Switch DatasheetDocumento6 páginasCisco Catalyst 2960X-24PS-L Switch DatasheetFREE SOFTWARE DOWNLOADAinda não há avaliações

- KDC-MP242U/MP342U KDC-MP443U/MP5043U KDC-MP543U: Service ManualDocumento46 páginasKDC-MP242U/MP342U KDC-MP443U/MP5043U KDC-MP543U: Service ManualCarol Eduardo Apitz DíazAinda não há avaliações

- Lecture 28Documento15 páginasLecture 28KumarAinda não há avaliações

- Time Division MultiplexingDocumento23 páginasTime Division MultiplexingAshish Ranjan0% (1)

- Imaster NCE-FAN V100R022C10 Product Description (Access Manager & Controller, Carrier) 02Documento242 páginasImaster NCE-FAN V100R022C10 Product Description (Access Manager & Controller, Carrier) 02ft6wmn5t2qAinda não há avaliações

- Linux Socials Botocamp DataDocumento7 páginasLinux Socials Botocamp DataFungsūk WangdúAinda não há avaliações

- Spectral EfficiencyDocumento13 páginasSpectral EfficiencyClark Linogao FelisildaAinda não há avaliações

- Why Migrate To p25 Digital LMR White Paper GlobalDocumento8 páginasWhy Migrate To p25 Digital LMR White Paper Global北梦Ainda não há avaliações

- EX300 User Manual V1.1 PDFDocumento17 páginasEX300 User Manual V1.1 PDFLuis Enrique GuzmanAinda não há avaliações

- 2014transport LayerDocumento25 páginas2014transport LayerNahidaNigarAinda não há avaliações

- CS425 Session and Presentation LayersDocumento6 páginasCS425 Session and Presentation LayersAnish VeettiyankalAinda não há avaliações

- PL Vention 20220721 Flat7.5Documento16 páginasPL Vention 20220721 Flat7.5lomoholic2000Ainda não há avaliações

- Deploying Optimized Multicast in EvpnvxlanDocumento186 páginasDeploying Optimized Multicast in EvpnvxlanLi KangAinda não há avaliações

- Master Slave Flip Flop-1Documento3 páginasMaster Slave Flip Flop-1Najiya NajiAinda não há avaliações

- Types of Delays that Impact ASIC DesignDocumento17 páginasTypes of Delays that Impact ASIC DesignJayanth bemesettyAinda não há avaliações

- Mni Ision: Ov7950/Ov7451 Cmos Analog NTSC C C With Omnipixel TechnologyDocumento31 páginasMni Ision: Ov7950/Ov7451 Cmos Analog NTSC C C With Omnipixel Technologymike chenAinda não há avaliações

- Finepix xp130 Catalogue 01Documento2 páginasFinepix xp130 Catalogue 01Admin Ops Inspeksi TeknikAinda não há avaliações

- 1TGC901080M0202 - System Clock Manual V2.3Documento22 páginas1TGC901080M0202 - System Clock Manual V2.3Abhijith SreevalsamAinda não há avaliações

- Mediant 800 Gateway e SBC Users Manual Ver 74Documento2.022 páginasMediant 800 Gateway e SBC Users Manual Ver 74locuras34Ainda não há avaliações

- Manual Tenda Wireless-N Router w268r enDocumento72 páginasManual Tenda Wireless-N Router w268r enshinobisefirotAinda não há avaliações

- SavatteriDocumento5 páginasSavatteriJohn EucilliaAinda não há avaliações

- Perkembangan Dan Masa Depan Telemedika Di Indonesia: Information and Communication Technology (ICT) YangDocumento8 páginasPerkembangan Dan Masa Depan Telemedika Di Indonesia: Information and Communication Technology (ICT) YangDebi MeilaniAinda não há avaliações

- Multi Carrier Cell Re-selection in LTEDocumento7 páginasMulti Carrier Cell Re-selection in LTEyounes CcAinda não há avaliações

- Measuring Teachers Readiness in Implementing VLE (Virtual Learning Environment) in Primary Classroom (24pgs)Documento24 páginasMeasuring Teachers Readiness in Implementing VLE (Virtual Learning Environment) in Primary Classroom (24pgs)Nisa Ben YunusAinda não há avaliações