Escolar Documentos

Profissional Documentos

Cultura Documentos

Digital Systems Design Using VHDL

Enviado por

K Praveen KumarDescrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Digital Systems Design Using VHDL

Enviado por

K Praveen KumarDireitos autorais:

Formatos disponíveis

Q6 Q6

www.jntuworld.com Q6 Q6 Q6

www.android.jntuworld.com Q6 Q6 Q6

www.jwjobs.net

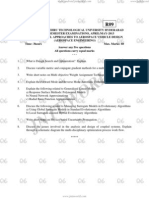

Code No: D5504

R09

Q6 Q6 Q6 Q6 Q6

JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

M.Tech II SEMESTER EXAMINATIONS, APRIL/MAY-2013

Q6 Q6 Q6

CPLD AND FPGA ARCHITECTURES AND APPLICATIONS

(EMBEDDED SYSTEMS)

Time: 3hours Max.Marks:60

Answer any five questions

Q6 Q6 Q6 Q6 Q6

All questions carry equal marks

---

Q6 Q6 Q6

1. Design a 4-bit Majority function generator and implement it with a suitable PAL.

2. With block diagram explain the Macro Cell of Altera 7000 CPLD.

Q6 Q6

3.

Q6 Q6 Q6

Explain, in detail, every block of FLEX 10000 Device.

Q6 Q6 Q6

Q6

4.

5.

Q6

Write down the behavioural model for XC4000 CLB

Q6 Q6 Q6 Q6 L D

Explain the alternative realizations for SM charts using microprogramming with

Q6 Q6

R

suitable examples.

O

6. Demonstrate the one-hot state assignment and discuss its advantages using an

example.

Q6 7.

Q6

8.

Q6 Q6

U W

Discuss the features of Mentor Graphics EDA tool.

Q6 Q6

A 4×4 array multiplier is to be implemented using an XC4000 family FPGA.

Q6

Without using the built-in-carry logic, partition the logic so that it fits in a

Q6

Q6 Q6 Q6

required.

N T

minimum number of logic cells. Draw loops around each set of components that

will fit in a single logic cell. Find the total number of F and G function generators

Q6 Q6 Q6 Q6 Q6

J *****

Q6 Q6 Q6 Q6 Q6 Q6 Q6 Q6

Q6 Q6 Q6 Q6 Q6 Q6 Q6 Q6

Q6 Q6 Q6 Q6 Q6 Q6 Q6 Q6

www.jntuworld.com

Você também pode gostar

- Advanced Control SystemsDocumento2 páginasAdvanced Control SystemsIbmWasuserAinda não há avaliações

- WWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksDocumento1 páginaWWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksSarath Chandra SuraganiAinda não há avaliações

- Advanced Power System ProtectionDocumento1 páginaAdvanced Power System ProtectionIbmWasuser100% (2)

- Simulation and ModelingDocumento15 páginasSimulation and ModelingMASUDI MWAKOJAAinda não há avaliações

- 9D57106c ASIC DesignDocumento1 página9D57106c ASIC DesignsubbuAinda não há avaliações

- Integration Qns Set 1Documento13 páginasIntegration Qns Set 1AnshumanAinda não há avaliações

- Modern Study 1Documento1 páginaModern Study 1D RivronAinda não há avaliações

- Ex3M. Hffi) G: Examination Control Division Moa4Ygsij!3)Documento20 páginasEx3M. Hffi) G: Examination Control Division Moa4Ygsij!3)wilsonshespAinda não há avaliações

- Intel Westmere and Nehalem Xeon Server CPU CompareDocumento3 páginasIntel Westmere and Nehalem Xeon Server CPU CompareChirag A GandhiAinda não há avaliações

- Vivekananda Institute of Professional StudiesDocumento25 páginasVivekananda Institute of Professional Studiesman ironAinda não há avaliações

- Industrial Automation Paper - MEDocumento8 páginasIndustrial Automation Paper - MEShrinivas GAinda não há avaliações

- 2017 IT Dec2017 PDFDocumento1 página2017 IT Dec2017 PDFShubhamAinda não há avaliações

- Break-Up SyllabusDocumento16 páginasBreak-Up SyllabusMussoorieAinda não há avaliações

- WWW - Manaresults.Co - In: Design For TestabilityDocumento2 páginasWWW - Manaresults.Co - In: Design For TestabilitykishorechiyaAinda não há avaliações

- Floor Layout Glasspex India - 2019Documento1 páginaFloor Layout Glasspex India - 2019Puja RoyAinda não há avaliações

- BRKSPG 2280Documento44 páginasBRKSPG 2280ali partoviAinda não há avaliações

- Kotronias Classical Systems-ExcerptDocumento18 páginasKotronias Classical Systems-ExcerptUjaan BhattacharyaAinda não há avaliações

- The Technical White Paper-Tiger Module PDFDocumento17 páginasThe Technical White Paper-Tiger Module PDFSAEL SOLARAinda não há avaliações

- IC Engine Lab AssignmentDocumento1 páginaIC Engine Lab Assignment21UME023 RATNADEEP CHAKRABORTYAinda não há avaliações

- Gigabyte Technology Socket 775 - Intel g31 - Ga-G31m-S2l (Rev. 1Documento5 páginasGigabyte Technology Socket 775 - Intel g31 - Ga-G31m-S2l (Rev. 1Lucas DuraesAinda não há avaliações

- Automobile Engineering PDFDocumento66 páginasAutomobile Engineering PDFMass Maharaja ObulAinda não há avaliações

- Automobile EngineeringDocumento66 páginasAutomobile EngineeringRaj KapoorAinda não há avaliações

- Automobile Engineering PDFDocumento66 páginasAutomobile Engineering PDFLokesh RajputAinda não há avaliações

- XXXXDocumento17 páginasXXXXAlbert LlatasAinda não há avaliações

- Ipjugaad - Bajmc 3rd Sem Radio Jockeying and News Reading Paper 2017Documento2 páginasIpjugaad - Bajmc 3rd Sem Radio Jockeying and News Reading Paper 2017The Shantanu KumarAinda não há avaliações

- SOM White Background Vivek Gupta PDFDocumento618 páginasSOM White Background Vivek Gupta PDFMr. Shivam Gupta67% (3)

- Mechanical Related JournalsDocumento6 páginasMechanical Related JournalsAshwini KumarAinda não há avaliações

- Computational Approaches To Aerospace Vehicle DesignDocumento1 páginaComputational Approaches To Aerospace Vehicle DesignIbmWasuserAinda não há avaliações

- Mup Module 1Documento47 páginasMup Module 1Abhimanyu AromalAinda não há avaliações

- Bcca 4 Sem Core Java Paper 3 Summer 2018Documento2 páginasBcca 4 Sem Core Java Paper 3 Summer 2018ashfaqAinda não há avaliações

- Question Bank of Unit 3,4, 5,6Documento2 páginasQuestion Bank of Unit 3,4, 5,6techaddictiveblogsAinda não há avaliações

- From PG 331 To 334 M.E (2017 PATTERN)Documento4 páginasFrom PG 331 To 334 M.E (2017 PATTERN)manashAinda não há avaliações

- Xilinx XC2C64A-7VQG44C - 5G Technology - Industrial ControlDocumento4 páginasXilinx XC2C64A-7VQG44C - 5G Technology - Industrial ControljackAinda não há avaliações

- Accademic SkillDocumento3 páginasAccademic SkillcombtmpfaprwAinda não há avaliações

- Som Notes Vivek Gupta 22.6.22-1-InvertDocumento616 páginasSom Notes Vivek Gupta 22.6.22-1-InvertAnkush rajAinda não há avaliações

- Analog & Digital Electronics Lab (ESC 391) : Full Adder Circuit Using MUX ICDocumento3 páginasAnalog & Digital Electronics Lab (ESC 391) : Full Adder Circuit Using MUX ICpogboi2342Ainda não há avaliações

- Muhammad Hud Bin Muhammad Ismail Form ADocumento2 páginasMuhammad Hud Bin Muhammad Ismail Form AMuhd HudAinda não há avaliações

- 史都華平台之仿生物演算法模糊強化學習控制與FPGA實現Documento99 páginas史都華平台之仿生物演算法模糊強化學習控制與FPGA實現李金輝Ainda não há avaliações

- Artificial Intelligence: Foundations & Applications: Prof. Partha P. Chakrabarti & Arijit MondalDocumento34 páginasArtificial Intelligence: Foundations & Applications: Prof. Partha P. Chakrabarti & Arijit MondalAnil YogiAinda não há avaliações

- CDocumento99 páginasCDonna Mae SibayanAinda não há avaliações

- AsdwDocumento74 páginasAsdwamel joyAinda não há avaliações

- QP 2018Documento8 páginasQP 2018Ashkar AshrafAinda não há avaliações

- SurveyDocumento3 páginasSurveyAnonymous mfbe373zFDAinda não há avaliações

- Qualified Vendors List (QVL) : B C Size Vendor Model CL Brand Ss/Ds ComponentDocumento3 páginasQualified Vendors List (QVL) : B C Size Vendor Model CL Brand Ss/Ds Componentamihaita3018Ainda não há avaliações

- Performance Improvement of QCA Design XOR Logic Gate Using Bistable Simulation Engine VectorDocumento4 páginasPerformance Improvement of QCA Design XOR Logic Gate Using Bistable Simulation Engine VectorEditor IJTSRDAinda não há avaliações

- P4P800 Se QVLDocumento3 páginasP4P800 Se QVLSandor EstokAinda não há avaliações

- Last 24 Hours Java ImpDocumento1 páginaLast 24 Hours Java Impprajwalpatil224466Ainda não há avaliações

- H55 HD PCB 6.XDocumento2 páginasH55 HD PCB 6.XVladmir AmorimAinda não há avaliações

- Qorivva MPC5500 Minimum Board Requirements: Application NoteDocumento49 páginasQorivva MPC5500 Minimum Board Requirements: Application NotefengheAinda não há avaliações

- Structure by Vivek GuptaDocumento637 páginasStructure by Vivek GuptajamunaAinda não há avaliações

- Lllit5: Embedded System DesignDocumento4 páginasLllit5: Embedded System DesignAnonymous 2MwnnyAinda não há avaliações

- Lang PointPillars Fast Encoders For Object Detection From Point Clouds CVPR 2019 PaperDocumento9 páginasLang PointPillars Fast Encoders For Object Detection From Point Clouds CVPR 2019 Paper姜峰Ainda não há avaliações

- Vlsi DesignDocumento2 páginasVlsi DesignXXXAinda não há avaliações

- Embedded System Design PDFDocumento37 páginasEmbedded System Design PDFLavanya R GowdaAinda não há avaliações

- 施耐德电气低压配电产品选型手册Documento464 páginas施耐德电气低压配电产品选型手册DUANAinda não há avaliações

- Quadcopter Project ThesisDocumento8 páginasQuadcopter Project Thesisafiwfnofb100% (2)

- IFS Portal Hunt - Expert Decoder TemplateDocumento14 páginasIFS Portal Hunt - Expert Decoder TemplateDeependra SinghAinda não há avaliações

- BC 302 PI Past PapersDocumento15 páginasBC 302 PI Past PapersDucky 6Ainda não há avaliações

- Co 4&5 Questionbank SE23Documento4 páginasCo 4&5 Questionbank SE23Rajeshwari R PAinda não há avaliações

- BEEE Unit I MaterialDocumento93 páginasBEEE Unit I MaterialK Praveen KumarAinda não há avaliações

- A Robust Kalman Filter Design For Image RestorationDocumento4 páginasA Robust Kalman Filter Design For Image RestorationK Praveen KumarAinda não há avaliações

- A Nash-Game Approach For Image Restoration and SegmentationDocumento1 páginaA Nash-Game Approach For Image Restoration and SegmentationK Praveen KumarAinda não há avaliações

- A Review of Adaptive Image Representations: Gabriel PeyréDocumento16 páginasA Review of Adaptive Image Representations: Gabriel PeyréK Praveen KumarAinda não há avaliações

- Alessandro Neri: Index Terms - Gauss-Laguerre Circular Harmonic FuncDocumento8 páginasAlessandro Neri: Index Terms - Gauss-Laguerre Circular Harmonic FuncK Praveen KumarAinda não há avaliações

- Spatial Image Processing For The Enhancement and Restoration of Film, Photography and PrintDocumento8 páginasSpatial Image Processing For The Enhancement and Restoration of Film, Photography and PrintK Praveen KumarAinda não há avaliações

- A Review: Image Compensation TechniquesDocumento5 páginasA Review: Image Compensation TechniquesK Praveen KumarAinda não há avaliações

- Review: Digital Object Identifier 10.1109/MSP.2008.924962Documento2 páginasReview: Digital Object Identifier 10.1109/MSP.2008.924962K Praveen KumarAinda não há avaliações

- Dell Latitude 7280 Compal CAZ10 LA-E121P Rev 0.1 SchematicDocumento52 páginasDell Latitude 7280 Compal CAZ10 LA-E121P Rev 0.1 SchematicCze GoogAinda não há avaliações

- Iot Based Automatic College Gong: S.Arockia Ranjith Kumar, R.Glarwin, M.Gowthamaraj, M.K.Vijayanainar, G.ShunmugalakshmiDocumento3 páginasIot Based Automatic College Gong: S.Arockia Ranjith Kumar, R.Glarwin, M.Gowthamaraj, M.K.Vijayanainar, G.ShunmugalakshmiMohseen SAinda não há avaliações

- HP z600 Workstation Datasheet (2010.09-Sep)Documento2 páginasHP z600 Workstation Datasheet (2010.09-Sep)JSSmithAinda não há avaliações

- Fina Points Calculator 2008 v2.0Documento12 páginasFina Points Calculator 2008 v2.0Nenad BoskovicAinda não há avaliações

- Lesson 2 Computer HardwareDocumento22 páginasLesson 2 Computer HardwarerommelAinda não há avaliações

- It - Unit 14 - Assignment 2 Jacob MayDocumento6 páginasIt - Unit 14 - Assignment 2 Jacob Mayapi-609785537Ainda não há avaliações

- Wii - Presentation Final VersionDocumento18 páginasWii - Presentation Final VersionFuse ChiuAinda não há avaliações

- HP Laptop 15-bs0xx Service ManualDocumento67 páginasHP Laptop 15-bs0xx Service ManualChintha Weliwatta75% (4)

- MD 100T00 ENU PowerPoint - M01Documento38 páginasMD 100T00 ENU PowerPoint - M01CourageMarumeAinda não há avaliações

- File ListDocumento22 páginasFile Listtony tAinda não há avaliações

- Basler Pilot Pia Camera Brochure - enDocumento6 páginasBasler Pilot Pia Camera Brochure - enKUMA1999Ainda não há avaliações

- SSK3000 Information Technology & Its Application: SEMESTER2 2015/2016Documento12 páginasSSK3000 Information Technology & Its Application: SEMESTER2 2015/2016Nasrullah roslanAinda não há avaliações

- Rog Rampage Vi Extreme Omega Dram QVL v3.0Documento20 páginasRog Rampage Vi Extreme Omega Dram QVL v3.0murat akdemirAinda não há avaliações

- Find A Laptop Motherboard Manufacturer PDFDocumento5 páginasFind A Laptop Motherboard Manufacturer PDFHamad ZiaAinda não há avaliações

- I-On Updater - Installation and User GuideDocumento8 páginasI-On Updater - Installation and User GuideGeorge Theodorou100% (1)

- Vmware Imp FaqsDocumento37 páginasVmware Imp FaqsNirav PatelAinda não há avaliações

- Applied Electronics Watermark PDFDocumento2 páginasApplied Electronics Watermark PDFRajat TaydeAinda não há avaliações

- Ways To Install Windows 11Documento5 páginasWays To Install Windows 11Jeff LAinda não há avaliações

- Recovering A Corrupt Cisco IOS Image On A 2500 Series RouterDocumento4 páginasRecovering A Corrupt Cisco IOS Image On A 2500 Series RouterHamami InkaZoAinda não há avaliações

- WPST R2.00 User GuideDocumento37 páginasWPST R2.00 User Guidemazen ahmedAinda não há avaliações

- Digi Conect SPDocumento2 páginasDigi Conect SPRonie ToledoAinda não há avaliações

- DBCS Hardware Service Manual PDFDocumento228 páginasDBCS Hardware Service Manual PDFΝΑΝΟΣ ΑΘΑΝΑΣΙΟΣAinda não há avaliações

- Compal La-7551p r1.0 Schematics PDFDocumento54 páginasCompal La-7551p r1.0 Schematics PDFJose Barroso GuerraAinda não há avaliações

- LeveloggerGold V3Documento74 páginasLeveloggerGold V3mojoboogyAinda não há avaliações

- Compal Confidential: Hasswell M/B Schematics DocumentDocumento60 páginasCompal Confidential: Hasswell M/B Schematics DocumentBabinVitaly VinlaptopAinda não há avaliações

- Spi 525Documento35 páginasSpi 525Milena Novato SilvaAinda não há avaliações

- h61 s2p SchematicsDocumento32 páginash61 s2p SchematicsJayesh Dalvi50% (2)

- Microprocessor Assignment (Assignment-2)Documento7 páginasMicroprocessor Assignment (Assignment-2)Ajay SahuAinda não há avaliações

- FAQ (1 of 5) : EM Mode Boot Procedures (Please Read... - Buffalo Tech ForumsDocumento3 páginasFAQ (1 of 5) : EM Mode Boot Procedures (Please Read... - Buffalo Tech ForumsNinjacearenseAinda não há avaliações

- Freertos Arm CortexDocumento344 páginasFreertos Arm Cortexshabid.ali373100% (3)