Escolar Documentos

Profissional Documentos

Cultura Documentos

VSP Lec00 PDF

Enviado por

Manish ChavdaTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

VSP Lec00 PDF

Enviado por

Manish ChavdaDireitos autorais:

Formatos disponíveis

VLSI Signal Processing

Systems

Chih-Wei Liu

cwliu@twins.ee.nctu.edu.tw

VSP Lecture0 - Chih-Wei Liu 1

(cwliu@twins.ee.nctu.edu.tw)

Course Information

• Lecture:

– Chih-Wei Liu 劉志尉

cwliu@twins.ee.nctu.edu.tw

–TEL: 5731685

–ED618

‧Teaching Assistants:

– 歐士豪 shou@twins.ee.nctu.edu.tw

– TEL: ext 54225

– ED412

VSP Lecture0 - Chih-Wei Liu (cwliu@twins.ee.nctu.edu.tw) 2

Course Information

• Text

– Keshab K. Parhi, VLSI Digital Signal Processing

Systems – Design and Implementation, Wiely, 1999

• Project

– The project can be individual project or a group project

– Project type can be either theory/algorithm

development type or implementation type

– Project report is required to be submitted before the

end of this course

– At the last week of this course, project presentation

will take place in class

• Course Grade

– Home work and project report (50%)

– Midterm Exam. 25%

– Final Exam. 25%

VSP Lecture0 - Chih-Wei Liu (cwliu@twins.ee.nctu.edu.tw) 3

What is VSP?

• This course will cover the most important

methodologies for designing custom or semi-

custom VLSI systems for some typical digital

signal processing applications.

• In this course, you will learn how to map DSP

algorithms into VLSI efficiently. Several high-

level algorithm and architecture design

techniques will be introduced that enable joint

optimization across the algorithmic, architectural,

and circuit domains

VSP Lecture0 - Chih-Wei Liu (cwliu@twins.ee.nctu.edu.tw) 4

Data Format Converter

• e.g. 3-by-3 Matrix transposition

input sequence: ABCDEFGHI

output sequence: ADGBEHCFI

Step 1: Lifetime analysis

Sample Tinput Tzlout Tdiff Toutput Life Period cycle

0 1 2 3 4 5 6 7 8 9 10 11 12

A 0 0 0 4 0 ~ 4 A

B 1 3 2 7 1 ~ 7 B

C 2 6 4 10 2 ~ 10 C

D 3 1 -2 5 3 ~ 5 D

E 4 4 0 8 4 ~ 8

E

F 5 7 2 11 5 ~ 11

F

G 6 2 -4 6 6 ~ 6

G

H 7 5 -2 9 7 ~ 9

8 8 0 12 8 H

I ~ 12

I

# live 1 2 3 4 4 4 4 4 4 3 2 1

1 2 3

VSP Lecture0 - Chih-Wei Liu (cwliu@twins.ee.nctu.edu.tw) 5

cycle

0 1 2 3 4 5 6 7 8 9 10 11 12

A

B

Step 2: C

D

Forward-backward

E

F

register allocation

G

H

I

# live 1 2 3 4 4 4 4 4 4 3 2 1

1 2 3

cycle input R1 R2 R3 R4 output cycle input R1 R2 R3 R4 output

0 a 0 a

1 b a 1 b a

2 c b a 2 c b a

3 d c b a 3 d c b a

4 e d c b a a 4 e d c b a a

5 f e d c b d 5 f e d c b d

6 g f e c g 6 g f e b c g

7 h f e 7 h c f e b b

8 i h f e e 8 i h c f e e

9 i h f h 9 i h c f h

10 i 10 i f c c

11 i 11 i f f

12 i i 12 i i

VSP Lecture0 - Chih-Wei Liu (cwliu@twins.ee.nctu.edu.tw) 6

Step 3: Hardware Architecture

output

input R1 R2 R3 R4

cycle input R1 R2 R3 R4 output

0 a

1 b a

2 c b a

3 d c b a

4 e d c b a a

5 f e d c b d

6 g f e b c g

7 h c f e b b

8 i h c f e e

9 i h c f h

10 i f c c

11 i f f

12 i i

VSP Lecture0 - Chih-Wei Liu (cwliu@twins.ee.nctu.edu.tw) 7

Concluding Remarks

• The same mathematical derivation or

algorithm

• Different hardware architecture

– Area consideration

– Speed consideration

– Or, …

• We have to learn more about VLSI

signal processing techniques

VSP Lecture0 - Chih-Wei Liu (cwliu@twins.ee.nctu.edu.tw) 8

Course Outline

• Overview

• Lec 01 : Pipelining & Retiming

– review of Pipelining & Retiming

• Lec 02: Unfolding Transformation

• Lec 03: Folding Transformation

– scheduling

• Case Study I : Programmable/Configurable DSP Architectures

• Lec 05: Systolic Arrays

• Lec 06: Algorithmic Strength Reduction

• Case Study II: FFT Processors

• Lec 08: Bit-Serial Architectures

• Lec 09: Redundant Arithmetic

• Lec 10: Numerical Strength Reduction

• Lec 11: Distributed Arithmetic

VSP Lecture0 - Chih-Wei Liu (cwliu@twins.ee.nctu.edu.tw) 9

HW for Lec. 0

• 5-by-5 Matrix transposition

VSP Lecture0 - Chih-Wei Liu (cwliu@twins.ee.nctu.edu.tw) 10

Você também pode gostar

- VLSI Digital Signal Processing Systems by Keshab K ParhiDocumento25 páginasVLSI Digital Signal Processing Systems by Keshab K Parhirahil1650% (4)

- Bjmp2033 Workshop A171 Suggestion AnswersDocumento20 páginasBjmp2033 Workshop A171 Suggestion AnswersNur Aina Syazwanna100% (1)

- Assignment: MTH601 (Fall 2020)Documento3 páginasAssignment: MTH601 (Fall 2020)Waseem SajjadAinda não há avaliações

- Rev A - HSDPA - HSUPA Performance Assessment Ericsson Cluster Airtel NigeriaDocumento166 páginasRev A - HSDPA - HSUPA Performance Assessment Ericsson Cluster Airtel Nigeriakunle kayodeAinda não há avaliações

- Deep LearningDocumento43 páginasDeep Learningdarshan shahAinda não há avaliações

- Yaprak Testler Sinavlar Aylik Çalişma Kitapçiklari KitaplarDocumento83 páginasYaprak Testler Sinavlar Aylik Çalişma Kitapçiklari KitaplarMon Soleil50% (2)

- Best Practices For Implementing A Secure Application Container ArchitectureDocumento31 páginasBest Practices For Implementing A Secure Application Container ArchitectureDizzyDude100% (1)

- VLSI Signal Processing SystemsDocumento12 páginasVLSI Signal Processing SystemsManju SharmaAinda não há avaliações

- PERT HO 19 - RlNav30RMXDocumento2 páginasPERT HO 19 - RlNav30RMXSHIKHAR ARORAAinda não há avaliações

- Solution: Activity Immediate Predecessors DurationDocumento5 páginasSolution: Activity Immediate Predecessors DurationherrajohnAinda não há avaliações

- Pert-Cpm: 1. Costruct The CPM NetworkDocumento5 páginasPert-Cpm: 1. Costruct The CPM NetworkJohn Bert LuisAinda não há avaliações

- Yadav Sir": DI-QuestionDocumento4 páginasYadav Sir": DI-QuestionDeepak BhartiyaAinda não há avaliações

- Tut 2 PM NEWDocumento11 páginasTut 2 PM NEWMariam MansourAinda não há avaliações

- Gujarat Technological UniversityDocumento2 páginasGujarat Technological UniversityhemalAinda não há avaliações

- Test-2 QTM Attempt Any Three Questions Out of Four. Total Time 10.30-12.45 PM Q1Documento4 páginasTest-2 QTM Attempt Any Three Questions Out of Four. Total Time 10.30-12.45 PM Q1pjAinda não há avaliações

- HT27LC020 Cmos 256K 8-Bit Otp Eprom: FeaturesDocumento16 páginasHT27LC020 Cmos 256K 8-Bit Otp Eprom: FeaturesvetchboyAinda não há avaliações

- Com 111Documento3 páginasCom 111benjamin bandaAinda não há avaliações

- Project Management (Ecu 08604X) Tutorial Questions On CPM and PertDocumento6 páginasProject Management (Ecu 08604X) Tutorial Questions On CPM and PertOLIVA MACHUMUAinda não há avaliações

- Ch03 PM Solved ProblemsDocumento2 páginasCh03 PM Solved ProblemsJonathan GutierrezAinda não há avaliações

- CHE1023: Production and Operations Management Da-IiDocumento3 páginasCHE1023: Production and Operations Management Da-Iivedant vermaAinda não há avaliações

- Project Management 1723Documento4 páginasProject Management 1723rajushamla9927Ainda não há avaliações

- Critical Path Analysis: Applications of Computer in Yarn/Fabric/Wet/Apparel/Management Lecture # Project ManagementDocumento9 páginasCritical Path Analysis: Applications of Computer in Yarn/Fabric/Wet/Apparel/Management Lecture # Project ManagementSuza Ahmed AuporboAinda não há avaliações

- Digital Logic Design Lab: Experiment #5 NAND / NOR Logic Circuit ImplementationDocumento9 páginasDigital Logic Design Lab: Experiment #5 NAND / NOR Logic Circuit ImplementationMohamad MonerAinda não há avaliações

- Activity Expected Time Variance 1-2 10 1 1-3 10 0 1-4 5 1 2-6 7 4 3-6 5 1 3-7 7 1 3-5 2 0 4-5 5 1 5-7 8 4 6-7 4 1Documento3 páginasActivity Expected Time Variance 1-2 10 1 1-3 10 0 1-4 5 1 2-6 7 4 3-6 5 1 3-7 7 1 3-5 2 0 4-5 5 1 5-7 8 4 6-7 4 1Abdul RazzakAinda não há avaliações

- Project Planning & Scheduling ExerciseDocumento3 páginasProject Planning & Scheduling ExerciseDejene AdugnaAinda não há avaliações

- 14-CI-A7 - Version Anglaise - Novembre 2015Documento7 páginas14-CI-A7 - Version Anglaise - Novembre 2015Wael MaroukAinda não há avaliações

- SAT Math NC Bubble SheetDocumento1 páginaSAT Math NC Bubble SheetRyan WangAinda não há avaliações

- Software Engineering Digital Assignment 1: NAME: Amitabh Mishra Reg - No: 18BCI0225Documento12 páginasSoftware Engineering Digital Assignment 1: NAME: Amitabh Mishra Reg - No: 18BCI0225Avk Aryan Vishant KulshreshthaAinda não há avaliações

- Correccion 16 PF CDocumento11 páginasCorreccion 16 PF CCamilo Matias Salinas RodriguezAinda não há avaliações

- BT CQDocumento3 páginasBT CQVo Thi Hoang Oanh B1900557Ainda não há avaliações

- Quiz 6Documento6 páginasQuiz 6TheMaddox5000Ainda não há avaliações

- Activity Immediate Predecessors Duration (In Months)Documento4 páginasActivity Immediate Predecessors Duration (In Months)Babu NarayananAinda não há avaliações

- MTH601 Spring MidTermDocumento7 páginasMTH601 Spring MidTermyobayi5874Ainda não há avaliações

- Poraque, Anthony Jay S. Bsce CE 516 Midterm ExamDocumento10 páginasPoraque, Anthony Jay S. Bsce CE 516 Midterm ExamdarwinAinda não há avaliações

- HT27C020Documento15 páginasHT27C020wardoyoAinda não há avaliações

- Timing Model Reduction For Hierarchical Timing Analysis: Shuo Zhou Synopsys November 7, 2006Documento30 páginasTiming Model Reduction For Hierarchical Timing Analysis: Shuo Zhou Synopsys November 7, 2006Deepak SinghalAinda não há avaliações

- Proj MGMTDocumento26 páginasProj MGMTavantikaAinda não há avaliações

- Anwer Key For Diagnostic Test Engage StarterDocumento1 páginaAnwer Key For Diagnostic Test Engage StarteradriAinda não há avaliações

- COM111 Assignment 1Documento5 páginasCOM111 Assignment 1benjamin bandaAinda não há avaliações

- Problem Set No 1Documento3 páginasProblem Set No 1Catherine HirangAinda não há avaliações

- Pert and CPM: Dr. Vineet TiwariDocumento19 páginasPert and CPM: Dr. Vineet TiwariAbdifatah AbdilahiAinda não há avaliações

- 8 - C - Project Scheduling PERTDocumento3 páginas8 - C - Project Scheduling PERTpranav guptaAinda não há avaliações

- 2023-12-01T073443.739Documento65 páginas2023-12-01T073443.739Korey BradleyAinda não há avaliações

- Assignment 3 PDFDocumento2 páginasAssignment 3 PDFcleousAinda não há avaliações

- TL07 - Selected SolutionDocumento4 páginasTL07 - Selected SolutionWang RunyuAinda não há avaliações

- Gramer Yaprak Testler (Gramer) - Cevap AnahtarıDocumento4 páginasGramer Yaprak Testler (Gramer) - Cevap AnahtarıesraAinda não há avaliações

- Tut 8Documento34 páginasTut 8SeanAinda não há avaliações

- Pert and CPMDocumento3 páginasPert and CPMsravani maddlaAinda não há avaliações

- ContabsandnotationDocumento7 páginasContabsandnotationedward sotoAinda não há avaliações

- Assignment Practice ProblemDocumento23 páginasAssignment Practice ProblemMANASAinda não há avaliações

- Adp 7 Recursos EjemploDocumento4 páginasAdp 7 Recursos Ejemploanahi alvaresAinda não há avaliações

- Assignment 2Documento2 páginasAssignment 2Tejaswani RAinda não há avaliações

- OM Explorer: Solver - Project Management: Single Time EstimateDocumento8 páginasOM Explorer: Solver - Project Management: Single Time EstimateMarco GuzmanAinda não há avaliações

- CPM Network AnalysisDocumento6 páginasCPM Network AnalysisParthJainAinda não há avaliações

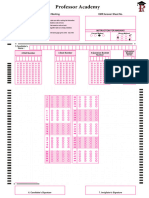

- OMR Sheet - Professor AcademyDocumento1 páginaOMR Sheet - Professor Academyvincy sundara rajAinda não há avaliações

- This Study Resource Was: Problem # 1Documento7 páginasThis Study Resource Was: Problem # 1MELISSA WONG PAU YU -Ainda não há avaliações

- Quiz Om Ascent SupplementDocumento4 páginasQuiz Om Ascent SupplementRahul RavindranathanAinda não há avaliações

- CSE408 Dijkstra, Huffmancoding: Lecture # 27Documento52 páginasCSE408 Dijkstra, Huffmancoding: Lecture # 27avinashAinda não há avaliações

- Activity Predecessor a m b Mean (μ) Variance (σ2) Std Deviation (σ)Documento1 páginaActivity Predecessor a m b Mean (μ) Variance (σ2) Std Deviation (σ)Mc GomezAinda não há avaliações

- Time Management 3 - Precedence NetworksDocumento6 páginasTime Management 3 - Precedence Networksdrelm7399Ainda não há avaliações

- Network Analysis - PERT N CPMDocumento50 páginasNetwork Analysis - PERT N CPMMukesh GautamAinda não há avaliações

- 8611x1 PDFDocumento1 página8611x1 PDFKhiara Claudine EspinosaAinda não há avaliações

- SineDocumento230 páginasSineManish ChavdaAinda não há avaliações

- Chap3 RevisedDocumento1.111 páginasChap3 RevisedManish ChavdaAinda não há avaliações

- Design of A High Frequency Low Voltage CMOS Operational Amplifier Compact Low-Power High Slew-Rate Cmos Buffer Amplifier With Power Gating TechniqueDocumento4 páginasDesign of A High Frequency Low Voltage CMOS Operational Amplifier Compact Low-Power High Slew-Rate Cmos Buffer Amplifier With Power Gating TechniqueManish ChavdaAinda não há avaliações

- Chap3 RevisedDocumento104 páginasChap3 RevisedmanojkumarAinda não há avaliações

- Chap3 RevisedDocumento104 páginasChap3 RevisedmanojkumarAinda não há avaliações

- VSP Lec00 PDFDocumento10 páginasVSP Lec00 PDFManish ChavdaAinda não há avaliações

- Test ScribdDocumento1 páginaTest ScribdManish ChavdaAinda não há avaliações

- Design of A High Frequency Low Voltage CMOS Operational Amplifier Compact Low-Power High Slew-Rate Cmos Buffer Amplifier With Power Gating TechniqueDocumento4 páginasDesign of A High Frequency Low Voltage CMOS Operational Amplifier Compact Low-Power High Slew-Rate Cmos Buffer Amplifier With Power Gating TechniqueManish ChavdaAinda não há avaliações

- Dell Latitude 7420 14 InchDocumento3 páginasDell Latitude 7420 14 InchAto AnsoriAinda não há avaliações

- Final PPT VNNDocumento88 páginasFinal PPT VNNPatel ManavAinda não há avaliações

- Course Title: Linear Integrated Circuits Course Code: 4042 Course Category: B Periods Per Week: 4 Periods Per Semester: 56 Credits: 4Documento4 páginasCourse Title: Linear Integrated Circuits Course Code: 4042 Course Category: B Periods Per Week: 4 Periods Per Semester: 56 Credits: 4Sona PrakashAinda não há avaliações

- PGDIT 101 Introduction To IT and Programming - Lecture 1 Program & Programming LanguagesDocumento12 páginasPGDIT 101 Introduction To IT and Programming - Lecture 1 Program & Programming LanguagesAnwarHossainSaikatAinda não há avaliações

- Autonomous Database Startup GuideDocumento9 páginasAutonomous Database Startup GuidetowAinda não há avaliações

- Events 1 00f9bspta3hc9b09Documento354 páginasEvents 1 00f9bspta3hc9b09Sarhan AhmedovAinda não há avaliações

- WimaxDocumento18 páginasWimaxshrishti.bhatiaAinda não há avaliações

- Image Editor: of Professor & Head, Department of IT, CBITDocumento20 páginasImage Editor: of Professor & Head, Department of IT, CBITmani moorthyAinda não há avaliações

- IO-Link Solutions: Unrestricted © Siemens 2017Documento33 páginasIO-Link Solutions: Unrestricted © Siemens 2017MyScribdAinda não há avaliações

- ManualDocumento121 páginasManualccmcmAinda não há avaliações

- CD54/74HC4059: High-Speed CMOS Logic CMOS Programmable Divide-by-N CounterDocumento7 páginasCD54/74HC4059: High-Speed CMOS Logic CMOS Programmable Divide-by-N CounterDanielAinda não há avaliações

- System Models, Design and ImplementationDocumento20 páginasSystem Models, Design and ImplementationNishanAinda não há avaliações

- Cisco 1100 Series Software Configuration Guide, Cisco IOS XE Fuji 16.9.xDocumento458 páginasCisco 1100 Series Software Configuration Guide, Cisco IOS XE Fuji 16.9.xStefano Di ChioAinda não há avaliações

- Daa Mini ReportDocumento28 páginasDaa Mini ReportMohammed Kaifulla KazimAinda não há avaliações

- Android Development TutorialsDocumento336 páginasAndroid Development TutorialsJesse FrankAinda não há avaliações

- 04 - Network Representations and TopologiesDocumento1 página04 - Network Representations and TopologiesWorldAinda não há avaliações

- The InteractionDocumento20 páginasThe Interactionguardianajohnlee22Ainda não há avaliações

- Chap 4Lesson05Device DriverDocumento14 páginasChap 4Lesson05Device DriverreneeshczAinda não há avaliações

- 4.7.1 Packet Tracer Physical Layer Exploration Physical ModeDocumento31 páginas4.7.1 Packet Tracer Physical Layer Exploration Physical ModeJENTRA SUKMA ASRULIAinda não há avaliações

- Chapter-4 Software Concepts: IntroductionDocumento12 páginasChapter-4 Software Concepts: IntroductionAskok RajAinda não há avaliações

- Grpahics LabDocumento7 páginasGrpahics LabEndash HaileAinda não há avaliações

- BCA 6th Semester SyllabusDocumento11 páginasBCA 6th Semester Syllabusshovongorain1002Ainda não há avaliações

- Dynamips I4 LogDocumento1 páginaDynamips I4 LogAYMAN EL BERKAOUIAinda não há avaliações

- z407 Bluetooth Computer Speakers With SubwooferDocumento34 páginasz407 Bluetooth Computer Speakers With SubwooferCristopher RojasAinda não há avaliações

- Power Off Reset ReasonDocumento4 páginasPower Off Reset ReasonMarlon CameyAinda não há avaliações

- 7 SLAAC RickGrazianiDocumento36 páginas7 SLAAC RickGrazianimtcssnspAinda não há avaliações

- Ansible QuestionsDocumento9 páginasAnsible QuestionsShaik ThajAinda não há avaliações