Escolar Documentos

Profissional Documentos

Cultura Documentos

Si7129DN: Vishay Siliconix

Enviado por

hamada13Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Si7129DN: Vishay Siliconix

Enviado por

hamada13Direitos autorais:

Formatos disponíveis

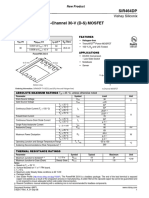

New Product

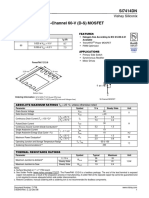

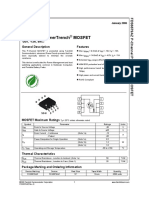

Si7129DN

Vishay Siliconix

P-Channel 30 V (D-S) MOSFET

PRODUCT SUMMARY FEATURES

• Halogen-free According to IEC 61249-2-21

VDS (V) RDS(on) (Ω) ID (A)e,f Qg (Typ.)

Definition

0.0114 at VGS = - 10 V - 35 • TrenchFET® Power MOSFET

- 30 24.6 nC

0.0200 at VGS = - 4.5V - 35 • Low Thermal Resistance PowerPAK®

Package with Small Size and Low 1.07 mm

Profile

• 100 % Rg and UIS Tested

• Compliant to RoHS Directive 2002/95/EC

PowerPAK 1212-8 APPLICATIONS

• Load Switch

S

• Adaptor Switch

3.30 mm 3.30 mm S

1

S • Notebook PC

2

S

3

G

4

D G

8

D

7

D

6

D

5

Bottom View

D

Ordering Information: Si7129DN-T1-GE3 (Lead (Pb)-free and Halogen-free) P-Channel MOSFET

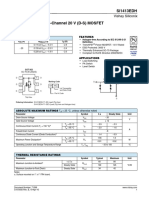

ABSOLUTE MAXIMUM RATINGS (TA = 25 °C, unless otherwise noted)

Parameter Symbol Limit Unit

Drain-Source Voltage VDS - 30

V

Gate-Source Voltage VGS ± 20

TC = 25 °C - 35e

TC = 70 °C - 35e

Continuous Drain Current (TJ = 150 °C) ID

TA = 25 °C - 14.4a, b

TA = 70 °C - 11.5a, b

A

Pulsed Drain Current IDM - 60

TC = 25 °C - 35e

Continuous Source-Drain Diode Current IS

TA = 25 °C - 3.2a, b

Avalanche Current IAS - 25

L = 0.1 mH

Single-Pulse Avalanche Energy EAS 31.25 mJ

TC = 25 °C 52.1

TC = 70 °C 3.3

Maximum Power Dissipation PD W

TA = 25 °C 3.8a, b

TA = 70 °C 2.4a, b

Operating Junction and Storage Temperature Range TJ, Tstg - 50 to 150

c, d

°C

Soldering Recommendations (Peak Temperature) 260

Notes:

a. Surface mounted on 1" x 1" FR4 board.

b. t = 10 s.

c. See solder profile (www.vishay.com/ppg?73257). The PowerPAK 1212-8 is a leadless package. The end of the lead terminal is exposed

copper (not plated) as a result of the singulation process in manufacturing. A solder fillet at the exposed copper tip cannot be guaranteed and

is not required to ensure adequate bottom side solder interconnection.

d. Rework conditions: manual soldering with a soldering iron is not recommended for leadless components.

e. Package limited.

f. Based on TC = 25 °C

Document Number: 68966 www.vishay.com

S10-2023-Rev. B, 06-Sep-10 1

New Product

Si7129DN

Vishay Siliconix

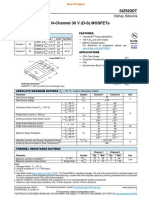

THERMAL RESISTANCE RATINGS

Parameter Symbol Typical Maximum Unit

Maximum Junction-to-Ambienta, b t ≤ 10 s RthJA 26 33

°C/W

Maximum Junction-to-Case (Drain) Steady State RthJC 1.9 2.4

Notes:

a. Surface mounted on 1" x 1" FR4 board.

b. Maximum under Steady State conditions is 81 °C/W.

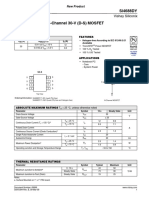

SPECIFICATIONS (TJ = 25 °C, unless otherwise noted)

Parameter Symbol Test Conditions Min. Typ. Max. Unit

Static

Drain-Source Breakdown Voltage VDS VGS = 0 V, ID = - 250 µA - 30 V

VDS Temperature Coefficient ΔVDS/TJ - 20

ID = - 250 µA mV/°C

VGS(th) Temperature Coefficient ΔVGS(th)/TJ 5

Gate-Source Threshold Voltage VGS(th) VDS = VGS, ID = - 250 µA - 1.5 - 2.8 V

Gate-Source Leakage IGSS VDS = 0 V, VGS = ± 20 V ± 100 nA

VDS = - 30 V, VGS = 0 V -1

Zero Gate Voltage Drain Current IDSS µA

VDS = - 30 V, VGS = 0 V, TJ = 55 °C - 10

On-State Drain Currenta ID(on) VDS ≤ - 5 V, VGS = - 10 V - 20 A

VGS = - 10 V, ID = - 14.4 A 0.0095 0.0114

Drain-Source On-State Resistancea RDS(on) Ω

VGS = - 4.5 V, ID = - 11.5 A 0.0160 0.0200

Forward Transconductancea gfs VDS = - 15 V, ID = - 14.4 A 37 S

Dynamicb

Input Capacitance Ciss 2230 3345

Output Capacitance Coss VDS = - 15 V, VGS = 0 V, f = 1 MHz 385 578 pF

Reverse Transfer Capacitance Crss 322

VDS = - 15 V, VGS = - 10 V, ID = - 14.4 A 47.5 71

Total Gate Charge Qg

24.6 37

nC

Gate-Source Charge Qgs VDS = - 15 V, VGS = - 4.5 V, ID = - 14.4 A 7.7

Gate-Drain Charge Qgd 12

Gate Resistance Rg f = 1 MHz 0.4 1.8 3.6 Ω

Turn-On Delay Time td(on) 50 75

Rise Time tr VDD = - 15 V, RL = 1.5 Ω 43 65

Turn-Off DelayTime td(off) ID ≅ - 10 A, VGEN = - 4.5 V, Rg = 1 Ω 30 45

Fall Time tf 14 21

ns

Turn-On Delay Time td(on) 14 21

Rise Time tr VDD = - 15 V, RL = 1.5 Ω 9 18

Turn-Off DelayTime td(off) ID ≅ - 10 A, VGEN = - 10 V, Rg = 1 Ω 36 54

Fall Time tf 10 20

Drain-Source Body Diode Characteristics

Continuous Source-Drain Diode Current IS TC = 25 °C - 35e

A

Pulse Diode Forward Currenta ISM - 60

Body Diode Voltage VSD IF = - 10 A - 0.8 - 1.2 V

Body Diode Reverse Recovery Time trr 31 47 ns

Body Diode Reverse Recovery Charge Qrr 30 45 nC

IF = - 10 A, dI/dt = 100 A/µs, TJ = 25 °C

Reverse Recovery Fall Time ta 15

ns

Reverse Recovery Rise Time tb 16

Notes:

a. Pulse test; pulse width ≤ 300 µs, duty cycle ≤ 2 %.

b. Guaranteed by design, not subject to production testing.

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation

of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum

rating conditions for extended periods may affect device reliability.

www.vishay.com Document Number: 68966

2 S10-2023-Rev. B, 06-Sep-10

New Product

Si7129DN

Vishay Siliconix

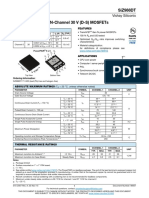

TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

60 1.2

VGS = 10 V thru 5 V

45 0.9

ID - Drain Current (A)

ID - Drain Current (A)

125 ºC

4V

30 0.6

25 ºC

15 0.3

- 55 ºC

0 0.0

0 3 6 9 12 15 0 1 2 3 4

VDS - Drain-to-Source Voltage (V) VGS - Gate-to-Source Voltage (V)

Output Characteristics Transfer Characteristics

0.030 3600

0.025 3000

RDS - On-Resistance (mΩ)

VGS = 4.5 V Ciss

C - Capacitance (pF)

0.020 2400

0.015 1800

VGS = 10 V

0.010 1200

600 Coss

0.005

Crss

0.000 0

0 10 20 30 40 50 60 0 6 12 18 24 30

VDS - Drain-Source Voltage (V)

ID - Drain Current (A)

On-Resistance vs. Drain Current and Gate Voltage Capacitance

10 1.8

ID = 14.4 A

VGS - Gate-to-Source Voltage (V)

8

1.5

RDS(on) - On-Resistance

VDS = 15 V, ID = 14.4 A

(normalized)

VGS = 10 V

6

1.2

4

VGS = 4.5 V

VDS = 24 V, ID = 14.4 A

0.9

2

0 0.6

0 10 20 30 40 50 - 50 - 25 0 25 50 75 100 125 150

Qg - Total Gate Charge (nC) TJ - Junction Temperature (ºC)

Gate Charge On-Resistance vs. Junction Temperature

Document Number: 68966 www.vishay.com

S10-2023-Rev. B, 06-Sep-10 3

New Product

Si7129DN

Vishay Siliconix

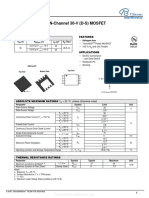

TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

100 0.04

RDS(on) - Drain-to-Source On-Resistance (Ω)

0.03

TJ = 150 ºC

IS - Source Current (A)

10

0.02

TJ = 25 ºC TJ = 125 ºC

1

0.01

TJ = 25 ºC

0.1 0.00

0.0 0.2 0.4 0.6 0.8 1.0 1.2 0 2 4 6 8 10 12 14 16 18 20

VSD - Source-to-Drain Voltage (V) VGS - Gate-to-Source Voltage (V)

Source-Drain Diode Forward Voltage On-Resistance vs. Gate-to-Source Voltage

2.4 50

ID = 250 µA

2.2 40

2.0

Power (W)

30

VGS(th) (V)

1.8

20

1.6

10

1.4

1.2 0

- 50 - 25 0 25 50 75 100 125 150

0.01 0.1 1.0 10 100 1000

TJ - Temperature (ºC)

Time (s)

Threshold Voltage Single Pulse Power, Junction-to-Ambient

100

Limited by RDS(on)* 100 µs

10

ID - Drain Current (A)

1 ms

10ms

1

100 ms

1s

0.1 10 s

TA = 25 ºC DC

Single Pulse BVDSS Limited

0.01

0.1 1 10 10

VDS - Drain-to-Source Voltage (V)

* VGS > minimum VGS at which RDS(on) is Specified

Safe Operating Area, Junction-to-Ambient

www.vishay.com Document Number: 68966

4 S10-2023-Rev. B, 06-Sep-10

New Product

Si7129DN

Vishay Siliconix

TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

60

50

ID - Drain Current (A)

40

30

20

10

0

0 25 50 75 100 125 150

TC - CaseTemperature (°C)

Current Derating*

75 2

60

1.5

Power (W)

45

Power (W)

30

0.5

15

0 0

0 25 50 75 100 125 150 0 25 50 75 100 125 150

TC - Case Temperature (ºC) TA - Ambient Temperature (ºC)

Power, Junction-to-Case Power, Junction-to-Ambient

* The power dissipation PD is based on TJ(max) = 150 °C, using junction-to-case thermal resistance, and is more useful in settling the upper

dissipation limit for cases where additional heatsinking is used. It is used to determine the current rating, when this rating falls below the package

limit.

Document Number: 68966 www.vishay.com

S10-2023-Rev. B, 06-Sep-10 5

New Product

Si7129DN

Vishay Siliconix

TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

1

Duty Cycle = 0.5

Normalized Effective Transient

Thermal Impedance

0.2

0.1 Notes:

0.1

PDM

0.05

t1

t2

0.02 t1

1. Duty Cycle, D =

t2

2. Per Unit Base = RthJA = 50 °C/W

3. TJM - TA = PDMZthJA(t)

Single Pulse 4. Surface Mounted

0.01

10 -4 10 -3 10 -2 10 -1 1 10 100 1000

Square Wave Pulse Duration (s)

Normalized Thermal Transient Impedance, Junction-to-Ambient

1

Duty Cycle = 0.5

Normalized Effective Transient

Thermal Impedance

0.2

0.1

0.1

0.05

0.02

Single Pulse

0.01

10 -4 10 -3 10 -2 10 -1 1

Square Wave Pulse Duration (s)

Normalized Thermal Transient Impedance, Junction-to-Case

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon

Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and

reliability data, see www.vishay.com/ppg?68966.

www.vishay.com Document Number: 68966

6 S10-2023-Rev. B, 06-Sep-10

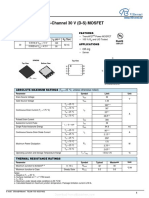

Package Information

www.vishay.com

Vishay Siliconix

PowerPAK® 1212-8, (Single / Dual)

L

H E2 K

D4

W E4

θ

M

8

1 1

e

Z

2

D1

D2

D5

2

D

3

4 5 4

b

θ

L1 E3

θ θ A1

Backside view of single pad

L

H K

A

E2

E4

c

D2 D3(2x) D4

2

1

E1 Detail Z D1

E 2

D5

Notes 3

K1

1. Inch will govern

2 Dimensions exclusive of mold gate burrs D2

4

b

3. Dimensions exclusive of mold flash and cutting burrs

E3

Backside view of dual pad

MILLIMETERS INCHES

DIM.

MIN. NOM. MAX. MIN. NOM. MAX.

A 0.97 1.04 1.12 0.038 0.041 0.044

A1 0.00 - 0.05 0.000 - 0.002

b 0.23 0.30 0.41 0.009 0.012 0.016

c 0.23 0.28 0.33 0.009 0.011 0.013

D 3.20 3.30 3.40 0.126 0.130 0.134

D1 2.95 3.05 3.15 0.116 0.120 0.124

D2 1.98 2.11 2.24 0.078 0.083 0.088

D3 0.48 - 0.89 0.019 - 0.035

D4 0.47 typ. 0.0185 typ

D5 2.3 typ. 0.090 typ

E 3.20 3.30 3.40 0.126 0.130 0.134

E1 2.95 3.05 3.15 0.116 0.120 0.124

E2 1.47 1.60 1.73 0.058 0.063 0.068

E3 1.75 1.85 1.98 0.069 0.073 0.078

E4 0.034 typ. 0.013 typ.

e 0.65 BSC 0.026 BSC

K 0.86 typ. 0.034 typ.

K1 0.35 - - 0.014 - -

H 0.30 0.41 0.51 0.012 0.016 0.020

L 0.30 0.43 0.56 0.012 0.017 0.022

L1 0.06 0.13 0.20 0.002 0.005 0.008

0° - 12° 0° - 12°

W 0.15 0.25 0.36 0.006 0.010 0.014

M 0.125 typ. 0.005 typ.

ECN: S16-2667-Rev. M, 09-Jan-17

DWG: 5882

Revison: 09-Jan-17 1 Document Number: 71656

For technical questions, contact: pmostechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

AN822

Vishay Siliconix

PowerPAK® 1212 Mounting and Thermal Considerations

Johnson Zhao

MOSFETs for switching applications are now available The PowerPAK 1212-8 has a footprint area compara-

with die on resistances around 1 mΩ and with the ble to TSOP-6. It is over 40 % smaller than standard

capability to handle 85 A. While these die capabilities TSSOP-8. Its die capacity is more than twice the size

represent a major advance over what was available of the standard TSOP-6’s. It has thermal performance

just a few years ago, it is important for power MOSFET an order of magnitude better than the SO-8, and 20

packaging technology to keep pace. It should be obvi- times better than TSSOP-8. Its thermal performance is

ous that degradation of a high performance die by the better than all current SMT packages in the market. It

package is undesirable. PowerPAK is a new package will take the advantage of any PC board heat sink

technology that addresses these issues. The PowerPAK capability. Bringing the junction temperature down also

1212-8 provides ultra-low thermal impedance in a increases the die efficiency by around 20 % compared

small package that is ideal for space-constrained with TSSOP-8. For applications where bigger pack-

applications. In this application note, the PowerPAK ages are typically required solely for thermal consider-

1212-8’s construction is described. Following this, ation, the PowerPAK 1212-8 is a good option.

mounting information is presented. Finally, thermal

and electrical performance is discussed. Both the single and dual PowerPAK 1212-8 utilize the

same pin-outs as the single and dual PowerPAK SO-8.

THE PowerPAK PACKAGE The low 1.05 mm PowerPAK height profile makes both

versions an excellent choice for applications with

The PowerPAK 1212-8 package (Figure 1) is a deriva-

space constraints.

tive of PowerPAK SO-8. It utilizes the same packaging

technology, maximizing the die area. The bottom of the

PowerPAK 1212 SINGLE MOUNTING

die attach pad is exposed to provide a direct, low resis-

tance thermal path to the substrate the device is To take the advantage of the single PowerPAK 1212-8’s

mounted on. The PowerPAK 1212-8 thus translates thermal performance see Application Note 826,

the benefits of the PowerPAK SO-8 into a smaller Recommended Minimum Pad Patterns With Outline

package, with the same level of thermal performance. Drawing Access for Vishay Siliconix MOSFETs. Click

(Please refer to application note “PowerPAK SO-8 on the PowerPAK 1212-8 single in the index of this

Mounting and Thermal Considerations.”) document.

In this figure, the drain land pattern is given to make full

contact to the drain pad on the PowerPAK package.

This land pattern can be extended to the left, right, and

top of the drawn pattern. This extension will serve to

increase the heat dissipation by decreasing the ther-

mal resistance from the foot of the PowerPAK to the

PC board and therefore to the ambient. Note that

increasing the drain land area beyond a certain point

will yield little decrease in foot-to-board and foot-to-

ambient thermal resistance. Under specific conditions

of board configuration, copper weight, and layer stack,

experiments have found that adding copper beyond an

area of about 0.3 to 0.5 in2 of will yield little improve-

ment in thermal performance.

Figure 1. PowerPAK 1212 Devices

Document Number 71681 www.vishay.com

03-Mar-06 1

AN822

Vishay Siliconix

PowerPAK 1212 DUAL

To take the advantage of the dual PowerPAK 1212-8’s ture profile used, and the temperatures and time

thermal performance, the minimum recommended duration, are shown in Figures 2 and 3. For the lead

land pattern can be found in Application Note 826, (Pb)-free solder profile, see http://www.vishay.com/

Recommended Minimum Pad Patterns With Outline doc?73257.

Drawing Access for Vishay Siliconix MOSFETs. Click

on the PowerPAK 1212-8 dual in the index of this doc-

ument.

The gap between the two drain pads is 10 mils. This

matches the spacing of the two drain pads on the Pow-

erPAK 1212-8 dual package.

This land pattern can be extended to the left, right, and

top of the drawn pattern. This extension will serve to

increase the heat dissipation by decreasing the ther-

mal resistance from the foot of the PowerPAK to the

PC board and therefore to the ambient. Note that

increasing the drain land area beyond a certain point

will yield little decrease in foot-to-board and foot-to-

ambient thermal resistance. Under specific conditions

of board configuration, copper weight, and layer stack,

experiments have found that adding copper beyond an Ramp-Up Rate + 6 °C /Second Maximum

area of about 0.3 to 0.5 in2 of will yield little improve- Temperature at 155 ± 15 °C 120 Seconds Maximum

ment in thermal performance. Temperature Above 180 °C 70 - 180 Seconds

Maximum Temperature 240 + 5/- 0 °C

Time at Maximum Temperature 20 - 40 Seconds

REFLOW SOLDERING

Ramp-Down Rate + 6 °C/Second Maximum

Vishay Siliconix surface-mount packages meet solder

reflow reliability requirements. Devices are subjected

Figure 2. Solder Reflow Temperature Profile

to solder reflow as a preconditioning test and are then

reliability-tested using temperature cycle, bias humid-

ity, HAST, or pressure pot. The solder reflow tempera-

10 s (max)

210 - 220 °C

3 ° C/s (max) 4 ° C/s (max)

183 °C

140 - 170 °C

50 s (max)

3° C/s (max) 60 s (min) Reflow Zone

Pre-Heating Zone

Maximum peak temperature at 240 °C is allowed.

Figure 3. Solder Reflow Temperatures and Time Durations

www.vishay.com Document Number 71681

2 03-Mar-06

AN822

Vishay Siliconix

TABLE 1: EQIVALENT STEADY STATE PERFORMANCE

Package SO-8 TSSOP-8 TSOP-8 PPAK 1212 PPAK SO-8

Configuration Single Dual Single Dual Single Dual Single Dual Single Dual

Thermal Resiatance RthJC(C/W) 20 40 52 83 40 90 2.4 5.5 1.8 5.5

PowerPAK 1212 Standard SO-8 Standard TSSOP-8 TSOP-6

49.8 °C 85 °C 149 °C 125 °C

2.4 °C/W 20 °C/W 52 °C/W 40 °C/W

PC Board at 45 °C

Figure 4. Temperature of Devices on a PC Board

THERMAL PERFORMANCE

Introduction Spreading Copper

A basic measure of a device’s thermal performance is Designers add additional copper, spreading copper, to

the junction-to-case thermal resistance, Rθjc, or the the drain pad to aid in conducting heat from a device. It

junction to- foot thermal resistance, Rθjf. This parameter is helpful to have some information about the thermal

is measured for the device mounted to an infinite heat performance for a given area of spreading copper.

sink and is therefore a characterization of the device Figure 5 and Figure 6 show the thermal resistance of a

only, in other words, independent of the properties of the PowerPAK 1212-8 single and dual devices mounted on

object to which the device is mounted. Table 1 shows a a 2-in. x 2-in., four-layer FR-4 PC boards. The two inter-

comparison of the PowerPAK 1212-8, PowerPAK SO-8, nal layers and the backside layer are solid copper. The

standard TSSOP-8 and SO-8 equivalent steady state internal layers were chosen as solid copper to model the

performance. large power and ground planes common in many appli-

By minimizing the junction-to-foot thermal resistance, the cations. The top layer was cut back to a smaller area and

MOSFET die temperature is very close to the tempera- at each step junction-to-ambient thermal resistance

ture of the PC board. Consider four devices mounted on measurements were taken. The results indicate that an

a PC board with a board temperature of 45 °C (Figure 4). area above 0.2 to 0.3 square inches of spreading copper

Suppose each device is dissipating 2 W. Using the junc- gives no additional thermal performance improvement.

tion-to-foot thermal resistance characteristics of the A subsequent experiment was run where the copper on

PowerPAK 1212-8 and the other SMT packages, die the back-side was reduced, first to 50 % in stripes to

temperatures are determined to be 49.8 °C for the Pow- mimic circuit traces, and then totally removed. No signif-

erPAK 1212-8, 85 °C for the standard SO-8, 149 °C for icant effect was observed.

standard TSSOP-8, and 125 °C for TSOP-6. This is a

4.8 °C rise above the board temperature for the Power-

PAK 1212-8, and over 40 °C for other SMT packages. A

4.8 °C rise has minimal effect on rDS(ON) whereas a rise

of over 40 °C will cause an increase in rDS(ON) as high

as 20 %.

Document Number 71681 www.vishay.com

03-Mar-06 3

AN822

Vishay Siliconix

105 130

Spreading Copper (sq. in.) 120 Spreading Copper (sq. in.)

95

110

85

100

RthJ A (°C/W)

RthJA (°C/W)

75 90

80

65 50 % 100 %

70

100 %

55 0%

50 % 60

0%

45 50

0.00 0.25 0.50 0.75 1.00 1.25 1.50 1.75 2.00 0.00 0.25 0.50 0.75 1.00 1.25 1.50 1.75 2.00

Figure 5. Spreading Copper - Si7401DN Figure 6. Spreading Copper - Junction-to-Ambient Performance

CONCLUSIONS

As a derivative of the PowerPAK SO-8, the PowerPAK The PowerPAK 1212-8 combines small size with attrac-

1212-8 uses the same packaging technology and has tive thermal characteristics. By minimizing the thermal

been shown to have the same level of thermal perfor- rise above the board temperature, PowerPAK simplifies

mance while having a footprint that is more than 40 % thermal design considerations, allows the device to run

smaller than the standard TSSOP-8. cooler, keeps rDS(ON) low, and permits the device to

Recommended PowerPAK 1212-8 land patterns are handle more current than a same- or larger-size MOS-

provided to aid in PC board layout for designs using this FET die in the standard TSSOP-8 or SO-8 packages.

new package.

www.vishay.com Document Number 71681

4 03-Mar-06

Application Note 826

Vishay Siliconix

RECOMMENDED MINIMUM PADS FOR PowerPAK® 1212-8 Single

0.152

(3.860)

0.039 0.068 0.010

(0.990) (1.725) (0.255)

0.016

(0.405)

(2.235)

(2.390)

0.088

0.094

0.026

(0.660)

0.025 0.030

(0.635) (0.760)

Recommended Minimum Pads

Dimensions in Inches/(mm)

Return to Index

Return to Index

APPLICATION NOTE

Document Number: 72597 www.vishay.com

Revision: 21-Jan-08 7

Legal Disclaimer Notice

www.vishay.com

Vishay

Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE

RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively,

“Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other

disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or

the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all

liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special,

consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular

purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay’s knowledge of

typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding

statements about the suitability of products for a particular application. It is the customer’s responsibility to validate that a

particular product with the properties described in the product specification is suitable for use in a particular application.

Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over

time. All operating parameters, including typical parameters, must be validated for each customer application by the customer’s

technical experts. Product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase,

including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining

applications or for any other application in which the failure of the Vishay product could result in personal injury or death.

Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk.

Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for

such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document

or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

© 2017 VISHAY INTERTECHNOLOGY, INC. ALL RIGHTS RESERVED

Revision: 08-Feb-17 1 Document Number: 91000

Você também pode gostar

- Vishay SIR464DP T1 GE3 DatasheetDocumento7 páginasVishay SIR464DP T1 GE3 DatasheetEge YekkkAinda não há avaliações

- Sir166Dp: Vishay SiliconixDocumento14 páginasSir166Dp: Vishay SiliconixJailani MatondangAinda não há avaliações

- Sira12dp 1764688Documento8 páginasSira12dp 1764688Alex EcheverriaAinda não há avaliações

- Sir474Dp: Vishay SiliconixDocumento13 páginasSir474Dp: Vishay Siliconixservicom3001Ainda não há avaliações

- Si7686DP: Vishay SiliconixDocumento13 páginasSi7686DP: Vishay SiliconixBarbero Pinoy Salonanwar ThegreenShopAinda não há avaliações

- P2003EVG: P-Channel 30-V (D-S) MOSFETDocumento9 páginasP2003EVG: P-Channel 30-V (D-S) MOSFETle2004leyAinda não há avaliações

- P-Channel 30-V (D-S) MOSFET: Features Product SummaryDocumento9 páginasP-Channel 30-V (D-S) MOSFET: Features Product SummaryBedjo TjahmricanAinda não há avaliações

- 17H6GDocumento8 páginas17H6GMie Hijau Tanpa PengawetAinda não há avaliações

- Siz 920 DTDocumento12 páginasSiz 920 DTziya tutuAinda não há avaliações

- Si7137DP: Vishay SiliconixDocumento13 páginasSi7137DP: Vishay SiliconixEduardo CidadeAinda não há avaliações

- SQ7414EN Product Bundle PDFDocumento31 páginasSQ7414EN Product Bundle PDFHarris RaoAinda não há avaliações

- Siz 988 DTDocumento14 páginasSiz 988 DTziya tutuAinda não há avaliações

- Si4413ADY: Vishay SiliconixDocumento9 páginasSi4413ADY: Vishay SiliconixShamim DhaliAinda não há avaliações

- Si 7129 DNDocumento12 páginasSi 7129 DNDimon SergeevichAinda não há avaliações

- Sis 782 DNDocumento12 páginasSis 782 DNnaspauzanAinda não há avaliações

- Si7848DP: Vishay SiliconixDocumento5 páginasSi7848DP: Vishay SiliconixДрагиша Небитни ТрифуновићAinda não há avaliações

- Si7848dp PDFDocumento5 páginasSi7848dp PDFДрагиша Небитни ТрифуновићAinda não há avaliações

- Sir 476Documento13 páginasSir 476Dacyr SiqueiraAinda não há avaliações

- DatasheetDocumento8 páginasDatasheetIvascu IulianAinda não há avaliações

- Si 5429 DuDocumento9 páginasSi 5429 DuGnana SekarAinda não há avaliações

- P-Channel 30-V MOSFET PowerPAK SpecsDocumento6 páginasP-Channel 30-V MOSFET PowerPAK SpecsFabrício CoelhoAinda não há avaliações

- Si7414DN: Vishay SiliconixDocumento11 páginasSi7414DN: Vishay SiliconixthoAinda não há avaliações

- Si 7212 DNDocumento12 páginasSi 7212 DNVenegas GamaAinda não há avaliações

- Dual N-Channel 30 V (D-S) MOSFET: Features Product SummaryDocumento9 páginasDual N-Channel 30 V (D-S) MOSFET: Features Product SummaryNirleudo MaiaAinda não há avaliações

- Si 7403 DNDocumento5 páginasSi 7403 DNJokoKiyerAinda não há avaliações

- Sira06Dp: Vishay SiliconixDocumento13 páginasSira06Dp: Vishay SiliconixArie HariyantoAinda não há avaliações

- Si4447ADY: Vishay SiliconixDocumento9 páginasSi4447ADY: Vishay SiliconixLeandro De VegaAinda não há avaliações

- Sir638Adp: Vishay SiliconixDocumento14 páginasSir638Adp: Vishay SiliconixNiculinaAinda não há avaliações

- Fdms7698: N-Channel Powertrench MosfetDocumento7 páginasFdms7698: N-Channel Powertrench MosfetAdrian Kim BabelaAinda não há avaliações

- Si4835BDY: Vishay SiliconixDocumento6 páginasSi4835BDY: Vishay SiliconixabdelbakiAinda não há avaliações

- 9435GM-P-Channel 30-V (D-S) MOSFETDocumento8 páginas9435GM-P-Channel 30-V (D-S) MOSFETtsromailAinda não há avaliações

- P-Channel 30-V (D-S) MOSFET: Features Product SummaryDocumento9 páginasP-Channel 30-V (D-S) MOSFET: Features Product SummarySantiago Luis GomezAinda não há avaliações

- Fdms7682: N-Channel Powertrench MosfetDocumento8 páginasFdms7682: N-Channel Powertrench MosfetGustavo RodriguezAinda não há avaliações

- Datasheet 1 2Documento2 páginasDatasheet 1 2America SanchezAinda não há avaliações

- General Description Product Summary: 30V P-Channel MOSFETDocumento5 páginasGeneral Description Product Summary: 30V P-Channel MOSFETStoica VictorAinda não há avaliações

- Si1413EDH: Vishay SiliconixDocumento6 páginasSi1413EDH: Vishay SiliconixRamot SimbolonAinda não há avaliações

- Mosfet DataDocumento8 páginasMosfet Dataibnu malkanAinda não há avaliações

- P-Channel 30-V (D-S) MOSFET: Features Product SummaryDocumento8 páginasP-Channel 30-V (D-S) MOSFET: Features Product SummaryYANISSE BADAinda não há avaliações

- 4430GM MosfetDocumento9 páginas4430GM MosfetMie Hijau Tanpa PengawetAinda não há avaliações

- AOSP21357Documento5 páginasAOSP21357Carlos Roman MonkadaAinda não há avaliações

- Si4134DY: Vishay SiliconixDocumento9 páginasSi4134DY: Vishay SiliconixUsep LoadAinda não há avaliações

- MOS650V0.68Ohm43nC650V Power Transistor Data SheetDocumento10 páginasMOS650V0.68Ohm43nC650V Power Transistor Data SheetAshish RanaAinda não há avaliações

- Si4835BDY: Vishay SiliconixDocumento6 páginasSi4835BDY: Vishay SiliconixAku KudupiknikAinda não há avaliações

- Si4410BDY: Vishay SiliconixDocumento8 páginasSi4410BDY: Vishay SiliconixKingsly pitchai muthuAinda não há avaliações

- Si 7850 DPDocumento12 páginasSi 7850 DPvolvoAinda não há avaliações

- Si4362DY: Vishay SiliconixDocumento6 páginasSi4362DY: Vishay Siliconixmanda fanoaAinda não há avaliações

- N-And P-Channel 60-V (D-S) MOSFET: Features Product SummaryDocumento14 páginasN-And P-Channel 60-V (D-S) MOSFET: Features Product SummaryJOHN BRICCO A. MATACSILAinda não há avaliações

- Irfi9Z34G, Sihfi9Z34G: Vishay SiliconixDocumento8 páginasIrfi9Z34G, Sihfi9Z34G: Vishay SiliconixPedro LeonAinda não há avaliações

- Sidr 638 DPDocumento9 páginasSidr 638 DPPM1978Ainda não há avaliações

- N-Channel 650V (D-S) Power MOSFET: Features Product SummaryDocumento10 páginasN-Channel 650V (D-S) Power MOSFET: Features Product SummaryGesiAinda não há avaliações

- $IBOOFM7 %4: Power MOSFETDocumento11 páginas$IBOOFM7 %4: Power MOSFETakmalAinda não há avaliações

- P9NK60ZDocumento10 páginasP9NK60ZisaiasvaAinda não há avaliações

- 2424 FDMS86300Documento7 páginas2424 FDMS86300Ivkan MarsovskiAinda não há avaliações

- HK Si4501bdy 4101260Documento15 páginasHK Si4501bdy 4101260Sahid Cota CamachoAinda não há avaliações

- DatasheetDocumento9 páginasDatasheetHabHabAinda não há avaliações

- Si4688 4688 MosfetDocumento9 páginasSi4688 4688 Mosfetdinh vinh nguyenAinda não há avaliações

- APM2054N: Pin Description FeaturesDocumento12 páginasAPM2054N: Pin Description FeaturespotatoAinda não há avaliações

- Mosfet Si4228dyDocumento9 páginasMosfet Si4228dyBrowsardAinda não há avaliações

- N-Channel 30 V (D-S) MOSFET: Features Product SummaryDocumento7 páginasN-Channel 30 V (D-S) MOSFET: Features Product Summarypglez93Ainda não há avaliações

- Acer Aspire 5742 Compal La 6582p Pew7181 Uma Schematic DiagramDocumento48 páginasAcer Aspire 5742 Compal La 6582p Pew7181 Uma Schematic DiagramBms Inels AutomatizăriAinda não há avaliações

- 978 3 319 72538 3 - 3Documento19 páginas978 3 319 72538 3 - 3hamada13Ainda não há avaliações

- 1N914 Thru 1N4454Documento2 páginas1N914 Thru 1N4454hamada13Ainda não há avaliações

- Samsung LTI460HA01Documento27 páginasSamsung LTI460HA01hamada13Ainda não há avaliações

- Dell 153537 Laptop SchematicsDocumento55 páginasDell 153537 Laptop SchematicsMustafa BozkurtAinda não há avaliações

- Max1630 Max1635Documento29 páginasMax1630 Max1635Giovanni Gomez MoralesAinda não há avaliações

- Dell 153537 Laptop SchematicsDocumento55 páginasDell 153537 Laptop SchematicsMustafa BozkurtAinda não há avaliações

- Dell 153537 Laptop SchematicsDocumento55 páginasDell 153537 Laptop SchematicsMustafa BozkurtAinda não há avaliações

- Smps Diagram SchematicsDocumento33 páginasSmps Diagram SchematicsBeto ZamaAinda não há avaliações

- Smps Diagram SchematicsDocumento33 páginasSmps Diagram SchematicsBeto ZamaAinda não há avaliações

- 2014 TV Firmware Upgrade Instruction T-MST14DEUCDocumento5 páginas2014 TV Firmware Upgrade Instruction T-MST14DEUCRafa MuñozAinda não há avaliações

- Four-Phase Buck PWM Controller With Integrated MOSFET Drivers For Intel VR10, VR11, and AMD ApplicationsDocumento35 páginasFour-Phase Buck PWM Controller With Integrated MOSFET Drivers For Intel VR10, VR11, and AMD Applicationshamada13Ainda não há avaliações

- Intel 815e r1.05 SchematicsDocumento12 páginasIntel 815e r1.05 SchematicsDesperado Manogaran MAinda não há avaliações

- Si4834BDY: Vishay SiliconixDocumento7 páginasSi4834BDY: Vishay Siliconixhamada13Ainda não há avaliações

- RJK0389DPADocumento11 páginasRJK0389DPAhamada13Ainda não há avaliações

- Si7129DN: Vishay SiliconixDocumento13 páginasSi7129DN: Vishay Siliconixhamada13Ainda não há avaliações

- RJK0389DPADocumento11 páginasRJK0389DPAhamada13Ainda não há avaliações

- NCL30100 Fixed Off Time Switched Mode LED Driver ControllerDocumento27 páginasNCL30100 Fixed Off Time Switched Mode LED Driver Controllerhamada13Ainda não há avaliações

- Nec Tokin Oe128 DatasheetDocumento2 páginasNec Tokin Oe128 DatasheetAfwan Al Fauzan Assalafy100% (3)

- FDS6679AZ DatasheetDocumento6 páginasFDS6679AZ DatasheetMarivaldo NascimentoAinda não há avaliações

- G41M-VS3 R2.0Documento51 páginasG41M-VS3 R2.0Kenneth HerreraAinda não há avaliações

- Max1630 Max1635Documento29 páginasMax1630 Max1635Giovanni Gomez MoralesAinda não há avaliações

- Si4834BDY: Vishay SiliconixDocumento7 páginasSi4834BDY: Vishay Siliconixhamada13Ainda não há avaliações

- FDMC4435BZ: P-Channel Power Trench MosfetDocumento7 páginasFDMC4435BZ: P-Channel Power Trench Mosfethamada13Ainda não há avaliações

- Fast Track Troubleshooting Manual for UN32EH5000FXZA LED TVDocumento8 páginasFast Track Troubleshooting Manual for UN32EH5000FXZA LED TVhamada13Ainda não há avaliações

- 2014 TV Firmware Upgrade Instruction T-MST14DEUCDocumento5 páginas2014 TV Firmware Upgrade Instruction T-MST14DEUCRafa MuñozAinda não há avaliações

- AN7522 Audio AmplifierDocumento11 páginasAN7522 Audio Amplifierhamada13Ainda não há avaliações

- AD52580B Audio AmplifierDocumento3 páginasAD52580B Audio Amplifierhamada13Ainda não há avaliações

- KA431-KA431A-KA431L Programmable Shunt RegulatorDocumento12 páginasKA431-KA431A-KA431L Programmable Shunt Regulatorhamada13Ainda não há avaliações

- Nature vs Nurture DebateDocumento3 páginasNature vs Nurture DebateSam GoldbergAinda não há avaliações

- ZXJ 10 SPCDocumento7 páginasZXJ 10 SPCMuhammad Yaseen100% (1)

- Advanced Blueprint 1Documento3 páginasAdvanced Blueprint 1api-728237431Ainda não há avaliações

- IBM Release Notes - IBM SPSS Statistics 21.0 - United States PDFDocumento3 páginasIBM Release Notes - IBM SPSS Statistics 21.0 - United States PDFraj sharmaAinda não há avaliações

- A Comparative Study of Different Image Denoising Methods: Afreen Mulla, A.G.Patil, Sneha Pethkar, Nishigandha DeshmukhDocumento6 páginasA Comparative Study of Different Image Denoising Methods: Afreen Mulla, A.G.Patil, Sneha Pethkar, Nishigandha DeshmukherpublicationAinda não há avaliações

- CP QB PT-3 Harish KumarDocumento3 páginasCP QB PT-3 Harish KumarVISHNU7 77Ainda não há avaliações

- Gmail LogoDocumento12 páginasGmail Logovinodram993480Ainda não há avaliações

- Development Drop - Number - Peformance - For - EstimateDocumento11 páginasDevelopment Drop - Number - Peformance - For - Estimateanon_459056029Ainda não há avaliações

- CM Group Marketing To Gen Z ReportDocumento20 páginasCM Group Marketing To Gen Z Reportroni21Ainda não há avaliações

- Druckabschaltventil enDocumento4 páginasDruckabschaltventil enSakthi Sekar CbiAinda não há avaliações

- Project Planning HandbookDocumento21 páginasProject Planning HandbookPhilip JonesAinda não há avaliações

- The Machine-Room-Less Elevator: Kone E MonospaceDocumento8 páginasThe Machine-Room-Less Elevator: Kone E MonospaceAbdelmuneimAinda não há avaliações

- ME1001, ME1004, ME1005 - Basic Mech+Graphics+Workshop Pract.Documento6 páginasME1001, ME1004, ME1005 - Basic Mech+Graphics+Workshop Pract.Mayank AgarwalAinda não há avaliações

- ¿Cómo Hacerlo?: Dr. Jorge Ramírez Medina, Dr. Guillermo Granados Ruíz EGADE Business SchoolDocumento17 páginas¿Cómo Hacerlo?: Dr. Jorge Ramírez Medina, Dr. Guillermo Granados Ruíz EGADE Business Schoolgalter6Ainda não há avaliações

- ABS Approved Foundries May 12 2014Documento64 páginasABS Approved Foundries May 12 2014Joe ClarkeAinda não há avaliações

- Check For Palindrome: Compute GCD and LCMDocumento3 páginasCheck For Palindrome: Compute GCD and LCMAadhi JAinda não há avaliações

- An Introduction To Pascal Programming MOD 2010Documento5 páginasAn Introduction To Pascal Programming MOD 2010Johnas DalusongAinda não há avaliações

- Wavemakers For Physical Models: EquipmentDocumento10 páginasWavemakers For Physical Models: Equipmentesmaeil013Ainda não há avaliações

- A Study To Assess The Effectiveness of PDocumento9 páginasA Study To Assess The Effectiveness of PKamal JindalAinda não há avaliações

- Veiga Et Al. 2015 - Composition, Structure and Floristic Diversity in Dense Rain Forest inDocumento8 páginasVeiga Et Al. 2015 - Composition, Structure and Floristic Diversity in Dense Rain Forest inYakov Mario QuinterosAinda não há avaliações

- 8.9 Basic Maths For Well PlanningDocumento9 páginas8.9 Basic Maths For Well PlanningKhanh Pham MinhAinda não há avaliações

- Table of Material Properties For Structural Steel S235, S275, S355, S420Documento4 páginasTable of Material Properties For Structural Steel S235, S275, S355, S420Mouhssine BrahmiaAinda não há avaliações

- BS (English) Dept of English University of SargodhaDocumento36 páginasBS (English) Dept of English University of SargodhaFEROZ KHANAinda não há avaliações

- Chlor Rid SlidesDocumento47 páginasChlor Rid Slidesmohammed goudaAinda não há avaliações

- BOQ Sample of Electrical DesignDocumento2 páginasBOQ Sample of Electrical DesignAshik Rahman RifatAinda não há avaliações

- An Overview On Recognition of State in International LawDocumento17 páginasAn Overview On Recognition of State in International LawRamanah VAinda não há avaliações

- DUPLICATE BILL TITLEDocumento8 páginasDUPLICATE BILL TITLEMohammed AhmedAinda não há avaliações

- Kerala University 2013 Admission ProspectusDocumento50 páginasKerala University 2013 Admission ProspectusMuneer SainulabdeenAinda não há avaliações

- Capacitor BanksDocumento49 páginasCapacitor BanksAmal P RaviAinda não há avaliações

- Curriculum Vitae: Name: Mobile: EmailDocumento3 páginasCurriculum Vitae: Name: Mobile: EmailRākesh RakhiAinda não há avaliações