Escolar Documentos

Profissional Documentos

Cultura Documentos

MEL G642-MidSem-Questions 2017-18 PDF

Enviado por

Gaurav PatilTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

MEL G642-MidSem-Questions 2017-18 PDF

Enviado por

Gaurav PatilDireitos autorais:

Formatos disponíveis

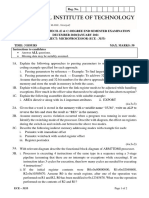

BIRLA INSTITUTE OF TECHNOLOGY & SCIENCE, PILANI

(PILANI, K.K.BIRLA GOA CAMPUSES)

II SEMESTER 2017-18

MEL G642 VLSI ARCHITECTURE 06-03-2018

Mid Sem Exam (CLOSED BOOK) MM:20 Duration 90 min

Q1. (a) What is a Carry select adder?

(b) Supposing you have fast 8 bit adder available to you as a building block, using this building

block and the carry select adder architecture, design the fastest possible 32 bit adder. [1M+3M]

Q2. With the help of schematic diagram explain the two different strategies used for register control

logic design in a CISC microprocessor.[4M]

Q3. With reference to the execution unit block diagram and associated rules of operation (given at

the end of the paper) write level 2 flowcharts for

(a) Address mode sequence for Register Indirect with displacement addressing mode

[Ry+d]@].Clearly state the assumptions you are making.

(b) A common sequence that can implement register to register instructions ADD, SUB and AND.

[3M+3M]

Q4. A CISC instruction set contains a powerful instruction that can test all the elements of a one

dimensional array and return the total count of non-zero elements of the array. RX field in the

instruction word specifies the register that contains the array size (number of elements in the array);

RY field specifies the register into which the count of non-zero elements of the array is returned by

the instruction. Elements of the array are stored in the memory at successive addresses starting

from the absolute address specified in the extension word of the instruction. At the end of the

execution of instruction value of Rx will be Zero

Write level 2 flowcharts for the instruction using the execution unit schematic diagram and rules of

operation given at the end of the QP. [6M]

Rules of Operation for the Execution Unit:

1. A transfer from source to bus to destination takes one state time

2. A source can drive up to three destination loads

3. Inputs to the ALU are from the A internal bus and either K (values 0, +1, -1) or the B internal

bus

4. When the ALU is a destination, T1 is automatically loaded from the ALU output

5. A transfer to AO activates the on-chip external bus controller

6. ALU supports addition and subtraction (B input – A input) operations on 2’s complement

binary integers, and can set condition codes reflecting condition of the ALU

result:V(arithmetic overflow), N(ALU result negative), Z(ALU result zero) when desired, or

leave the condition codes unaltered if so desired.

7. All memory addresses are represented as positive integers in 2’s complement binary

representation

Você também pode gostar

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Ainda não há avaliações

- innovusDBAref PDFDocumento1.373 páginasinnovusDBAref PDFGaurav Patil100% (1)

- Introduction To Pic MicrocontrollerDocumento16 páginasIntroduction To Pic MicrocontrollernothingtohideAinda não há avaliações

- Getdb PDFDocumento25 páginasGetdb PDFGaurav Patil100% (1)

- Getdb PDFDocumento25 páginasGetdb PDFGaurav Patil100% (1)

- Legacy2CUI PDFDocumento17 páginasLegacy2CUI PDFGaurav Patil100% (1)

- Verilog Code For PLLDocumento4 páginasVerilog Code For PLLvenkatraman1983Ainda não há avaliações

- MEL G642-MidSem Exam Question PaperDocumento2 páginasMEL G642-MidSem Exam Question PaperNivedita Acharyya 2035Ainda não há avaliações

- Low Power and Area-Efficient Carry Select Adder: K.SaranyaDocumento4 páginasLow Power and Area-Efficient Carry Select Adder: K.Saranyapraba821Ainda não há avaliações

- Microprocessor (ECE-3153)Documento2 páginasMicroprocessor (ECE-3153)RAHUL RTRAinda não há avaliações

- CA Assignment IIDocumento9 páginasCA Assignment IISomesh ThakurAinda não há avaliações

- An Efficient 64-Bit Carry Select Adder With Less Delay and Reduced Area ApplicationDocumento5 páginasAn Efficient 64-Bit Carry Select Adder With Less Delay and Reduced Area ApplicationkumaranrajAinda não há avaliações

- Microcontroller and Applications Sem II Pattern 2020 Endsem Exam May 2023 - ETCDocumento2 páginasMicrocontroller and Applications Sem II Pattern 2020 Endsem Exam May 2023 - ETCradhika.22210203Ainda não há avaliações

- Microcontroller and Applications Sem II Pattern 2020 Endsem Exam May 2023 - ETCDocumento2 páginasMicrocontroller and Applications Sem II Pattern 2020 Endsem Exam May 2023 - ETCradhika.22210203Ainda não há avaliações

- An Efficient Modified High Speed Square Root Carry Select AdderDocumento4 páginasAn Efficient Modified High Speed Square Root Carry Select Addervanchip28Ainda não há avaliações

- Constant Log BCJR Turbo Decoder With Pipelined ArchitectureDocumento5 páginasConstant Log BCJR Turbo Decoder With Pipelined ArchitectureInternational Journal of Scientific Research and Engineering StudiesAinda não há avaliações

- MST 2017 (O) PDFDocumento2 páginasMST 2017 (O) PDFAdamyaKaushikAinda não há avaliações

- Thapar University, Patiala: Proc # RTN #A RTN #B RTN #C RTN #DDocumento2 páginasThapar University, Patiala: Proc # RTN #A RTN #B RTN #C RTN #DAdamyaKaushikAinda não há avaliações

- 32 Bit Kogge Stone Based Hybrid Adder Implemented Using Standard Cells of Different Logic FamiliesDocumento9 páginas32 Bit Kogge Stone Based Hybrid Adder Implemented Using Standard Cells of Different Logic FamiliesDivya DewkatheAinda não há avaliações

- S.V. National Institute of Technology, Surat: EC306: Embedded SystemsDocumento2 páginasS.V. National Institute of Technology, Surat: EC306: Embedded SystemsBittu GoswamiAinda não há avaliações

- Fpga Implementation of 16 Bit Risc Cpu and Performance AnalysisDocumento4 páginasFpga Implementation of 16 Bit Risc Cpu and Performance AnalysisJournalNX - a Multidisciplinary Peer Reviewed JournalAinda não há avaliações

- CS COA KCS-302 Assignment 1Documento1 páginaCS COA KCS-302 Assignment 1Abhishek MauryaAinda não há avaliações

- Modified Low-Power and Area-Efficient Carry Select Adder Using D-LatchDocumento8 páginasModified Low-Power and Area-Efficient Carry Select Adder Using D-LatchhemanthbbcAinda não há avaliações

- International Journal of Engineering Research and Development (IJERD)Documento7 páginasInternational Journal of Engineering Research and Development (IJERD)IJERDAinda não há avaliações

- University of Bristol Faculty of Engineering: Digital Circuits & Systems EENG14000Documento7 páginasUniversity of Bristol Faculty of Engineering: Digital Circuits & Systems EENG14000栾子璇Ainda não há avaliações

- Carry Select Adder With Low Power and Area Efficiency: Deepthi Obul Reddy, P.Ramesh YadavDocumento7 páginasCarry Select Adder With Low Power and Area Efficiency: Deepthi Obul Reddy, P.Ramesh YadavIJERDAinda não há avaliações

- Assignment-1 - CSE211 - SJDocumento4 páginasAssignment-1 - CSE211 - SJDeepak VishwakarmaAinda não há avaliações

- CA Classes-111-115Documento5 páginasCA Classes-111-115SrinivasaRaoAinda não há avaliações

- Solution To Assignments For BScCSIT 3rd Semester (2069)Documento8 páginasSolution To Assignments For BScCSIT 3rd Semester (2069)Bijay MishraAinda não há avaliações

- Digital Ic Applications: B.Tech II Year II Semester (R07) Supplementary Examinations, April/May 2013Documento1 páginaDigital Ic Applications: B.Tech II Year II Semester (R07) Supplementary Examinations, April/May 2013subbuAinda não há avaliações

- CompreDocumento2 páginasCompref20201654Ainda não há avaliações

- April 2005 WithsloutionDocumento21 páginasApril 2005 Withsloutionapi-3755462Ainda não há avaliações

- Implentation of Goldschmidt's Algorithm For 16 Bit Division and Square RootDocumento13 páginasImplentation of Goldschmidt's Algorithm For 16 Bit Division and Square RootCale Spratt100% (1)

- IEEE Carl HamacherDocumento4 páginasIEEE Carl HamacherSivakumar SoubrayluAinda não há avaliações

- Engineering Journal New Hybrid Concatenated CodesDocumento7 páginasEngineering Journal New Hybrid Concatenated CodesEngineering JournalAinda não há avaliações

- Assignment 1 - CSE211 RGDocumento4 páginasAssignment 1 - CSE211 RGSurya TyagiAinda não há avaliações

- ECE448 S12 In-Class MidtermDocumento3 páginasECE448 S12 In-Class Midtermbilalhabib2001Ainda não há avaliações

- PLC Question BankDocumento3 páginasPLC Question BankAjay kumarAinda não há avaliações

- L-4rr-lI/CSE Date: 27/0312023: Section-ADocumento35 páginasL-4rr-lI/CSE Date: 27/0312023: Section-AQuazi Hasnat IrfanAinda não há avaliações

- Scaling Free CORDIC Algorithm Implementation of Sine and Cosine FunctionDocumento4 páginasScaling Free CORDIC Algorithm Implementation of Sine and Cosine FunctionharivarahiAinda não há avaliações

- Final Apr 03 SolnsDocumento16 páginasFinal Apr 03 Solnsapi-3755462Ainda não há avaliações

- 19ecs431 - Embedded SystemsDocumento18 páginas19ecs431 - Embedded SystemsNaresh KumarAinda não há avaliações

- Efficient Carry Select Adder using 0.12μm Technology for Low Power ApplicationsDocumento4 páginasEfficient Carry Select Adder using 0.12μm Technology for Low Power ApplicationsUmamahesh MavuluriAinda não há avaliações

- Embedded Processors - PRELIM - QP - 2017-18Documento2 páginasEmbedded Processors - PRELIM - QP - 2017-18harshad lokhandeAinda não há avaliações

- Me 1Documento436 páginasMe 1Akshay Mane0% (1)

- 38 DLD SAK Final Assessment Spring 2020 StudName StudIDDocumento3 páginas38 DLD SAK Final Assessment Spring 2020 StudName StudIDBilal AnsariAinda não há avaliações

- Dec 2009Documento2 páginasDec 2009sandeepaprAinda não há avaliações

- Cst202 Scheme July 2021Documento13 páginasCst202 Scheme July 2021Arun JoseAinda não há avaliações

- F Capacitor, Find The Appropriate Value ofDocumento2 páginasF Capacitor, Find The Appropriate Value ofJoginder YadavAinda não há avaliações

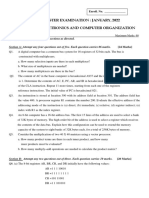

- End Semester Examination: January, 2022 Digital Electronics and Computer OrganizationDocumento3 páginasEnd Semester Examination: January, 2022 Digital Electronics and Computer OrganizationFFFAinda não há avaliações

- Question Paper With Solution of Computer Organization Dec-2020Documento15 páginasQuestion Paper With Solution of Computer Organization Dec-2020Anuja GaikwadAinda não há avaliações

- Switching Theory and Logic DesignDocumento8 páginasSwitching Theory and Logic DesignVenkat ChadalavadaAinda não há avaliações

- Switching Theory and Logic Design April 2019 PDFDocumento4 páginasSwitching Theory and Logic Design April 2019 PDFTulasi LassiAinda não há avaliações

- Microprocessors (CSE 206) (Makeup)Documento2 páginasMicroprocessors (CSE 206) (Makeup)Vishal VimalkumarAinda não há avaliações

- CS2102 Computer System ArchitectureDocumento2 páginasCS2102 Computer System ArchitectureDhyey DESAIIIAinda não há avaliações

- Pmas Arid Agriculture University Rawalpindi: Final Term Examination-Fall 2014Documento2 páginasPmas Arid Agriculture University Rawalpindi: Final Term Examination-Fall 2014Ayesha banoAinda não há avaliações

- Tutorial 3 2022 StudentsDocumento5 páginasTutorial 3 2022 StudentsIndongo EliaserAinda não há avaliações

- Final Exam of COADocumento3 páginasFinal Exam of COATigabu Yaya100% (1)

- Assignment On Module 2Documento2 páginasAssignment On Module 2chaitanyaAinda não há avaliações

- SS 9A04602 Microprocessors & Microcontrollers6Documento1 páginaSS 9A04602 Microprocessors & Microcontrollers6subbuAinda não há avaliações

- Control System Engineering 3Documento3 páginasControl System Engineering 3Mohamed RiyaazAinda não há avaliações

- Practical-1 AIM: Implement Register Transfer Operation in Logisim SimulatorDocumento23 páginasPractical-1 AIM: Implement Register Transfer Operation in Logisim SimulatorDigvijay Sinh ChauhanAinda não há avaliações

- E6995ca TutDocumento14 páginasE6995ca Tutrabinoss0% (1)

- Sheet FourDocumento3 páginasSheet FourRana BadranAinda não há avaliações

- Inner and Outer Decoding Performance of Convolutional Codes: MelindaDocumento6 páginasInner and Outer Decoding Performance of Convolutional Codes: MelindaAiShaKhanAinda não há avaliações

- Sigma Delta AdcDocumento3 páginasSigma Delta AdcGaurav PatilAinda não há avaliações

- Lecture-ASIP DSP ImplementationDocumento49 páginasLecture-ASIP DSP ImplementationGaurav PatilAinda não há avaliações

- PDFDocumento16 páginasPDFGaurav PatilAinda não há avaliações

- Flow MapDocumento12 páginasFlow MapGaurav PatilAinda não há avaliações

- Question Paper (Unit-Test-1) Analog IC Design (MEL G 632) Date: 21-02-2017 Time: 12:00 Hours To 13:00 Hours Closed Book Full-Marks: 15Documento2 páginasQuestion Paper (Unit-Test-1) Analog IC Design (MEL G 632) Date: 21-02-2017 Time: 12:00 Hours To 13:00 Hours Closed Book Full-Marks: 15Gaurav PatilAinda não há avaliações

- MEL G642-Compre Solution - 2 2016-17Documento9 páginasMEL G642-Compre Solution - 2 2016-17Gaurav PatilAinda não há avaliações

- LogDocumento15 páginasLogSadia KhurramAinda não há avaliações

- Tutorial Questions Ch7Documento20 páginasTutorial Questions Ch7Shri KumaranAinda não há avaliações

- Bill of Materials 555Documento1 páginaBill of Materials 555Daniel Hernandez GarciaAinda não há avaliações

- Micropro Compilation ReinierDocumento16 páginasMicropro Compilation ReinierKei DeeAinda não há avaliações

- Analysis of Radiation-Induced Transient Errors On 7 NM FinFET TechnologyDocumento5 páginasAnalysis of Radiation-Induced Transient Errors On 7 NM FinFET TechnologyDanisi ObregonAinda não há avaliações

- Assignment 2Documento2 páginasAssignment 2preetik917Ainda não há avaliações

- Cse - 321 - 2Documento37 páginasCse - 321 - 2lizuAinda não há avaliações

- DD Lab Manual PDFDocumento337 páginasDD Lab Manual PDFAnkit SharmaAinda não há avaliações

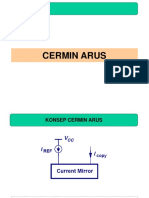

- Cermin ArusDocumento24 páginasCermin ArusMarissa Tania TAinda não há avaliações

- Interrupt Service (Handling) MechanismDocumento20 páginasInterrupt Service (Handling) MechanismManan MehtaAinda não há avaliações

- GrlibDocumento85 páginasGrlibshrikul.joshi100% (1)

- VerilogA ModelingDocumento15 páginasVerilogA ModelingNourAinda não há avaliações

- Switching Circuits and Logic DesignsDocumento4 páginasSwitching Circuits and Logic DesignsTrustWorthy100Ainda não há avaliações

- VLSI SYllabus With CODocumento1 páginaVLSI SYllabus With COchandranv76Ainda não há avaliações

- Lab Manual # 04 Power Electronics Lab: Submitted ToDocumento8 páginasLab Manual # 04 Power Electronics Lab: Submitted ToEngr Abdul QadeerAinda não há avaliações

- Demultiplexer AdocDocumento10 páginasDemultiplexer Adocy.harsha vardhan reddyAinda não há avaliações

- HDI Stackup Planner - Detailed Report For HSP-289295 Option ADocumento2 páginasHDI Stackup Planner - Detailed Report For HSP-289295 Option AAlbert NguyenAinda não há avaliações

- Pg063 Dist Mem GenDocumento60 páginasPg063 Dist Mem GendanicasAinda não há avaliações

- Difference Between Von Neumann and Harvard ArchitectureDocumento6 páginasDifference Between Von Neumann and Harvard ArchitectureSuraj KhatalAinda não há avaliações

- Advanced Packaging TechnologiesDocumento5 páginasAdvanced Packaging TechnologiesSam HongAinda não há avaliações

- Organisasi Dan Arsitektur Komputer: CPU Execution Time Amil A. IlhamDocumento19 páginasOrganisasi Dan Arsitektur Komputer: CPU Execution Time Amil A. IlhamcharlesAinda não há avaliações

- What Is Altera FPGA Development BoardDocumento12 páginasWhat Is Altera FPGA Development BoardjackAinda não há avaliações

- On Timing Closure: Hold-Violation Removal Using Insertion of Buffers, Inverters and Delay CellsDocumento5 páginasOn Timing Closure: Hold-Violation Removal Using Insertion of Buffers, Inverters and Delay CellsabhiAinda não há avaliações

- Lab 7Documento6 páginasLab 7Minh NamAinda não há avaliações

- Unit 2 - Over View + DEDocumento23 páginasUnit 2 - Over View + DEJaswanth SuggulaAinda não há avaliações

- Datasheet Ic 74hc123aDocumento4 páginasDatasheet Ic 74hc123aNayla AzzahraAinda não há avaliações

- CDA3101 L01 Introduction MSSDocumento20 páginasCDA3101 L01 Introduction MSSRosemond FabienAinda não há avaliações

- 02 - Building A RegisterDocumento16 páginas02 - Building A RegisterfayeqAinda não há avaliações